# 12 V/24 V smart analog high-side MOSFET gate driver

#### **Features**

- PRO-SIL<sup>™</sup> ISO 26262-ready for supporting the integrator in evaluation of hardware element according to ISO 26262:2018 Clause 8-13

- · One channel device with two high-side gate driver outputs

- 3  $\Omega$  pull-down, 50  $\Omega$  pull-up for fast switch on/off

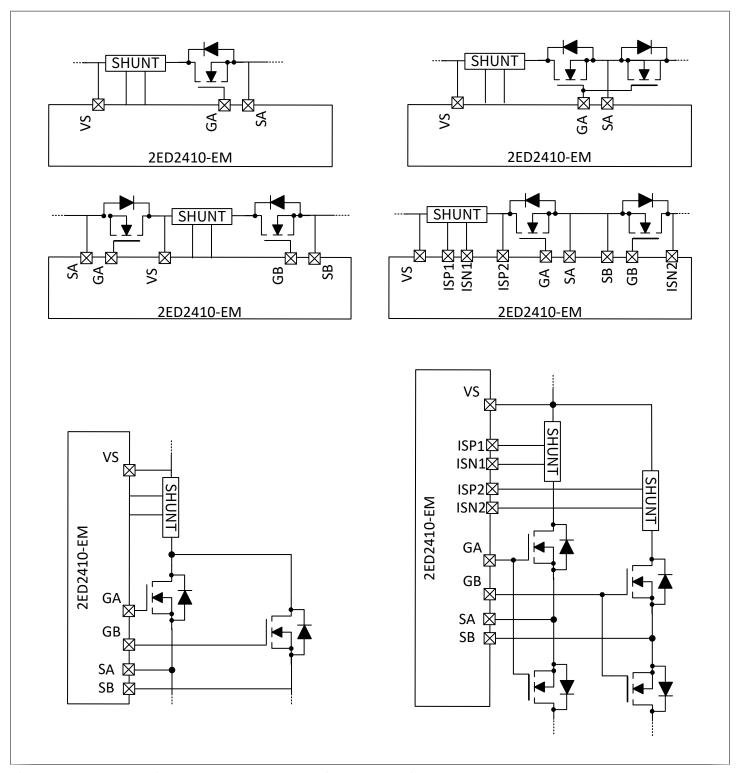

- Support back-to-back MOSFET topologies (common drain and common source)

- Two bidirectional high-side analog current sense interfaces with externally adjustable gain

- Adjustable overcurrent/short-circuit protection

- Versatile comparator to implement: adjustable I-t wire protection, overvoltage/undervoltage or overtemperature protection

# September 1

## **Potential applications**

- Fail operational power supply targeting high current applications

- Connection/isolation switch between power supplies (e.g. for hybrids and electric vehicles)

- Developed to support dependable power supply and distribution

#### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100, Grade 1.

## **Description**

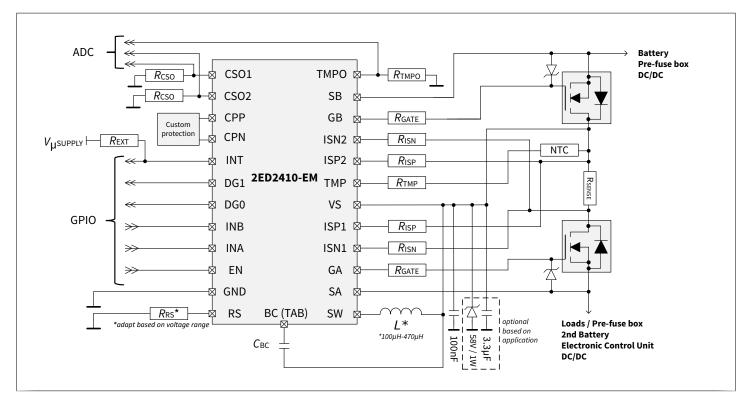

2ED2410-EM is a one channel gate driver with two independent gate outputs for 12 / 24 V automotive applications. It offers several protection features for connecting/disconnecting loads or different power supplies.

Typical application example

| Product type | Package     | Marking    |  |  |

|--------------|-------------|------------|--|--|

| 2ED2410-EM   | PG-TSDSO-24 | 2ED2410-EM |  |  |

## Datasheet

## **Table of contents**

|     | Table of contents                                           | 2              |

|-----|-------------------------------------------------------------|----------------|

| 1   | Block diagrams                                              | 4              |

| 2   | Pin configuration                                           | 6              |

| 3   | General product characteristics                             | 9              |

| 3.1 | Absolute maximum ratings                                    | 9              |

| 3.2 | Functional ranges                                           | 9              |

| 3.3 | Thermal characteristics                                     | LO             |

| 4   | Electrical characteristics                                  | 11             |

| 4.1 | Static electrical characteristics                           | 11             |

| 4.2 | Protection characteristics                                  | 12             |

| 4.3 | Driver outputs electrical characteristics                   | 13             |

| 4.4 | Boost converter (BC) characteristics                        | 14             |

| 4.5 | Current consumptions                                        | 15             |

| 5   | General operation                                           | ۱7             |

| 5.1 | Operating modes                                             | ۱7             |

| 5.2 | Current consumption                                         | ۱7             |

| 5.3 | Timing diagram                                              | 18             |

| 5.4 | Logic pins                                                  | 19             |

| 5.5 | Gate outputs                                                | 20             |

| 5.6 | Ground loss protection: module level                        | 22             |

| 6   | Low by-pass current feature                                 | 23             |

| 7   | Measurement features                                        | 24             |

| 7.1 | VDS monitoring in IDLE mode                                 | 24             |

| 7.2 | Current senses in ON and SAFESTATE modes                    | 25             |

| 7.3 | Temperature measurement amplifier in ON and SAFESTATE modes | 27             |

| 8   | Protections features in ON mode                             | 28             |

| 8.1 | Short-circuit protection                                    | 28             |

| 8.2 | Undervoltage protection on VS                               | 29             |

| 8.3 | Custom protections with comparator                          | 30             |

| 8.4 | Gate undervoltage lock-out protection                       | 31             |

| 8.5 | Reset of SAFESTATE                                          | 31             |

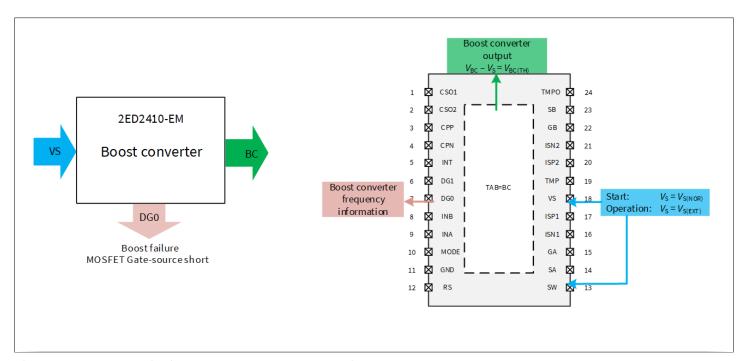

| 9   | Driver supply: boost converter                              | 32             |

| 10  | MOSFET connections in application                           | 35             |

| 11  | Characterization graphs                                     | 37             |

| 12  | Package information                                         | <del>1</del> 5 |

|     | Revision history                                            | 18             |

## **Datasheet**

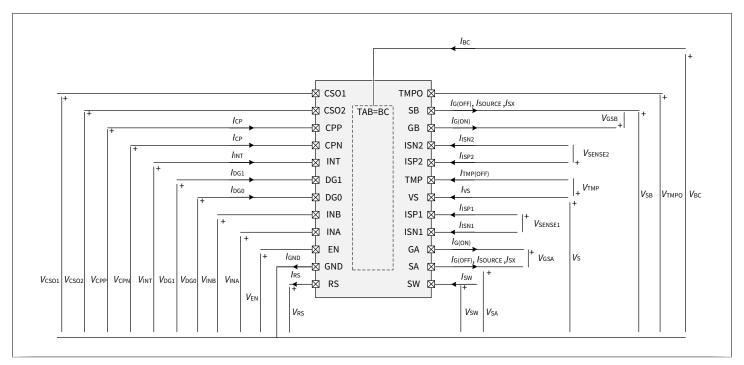

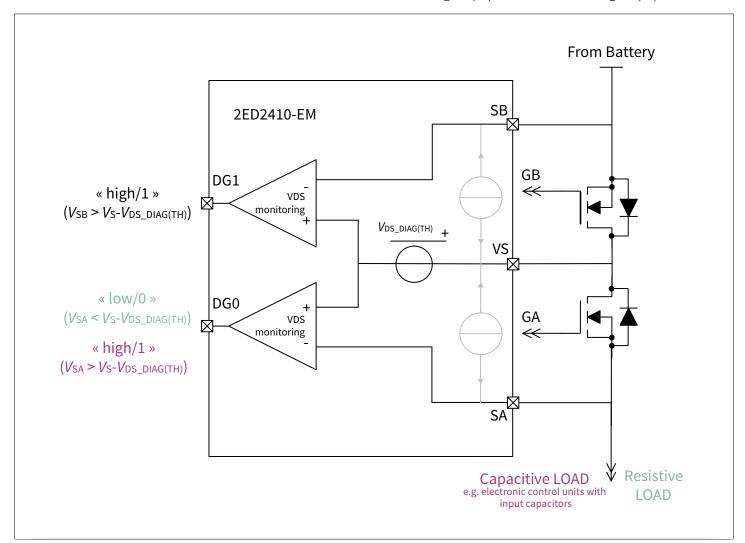

1 Block diagrams

## 1 Block diagrams

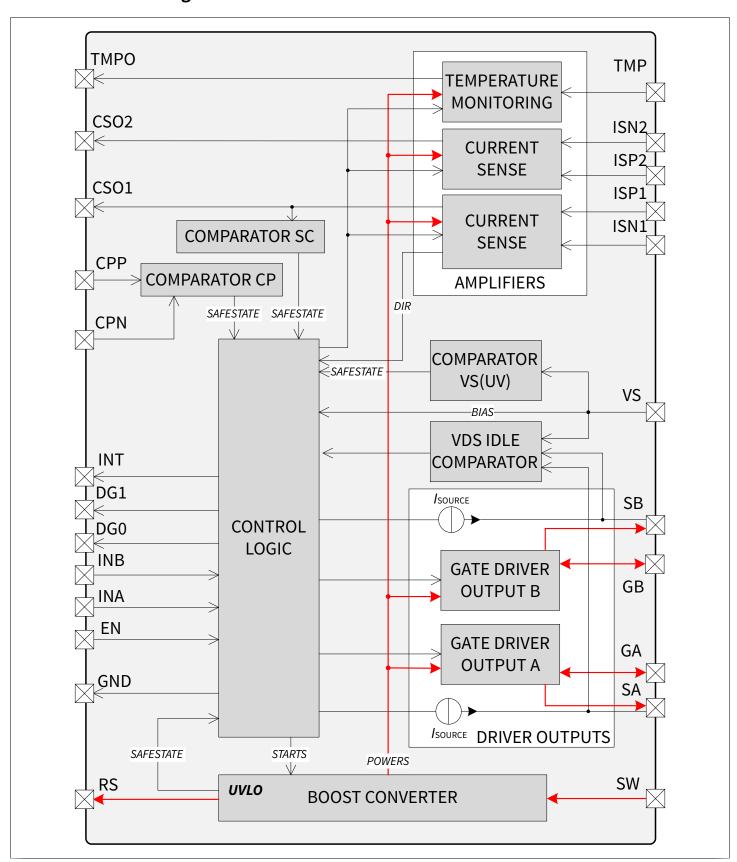

Figure 2 Functional block diagram

## **Datasheet**

1 Block diagrams

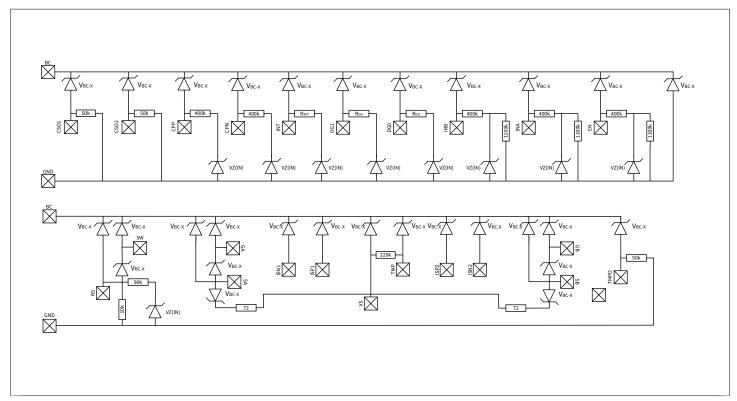

Figure 3 Diodes block diagram

#### **Datasheet**

2 Pin configuration

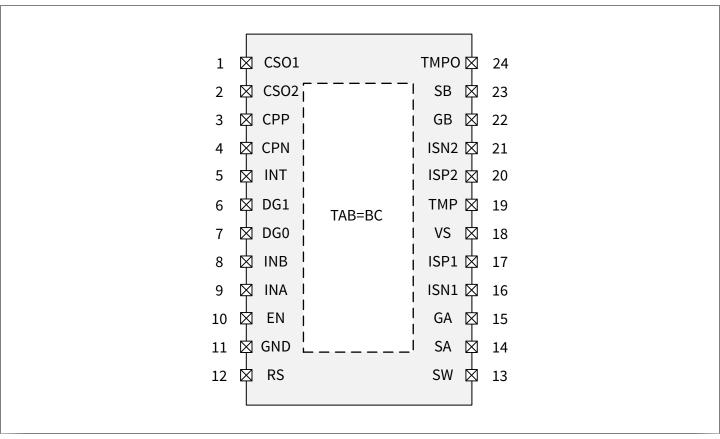

# 2 Pin configuration

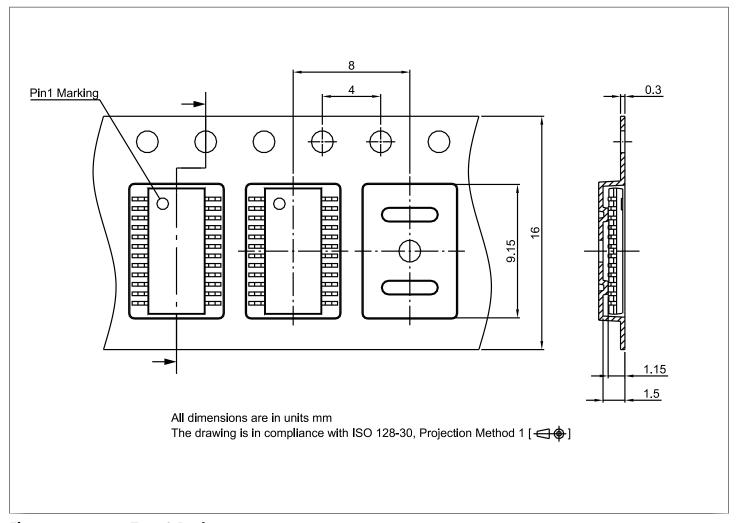

Figure 4

Table 1Pin definitions and functions

| Pin<br>number | Symbol | I/O | Function                                                                                                                                                       |

|---------------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | CSO1   | I   | Analog voltage to force SAFESTATE mode.                                                                                                                        |

|               |        | 0   | <b>C</b> urrent <b>S</b> ense <b>O</b> utput <b>1</b> : analog voltage feedback, provides a voltage proportional to the shunt current or VDS across ISP1/ISN1. |

| 2             | CSO2   | 0   | <b>C</b> urrent <b>S</b> ense <b>O</b> utput <b>2</b> : analog voltage feedback, provides a voltage proportional to the shunt current or VDS across ISP2/ISN2. |

| 3             | СРР    | I   | Comparator Positive: analog positive input of comparator.                                                                                                      |

| 4             | CPN    | I   | Comparator Negative: analog negative input of comparator.                                                                                                      |

| 5             | INT    | 0   | Interrupt: open drain interrupt output.                                                                                                                        |

(table continues...)

## **Datasheet**

2 Pin configuration

| Table 1 | (co  | ontinued) | Pin definitions and functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6       | DG1  | 0         | Diagnostic 1:  DG1 is logic low in SLEEP mode.  Digital voltage information of channel B VDS comparison to VS in IDLE mode.  Digital voltage information of current flow direction in ON mode:  DG1 is logic high if current flows from ISP1 to ISN1 connection  DG1 is logic low if current flows from ISN1 to ISP1 connection  Digital voltage information in SAFESTATE mode:  DG1 is logic high if SAFESTATE because of CP or SC or VS(UV)  DG1 is logic low if SAFESTATE because of UVLO |

| 7       | DG0  | 0         | Diagnostic 0:  DG0 is logic low in SLEEP mode.  Digital voltage information of channel A VDS comparison to VS in IDLE mode.  Digital voltage information of boost converter frequency in ON mode.  Digital information in SAFESTATE mode:  DG0 is logic high if SAFESTATE because of CP or UVLO  DG0 is logic low if SAFESTATE because of SC or VS(UV)                                                                                                                                       |

| 8       | INB  | I         | Input B:  If INB digital logic is low, channel B switches OFF. If INB digital logic is high, channel B switches ON and gate driver is in ON mode only if pin ENABLE is logic high.                                                                                                                                                                                                                                                                                                           |

| 9       | INA  | I         | Input A:  If INA digital logic is low, channel A switches OFF. If INA digital logic is high, channel A switches ON and gate driver is in ON mode only if pin ENABLE is logic high.                                                                                                                                                                                                                                                                                                           |

| 10      | EN   | I         | If <b>EN</b> ABLE digital logic is low, gate driver is in SLEEP mode, channels A and B are switched OFF and gate driver is RESET.  If ENABLE digital logic is high, gate driver is in IDLE mode when INA and INB are both logic low.                                                                                                                                                                                                                                                         |

| 11      | GND  | I/O       | Ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12      | RS   | 0         | <b>R</b> esistor <b>s</b> ense output of boost converter: current measurement of the boost converter.                                                                                                                                                                                                                                                                                                                                                                                        |

| 13      | SW   | I         | <b>Sw</b> itching supply input of boost converter. Inductance connection.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14      | SA   | 0         | Source A: output A connection to external MOSFET sources.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15      | GA   | I/O       | Gate A: output A connection to external MOSFET gates.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16      | ISN1 | I         | I Sense Negative 1: external shunt or VDS negative connection.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 17      | ISP1 | I         | I Sense Positive 1: external shunt or VDS positive connection.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18      | VS   | I/O       | <b>V</b> oltage reference, extended 3 V to 58 V.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19      | TMP  | I         | <b>T</b> e <b>mp</b> erature Input: analog connection to external NTC or PTC thermistor.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20      | ISP2 | I         | I Sense Positive 2: external shunt or VDS negative connection.                                                                                                                                                                                                                                                                                                                                                                                                                               |

(table continues...)

## **Datasheet**

2 Pin configuration

## Table 1 (continued) Pin definitions and functions

| 21  | ISN2 | 1   | I <b>S</b> ense <b>N</b> egative 2: external shunt or VDS positive connection.                                         |

|-----|------|-----|------------------------------------------------------------------------------------------------------------------------|

| 22  | GB   | I/O | Gate B: output B connection to external MOSFET gates.                                                                  |

| 23  | SB   | 1   | <b>S</b> ource <b>B</b> : output B connection to external MOSFET sources.                                              |

| 24  | ТМРО | 0   | <b>Temp</b> erature <b>O</b> utput: analog voltage feedback provides a voltage proportional to thermistor temperature. |

| TAB | ВС   | 0   | <b>B</b> oost <b>C</b> onverter output capacitor connection; driver supply.                                            |

Voltages are defined positive with respect to ground.

Currents are defined flowing into or from the pin depending on pins.

Figure 5 Voltage and current definitions – IEC 60375

#### **Datasheet**

3 General product characteristics

## **3** General product characteristics

# 3.1 Absolute maximum ratings

$T_J = -40$ °C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

Table 2 Absolute maximum ratings

| Parameter                                                         | Symbol                            |      | Values | 1    | Unit | Note or condition                                                       | P-<br>Number |

|-------------------------------------------------------------------|-----------------------------------|------|--------|------|------|-------------------------------------------------------------------------|--------------|

|                                                                   |                                   | Min. | Тур.   | Max. |      |                                                                         |              |

| Maximum voltage VBC (boost converter output) - all pins           | V <sub>BC</sub> - X               | -0.3 | _      | 75   | V    | 1)                                                                      | PRQ-26       |

| Maximum drain-source<br>voltages on each output                   | V <sub>S</sub> - V <sub>SX</sub>  | -36  | -      | 75   | V    | 1)                                                                      | PRQ-14       |

| Maximum voltage between<br>gate and source pins on each<br>output | V <sub>GX</sub> - V <sub>SX</sub> | -0.3 | _      | 75   | V    | 1)                                                                      | PRQ-331      |

| Maximum voltage between<br>SW and RS pin                          | V <sub>SW</sub> - V <sub>RS</sub> | -0.3 | -      | 75   | V    | 1)                                                                      | PRQ-332      |

| Maximum pulsed current in SW pin                                  | I <sub>SW</sub>                   | _    | _      | 200  | mA   | 1)                                                                      | PRQ-16       |

| Maximum operating junction temperature                            | $T_{J(MAX)}$                      | -40  | _      | 150  | °C   | 1)                                                                      | PRQ-23       |

| Storage temperature                                               | T <sub>STG(MAX)</sub>             | -55  | _      | 150  | °C   | 1)                                                                      | PRQ-24       |

| ESD HBM susceptibility all pins                                   | V <sub>ESD(HBM)</sub>             | -2   | -      | 2    | kV   | 1) HBM according to ANSI/ESDA/JEDEC JS001 (1.5 kΩ, 100 pF)              | PRQ-130      |

| ESD CDM susceptibility all pins                                   | V <sub>ESD(CDM)</sub>             | -500 | -      | 500  | V    | Charged Device Model<br>"CDM" according<br>to ANSI/ESDA/JEDEC<br>JS-002 | PRQ-131      |

| ESD CDM susceptibility<br>corner pins                             | V <sub>ESD(CDM)</sub>             | -750 | -      | 750  | V    | Charged Device Model "CDM" according to ANSI/ESDA/JEDEC JS-002          | PRQ-132      |

<sup>1)</sup> Not subject to production test, specified by design

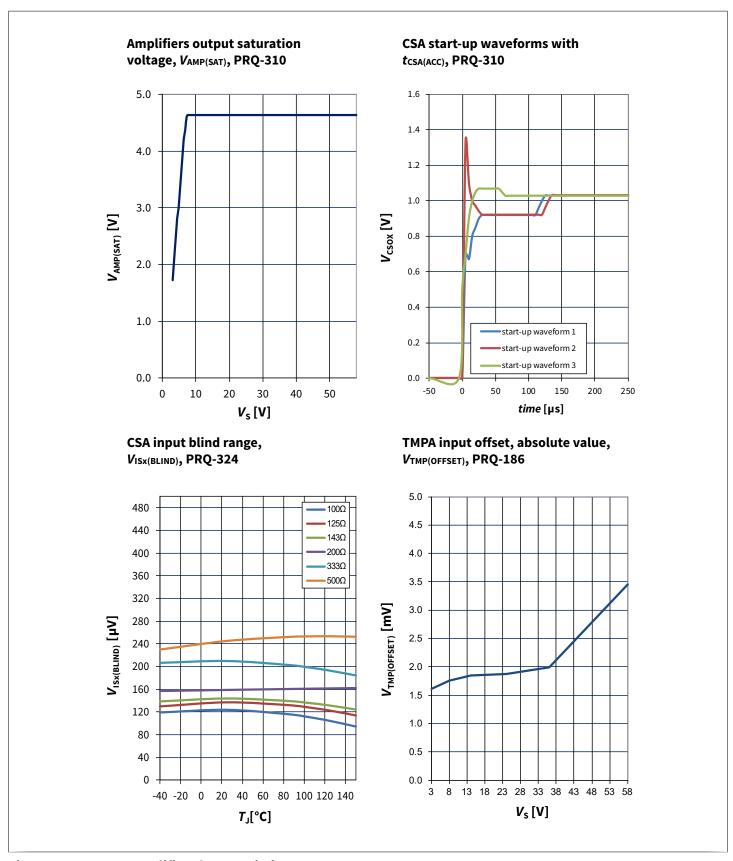

## 3.2 Functional ranges

$T_J$  = -40 to 150°C, all voltages with respect to ground, typical values are given for  $V_S$  = 14 V and  $T_J$  = 25°C

#### **Datasheet**

3 General product characteristics

## Table 3 Functional ranges

| Parameter                                                   | Symbol                                 |      | Values |                                 | Unit | Note or condition                                        | P-      |

|-------------------------------------------------------------|----------------------------------------|------|--------|---------------------------------|------|----------------------------------------------------------|---------|

|                                                             |                                        | Min. | Тур.   | Max.                            |      |                                                          | Number  |

| Voltage reference range for normal operation                | V <sub>S(NOR)</sub>                    | 8    | -      | 36                              | V    | 1)                                                       | PRQ-39  |

| Voltage reference extended range                            | $V_{S(EXT)}$                           | 3    | -      | 58                              | V    | Parameter deviations possible                            | PRQ-266 |

| Voltage reference range with lower short-circuit protection | V <sub>S(SC)LOW</sub>                  | 3    | _      | 8                               | V    | 1)                                                       | PRQ-40  |

| Input pins ENABLE, INA, INB                                 | $V_{\rm EN}, V_{\rm INA}, V_{\rm INB}$ | 0    | -      | 5.5                             | V    | 1)                                                       | PRQ-307 |

| Diagnostic pins DG0, DG1                                    | $V_{\rm DG0}, V_{\rm DG1}$             | 0    | _      | k <sub>DG</sub> *V <sub>E</sub> | V    | See $k_{DG}$ parameter                                   | PRQ-308 |

| Interrupt pin INT                                           | $V_{INT}$                              | 0    | _      | 5.5                             | V    | 1)                                                       | PRQ-309 |

| Comparator reference<br>voltage pins CPN, CPP               | V <sub>CP(REF)</sub>                   | 1    | _      | 5.5                             | V    | 1)                                                       | PRQ-183 |

| Analog output pins<br>saturation CSO 1&2, TMPO              | V <sub>AMP(SAT)</sub>                  | 4    | 4.6    | 5.5                             | V    | $V_{\rm S} = V_{\rm S(NOR)}$                             | PRQ-310 |

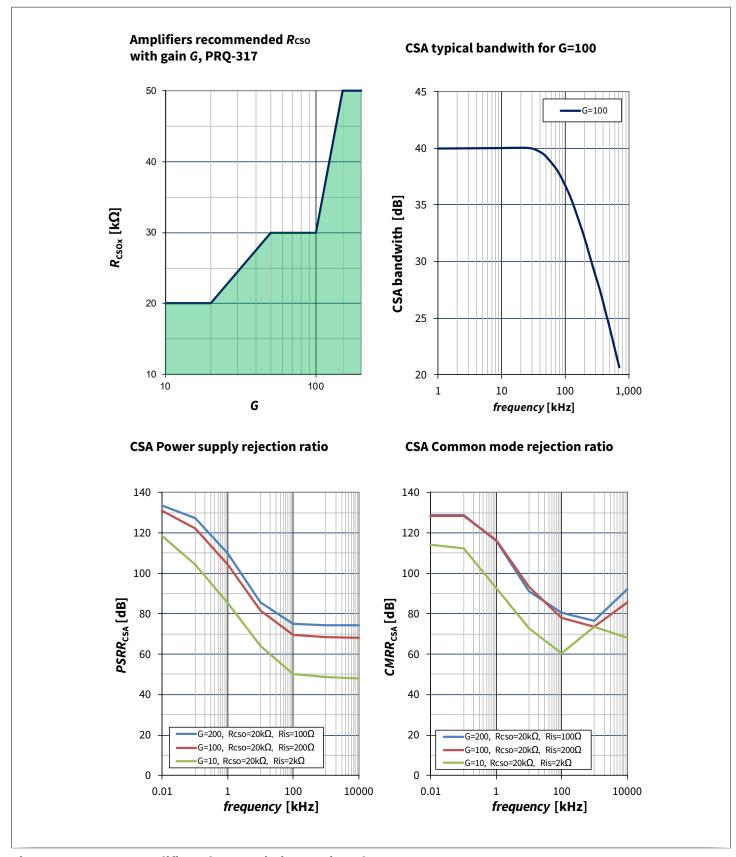

| Current sense amplifiers gain range                         | G                                      | 10   | -      | 200                             | _    | For $G \le 30$ , use only $R_{CSO} = 10 \text{ k}\Omega$ | PRQ-317 |

| Supply voltage range for amplifier operation                | V <sub>BC</sub> -V <sub>S</sub>        | 6    | _      | 15                              | V    | 1)                                                       | PRQ-339 |

| Amplifier input voltage range                               | V <sub>BC</sub> -V <sub>ISxx</sub>     | 6    | _      | 15                              | V    | 1)                                                       | PRQ-341 |

| Amplifier input voltage<br>threshold for disconnection      | V <sub>ISxx-GND(TH)</sub>              | 0.2  | 0.7    | 1.5                             | V    | 1)                                                       | PRQ-340 |

Not subject to production test, specified by design

## 3.3 Thermal characteristics

#### Table 4 Thermal characteristic

| Parameter                              | Symbol            |      | Values |      | Unit | Note or condition | P-     |

|----------------------------------------|-------------------|------|--------|------|------|-------------------|--------|

|                                        |                   | Min. | Тур.   | Max. |      |                   | Number |

| Thermal resistance junction to ambient | R <sub>thJA</sub> | -    | 27     | _    | K/W  | 1) 2)             | PRQ-38 |

<sup>1)</sup> Not subject to production test, specified by design

According to JEDEC51-2,-5,-7 at natural convection on FR4 2s2p board; the product (chip + package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 μm Cu, 2 x 35 μm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer. T<sub>A</sub> = 85°C. Device is loaded with 1 W power.

#### **Datasheet**

4 Electrical characteristics

#### **Electrical characteristics** 4

#### **Static electrical characteristics** 4.1

$T_J$  = -40 to 150°C,  $V_S$  = 8 V to 36 V (unless otherwise specified), all voltages with respect to ground, positive current flowing into pin (unless otherwise specified), typical values are given for  $V_S$  = 14 V and  $T_J$  = 25°C

**Static electrical characteristics** Table 5

| Parameter                                                   | Symbol                         |      | Values |      | Unit | Note or condition                                                                                             | P-      |  |

|-------------------------------------------------------------|--------------------------------|------|--------|------|------|---------------------------------------------------------------------------------------------------------------|---------|--|

|                                                             |                                | Min. | Тур.   | Max. |      |                                                                                                               | Number  |  |

| Inputs pins                                                 |                                |      |        |      |      |                                                                                                               |         |  |

| Input A,B & Enable voltage high level                       | $V_{\rm IN(H)}, V_{\rm EN(H)}$ | 2.5  | _      | _    | V    | _                                                                                                             | PRQ-74  |  |

| Input A,B & Enable voltage<br>low level                     | $V_{\rm IN(L)}, V_{\rm EN(L)}$ | _    | _      | 0.7  | V    | _                                                                                                             | PRQ-75  |  |

| Input A,B & Enable pull-down internal resistor              | $R_{\rm IN(GND)}$              | 0.5  | 1.5    | 2.5  | МΩ   | -                                                                                                             | PRQ-318 |  |

| Input zener diode for local pins                            | $V_{Z(IN)}$                    | 5.5  | 6      | 6.5  | V    | 1) See Figure 3                                                                                               | PRQ-319 |  |

| Digital diagnostic pins                                     |                                | I    |        |      |      | -                                                                                                             |         |  |

| Ratio diagnostic pin voltage high level over VEN            | k <sub>DG(H)</sub>             | 0.9  | 1      | 1.1  | -    | -                                                                                                             | PRQ-84  |  |

| Diagnostic pin voltage low level                            | $V_{DG(L)}$                    | -    | _      | 0.1  | V    | V <sub>BC</sub> = 72 V                                                                                        | PRQ-85  |  |

| Diagnostic pin serial resistor                              | R <sub>DG(GND)</sub>           | 5    | 10     | 20   | kΩ   | -                                                                                                             | PRQ-86  |  |

| Threshold for diagnostic change in IDLE mode                | V <sub>DS_DIAG(TH)</sub>       | 1    | 2      | 3    | V    | V <sub>S</sub> -V <sub>SA</sub> (DG0)<br>V <sub>S</sub> -V <sub>SB</sub> (DG1)                                | PRQ-91  |  |

| Diagnostic delay in IDLE mode                               | $t_{DG(IDLE)}$                 | 0    | 40     | 100  | μs   | IDLE mode only                                                                                                | PRQ-275 |  |

| Delay for current direction change on DG1                   | t <sub>ISD</sub>               | 0    | 8      | 18   | μs   | Indicates current flow<br>direction change on<br>CSA1 only<br>ON mode only                                    | PRQ-164 |  |

| Interrupt pin pull-down internal resistor, SAFESTATE active | R <sub>INT</sub>               | 7    | 12     | 17   | kΩ   | _                                                                                                             | PRQ-88  |  |

| Interrupt pin current leakage                               | / <sub>INT(NOSAFESTATE)</sub>  | _    | _      | 0.3  | μΑ   | V <sub>INT(H)</sub> ≤ 5.5 V                                                                                   | PRQ-89  |  |

| Comparator (CP)                                             | •                              | •    |        |      |      |                                                                                                               | •       |  |

| Comparator offset                                           | V <sub>CP(OFFSET)</sub>        | -50  | _      | 50   | mV   | $V_{\text{CP}(\text{REF})\text{MIN}} \leq V_{\text{CP}(\text{REF})} \leq V_{\text{CP}(\text{REF})\text{MAX}}$ | PRQ-284 |  |

| Comparator leakage input current                            | I <sub>CP</sub>                | -100 | _      | 100  | nA   | V <sub>CP</sub> = 5.5 V                                                                                       | PRQ-242 |  |

## (table continues...)

#### **Datasheet**

4 Electrical characteristics

## Table 5 (continued) Static electrical characteristics

| Parameter                               | Symbol                   |      | Values |      | Unit              | Note or condition                                                                | P-      |

|-----------------------------------------|--------------------------|------|--------|------|-------------------|----------------------------------------------------------------------------------|---------|

|                                         |                          | Min. | Тур.   | Max. |                   |                                                                                  | Number  |

| Temperature amplifier (TMP              | A)                       |      |        |      | •                 |                                                                                  | '       |

| TMPA input current                      | I <sub>TMP(OFF)</sub>    | -100 | _      | 100  | nA                | _                                                                                | PRQ-185 |

| TMPA input offset                       | V <sub>TMP(OFFSET)</sub> | -10  | 0      | +10  | mV                | _                                                                                | PRQ-186 |

| TMPA ratio                              | k <sub>TMP</sub>         | 9.5  | 10     | 10.5 | _                 | _                                                                                | PRQ-187 |

| TMPA pull-down resistor                 | R <sub>TMPO</sub>        | 20   | _      | 100  | kΩ                | 1)                                                                               | PRQ-188 |

| Current sense amplifiers (CS            | A1 & CSA2)               |      | 1      |      |                   |                                                                                  |         |

| CSA input offset                        | V <sub>ISx(OFFSET)</sub> | -50  | 0      | 50   | μV                | 1)                                                                               | PRQ-323 |

| CSA input blind range                   | V <sub>ISx(BLIND)</sub>  | -500 | 0      | 500  | μV                | -                                                                                | PRQ-324 |

| CSA delay maximum accuracy              | t <sub>CSA(ACC)</sub>    | 0    | 200    | 400  | μs                | -                                                                                | PRQ-325 |

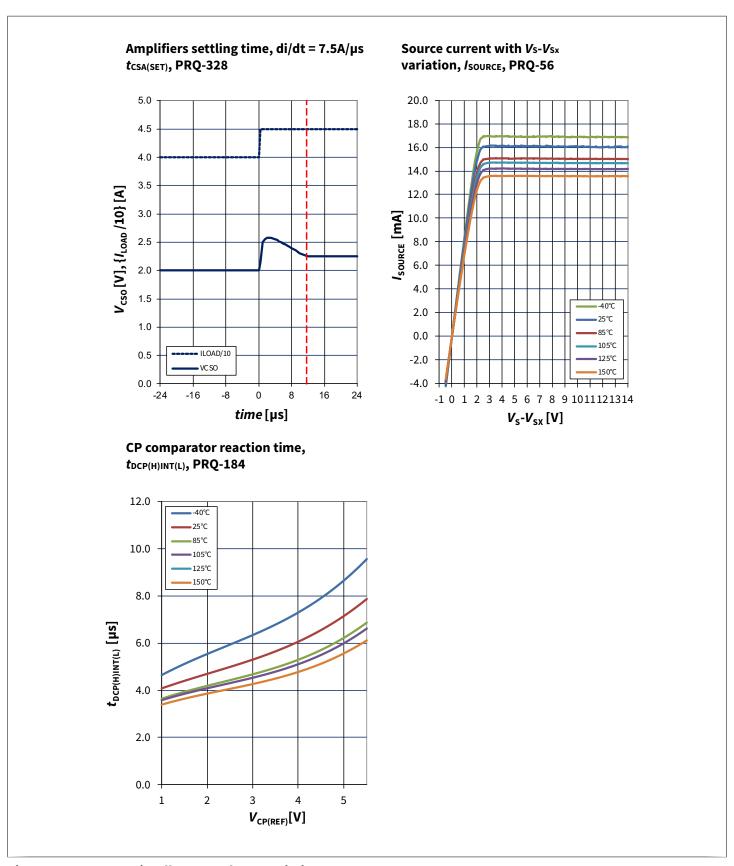

| CSA settling time                       | t <sub>CSA(SET)</sub>    | 1    | 10     | 20   | μs                | Step 25%<br>G=100                                                                | PRQ-328 |

| CSA output pull-down resistor           | R <sub>CSOx</sub>        | 10   | 20     | 50   | kΩ                | 1)                                                                               | PRQ-326 |

| CSA gain intrinsic error                | <i>ε</i> (G)             | -1   | 0      | 1    | %                 | 1)<br>G = 10200                                                                  | PRQ-327 |

| PSRR - CSA power supply rejection ratio | PSRR <sub>1kHz</sub>     | -    | 105    | -    | dB                | $^{2)} f = 1 \text{ kHz}, G = 100,$<br>$R_{CSO} = 20 \text{ k}$<br>see Figure 34 | PRQ-336 |

| CMRR - CSA common mode rejection ratio  | CMRR <sub>1kHz</sub>     | -    | 116    | -    | dB                | $^{2)} f = 1 \text{ kHz}, G = 100, R_{CSO} = 20 \text{ k}$<br>see Figure 34      | PRQ-337 |

| Noise - CSA Voltage noise, RTI          | Noise                    | -    | 180    | _    | nV <sub>RMS</sub> | $^{2)}G = 100, R_{CSO} = 20 \text{ k}$<br>RTI                                    | PRQ-338 |

<sup>1)</sup> Not subject to production test, specified by design

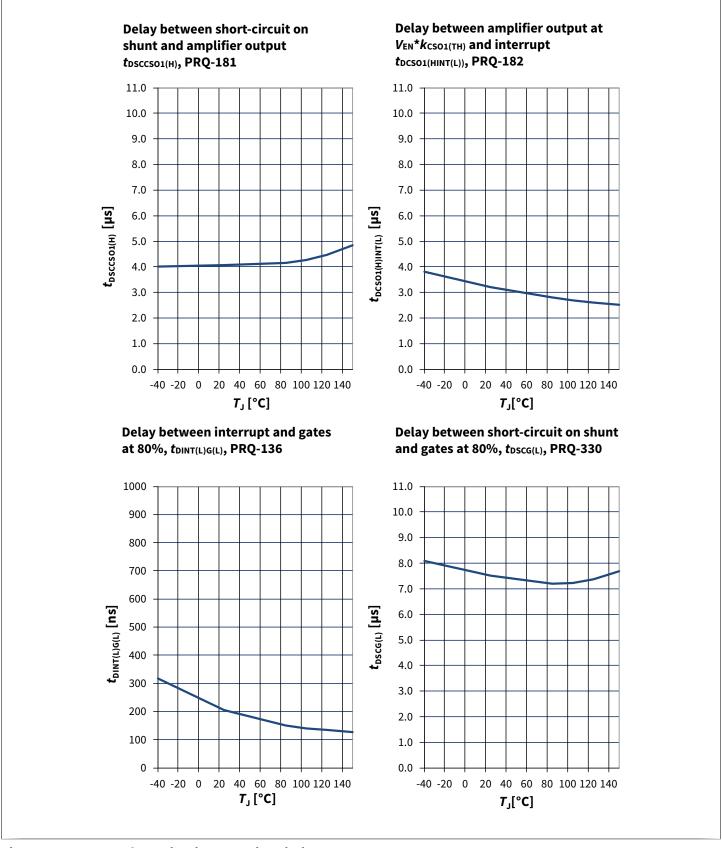

## **4.2** Protection characteristics

$T_J$  = -40 to 150°C,  $V_S$  = 8 V to 36 V (unless otherwise specified), all voltages with respect to ground, positive current flowing into pin (unless otherwise specified), typical values are given for  $V_S$  = 14 V and  $T_J$  = 25°C

<sup>2)</sup> Not subject to production test, specified by characterization.

#### **Datasheet**

4 Electrical characteristics

#### **Protection characteristics** Table 6

| Parameter                                                         | Symbol                       |      | Values |      | Unit | Note or condition                                                                                   | P-<br>Number |

|-------------------------------------------------------------------|------------------------------|------|--------|------|------|-----------------------------------------------------------------------------------------------------|--------------|

|                                                                   |                              | Min. | Тур.   | Max. |      |                                                                                                     |              |

| Protection thresholds                                             |                              | '    |        |      |      |                                                                                                     |              |

| Current shutdown internal threshold ratio from Enable pin voltage | k <sub>CSO1(TH)</sub>        | 0.71 | 0.74   | 0.77 | _    | V <sub>S</sub> = 8 V to 58 V<br>ON mode, CSA1 only<br>See Chapter 8.1                               | PRQ-168      |

| Under voltage threshold                                           | V <sub>S(UV)</sub>           | 0.5  | 1      | 1.5  | V    | V <sub>S</sub> - GND<br>ON mode only                                                                | PRQ-66       |

| Protection delays                                                 |                              | ·    |        |      |      |                                                                                                     |              |

| Delay between short circuit and CSO1 high                         | t <sub>DSCCSO1(H)</sub>      | 0.2  | 1.5    | 6    | μs   | 1) G = 100 V <sub>EN</sub> =3.3V                                                                    | PRQ-181      |

| Delay between CSO1 high<br>and INT = low                          | $t_{	extsf{DCSO1(H)INT(L)}}$ | 0.5  | 5      | 10   | μs   | 1)<br>G = 100                                                                                       | PRQ-182      |

| Delay between CP high and INT                                     | t <sub>DCP(H)INT(L)</sub>    | 1    | 9      | 17   | μs   | $V_{\text{CP}(\text{REF})\text{MIN}} \leq V_{\text{CP}(\text{REF})} \leq V_{\text{CP}(\text{REF})}$ | PRQ-184      |

| Delay between UV on VS and INT = low                              | $t_{DUV(H)INT(L)}$           | 8    | 22     | 40   | μs   | _                                                                                                   | PRQ-320      |

| Delay between INT = low and gate 80%                              | $t_{DINT(L)G(L)}$            | -    | 3      | 5    | μs   | $C_{G(EQ)} = 100 \text{ nF}$                                                                        | PRQ-136      |

| Delay between short circuit and gate 80%                          | $t_{\mathrm{DSCG(L)}}$       | 0.7  | 5.5    | 10   | μs   | $G = 100$ $V_{EN} = 3.3 \text{ V}$ $C_{G(EQ)} = 100 \text{ nF}$                                     | PRQ-330      |

| Time to reset                                                     | t <sub>RESET</sub>           | 3    | -      | 30   | μs   | Reset from SAFESTATE: $V_{EN} < V_{EN(L)}$ for $t_{RESET}$ duration                                 | PRQ-94       |

Sum of PRQ-181, PRQ-182, PRQ-136 max. does match max. of the sum PRQ-330 due to silicon process and variation. 1)

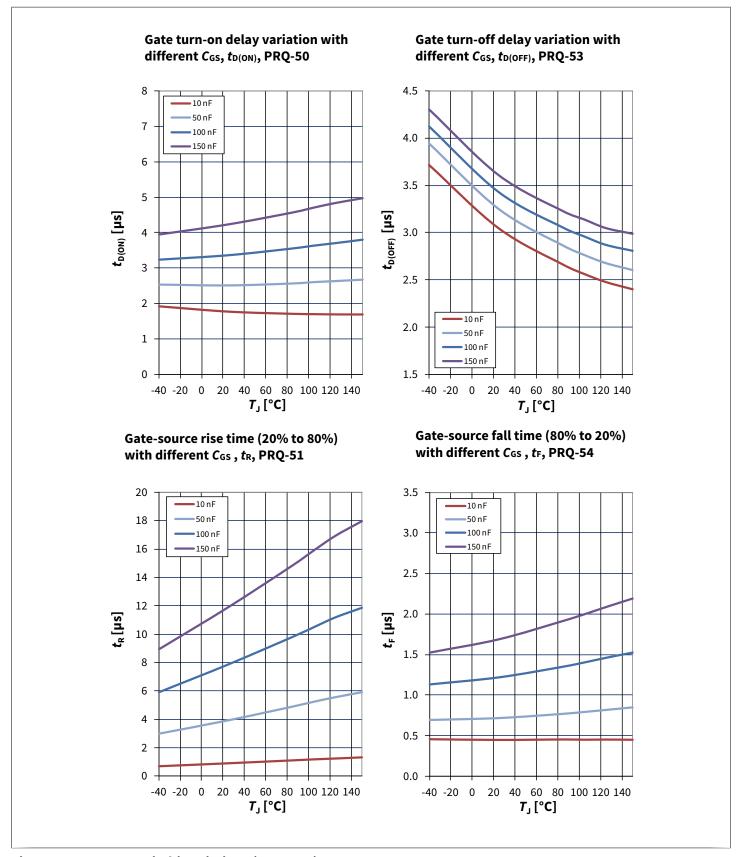

#### **Driver outputs electrical characteristics** 4.3

$T_J$  = -40 to 150°C,  $V_S$  = 8 V to 36 V (unless otherwise specified), all voltages with respect to ground, current positive while flowing out of pin (unless otherwise specified), typical values are given for  $V_S = 14 \text{ V}$  and  $T_J = 25 ^{\circ}\text{C}$

Table 7 **Driver outputs electrical characteristics**

| Parameter                 | Symbol              | Values |      | Values |    | Unit                                  | Note or condition | P- |

|---------------------------|---------------------|--------|------|--------|----|---------------------------------------|-------------------|----|

|                           |                     | Min.   | Тур. | Max.   |    |                                       | Number            |    |

| Source pre-charge current | I <sub>SOURCE</sub> | 6      | 15   | 25     | mA | $V_{S} - V_{Sx} \ge V_{DS\_DIAG(TH)}$ | PRQ-56            |    |

(table continues...)

## **Datasheet**

4 Electrical characteristics

#### Table 7 (continued) Driver outputs electrical characteristics

| Parameter                                                              | Symbol              |      | Values | ;    | Unit | Note or condition                                            | P-      |  |

|------------------------------------------------------------------------|---------------------|------|--------|------|------|--------------------------------------------------------------|---------|--|

|                                                                        |                     | Min. | Тур.   | Max. |      |                                                              | Number  |  |

| Delay between Enable =<br>high and Source pre-charge<br>current active | $t_{DSOURCE}$       | 4    | -      | 100  | μs   | IDLE mode only                                               | PRQ-210 |  |

| Power on input delay                                                   | t <sub>POI</sub>    | 0    | 2      | 5    | μs   | Time to activate protections before turn-on after INx = high | PRQ-158 |  |

| Turn-on delay                                                          | $t_{D(ON)}$         | 1    | 4      | 7    | μs   | $C_{G(EQ)} = 100 \text{ nF}$                                 | PRQ-50  |  |

| Rise time on gate 20% to 80% of VBC - VS                               | $t_{R}$             | 0    | 7      | 15   | μs   | $C_{G(EQ)} = 100 \text{ nF}$                                 | PRQ-51  |  |

| Gate turn on short circuit pulsed current per gate                     | I <sub>G(ON)</sub>  | 50   | 175    | -    | mA   | $V_{\rm GX}$ - $V_{\rm SX}$ = 0 V                            | PRQ-52  |  |

| Turn-off delay                                                         | t <sub>D(OFF)</sub> | 1    | 4      | 7    | μs   | C <sub>G(EQ)</sub> = 100 nF                                  | PRQ-53  |  |

| Fall time on gate 80% to 20% of VBC - VS                               | t <sub>F</sub>      | 0    | 2      | 5    | μs   | C <sub>G(EQ)</sub> = 100 nF                                  | PRQ-54  |  |

| Gate turn-off short circuit pulsed current per gate                    | I <sub>G(OFF)</sub> | 350  | 1400   | -    | mA   | $V_{\rm GX} - V_{\rm SX} = 14  \rm V$                        | PRQ-276 |  |

#### **Boost converter (BC) characteristics** 4.4

$T_{\rm J}$  = -40 to 150°C,  $V_{\rm S}$  = 8 V to 36 V (unless otherwise specified), all voltages with respect to ground, typical values are given for  $V_{\rm S}$  = 14 V and  $T_{\rm J}$  = 25°C

**Boost converter (BC) characteristics** Table 8

| Parameter                                | Symbol              |                         | Values |      | Unit | Note or condition                                                      | P-      |  |

|------------------------------------------|---------------------|-------------------------|--------|------|------|------------------------------------------------------------------------|---------|--|

|                                          |                     | Min. Typ.               |        | Max. |      |                                                                        | Number  |  |

| BC Boost capacitor                       | C <sub>BC</sub>     | 20 * C <sub>G(EQ)</sub> | -      | -    | F    | 1) $C_{G(EQ)}$ = external  MOSFET equivalent  gate source  capacitance | PRQ-137 |  |

| BC switching current limitative resistor | R <sub>RS</sub>     | 10                      | -      | 30   | Ω    | Use 1/2 W resistor min.                                                | PRQ-138 |  |

| BC output VBC - VS regulation voltage    | V <sub>BC(TH)</sub> | 11.5                    | 12.5   | 14   | V    | -                                                                      | PRQ-139 |  |

| VBC(TH) to UVLO regulation gap           | $V_{\rm BC(RG)}$    | 1.9                     | 2.5    | _    | V    | -                                                                      | PRQ-141 |  |

| BC undervoltage lockout voltage          | UVLO                | 9.5                     | 10     | 11   | V    | -                                                                      | PRQ-140 |  |

(table continues...)

#### **Datasheet**

4 Electrical characteristics

#### (continued) Boost converter (BC) characteristics Table 8

| Parameter                               | Symbol                      |      | Values |      | Unit | Note or condition                                                                                                                          | P-      |  |

|-----------------------------------------|-----------------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

|                                         |                             | Min. | Тур.   | Max. |      |                                                                                                                                            | Number  |  |

| Delay between UVLO and INT = low        | t <sub>DUVLO(H)INT(L)</sub> | 0    | 10     | 40   | μs   | -                                                                                                                                          | PRQ-142 |  |

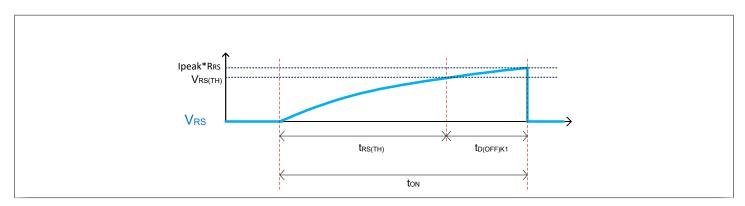

| RS deactivation threshold               | V <sub>RS(TH)</sub>         | 0.7  | 1      | 1.4  | V    | -                                                                                                                                          | PRQ-147 |  |

| Forward voltage of BC diode             | $V_{FBC}$                   | 0    | 0.9    | 1.1  | V    | I <sub>F</sub> = 100 mA                                                                                                                    | PRQ-148 |  |

| On-state resistance of BC switch        | R <sub>DS(ON)K1(25)</sub>   | 1    | 11     | 15   | Ω    | $I = 100 \text{ mA}; T_J = 25^{\circ}\text{C}$                                                                                             | PRQ-150 |  |

| Boost converter off-time                | t <sub>BC(OFF)</sub>        | 1    | 4      | 5    | μs   | -                                                                                                                                          | PRQ-152 |  |

| Time to reach RS deactivation threshold | t <sub>RS(TH)</sub>         | -    | 920    | -    | ns   | $^{2)}V_{S} = 12 \text{ V};$<br>$R_{RS} = 10 \Omega;$<br>$L = 100 \mu\text{H} / 1.7 \Omega;$<br>$T_{J} = 25 ^{\circ}\text{C}$              | PRQ-154 |  |

| Turn-off delay of K1                    | t <sub>D(OFF)K1</sub>       | 0.05 | 0.2    | 0.3  | μs   | -                                                                                                                                          | PRQ-155 |  |

| Boost power-on delay                    | $t_{POD}$                   | _    | 960    | -    | μs   | $^{3)}V_{S} = 12 \text{ V}; R_{RS} = 10 \Omega;$<br>$L = 100  \mu\text{H} / 2 \Omega ; C_{BC} = 1 \mu\text{F}; T_{J} = 25^{\circ}\text{C}$ | PRQ-157 |  |

|                                         |                             |      |        |      |      | See AppNote Getting<br>Started with 2ED2410-<br>EM                                                                                         |         |  |

Not subject to production test, specified by design

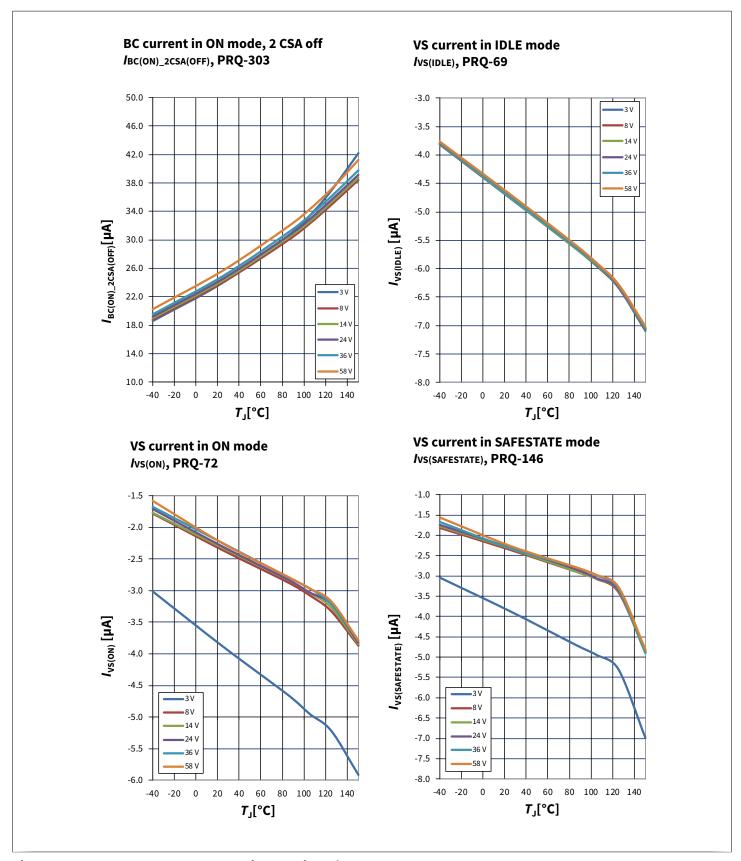

#### **Current consumptions** 4.5

$T_J$  = -40 to 150°C,  $V_S$  = 8 V to 36 V (unless otherwise specified), all voltages with respect to ground, positive current flowing into pin (unless otherwise specified), typical values are given for  $V_S$  = 14 V and  $T_J$  = 25°C

**Current consumptions** Table 9

| Parameter                             | Symbol                      |      | Values |      | Unit | Note or condition                                                                  | P-               |  |

|---------------------------------------|-----------------------------|------|--------|------|------|------------------------------------------------------------------------------------|------------------|--|

|                                       |                             | Min. | Тур.   | Max. |      |                                                                                    | Number<br>PRQ-68 |  |

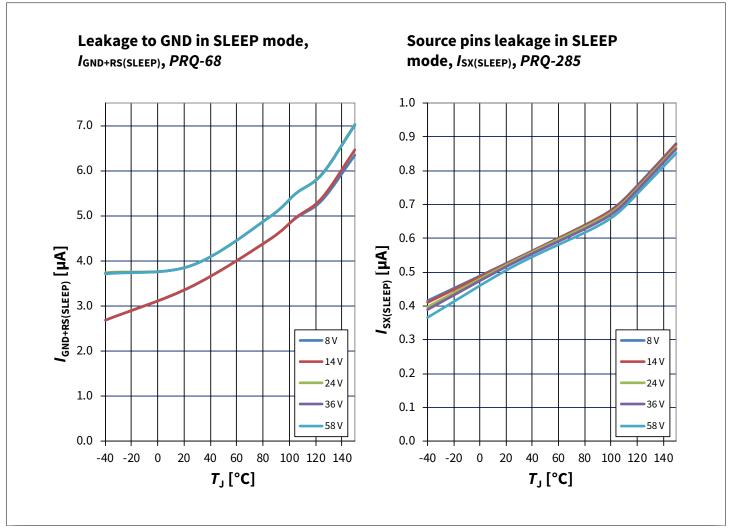

| GND pin current in SLEEP mode         | I <sub>GND+RS</sub> (SLEEP) | 1    | 6      | 15   | μΑ   | $V_S = 24 \text{ V}$<br>$V_{BC} = V_S$                                             |                  |  |

| Sources leakage current in SLEEP mode | I <sub>SX(SLEEP)</sub>      | 0.1  | 0.5    | 4    | μΑ   | $V_{\text{BAT}} = 24 \text{ V}$<br>$V_{\text{S}} - V_{\text{SX}} = V_{\text{BAT}}$ | PRQ-285          |  |

| VS pin current in IDLE mode           | I <sub>VS(IDLE)</sub>       | -15  | -6     | -2   | μА   | $V_S = 24 \text{ V}$<br>$V_{SX} = V_S$                                             | PRQ-69           |  |

| VS pin current in IDLE mode, 25°C     | / <sub>VS(IDLE)25</sub>     | -10  | -6     | -2   | μΑ   | T <sub>J</sub> = 25°C                                                              | PRQ-294          |  |

<sup>1)</sup> 2) 3) Not subject to production test, specified by calculation.

Not subject to production test, specified by characterization.

## **Datasheet**

4 Electrical characteristics

## Table 9 (continued) Current consumptions

| Parameter                                                        | Symbol                               |      | Values |      | <b>Unit</b><br>μΑ | Note or condition                                                         | P-      |  |

|------------------------------------------------------------------|--------------------------------------|------|--------|------|-------------------|---------------------------------------------------------------------------|---------|--|

|                                                                  |                                      | Min. | Тур.   | Max. |                   |                                                                           | Number  |  |

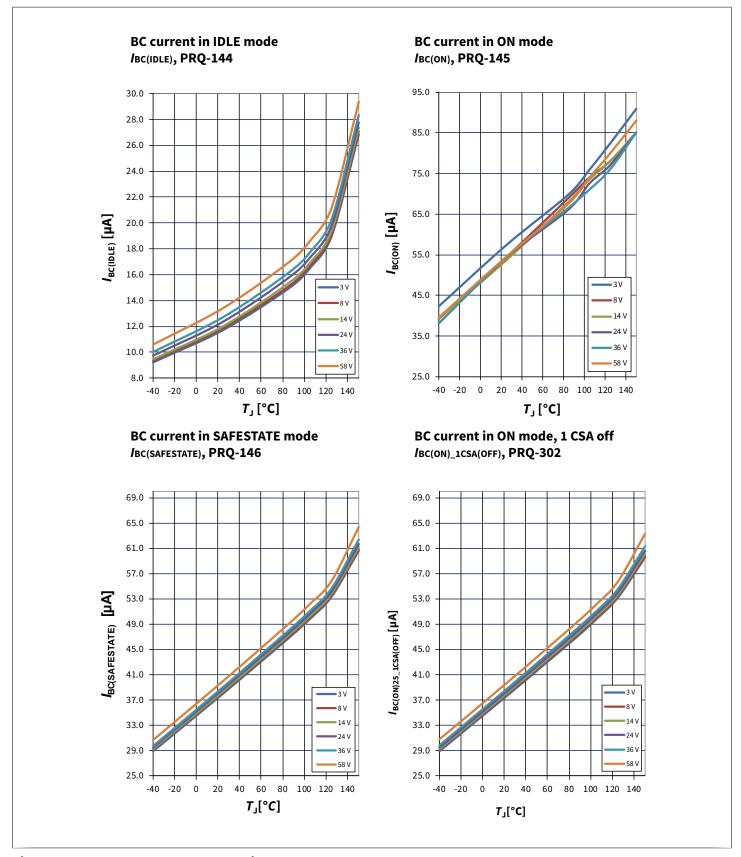

| BC current in IDLE mode                                          | I <sub>BC(IDLE)</sub>                | 5    | 10     | 50   |                   | V <sub>S</sub> = 24 V                                                     | PRQ-144 |  |

|                                                                  |                                      |      |        |      |                   | $V_{BC}$ - $V_S$ = 14 V                                                   |         |  |

| BC current in IDLE mode,<br>25°C                                 | I <sub>BC(IDLE)25</sub>              | 5    | 10     | 20   | μΑ                | T <sub>J</sub> = 25°C                                                     | PRQ-297 |  |

| VS pin current in ON mode                                        | I <sub>VS(ON)</sub>                  | -20  | -4     | 0    | μA                | -                                                                         | PRQ-72  |  |

| VS pin current in ON mode,<br>25°C                               | I <sub>VS(ON)25</sub>                | -10  | -4     | -1   | μА                | T <sub>J</sub> = 25°C                                                     | PRQ-295 |  |

| BC current in ON mode                                            | I <sub>BC(ON)</sub>                  | 10   | 55     | 150  | μΑ                | V <sub>BC</sub> - V <sub>S</sub> = 14 V                                   | PRQ-145 |  |

| BC current in ON mode, 25°C                                      | I <sub>BC(ON)25</sub>                | 10   | 55     | 90   | μΑ                | T <sub>J</sub> = 25°C                                                     | PRQ-298 |  |

| BC current in ON mode, 25°C, one CSA disconnected                | I <sub>BC(ON)25_1CSA(O</sub><br>FF)  | 10   | 45     | 70   | μΑ                | $T_J = 25^{\circ}\text{C}$<br>CSA 1 <b>or</b> 2 not used<br>see Chapter 7 | PRQ-300 |  |

| BC current in ON mode, 25°C,<br>all amplifiers disconnected      | I <sub>BC(ON)25_2CSA(O</sub><br>FF)  | 6    | 20     | 35   | μА                | T <sub>J</sub> = 25°C<br>CSA 1 and 2 not used<br>see Chapter 7            | PRQ-301 |  |

| BC current in ON mode, ≤<br>85°C, one CSA disconnected           | I <sub>BC(ON)</sub><br>≤85_1CSA(OFF) | 10   | 45     | 85   | μА                | 1)  T <sub>J</sub> ≤ 85°C  CSA 1 <b>or</b> 2 not used  see Chapter 7      | PRQ-302 |  |

| BC current in ON mode,<br>≤ 85°C, all amplifiers<br>disconnected | I <sub>BC(ON)</sub><br>≤85_2CSA(OFF) | 6    | 20     | 45   | μА                | 1)  T <sub>J</sub> ≤ 85°C  CSA 1 and 2 not used see Chapter 7             | PRQ-303 |  |

| VS pin current in SAFESTATE<br>mode                              | I <sub>VS(SAFESTATE)</sub>           | -20  | -4     | 0    | μΑ                | -                                                                         | PRQ-73  |  |

| BC current in SAFESTATE<br>mode                                  | I <sub>BC(SAFESTATE)</sub>           | 10   | 55     | 150  | μΑ                | $V_{BC} - V_{S} = 14 \text{ V}$                                           | PRQ-146 |  |

<sup>1)</sup> Not subject to production test, specified by design

5 General operation

## **5** General operation

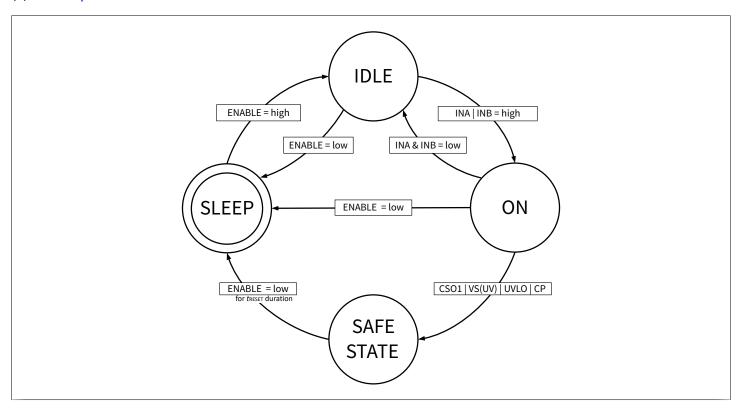

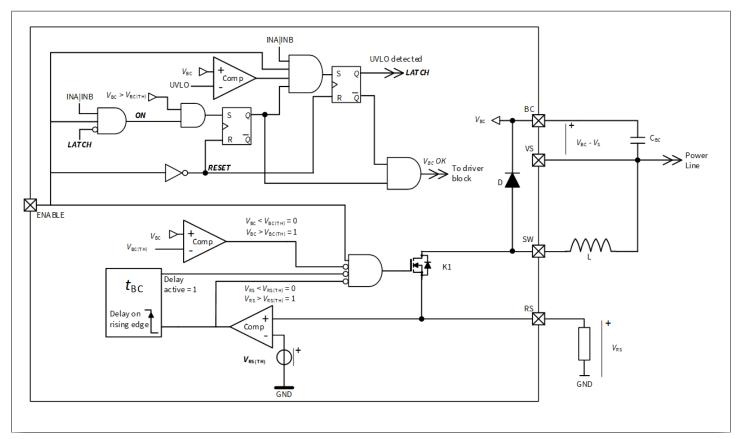

## 5.1 Operating modes

2ED2410-EM works with 4 operating modes: SLEEP, IDLE, ON and SAFESTATE, selected by a combination of inputs INA, INB and ENABLE pins, and in the case of SAFESTATE, by protection features or force signal.

|    | NPU | ITS | OUTPUTS        |          |                                                         |         |            |              |                   |                   |                     |                      |                                                                           |                      |                                                                                                                                                       |

|----|-----|-----|----------------|----------|---------------------------------------------------------|---------|------------|--------------|-------------------|-------------------|---------------------|----------------------|---------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN | INA | INE | Operating mode |          | Boost converter output V <sub>BC</sub> - V <sub>S</sub> | INT     | DG0        | DG1          | V <sub>cso1</sub> | V <sub>CSO2</sub> | V <sub>TMPO</sub>   | $V_{GA}$ - $V_{SA}$  | V <sub>GB</sub> -V <sub>SB</sub>                                          | ISOURCE              | comments                                                                                                                                              |

| 0  | Χ   | Х   | SLEE           | EP       | 0                                                       | 1*      | 0          | 0            | 0                 | 0                 | 0                   | 0                    | 0                                                                         | 0                    | *once reset is done, provided that pull-up voltage is available                                                                                       |

| 1  | 0   | 0   | IDL            | E        | V <sub>BC(ТН)</sub>                                     | 1       | Vs-VsA*    | Vs-VsB*      | 0                 | 0                 | 0                   | 0                    | 0                                                                         | active <sup>1)</sup> | *DG <sub>X</sub> = 0 if $V_S$ - $V_{SX}$ > $V_{DS\_DIAG(TH)}$ for each output, else DG <sub>X</sub> = 1 if $V_S$ - $V_{SX}$ $\leq$ $V_{DS\_DIAG(TH)}$ |

|    | 1   | 0   |                |          |                                                         |         | pulse when | direction of |                   |                   |                     | V <sub>BC(TH)</sub>  | 0                                                                         |                      |                                                                                                                                                       |

| 1  | 0   | 1   | ON             | 1 1'     |                                                         | current | active     | active       | ive active        | 0                 | V <sub>BC(TH)</sub> | active <sup>1)</sup> | *high level: see $V_{\rm DG0}$ , $V_{\rm DG1}$ in Functional ranges Table |                      |                                                                                                                                                       |

|    | 1   | 1   |                |          |                                                         |         | activated* | CSA1*        |                   |                   |                     | V <sub>BC(TH)</sub>  | V <sub>BC(TH)</sub>                                                       |                      |                                                                                                                                                       |

|    |     |     |                | SC or UV | V <sub>ВС(ТН)</sub>                                     |         | 0          | 1            |                   |                   |                     |                      |                                                                           |                      | NB: if several faults occurs in series, only first fault is                                                                                           |

| 1  | Х   | Х   | SAFESTATE      | UVLO     | ≤ <i>V</i> BC(TH)*                                      | 0       | 1          | 0            | active            | active            | ive active          | 0                    | 0                                                                         | active <sup>1)</sup> | indicated by DG1 and DG0                                                                                                                              |

|    |     |     |                | СР       | V <sub>BC(TH)</sub>                                     |         | 1          | 1            |                   |                   |                     |                      |                                                                           |                      | *depends on UVLO root cause                                                                                                                           |

Figure 6 Inputs, modes and outputs states

(1) See Chapter 6.

Figure 7 State machine of 2ED2410-EM

## 5.2 Current consumption

The current consumption of the driver from the system battery(or power supply), also named quiescent current ( $I_q$ ) of 2ED2410-EM, depends on:

#### **Datasheet**

5 General operation

- the mode the driver is in.

- the external components used for the boost converter, which is both the driver supply and the external MOSFET gate supply.

- for SLEEP mode, it also depends on the MOSFET structure used.

In this datasheet are only given consumption at driver level, not at system battery/power supply level.

Details of quiescent current calculation from the battery are given in the application note "Getting started with 2ED2410-EM".

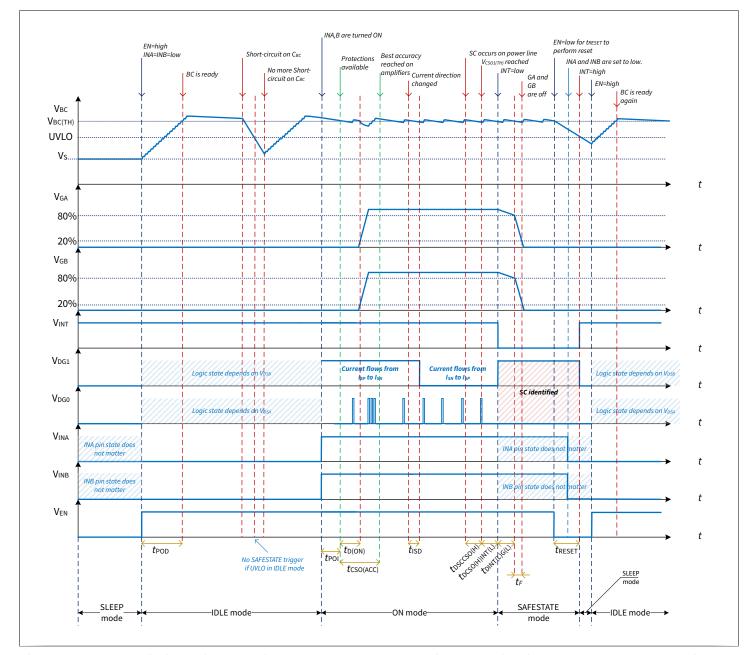

## 5.3 Timing diagram

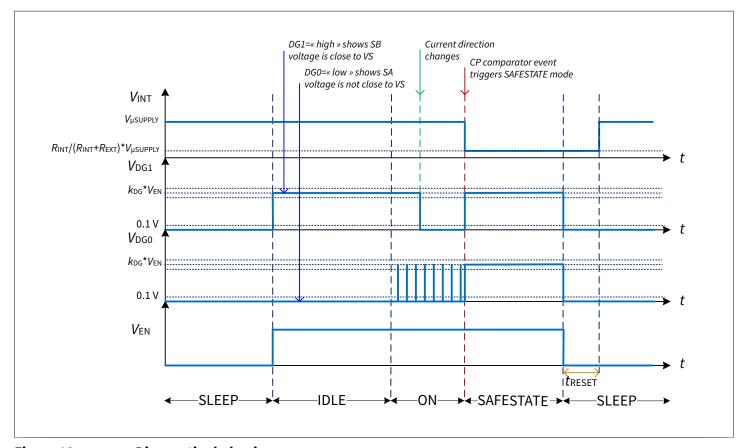

The following diagram shows digital inputs, digital outputs, the boost converter output and gate outputs from SLEEP to ON until short-circuit event occurs, and the reset procedure back to SLEEP mode.

Figure 8 Timings diagram with IDLE mode, ON mode with short-circuit event and SAFESTATE with reset – Note: time and voltages are not to scale

#### **Datasheet**

5 General operation

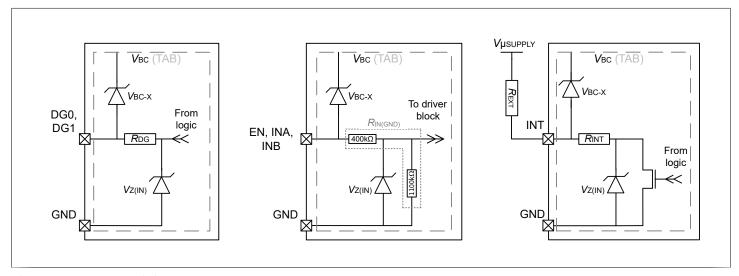

## 5.4 Logic pins

Logic pins are compatible to 5 V and 3.3 V microcontrollers. They can be connected directly to a microcontroller output without the need of an additional component. There is an internal series and pull-down resistor [PRQ-318]. A RC network for stabilizing voltage on EN pin can be used, since EN voltage is used for internal reference in the logic.

Figure 9 Digital I/O

The inputs control circuitry drives the output gate driver stage. They are pulled-down to GND with a  $R_{\text{IN}(\text{GND})}$  resistor to avoid unintended switch-on.

The inputs circuitry are set to logic high when  $V_{INX} > V_{IN(H)}$  or  $V_{EN} > V_{IN(H)}$ .

The ENABLE pin controls the ON/OFF of the boost converter and biases all analog logic.

ENABLE = 1 sets  $V_{BC}$ - $V_{S} \ge V_{BC(TH)}$  after a time  $t_{POD}$ .

The INx pins directly control the gate outputs therefore INA = 1 sets GA = 1 and INB = 1 sets GB = 1. The inputs/outputs A and B are independent

If ENABLE and at least one of the INx pins are set high together, protections and measurements are turned ON but gates will turn-on only when  $V_{BC}$ - $V_S \ge V_{BC(TH)}$ .

When driver enters ON mode by INx = 1, protections are ready after a time  $t_{POI}$  and amplifiers get maximum accuracy after a time  $t_{CSA(ACC)}$  (see Chapter 4.1).

The INx and ENABLE pins are set to logic low when  $V_{INX} < V_{IN(L)}$  or  $V_{EN} < V_{IN(L)}$ .

The digital outputs give back either a low or high logic level signal. The output high voltage level is based on  $V_{\rm EN}$  and is given in the electrical characteristics table as a ratio between  $V_{\rm DGx}$  and  $V_{\rm EN}$ . See parameter  $k_{\rm DG}$  in Chapter 4.1.

DG0 and DG1 in a low logic state have a value  $\leq V_{DG(L)}$ . The state of the diagnostic depends the operating mode the driver is in, refer to Chapter 5.1.

In ON mode, DG0 reflects the activation of boost converter switch K1 (see Chapter 9): each time K1 is activated, DG0 = 1.

In ON mode, DG1 reflects the current direction on CSA1: DG1 = 0 if current is flowing from ISP1 to ISN1, DG1 = 1 if current is flowing from ISN1 to ISP1 (see Chapter 7).

INT pin is an open-drain output. The intent is to deliver an interrupt signal to relevant surrounding devices, such as microcontroller or power supply management chip (e.g. Infineon SBC).

INT needs to be externally pulled-up, e.g. to the microcontroller supply  $V\mu_{\text{SUPPLY}}$ . The value of  $V_{\text{INT}}$  when SAFESTATE is triggered, is the result of the voltage divider between the external resistor  $R_{\text{EXT}}$  and  $R_{\text{INT}}$ .

#### **Datasheet**

5 General operation

Figure 10 Diagnostics behavior

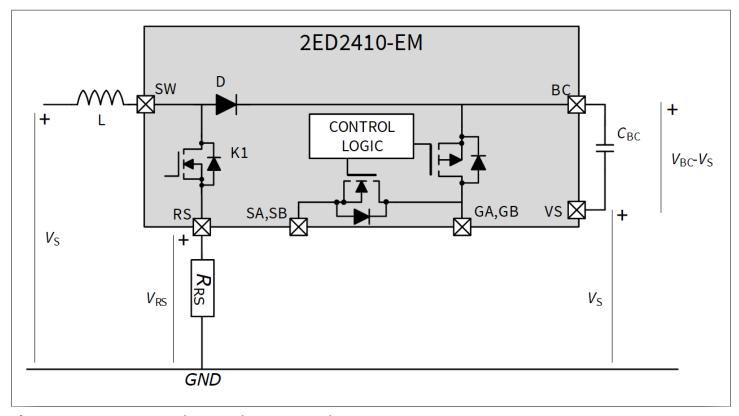

## 5.5 Gate outputs

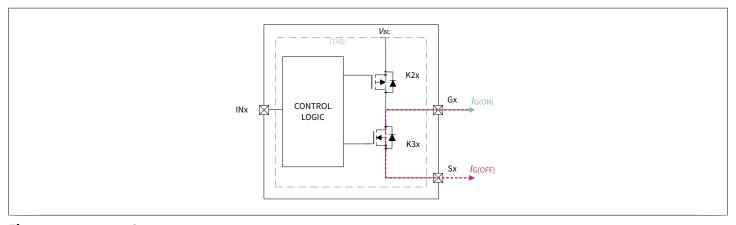

2ED2410-EM features two identical gate outputs GA and GB working with source pins SA and SB respectively.

These outputs are activated by setting the corresponding digital input INA or INB to a high logic level.

The structure of these outputs is a push-pull and the logic ensures by design that both MOSFET K2x and K3x will not be ON at the same time (no shoot-through).

K2x are P-channel enhancement MOSFET and K3x are N-channel enhancement MOSFET.

The current to switch ON the external MOSFET connected to the gate driver is delivered by boost converter capacitor  $C_{\rm BC}$ , through K2x to the gate pins Gx.

The current to switch OFF the external MOSFET is sunk from gate pins Gx through K3x to the source pins Sx.

5 General operation

Figure 11 Gate output structure

When the first input is switched on, a time delay  $t_{\rm POI}$  needs to be considered. This time delay, power-on-input, is needed to make sure protections are activated before sending gate signal activation, so 2ED2410-EM never switches the MOSFET on without current sense and temperature amplifiers. If these functions are not used,  $t_{\rm POI}$  still needs to be considered.

If  $V_{BC}$ - $V_{S} \le V_{BC(TH)}$  when the input signals INx are set high, the driver will be in ON mode but the gate outputs will remain OFF until  $V_{BC(TH)}$  is reached on boost converter output.

If  $V_{BC}$ - $V_{S} \le V_{BC(TH)}$  occurs when the gates are ON, this under-voltage on the boost converter will trigger the lock-out of the gates and the driver will enter SAFESTATE, consequently turning and keeping off the gates. See Chapter 8.4 and refer to Chapter 9 to see how gate outputs and the boost converter are connected.

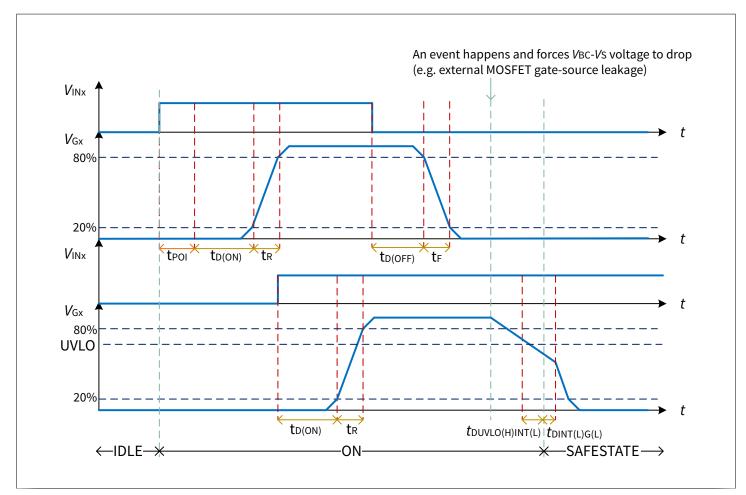

The timings for the gate outputs are described in Figure 12.

Figure 12 Gate timings (not to scale, for understanding purposes only)

#### **Datasheet**

5 General operation

## 5.6 Ground loss protection: module level

MOSFET K3 (see Figure 11, chapter 5.5) is turned on by default on each output as long as VS present. If GND board/ECU connection is lost, K3 remains on or is turned on as long as the below conditions are true. As a result gate-source is pulled-down in the following conditions:

- VS pin is connected to battery line

- GND board/ECU disconnected

- SLEEP, IDLE, ON or SAFESTATE modes

In ON mode, if GND board/ECU is connected back, driver outputs will be turned on again (and therefore K3 switch off) without necessary reset from pin ENABLE.

6 Low by-pass current feature

## 6 Low by-pass current feature

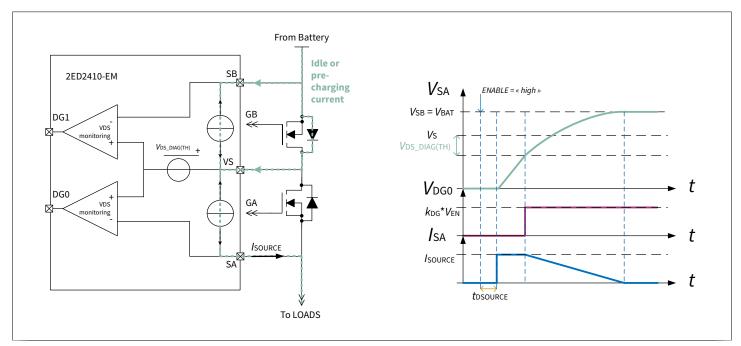

When in IDLE mode, 2ED2410-EM can sink a low current from VS pin to its source pins SA and/or SB and from SA to SB or SB to SA.

The activation is autonomous.

Up to  $V_{\rm SX} = V_{\rm S} - V_{\rm DS\_DIAG(TH)}$ ,  $I_{\rm SOURCE}$  is delivered with typical value [see PRQ-56]. When  $V_{\rm S} - V_{\rm DS\_DIAG(TH)}$  threshold [see PRQ-91] is reached on the corresponding source the  $I_{\rm SOURCE}$  decreases gradually and is turned-off when  $V_{\rm SA} = V_{\rm SB} = V_{\rm S}$ . As a consequence, 2ED2410-EM is able to supply a current  $I_{\rm SOURCE}$  to supply ECU idle mode currents, while keeping its self-consumption very low.

It can also be used to pre-charge ECU input capacitors in the downstream power-net, and keep them charged in car park mode with minimal current consumption.

If a short-circuit occurs at ECU side during the driver's IDLE mode,  $I_{SOURCE}$  is still supplied, however  $V_{DSX}$  is constantly monitored and the corresponding DGx is set to low. This allows, for example, detection of a short-circuit before turn-on. See Chapter 7.1 for diagnostics behaviour in IDLE mode.

Figure 13 Low by-pass current principle of operation and timing diagram (not to scale)

7 Measurement features

#### 7 **Measurement features**

#### 7.1 **VDS monitoring in IDLE mode**

The VDS monitoring function can be read on DGx pins in IDLE mode.

DG0 and DG1 respectively monitor  $V_{DSA}$  ( $V_S - VSA$ ) and  $V_{DSB}$  ( $V_S - V_{SB}$ ), provided that MOSFET drains are connected to VS pin.

If  $V_{DSA}$  (or  $V_{DSB}$ ) >  $V_S$  -  $V_{DS-DIAG(TH)}$  => DG0 (or DG1) = high level ( $I_{source\ B}$  active, see Chapter 6). If  $V_{DSA}$  (or  $V_{DSB}$ ) <  $V_S$  -  $V_{DS}$  DIAG(TH) => DG0 (or DG1) = low level ( $I_{source B}$  active, see Chapter 6).

MOSFET sources are compared to an internal reference voltage  $V_S - V_{DS-DIAG(TH)}$  (see parameter  $V_{DS-DIAG(TH)}$ ).

VDS monitoring diagram with example Figure 14

VDS monitoring allows to detect various situations depending on the switch positions in the boardnet. It depends on the application.

A non-exhaustive list of possible switch position in the boardnet and situation are described below:

#### Case 1: battery - resistive / inductive load configuration

The driver is used to drive the load.

DG1 = high show an open connector / or load is high impedance (HZ)  $> V_{BAT} / I_{SOURCE}$ .

#### **Datasheet**

#### 7 Measurement features

DG1 = low shows that the load is still present. To avoid leakage Isource in IDLE mode, SLEEP mode can be used in car park mode.

#### Case 2: battery - Electronic Control Units (ECU)/capacitive load configuration

The driver is used to separate a power-net which is without power supply from the main power-net with power supply. DG1 = high shows that all ECUs input capacitors are charged and that there is no leakage.

DG1 = low shows that ECUs input capacitors are charging with  $I_{SOURCE}$  or that there is a leakage.

## Case 3: battery - battery configuration

The driver is used to connect two power-nets where both power-nets have their power supply.

DG1 = high shows that  $V_{BAT(A)} - V_{BAT(B)} < V_{DS\_DIAG(TH)}$ .

DG1 = low shows that  $V_{BAT(A)} - V_{BAT(B)} > V_{DS\_DIAG(TH)}$ .

A very high current may flow when reconnecting and trigger SAFESTATE. Inductances between batteries must be carefully considered, including ground path.

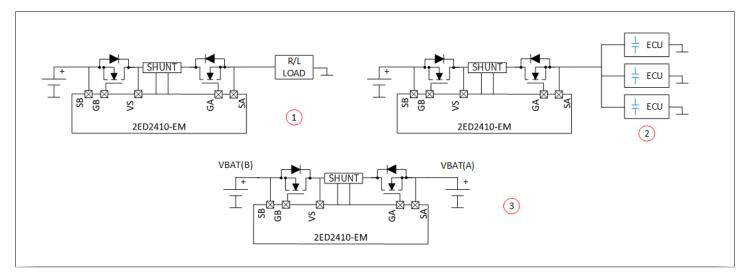

Figure 15 Cases 1, 2, 3

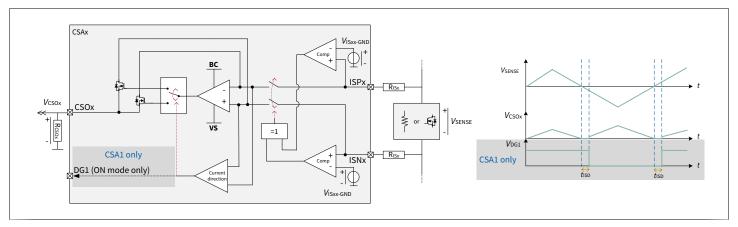

#### 7.2 Current senses in ON and SAFESTATE modes

2ED2410-EM features two integrated current sense amplifiers (active in ON and SAFESTATE modes).

These **current sense amplifiers CSA1 and CSA2** are implemented with two identical differential amplifiers with a wide adjustable gain (*G*) (see PRQ-317).

The inputs are ISP1/2 and ISN1/2 pins and the outputs are CSO1/2 pin.

The current sensors must have a high-side position, or be positioned between the MOSFET drains in a back-to-back common drain configuration.

The current sense amplifier allows to monitor the currents flowing into the shunt (or MOSFET) in **both** directions, which is referred to as bidirectional current sensing.

The gain is set with external resistors  $R_{\rm ISP1/2} = R_{\rm ISN1/2}$  on input (on sensor side) and  $R_{\rm CSO1/2}$  on output (on microcontroller/connector side).  $R_{\rm ISP}$  and  $R_{\rm ISN}$  can be different if a different gain is necessary depending of the current direction. On CSA1, this difference in gain will also impact the short-circuit protection which can be higher or lower depending on the gain magnitude.

Resistor values can be adjusted based on the customer's current sensor solution.

The output is an analog voltage signal,  $V_{\rm CSO1/2}$ , which represents the current flowing in the current sensor. It can be directly read on pin CSO1/2 (Current Sense Output) by a microcontroller.  $V_{\rm CSO1/2}$  output voltage varies from 0 V to  $V_{\rm EN}$ , in both directions, allowing better accuracy than current sensors using an offset as middle point for zero current.

#### **Datasheet**

7 Measurement features

The information of current direction is available only for **CSA1** and can be read in ON mode directly on pin DG1 (0 if current direction is from ISN1 to ISP1, 1 otherwise) by a microcontroller.

**CSA1** features an integrated comparator for fast short-circuit protection. See Chapter 8.1.

Figure 16 Current sense measurement principle and timing diagram [not to scale]

The amplifiers are supplied between BC and VS. If the  $V_{\rm BC}$ - $V_{\rm S}$  voltage is below or above its functional range (see PRQ-339), the amplifiers input switches will open. As a result the current sense function is ensured and random reconnection can connect unwanted SAFESTATE.

The gain of the current sense amplifiers is configurable by three external resistors ( $R_{CSO}$ , 2 x  $R_{IS}$ ).

The relationship between  $V_{\text{SENSE}}$  and  $V_{\text{CSO}}$  through the current sense amplifier is given by:

$$V_{CSO} = |V_{SENSE}| \times \frac{R_{CSO}}{R_{IS}} \tag{1}$$

Where the gain is set by:

$$G_{CSO} = \frac{R_{CSO}}{R_{IS}} \tag{2}$$

Special care has to be taken when setting the gain and the parameters  $G_{\rm CSO}$  and  $R_{\rm CSO}$  must be observed. Resistors are recommended with at least 1% precision and should be placed as close as possible to the 2ED2410-EM pins. See application note "Getting started with 2ED2410-EM" for a complete description on how to use the current sense amplifiers.

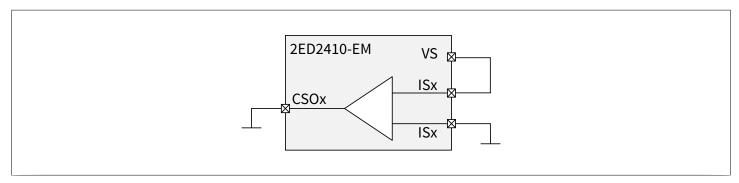

If not used, CSA1 or CSA2, or both, can be simply disconnected with the following configuration. One of the two input pins, either ISP or ISN needs to be connected close to GND (see PRQ-340).

This will reduce the driver self-consumption in ON and SAFESTATE modes.

Warning: short-circuit protection with internal comparator on CSA1 will also be disabled if CSA1 is disabled.

7 Measurement features

Figure 17 CSA1 & 2 disconnection configuration

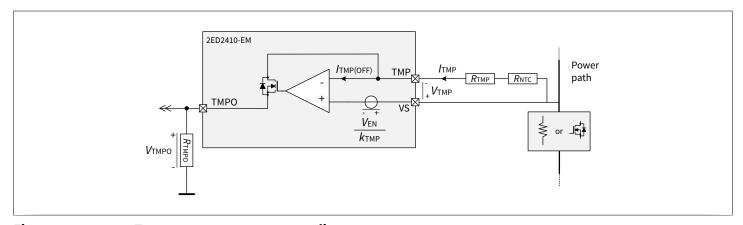

## 7.3 Temperature measurement amplifier in ON and SAFESTATE modes

2ED2410-EM features an integrated temperature monitoring amplifier TMPA (active in ON and SAFESTATE modes).

This **temperature monitoring** function is implemented with a differential amplifier.

The input pin is TMP and the output pin is TMPO.

The temperature amplifier allows to monitor the heat flowing into the  $R_{\rm NTC}$  by monitoring  $V_{\rm TMPO}$ .

The gain is not directly adjustable and the ratio  $k_{\text{TMP}}$  is kept constant by the driver auto-adjusting the gain.

The ratio is kept with the  $R_{\rm NTC}$  in input and  $R_{\rm TMPO}$  in output. Resistor values can be adjusted based on customer's thermistor solution.

In the present document, the temperature sensor is referred to as " $R_{\rm NTC}$ " but other sensors, such as PTC or other thermistors can be implemented.

The output is an analog voltage signal:  $V_{\mathsf{TMPO}}$  represents the temperature in the  $R_{\mathsf{NTC}}$ . It can be directly read on pin TMPO (Temperature Output) by a microcontroller.  $R_{\mathsf{TMP}}$  is not mandatory, but may be needed for linearisation of the output signal  $V_{\mathsf{TMPO}}$ , depending on the thermistor solution choice.

Finally, TMPA can also be disabled if not used. TMP and TMPO pins can be left open.

Figure 18 Temperature measurement diagram

The ratio  $k_{TMP}$  is defined as follows according to the Figure 18.

$$k_{TMP} = \frac{V_{EN}}{V_{TMP}} \tag{3}$$

27

8 Protections features in ON mode

#### 8 Protections features in ON mode

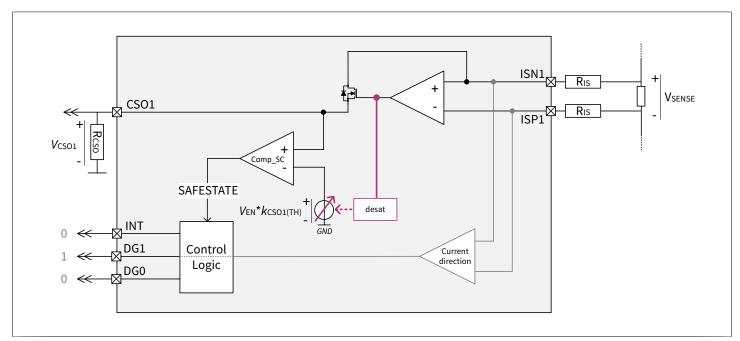

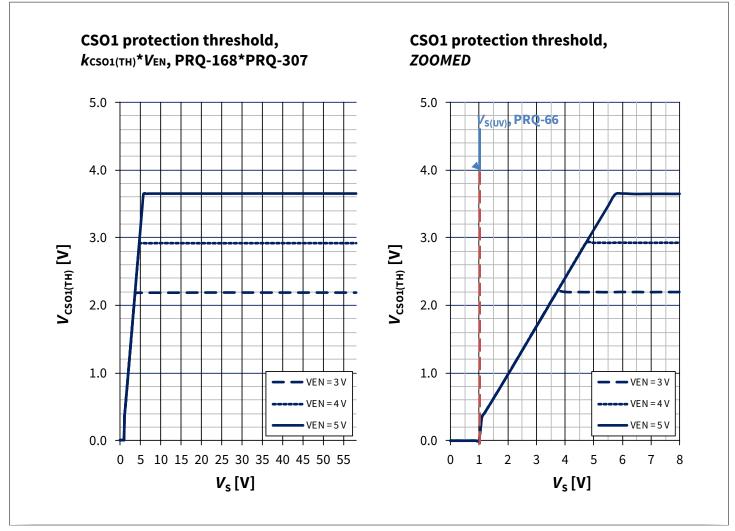

## 8.1 Short-circuit protection

CSA1 has a fast comparator on its output CSO1, which allows 2ED2410-EM to enter SAFESTATE mode when  $V_{\rm CSO1}$  reaches  $V_{\rm CSO(TH)} = k_{\rm CSO} \times V_{\rm EN}$ .

This allows fast turn-off delay time in case of overcurrent/short-circuit when CSA1 is used. 2ED2410-EM is able to switch off the MOSFET without the microcontroller.

The turn-off delay time is  $t_{DSCG(L)}$  and can be computed by the sum  $t_{DSCCSO1(H)} + t_{DCSO1(H)INT(L)} + t_{DINT(L)G(L)}$ . However, the maximum of  $t_{DSCG(L)}$  is not the sum of the maximum of the other delays, because by construction, the silicon process and variation make such a case impossible. This is why only the maximum of  $t_{DSCG(L)}$  (PRQ-330) should be considered when considering the worst case turn-off delay in case of short-circuit detection by CSA1 comparator.

See Chapter 5.1 for details on diagnostics in SAFESTATE mode.

Once in SAFESTATE mode, the driver needs to be reset.

Figure 19 CSA1, internal comparator and diagnostics (one amplifier direction represented for simplicity)

The nominal voltage range for short-circuit protection is  $V_{S(NOR)}$ . As represented in the graph in Figure 20, in the  $V_{S(SC)LOW}$  range (PRQ-40), 2ED2410-EM keeps operating if already in ON or IDLE mode. In the  $V_{S(SC)LOW}$  range the short-circuit detection and shutdown are operational and 2ED2410-EM is protected but the  $V_{CSO(TH)}$  parameter, hence the short-circuit detection depends on  $V_S$  and  $V_{EN}$ . A dedicated function named DESAT covers the protection threshold in the  $V_{S(SC)LOW}$  range.

The variation of  $V_{CSO(TH)}$  is shown in the following graphs.

8 Protections features in ON mode

Figure 20 Typical  $V_{CSO1(TH)}$  versus  $V_S$  and  $V_{EN}$  (independent of  $T_J$ )

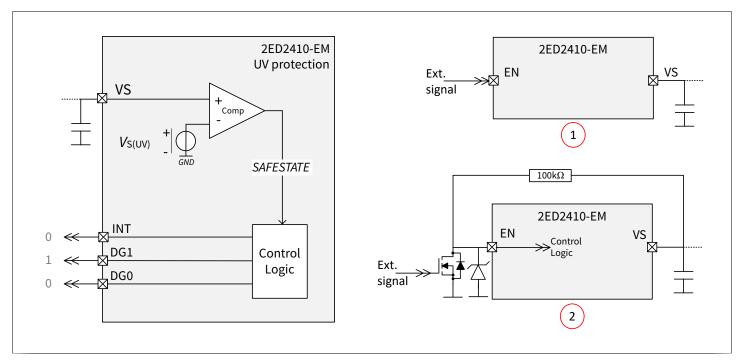

## 8.2 Undervoltage protection on VS

VS pin has an integrated comparator comparing permanently  $V_S$  voltage to  $V_{S(UV)}$  reference (PRQ-66), which allows 2ED2410-EM to enter SAFESTATE mode when  $V_S$  reaches down  $V_{S(UV)}$  level.

The turn-off delay time is computed by the sum  $t_{DUV(H)INT(L)} + t_{DINT(L)G(L)}$  (PRQ-320, PRQ-136).

#### This has two consequences:

- The driver is protected down to 0 V on battery, meaning that a very strong short-circuit that would actually bring the voltage on VS node to 0 V is covered and switch is protected.

- The driver could be sensitive to micro-cuts on the supply if the micro-interruptions are longer than  $t_{\rm DUV(H)INT(L)}$ . To overcome this effect, a capacitor can be used next to VS pin (e.g. a few micro-farad). Additionally, if large micro-cuts are expected in the application, ENABLE pin can be connected to VS pin directly through a  $100 {\rm k}\Omega$  (or more) resistor. An additional Zener diode is necessary on the ENABLE pin to limit the voltage to the desired value, e.g.  $3.3 {\rm V}$  or  $5 {\rm V}$ . When the micro-interruption is over, the driver will automatically turn-on again as soon as  $V_{\rm EN(H)}$  (PRQ-74) threshold is reached again on the ENABLE pin.

See Chapter 5.1 for details on diagnostics in SAFESTATE mode.

Once in SAFESTATE mode, the driver needs to be reset.

#### **Datasheet**

8 Protections features in ON mode

The figure below shows the diagram, (1), the normal driver configuration, and (2), a possible adapted configuration with external circuitry for connection of the ENABLE pin to VS which will reset the driver automatically in case of a large micro-interruption.

Figure 21  $V_{S(UV)}$  protection diagram and possible driver configuration

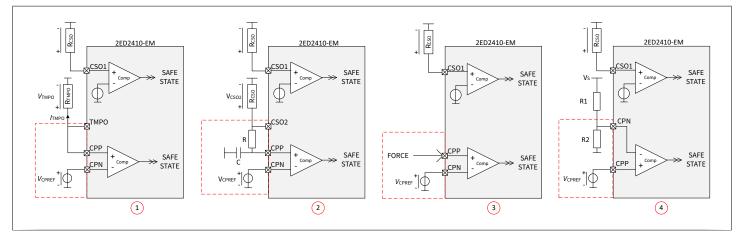

## 8.3 Custom protections with comparator

2ED2410-EM features a voltage comparator with inputs CPP and CPN.

This comparator can be used to trigger SAFESTATE mode based on any analog voltage, even a voltage external to 2ED2410-EM.

CPP is the positive input of the comparator and CPN is the negative input.

$V_{\text{CPREF}}$  can be adjusted by microcontroller, or fixed by an on-board power supply chip, such as an Infineon SBC, or a simple voltage divider, within the limits  $V_{\text{CP(REF)}}$  for stability.

Using this comparator allows 2ED2410-EM to enter SAFESTATE and turn-off MOSFET independently from the microcontroller. The comparator reacts with a delay time  $t_{\text{DCP(H)INT(L)}}$ . Consequently the turn-off delay time in case of shutdown by comparator CP can be computed by the sum  $t_{\text{DCP(H)INT(L)}} + t_{\text{DINT(L)G(L)}}$ .