SR 5015-XXX SR 5015-80 SR 5015-81 SR 5015-133

# **Quad Static Shift Register**

#### **FEATURES**

- ☐ COPLAMOS® N Channel Silicon Gate Technology

- ☐ Variable Length—Single Mask Programmable—1 to 134 bits

- ☐ Directly TTL-compatible on all inputs, outputs, and clock

- ☐ Clear function

- ☐ Operation guaranteed from DC to 1.0 MHz

- ☐ Recirculate logic on-chip

- ☐ Single +5.0V power supply

- Low clock input capacitance16 pin ceramic DIP Package

- ☐ Pin for Pin replacement for AMI S2182, 83, 85

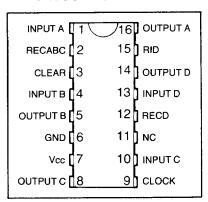

### PIN CONFIGURATION

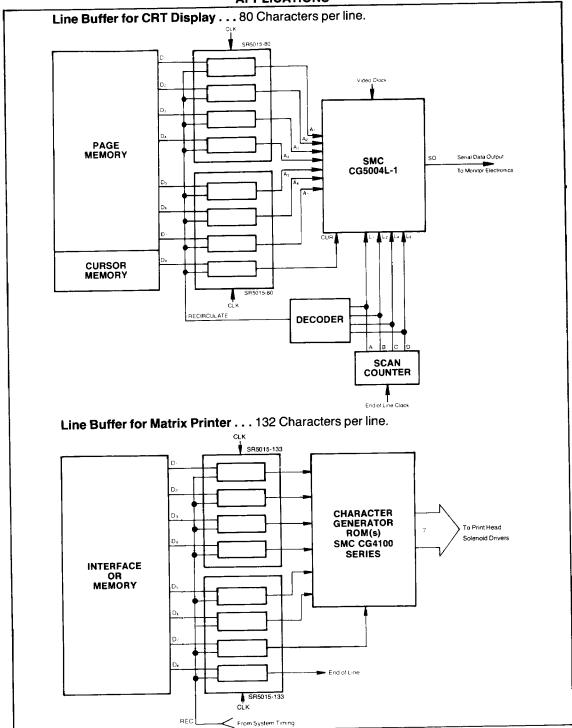

#### **APPLICATIONS**

- ☐ Memory Buffering

- ☐ Unique Buffering Lengths

- □ Terminals

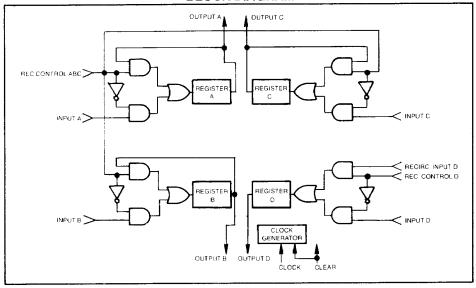

#### **BLOCK DIAGRAM**

## **General Description**

The SMC SR 5015-XXX is a quad static shift register family fabricated using SMC's COPLAMOS® N channel silicon gate process which provides a higher functional density and speed on a monolithic chip than conventional MOS technology. The COPLAMOS® process provides high speed operation, low power dissipation, low clock input capacitance, and single +5 volt power supply operation.

These shift registers can be driven by either T<sup>2</sup>L circuits or by MOS circuits and provide driving capability to MOS or T<sup>2</sup>L circuits. This device consists of four separate static shift registers with independent input and output terminals and logic for loading, recirculating or shifting information. The SR 5015-80, SR 5015-81, and SR 5015-133 are respectively 80, 81, and 133 bit quad shift registers.

The recirculate control pin is common for registers A, B, and C. Register D has an independent recirculate control pin as well as a recirculate input pin.

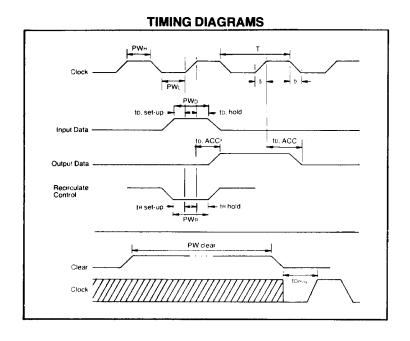

A clear pin has been provided that will cause the shift register to be cleared when the pin is at Vcc. A single T<sup>2</sup>L clock is required for operation.

The transfer of data into the register is accomplished on the low-to-high transition of the clock with the recirculate control low. For long term data storage the clock may be stopped and held in either logic state. Recirculate occurs when the recirculate control is high. Output data appears on the low-to-high transition of the clock pulse.

Bits 81 and 133 are available for flag storage.

This device has been designed to be used in high speed buffer storage systems and small recirculating memories.

Special custom configurations are achieved via single mask programming in lengths of 1 to 134 bits.

## MAXIMUM GUARANTEED RATINGS\*

| AXIMUM GUARANTEED HATINGS"                                                                               | 0°C to + 70°C   |

|----------------------------------------------------------------------------------------------------------|-----------------|

| AXIMUM GUARANTEED RATINGS* Operating Temperature Range                                                   | -55°C to +150°C |

| Operating Temperature Range Storage Temperature Range                                                    | +325°C          |

|                                                                                                          |                 |

|                                                                                                          |                 |

| Positive Voltage on any Pin, with respect to ground  Negative Voltage on any Pin, with respect to ground |                 |

<sup>\*</sup>Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

ELECTRICAL CHARACTERISTICS (Ta=0°C to 70°C, Vcc=+5V±5%, unless otherwise noted)

| Parameter                       | Min.    | Тур. | Max. | Unit    | Comments               |

|---------------------------------|---------|------|------|---------|------------------------|

| ).C. Characteristics            |         |      |      |         |                        |

| NPUT VOLTAGE LEVELS             |         |      | 0.8  | ٧       |                        |

| Low Level, VIL                  |         |      | Vcc  | V       |                        |

| High Level, ViH                 | Vcc-1.5 |      | VCC  | v       |                        |

| OUTPUT VOLTAGE LEVELS           |         |      |      | ٧       | lo <sub>L</sub> =1.6ma |

| Low Level, Vol                  |         |      | 0.4  | V       | loн=1.0ma              |

| High Level, Vон                 | Vcc-1.5 | 4.0  |      | •       | Vin=Vcc                |

| NPUT LEAKAGE CURRENT            |         |      | 1.0  | $\mu a$ | VIN=VCC                |

| CLOCK, CLEAR                    |         |      | 25   | pf      |                        |

| All Other                       |         |      | 10   | pf      |                        |

| POWER SUPPLY CURRENT            |         |      | 80   | ma      |                        |

| A.C. Characteristics            |         |      |      |         | $T_A = +25^{\circ}C$   |

|                                 |         |      |      |         |                        |

| CLOCK<br>PWh                    | 300     |      |      | ns      |                        |

| PWL                             | 600     |      |      | ns      |                        |

| Transition, t <sub>r</sub> , tr | -       | 0.02 | 1.0  | $\mu$ s |                        |

| Repetition Rate, 1/T            | 0       |      | 1.0  | MHz     |                        |

| •                               | 300     |      |      | ns      |                        |

| <sup>t</sup> Delay              |         |      |      |         |                        |

| INPUT DATA                      | 100     |      |      | ns      |                        |

| to, set-up                      | 200     |      |      | ns      |                        |

| t₀, hold<br>PWo                 | 300     |      |      | ns      |                        |

|                                 |         |      |      |         |                        |

| OUTPUT DATA                     |         | 200  | 350  | ns      |                        |

| to, ACC                         |         |      |      |         |                        |

| RECIRCULATE CONTROL             | 200     |      |      | ns      |                        |

| tn, set-up                      | 300     |      |      | ns      |                        |

| te, hold                        | 500     |      |      | ns      |                        |

| PWR                             | 220     |      |      |         |                        |

| CLEAR                           | 20      |      |      | μS      |                        |

| PWCLEAR                         |         |      |      | •       |                        |

|         | Description of Pin Functions |                          |                                                                                                                                                            |  |  |  |  |  |

|---------|------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin No. | Symbol                       | Name                     | Function                                                                                                                                                   |  |  |  |  |  |

| 1       | A                            | Input A                  | Input signal which is either high or low depending on what word is to be loaded into shift register.                                                       |  |  |  |  |  |

| 2       | RECABC                       | Recirculate ABC          | Input signal when high disconnects inputs from registers<br>and connects outputs to inputs, thus recirculating<br>data. Recirculates only A, B, C outputs. |  |  |  |  |  |

| 3       | CLR                          | Clear                    | Input signal when high forces outputs to a low state<br>immediately and clears all the registers.                                                          |  |  |  |  |  |

| 4       | В                            | Input B                  | Input signal for B register.                                                                                                                               |  |  |  |  |  |

| 5       | Ов                           | Output B                 | Output signal for B register.                                                                                                                              |  |  |  |  |  |

| 6       | GND                          | GND                      | Power supply Ground.                                                                                                                                       |  |  |  |  |  |

| 7       | Vcc                          | +5 Volt                  | 5 volt power supply.                                                                                                                                       |  |  |  |  |  |

| 8       | Oc                           | Output C                 | Output signal for C register.                                                                                                                              |  |  |  |  |  |

| 9       | CLK                          | Clock Input              | Input signal which is normally low and pulses high to shift data into the registers. The data is clocked in on low to high edge of clock.                  |  |  |  |  |  |

| 10      | С                            | Input C                  | Input signal for C register.                                                                                                                               |  |  |  |  |  |

| 11      | NC                           | NC                       | •                                                                                                                                                          |  |  |  |  |  |

| 12      | RECD                         | Recirculate<br>Control D | Input signal which is normally low and, when goes high,<br>disconnects Input D to register and connects<br>Recirculate Input D to register.                |  |  |  |  |  |

| 13      | D                            | Input D                  | Input signal for D register.                                                                                                                               |  |  |  |  |  |

| 14      | Oρ                           | Output D                 | Output signal for D register.                                                                                                                              |  |  |  |  |  |

| 15      | RID                          | Recirculate<br>Input D   | Input signal which is the input to the D register when Recirculate Control D is high: RECD=1.                                                              |  |  |  |  |  |

| 16      | OA                           | Output A                 | Output signal for A register.                                                                                                                              |  |  |  |  |  |

## **APPLICATIONS**

Circuit diagrams utilizing SMC products are included as a means of illustrating typical semiconductor applications: consequently complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchase of the semiconductor devices described any license under the patent rights of SMC or others. SMC reserves the right to make changes at any time in order to improve design and supply the best product possible.