# HIP4011

April 1994

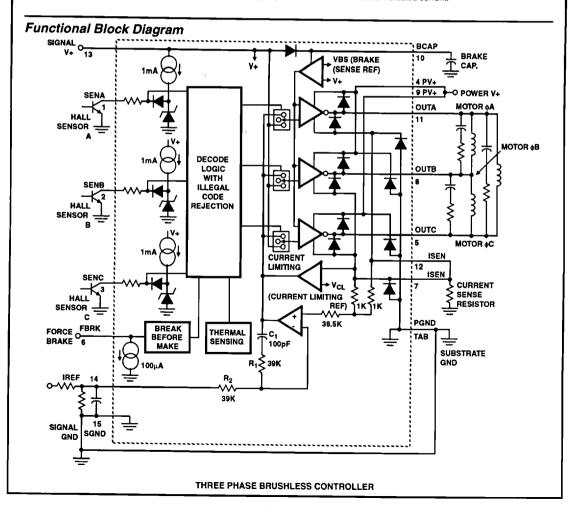

# Three Phase Brushless DC Motor Controller

#### Features

- · 3A DC. 5A Peak Output Current

- 16V Max. Rated Supply Voltage

- . Built-in "Free-Wheeling" Diodes

- · Output dv/dt Limited to Reduce EMI

- · External Dynamic Brake Control Switch With Undervoltage Sense

- . Thermal and Current Limiting Protects Against **Locked Rotor Conditions**

- Provides Analog Current Sense and Reference Inputs

- · Decode Logic with illegal Code Rejection

### **Applications**

Pinout

- · Drive Spindie Motor Controller

- 3 Phase Brushless DC Motor Controller

- . Brushless DC Motor Driver for 12V Battery Powered **Appliances**

- Phased Driver for 12V DC Applications

- · Logic Controlled Driver for Solenoids, Relays and Lamps

# Description

The HIP4011 motor driver is intended for three phase Brushless motor control at continuous output currents up to 3A. It accepts inputs from buffered Hall effect sensors and drives three motor windings, regulating the current through an external current sensing resistor, according to an analog control input. Output "freewheeling" diodes are built in and output dv/dt is limited to decrease the generated EMI. Thermal and current limiting are used to protect the device from locked rotor conditions. A brake control input forces all outputs to ground simultaneously to provide dynamic braking, and an internal voltage sensor does the same when the supply drops below a predetermined switch point. Power down braking energy is stored in an external capacitor.

# Ordering Information

| PART<br>NUMBER | TEMPERATURE<br>RANGE | PACKAGE                             |

|----------------|----------------------|-------------------------------------|

| HIP4011IS      | -40°C to +85°C       | 15 Pin Plastic SIP<br>Surface Mount |

#### HIP4011 (SIP) TOP VIÈW SGND = SIGNAL GROUND SPD = SPEED CONTROL = SIGNAL V+ PGND PIN SV+ (TAB) MUST BE O = ISENSE OUTA = OUTPUT A ELECTRICALLY BCAP = BRAKING CAPACITOR 10 CONNECTED PV+ = POWER V+ OUTB = OUTPUT B ISEN = ISENSE FBRK = FORCED BRAKE OUTC - OUTPUT C 0 PV+ = POWER V+ SENC = SENSE INPUT C

#### **OUTPUT TRUTH TABLE**

|   | SENSOR<br>INPUTS |   | FORCE<br>BRAKE<br>INPUT* | OUTPUTS |     |     |

|---|------------------|---|--------------------------|---------|-----|-----|

| Α | В                | C | FBRK                     | A       | В   | O   |

| 0 | 0                | 0 | 0                        | OFF     | OFF | OFF |

| 1 | 0                | 0 | 0                        | 1       | OFF | 0   |

| 0 | 1                | 0 | 0                        | 0       | 1   | OFF |

| 1 | 1                | 0 | 0                        | OFF     | 1   | 0   |

| 0 | 0                | 1 | 0                        | OFF     | 0   | 1   |

| 1 | 0                | 1 | 0                        | 1       | 0   | OFF |

| 0 | 1                | 1 | 0                        | 0       | OFF | 1   |

| 1 | 1                | 1 | 0                        | OFF     | OFF | OFF |

| х | ×                | Х | 1                        | 0       | 0   | 0   |

Undervoltage and Force Brake logic truth table entries are identical.

SENB = SENSE INPUT B

<sup>&</sup>quot;X" = Don't Care

# Specifications HIP4011

| Referred to SGND or PGND (Note 1) 15 Lead SIP Power Package | Absolute Maximum Ratings          | Thermal Information                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Logic Input Current                                         | Referred to SGND or PGND (Note 1) | 15 Lead SIP Power Package. 45°C/W 3°C/W Power Dissipation (Note 3) . 25W Junction Temperature Range, Operating . +150°C Storage Temperature Range55°C to +150°C Power Dissipation Up to +125°C without heat sink . 0.56W Above +125°C without Heat Sink . Derate Linearly at 22mW/°C Up to +125°C with Infinite Heat Sink . 8.33W Above +125°C with Infinite Heat Sink |

#### NOTES:

- 1. PV+ and SV+ are to be tied together, as are PGND and SGND.

- 2. Operating above the continuous current rating causes a decrease in operating life.

- 3. Derate power dissipation above case temperature of +75°C at 0.33 Watts/°C.

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

# Electrical Specifications T<sub>A</sub> = +25°C and SV+ = PV+ = 10.4V to 13.2V, Unless Otherwise Specified

| PARAMETERS                 | TEST CONDITION                                                 | MIN             | TYP                                     | MAX      | UNITS |

|----------------------------|----------------------------------------------------------------|-----------------|-----------------------------------------|----------|-------|

| SUPPLY (SV+) CURRENT       |                                                                |                 | -                                       |          |       |

| No Drive                   | Outputs Off                                                    | 1 -             | -                                       | 10       | mA    |

| With Drive                 | Outputs On                                                     | •               | -                                       | 15       | mA    |

| LOGIC INPUT CURRENT        | · · · · · ·                                                    |                 |                                         |          |       |

| Sensor Inputs              | SENA, SENB & SENC = 0V to 3V                                   | -0.5            | -                                       | -1.5     | mA    |

| Brake Input                | FBRK = 0.8V to 2.4V                                            | 50              | ·                                       | 150      | μА    |

| LOGIC INPUT THRESHOLDS     |                                                                |                 |                                         |          |       |

| Sensor Inputs              | Logic "0" Input Voltage                                        | •               | -                                       | 1.8      | V     |

| Sensor Inputs              | Logic "1" Input Voltage                                        | 3               | -                                       | -        | V     |

| Brake Input                | Logic "0" Input Voltage                                        | -               | •                                       | 0.8      | V     |

| Brake Input                | Logic "1" Input Voltage                                        | 2.4             | -                                       | •        | V     |

| AMPLIFIER INPUT (SPD)      | •                                                              |                 |                                         |          |       |

| Bias Current               |                                                                | •               | •                                       | 700      | nA    |

| Offset Voltage             |                                                                | -               | -                                       | 3        | m∨    |

| Input Range (Linear)       |                                                                | 0               | -                                       | 1        | V     |

| Input Impedance            |                                                                | 1               | -                                       | -        | MΩ    |

| System Bandwidth           | (Note 1)                                                       | · ·             | 35                                      | -        | kHz   |

| Current Limit              | Rsense = 0.20Ω                                                 | · ·             | 5                                       | -        | A     |

| THERMAL LIMIT              |                                                                |                 | • • • • • • • • • • • • • • • • • • • • |          | •     |

| Threshold                  |                                                                | •               | 155                                     |          | °C    |

| Hysteresis                 |                                                                | -               | 40                                      |          | °C    |

| OUTPUT DRIVERS             |                                                                |                 |                                         | •        | •     |

| On Saturation (See Note 5) | I <sub>OUT</sub> = 3A, V <sub>PMOS</sub> + V <sub>NMOS</sub>   | · · ·           | -                                       | 2.2      | V     |

| On Saturation (See Note 5) | I <sub>OUT</sub> = 0.6A, V <sub>PMOS</sub> + V <sub>NMOS</sub> | -               | -                                       | 0.44     | V     |

| Off Leakage                | PV+ > V <sub>OUT</sub> > PGND or I <sub>SEN</sub>              | <del>- </del> - |                                         | 1        | mA    |

| Slew Rate                  | (See Note 2)                                                   | · ·             | 0.5                                     | <u> </u> | V/µS  |

# Electrical Specifications T<sub>A</sub> = +25°C and SV+ = PV+ = 10.4V to 13.2V, Unless Otherwise Specified (Continued)

| PARAMETERS                   | TEST CONDITION                                | MIN | TYP | MAX      | UNITS |

|------------------------------|-----------------------------------------------|-----|-----|----------|-------|

| FREEWHEEL DIODES             |                                               |     |     |          |       |

| Forward Drop                 | I <sub>OUT</sub> = 1A                         |     |     | 1.5      | V     |

| INTERNAL BRAKE DRIVER        |                                               |     | L   | <u> </u> |       |

| Undervoltage Trip Point, PV+ | (See Note 3)                                  | 2.7 |     | 3.3      | T v   |

| Hysteresis                   | (See Note 4)                                  | 40  |     | 60       | %     |

| On Saturation                | Each N <sub>MOS</sub> , I <sub>OUT</sub> = 3A | -   |     | 0.4      | V     |

| BRAKE CAPACITOR (BCAP)       |                                               |     |     | ·        |       |

| Discharge Leakage            | SV+ = PV+ = 3V to 12V, BCAP = 10V             |     |     | 5        | μА    |

#### NOTES:

- 1. The system bandwidth is fixed by an internal RC network around the amplifier.

- 2. Internal limiting of turn on and turn off drive is used to limit output dv/dt.

- 3. The braking action starts at the given trip point with a falling supply voltage.

- 4. Hysteresis causes the brake to be removed at a higher trip point with a rising supply voltage.

- 5. This value includes the combined voltage drops of one upper plus one lower switch at the indicated current.