The Future of Analog IC Technology

# Battery Protection IC for 2-/3-Series Cell Li-Ion with Integrated Protective MOSFET and PTC Interface in TSOT23-8 Package

#### DESCRIPTION

The MP6420 provides over-charge protection that integrates a protective, open-drain MOSFET for 2- or 3-series cell Li-ion power systems.

The MP6420 provides a ±25mV, high-accuracy, over-charge threshold to monitor all series' battery pack conditions. With the high-accuracy threshold, the MP6420 can provide different fixed thresholds from 4.2V to 4.8V internally. Any cell over-charge that occurs turns on the internal protective MOSFET to indicate an error after an internally set, fixed delay time.

The MP6420 is available in a small, space-saving TSOT23-8 package.

#### **FEATURES**

- Wide VB1 Range from 3.6V to 18V

- Fixed Over-Charge Threshold from 4.2V to 4.8V

- High-Accuracy ±25mV Over-Charge Threshold

- Supports 2- and 3-Series Cells

- Fixed Delay Time from 2s to 8s

- Integrated 24V/100mΩ Protective MOSFETs

- Low Quiescent Current: 3µA

- Over-Voltage Protection (OVP) Indicator (FLAG) and PTC Interface

- External Control (CTL)

- Available in a TSOT23-8 Package

#### **APPLICATIONS**

- Battery Packs

- Uninterruptible Power Supply (UPS)

- Power Tools

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

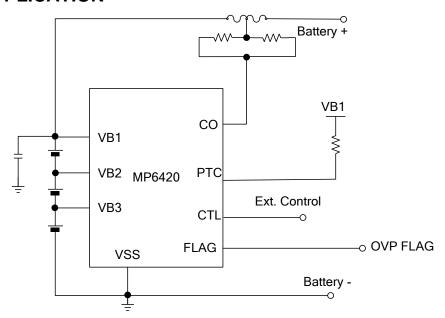

# TYPICAL APPLICATION

# **ORDERING INFORMATION**

| Part Number* | Package  | Top Marking |

|--------------|----------|-------------|

| MP6420GJ     | TSOT23-8 | See Below   |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP6420GJ-Z)

# **TOP MARKING**

| AVFY

AVF: Product code of MP6420GJ

Y: Year code

# **OVER-VOLTAGE THRESHOLD**

| Part Number  | Over-Voltage Threshold (Vov) | Over-Voltage Threshold<br>(Vov_н) | Over-Voltage<br>Delay Time |  |

|--------------|------------------------------|-----------------------------------|----------------------------|--|

| MP6420GJ-445 | 4.45V ± 25mV                 | -0.4 ± 0.16V                      | $3.8 \pm 0.8s$             |  |

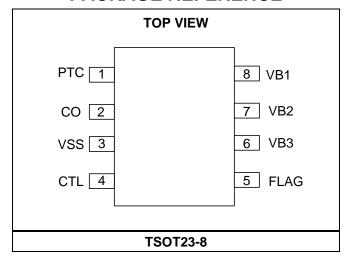

# **PACKAGE REFERENCE**

#

Operating junction temp. (T<sub>J</sub>)...-40°C to +125°C

| Thermal Resistance (4)      | $oldsymbol{	heta}_{JA}$ | θις     |

|-----------------------------|-------------------------|---------|

| TSOT23-8                    |                         |         |

| JESD51-7 <sup>(4)</sup>     | . 100                   | 55 °C/W |

| EV6420-J-00A <sup>(5)</sup> | . 100                   | 26 °C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

- 5) Measured on EV6420-J-00A,2-player PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{B1}$  = 12V,  $V_{B1}$  to  $V_{B2}$  =  $V_{B2}$  to  $V_{B3}$  =  $V_{B3}$  to  $V_{SS}$  = 4V,  $T_J$  = -40°C to +125°C, typical value is tested at  $T_J$  = 25°C. The limit over temperature is guaranteed by characterization, unless otherwise noted.

| Parameters                                         | Symbol               | Condition                                                                                           | Min  | Тур               | Max | Units |

|----------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------|------|-------------------|-----|-------|

| Input and Supply Voltage Rang                      | je                   | <u> </u>                                                                                            | •    |                   |     |       |

| Input voltage                                      | $V_{B1}$             | V <sub>B1</sub> voltage                                                                             | 3.6  |                   | 18  | V     |

| V <sub>B1</sub> under-voltage lockout<br>threshold | V <sub>B1_UVLO</sub> | Rising edge                                                                                         |      | 3.2               | 4   | V     |

| UVLO hysteresis (8)                                | V <sub>B1_HYS</sub>  |                                                                                                     |      | 200               |     | mV    |

| Quiescent current                                  | Ιq                   | Normal condition (6) (7)                                                                            |      | 3                 | 5   | μA    |

| Quiescent current during over-<br>discharge        |                      | Over-discharge condition, $V_{B1}$ to $V_{B2}$ = $V_{B2}$ to $V_{B3}$ = $V_{B3}$ to $V_{SS}$ = 3.3V |      | 2                 |     | μA    |

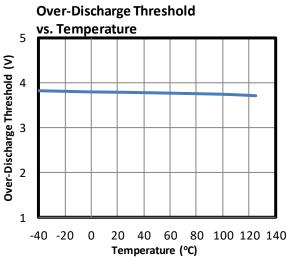

| Over-discharge cell voltage                        | $V_{Dis}$            | Falling edge, $V_{B1}$ to $V_{B2} = V_{B2}$ to $V_{B3} = V_{B3}$ to $V_{SS}$                        | 3.5  | 3.8               | 4.1 | V     |

| Over-discharge cell voltage hysteresis             |                      |                                                                                                     |      | 60                |     | mV    |

| Quiescent current during shutdown                  |                      | Over-discharge condition, $V_{B1}$ to $V_{B2} = V_{B2}$ to $V_{B3} = V_{B3}$ to $V_{SS} = 2.2V$     |      | 1                 |     | μA    |

| V <sub>BX</sub> leakage current                    | I <sub>BX</sub>      | Normal condition (6) (7)                                                                            |      | 0                 |     | μA    |

| Voltage Threshold                                  |                      |                                                                                                     |      |                   |     |       |

| Over-charge threshold                              | Vov                  | See ordering info                                                                                   |      | Vov               |     | V     |

| •                                                  |                      | T <sub>J</sub> = 25°C                                                                               | -25  |                   | 25  |       |

| Over-charge threshold range                        |                      | $T_J = 85^{\circ}C^{(8)}$                                                                           | -30  |                   | 45  | mV    |

|                                                    |                      | $T_J = -40^{\circ}C^{(8)}$                                                                          | -50  |                   | 30  |       |

| Over-charge hysteresis                             | $V_{OV_{H}}$         | See ordering info                                                                                   |      | V <sub>OV_H</sub> |     | mV    |

| Over-charge hysteresis range                       |                      | $T_J = 25$ °C                                                                                       | -160 |                   | 160 | mV    |

| Protective MOSFET                                  |                      |                                                                                                     |      |                   |     |       |

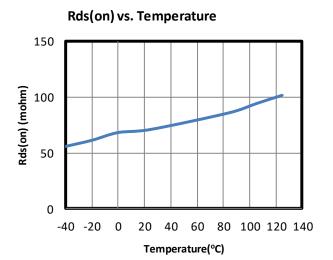

| On resistance                                      | R <sub>DS(ON)</sub>  | $V_{B1} = 5.0V$ , single channel                                                                    |      | 100               |     | mΩ    |

| Current capability                                 |                      | Guaranteed by design                                                                                | 4.5  |                   |     | Α     |

| Breakdown voltage                                  |                      |                                                                                                     | 28   |                   |     | V     |

| Resistor between FLAG and CTL                      |                      |                                                                                                     |      | 240               |     | kΩ    |

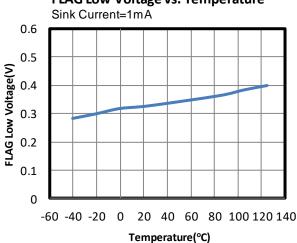

| FLAG low voltage                                   |                      | Sink 1mA                                                                                            |      |                   | 0.5 | V     |

| FLAG high voltage                                  |                      | Source 1mA                                                                                          | 4    |                   | 5.5 | V     |

| CTL low voltage                                    |                      | $V_{B1}$ to $V_{B2} = V_{B2}$ to $V_{B3} = V_{B3}$ to $V_{SS} = 3.7V$ , sink $1\mu A$               |      |                   | 0.3 | V     |

| CTL high voltage                                   |                      | $V_{B1}$ to $V_{B2} = V_{B2}$ to $V_{B3} = V_{B3}$ to $V_{SS} = 4.5V$ , source 1 $\mu$ A load       | 4    | 4.5               | 5.5 | V     |

| CTL rising threshold                               |                      | Turn on the protective MOSFET                                                                       |      | 2                 |     | V     |

| CTL falling threshold                              |                      | Turn off the protective MOSFET                                                                      |      | 1.5               |     | V     |

| PTC Interface                                      |                      | •                                                                                                   |      |                   |     |       |

| PTC threshold                                      |                      | Falling edge                                                                                        |      | V <sub>B1</sub> - |     | V     |

| PTC hysteresis                                     |                      | Rising edge                                                                                         |      | 400               |     | mV    |

| PTC deglitch delay                                 |                      | Guaranteed by design                                                                                |      | 100               |     | μs    |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{B1}$  = 12V,  $V_{B1}$  to  $V_{B2}$  =  $V_{B2}$  to  $V_{B3}$  =  $V_{B3}$  to  $V_{SS}$  = 4V,  $V_{J}$  = -40°C to +125°C, typical value is tested at  $V_{J}$  = 25°C. The limit over temperature is guaranteed by characterization, unless otherwise noted.

| Parameters                    | rameters Symbol Condition |                                     | Min | Тур | Max | Units |  |

|-------------------------------|---------------------------|-------------------------------------|-----|-----|-----|-------|--|

| Delay Time                    |                           |                                     |     |     |     |       |  |

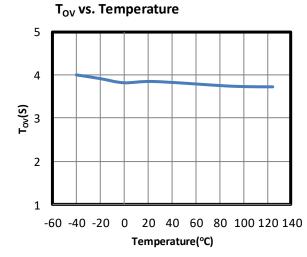

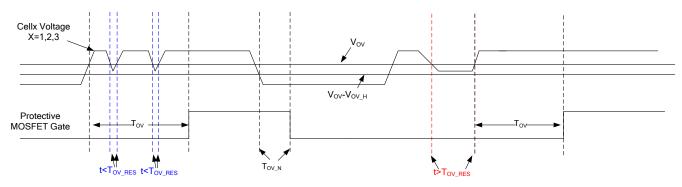

| Over-charge response delay    | Tov                       | Any V <sub>BX</sub> over-charge     | 3   | 3.8 | 4.6 | S     |  |

| Over-charge reset time        | T <sub>OV_RES</sub>       |                                     |     | 10  |     | ms    |  |

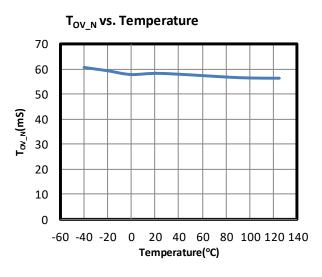

| Over-charge release delay     | T <sub>OV_N</sub>         |                                     |     | 60  |     | ms    |  |

| PTC response delay            |                           | Before turning on protective MOSFET |     | 1.8 |     | ms    |  |

| Over-discharge recovery delay |                           | From over-discharge to normal mode  |     | 1   |     | ms    |  |

| Internal Filter               |                           |                                     |     |     |     |       |  |

| Filter resistor (9)           |                           |                                     |     | 3   |     | ΜΩ    |  |

| Filter capacitor (9)          |                           |                                     |     | 100 |     | pF    |  |

#### NOTES:

- 6) Normal condition means no over-charge condition occurred.  $V_{B1}$  to  $V_{B2} = V_{B2}$  to  $V_{B3} = V_{B3}$  to  $V_{SS} = 4V$ .

- 7) Test schematic excludes FLAG sink current.

- 8) Not tested in production, guaranteed by design specification.

- 9) Guaranteed by design.

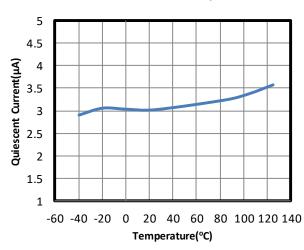

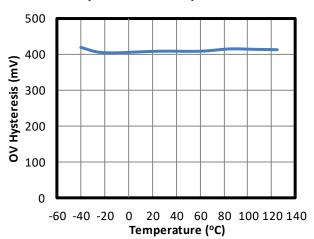

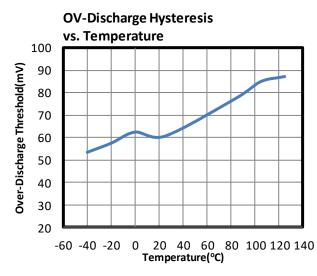

# **TYPICAL CHARACTERISTICS**

$V_{B1}$  = 12V,  $V_{B1}$  to  $V_{B2}$  =  $V_{B2}$  to  $V_{B3}$  =  $V_{B3}$  to  $V_{SS}$  = 4V,  $T_J$  = -40°C to +125°C. Test based on MP6420GJ-445, unless otherwise noted.

#### **Quiescent Current vs. Temperature**

#### **OV Hysteresis vs. Temperature**

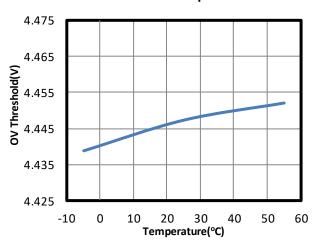

#### **OV Threshold Vs. Temperature**

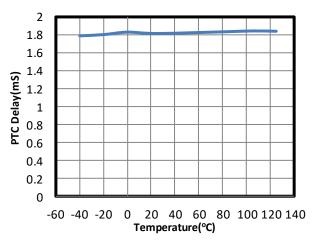

PTC Delay vs. Temperature

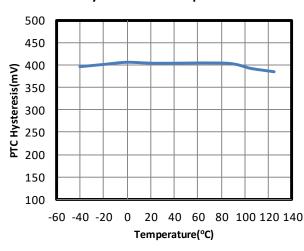

#### PTC Hysteresis vs. Temperature

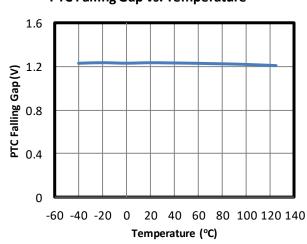

#### PTC Falling Gap vs. Temperature

# TYPICAL CHARACTERISTICS (continued)

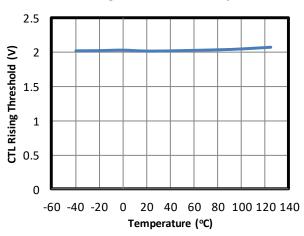

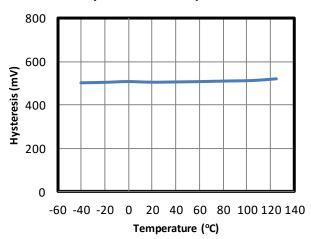

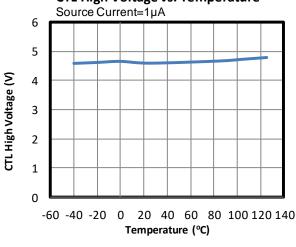

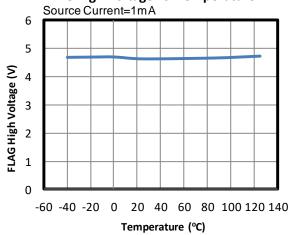

$V_{B1}$  = 12V,  $V_{B1}$  to  $V_{B2}$  =  $V_{B2}$  to  $V_{B3}$  =  $V_{B3}$  to  $V_{SS}$  = 4V,  $T_J$  = -40°C to +125°C. Test based on MP6420GJ-445, unless otherwise noted.

#### CTL Rising Threshold vs. Temperature

#### CTL Hysteresis vs. Temperature

#### **CTL High Voltage vs. Temperature**

# CTL Low voltage vs. Temperature

#### **FLAG High Voltage vs. Temperature**

# **FLAG Low Voltage vs. Temperature**

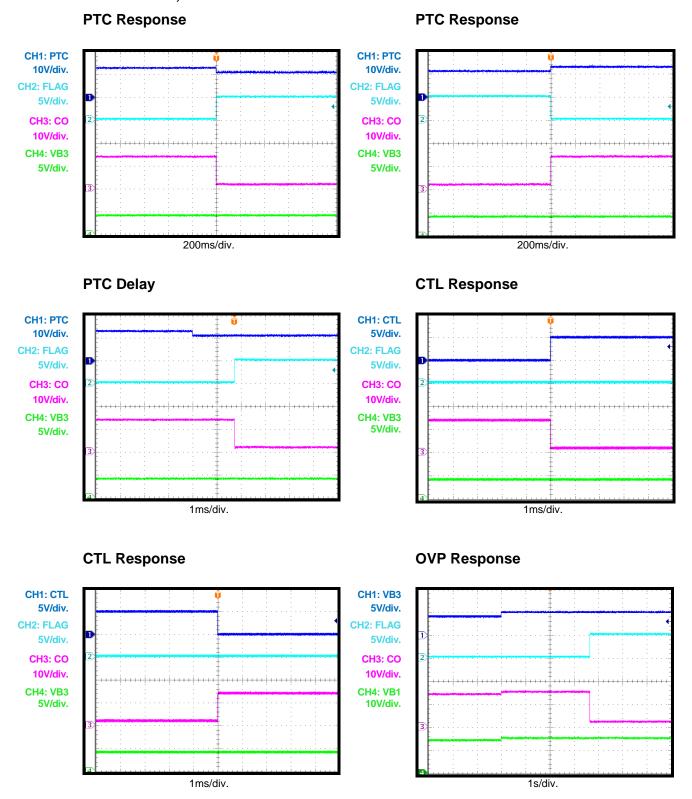

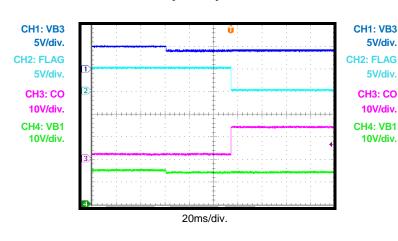

# TYPICAL CHARACTERISTICS (continued)

$V_{B1}$  = 12V,  $V_{B1}$  to  $V_{B2}$  =  $V_{B2}$  to  $V_{B3}$  =  $V_{B3}$  to  $V_{SS}$  = 4V,  $T_J$  = -40°C to +125°C. Test based on MP6420GJ-445, unless otherwise noted.

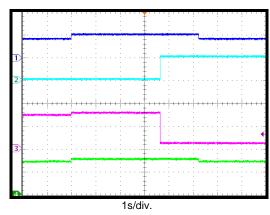

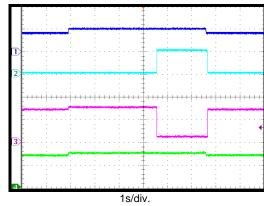

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{B1}$  to  $V_{B2}$  =  $V_{B2}$  to  $V_{B3}$  =  $V_{B3}$  to  $V_{SS}$  = 4V with 10k $\Omega$  resistor between VB1 and PTC,  $T_J$  = 25°C. Test based on MP6420GJ-445, unless otherwise noted.

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{B1}$  to  $V_{B2} = V_{B2}$  to  $V_{B3} = V_{B3}$  to  $V_{SS} = 4V$  with  $10k\Omega$  resistor between VB1 and PTC,  $T_J = 25$ °C. Test based on MP6420GJ-445, unless otherwise noted.

CH1: VB3

5V/div.

5V/div.

CH3: CO 10V/div.

CH4: VB1

10V/div.

# **OVP Recovery Delay**

# **OVP Response**

#### **OVP Recovery**

VB1 to VB2 = VB2 to VB3 = 3.9V

# **PIN FUNCTIONS**

| Package<br>Pin # | Name | Description                                                                                                                         |

|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1                | PTC  | Positive thermal coefficient interface.                                                                                             |

| 2                | CO   | Open-drain output of the protective MOSFET.                                                                                         |

| 3                | VSS  | Negative power supply.                                                                                                              |

| 4                | CTL  | <b>External control.</b> CTL connects to the gate pin of the internal protective MOSFET.                                            |

| 5                | FLAG | <b>Battery OVP indicator.</b> When OVP occurs and the internal protective MOSFET turns on, FLAG is pulled up to at least 4V.        |

| 6                | VB3  | <b>Voltage sense point of battery cell 3.</b> VB3 is connected to the positive voltage of cell 3. Place cell 2 between VB2 and VB3. |

| 7                | VB2  | Voltage sense point of battery cell 2. VB2 is connected to the positive voltage of cell 2. Place cell 1 between VB1 and VB2.        |

| 8                | VB1  | Voltage sense point of battery cell 1. VB1 is connected to the positive voltage of cell 1.                                          |

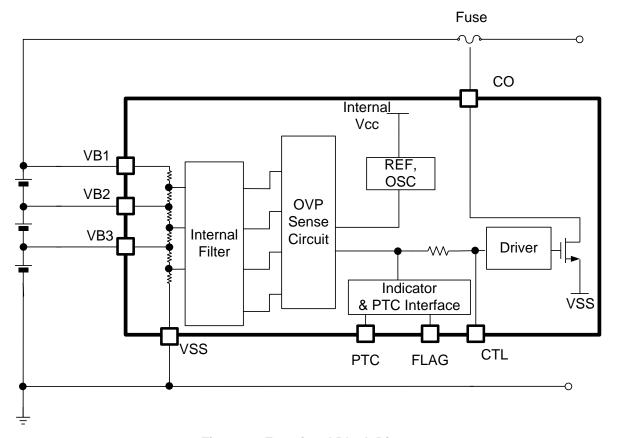

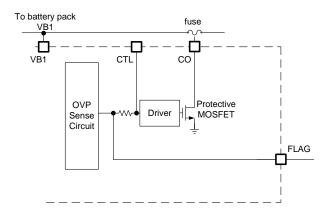

# **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

#### **OPERATION**

The MP6420 provides an over-charge protection that integrates a protective, opendrain MOSFET for 2- or 3-series cell Li-ion power systems.

The MP6420 provides a ±25mV, high-accuracy, over-charge threshold to monitor all series' battery pack conditions. With the high-accuracy threshold, the MP6420 provides different fixed thresholds from 4.2V to 4.8V internally. Any cell over-charge turns on the internal protective MOSFET to indicate an error after a fixed, internally set delay time. FLAG is used to indicate an over-voltage protection (OVP) condition, provide a PTC interface, and can control the protective MOSFET externally with CTL.

#### Over-Voltage Detection

All cells are monitored between VB1 and VB2, VB2 and VB3, and VB3 and VSS. If any of the voltages from these cells rise higher than the over-voltage threshold ( $V_{OV}$ ), OVP is triggered. The internal MOSFET turns on and remains on until the cell over-voltage status remains longer than the over-charge response delay ( $T_{OV}$ ). The  $T_{OV}$  timer can be reset if the cell voltage drops below the over-threshold voltage and remains longer than the over-charge reset time ( $T_{OV\_RES}$ ). The OVP status is released if all cell voltages fall below the over-voltage release voltage ( $V_{OV} - V_{OV\_H}$ ), and the internal MOSFET turns off again. There is an over-charge release delay ( $T_{OV\_N}$ ) to deglitch noise (see Figure 2).

Figure 2: MP6420 Over-Voltage Response

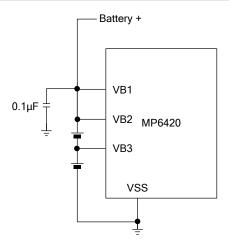

#### **Integrated MOSFET and Filter**

Traditionally, secondary battery protection ICs need an external, high-voltage, or large-current MOSFET. Each cell requires an R-C filter to prevent cell voltage noise. The MP6420 provides a fully integrated solution with a protective MOSFET and internal filter. The internal filter has an equivalent  $1k\Omega/0.1\mu F$  external R-C filter performance. This helps lower cost and make the layout easier. The internal protective MOSFET is a  $24V/100m\Omega$  device. The filter works with an anti-noise overvoltage comparator, which can monitor the battery voltage.

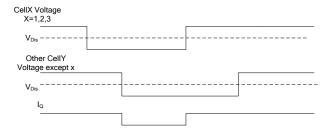

#### **Over-Discharge Status**

The MP6420 saves quiescent current when the voltage on all cells is over-discharged. If the voltage of all the cells is lower than the over-discharge threshold (V<sub>Dis</sub>), the cell over-voltage monitor block is disabled. The disabled over-charge detection block decreases the quiescent current during an over-discharge status (see Figure 3).

Figure 3: Over-Discharge Status

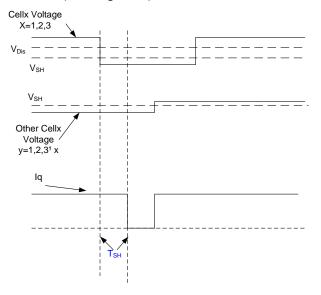

#### **Shutdown Status**

The MP6420 decreases most of the quiescent current during shutdown. When all cell voltages are lower than  $V_{Dis}$  and the shutdown voltage ( $V_{SH}$ ), all over-voltage (OV) monitor blocks are disabled (see Figure 4).

Figure 4: Shutdown Status

#### **FLAG Indicator**

FLAG is an indicator pin. Under normal conditions, FLAG is at logic low. When over-charge occurs or over-temperature is detected by PTC, FLAG is pulled up to an internal 5V supply (see Figure 5). FLAG can be floated.

Figure 5: FLAG and CTL Structure

#### **Cell Connection Power Sequence**

Since the MP6420 internal VCC is based on VB3, it is recommended to make VB3 the first connection in the power sequence (see Table 1). CTL provides another way to avoid a malfunction during the assembly process. CTL is pulled down to VSS so that the inner protective MOSFET is not active.

Figure 6: Recommended Safe Operation during Assembly Process

**Table 1: Recommended Connection Sequence**

| Connection Sequence | FLAG Pin Signal |     |     | CO Pin Signal |      |      |      |      |

|---------------------|-----------------|-----|-----|---------------|------|------|------|------|

| Connection Sequence | Int.            | 1st | 2nd | 3rd           | Int. | 1st  | 2nd  | 3rd  |

| →VSS→VB3→VB2→VB1    | Low             | Low | Low | Low           | Low  | High | High | High |

| →VSS→VB3→VB1→VB2    | Low             | Low | Low | Low           | Low  | High | High | High |

#### APPLICATION INFORMATION

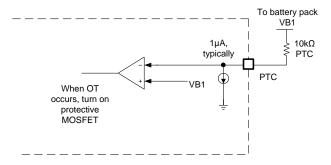

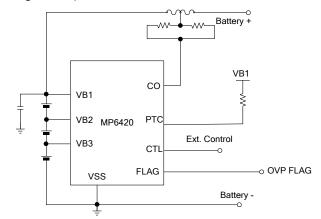

#### **PTC Interface**

PTC can be used to monitor the ambient temperature and turn on the protective MOSFET. PTC cannot be floated. PTC requires a resistor (typically  $10k\Omega$ ) pulled to VB1 (see Figure 7). When the PTC interface is required, a  $10k\Omega$  PTC resistor is recommended. See Table 2 for a list of recommended resistors and manufacturers.

Figure 7: MP6420 PTC Interface

There is an internal sink current source used to pull down the PTC voltage (typically ~1 $\mu$ A). Under normal conditions, the FLAG output is at logic low. With 10k $\Omega$  of PTC resistance under room temperature, the PTC voltage is almost equal to VB1. If the sensor PTC resistor monitors high temperatures, the PTC resistance ramps quickly, and the PTC voltage drops. When the PTC voltage is lower than VB1 - 1.2V, the MP6420 triggers PTC protection.

If the PTC function is not needed, a normal  $10k\Omega$  resistor is sufficient.

**Table 2: Recommended PTC Resistors**

| Part Number        | Description    | Vendor  |

|--------------------|----------------|---------|

| PRF15BB103RB6RC    | 10kΩ,<br>130°C | Murata  |

| ECPTH1608103P130ST | 10kΩ,<br>130°C | Joinset |

#### 2-/3-Cell Usage

When the MP6420 has more monitor ports than it is using, the unused ports should be shorted. The VB1 - VB3 monitors must be used from the bottom side. For example, if only two cells are used, then VB1 should be shorted to VB2 (see Figure 8).

Figure 8: 2-Cell Usage

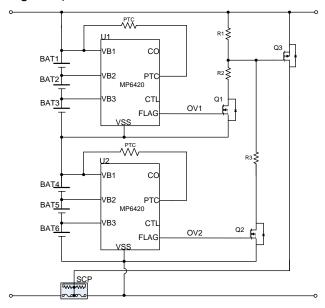

# More than 3-Cell Usage

For applications using a battery with more than three cells, use a MP6420 series circuit (see Figure 9).

Figure 9: 3-Cell Battery or More Application Circuit

Each FLAG is active high when one-cell OVP is triggered. Q3 then turns on to pull down the self-control protector (SCP). The OR logic circuit consists of extra MOSFETs (Q1, Q2, Q3) and pull-up resistors (R1, R2, R3). Choose MOSFETs and resistors based Equation (1):

$$V_{ds max Q1} = 1.3 \times V_{BAT} \tag{1}$$

Where  $V_{BAT}$  is the voltage of each cell battery.

When OV1 is low (no OV trigger on U1) and considering a 30% margin, calculate  $V_{ds}$  with Equation (2):

$$V_{ds max Q2}=1.3\times6V_{BAT}$$

(2)

The Q2 maximum  $V_{ds} = 3V_{BAT}$ .

When OV2 is low (no OV trigger on U2) and considering a 30% margin, calculate  $V_{ds}$  with Equation (3):

$$V_{ds max Q3}=1.3\times6V_{BAT}$$

(3)

The Q3 maximum  $V_{ds} = 6V_{BAT}$ .

When both OV1 and OV2 are low (no OV trigger on either cell) and considering a 30% margin, calculate  $V_{gs}$  with Equation (4) and Equation (5):

$$V_{qs(th) max Q3} < 3V_{BAT} \times R1/(R1 + R2) < V_{qs max Q3}$$

(4)

$$V_{gs(th)_max_Q3} < 6V_{BAT} \times R1/(R1+R3) < V_{gs_max_Q3}$$

(5)

Where  $V_{gs(th)\_max\_Q3}$  is the maximum gate-to-source threshold voltage, and  $V_{gs\_max\_Q3}$  is the maximum gate-to-source voltage of Q3.

#### **Testing Over-Voltage Safely**

During the production test, OVP can be tested safely without blowing the fuse. Connect CTL to GND externally. The protective MOSFET gate is pulled to GND. With this configuration, the battery status can be indicated with FLAG (see Figure 10).

Figure 10: Safe OVP Test

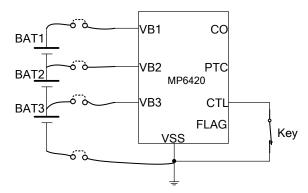

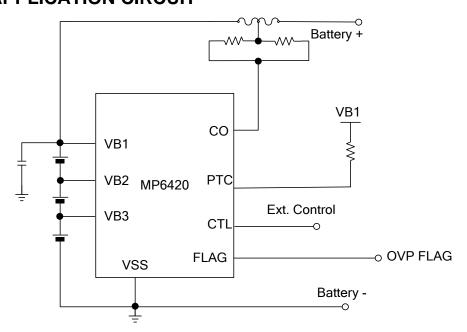

# TYPICAL APPLICATION CIRCUIT

Figure 11: MP6420 Typical Schematic

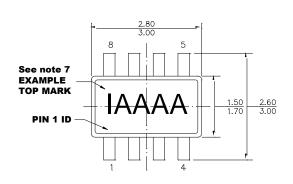

# **PACKAGE INFORMATION**

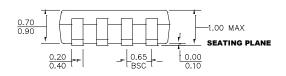

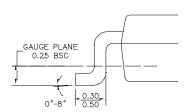

#### **TSOT23-8**

#### **TOP VIEW**

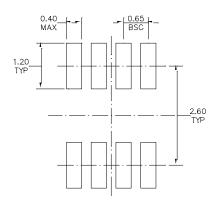

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

**SIDE VIEW**

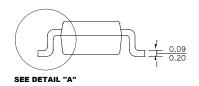

**DETAIL "A"**

#### **NOTE:**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE

- INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS

- AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) JEDEC REFERENCE IS MO-193, VARIATION BA.

- 6) DRAWING IS NOT TO SCALE.

- 7) PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.