## High power density 600V half-bridge driver with two enhancement mode GaN **Power HEMT**

#### OFN 9x9x1 mm

#### **Features**

- 600 V system-in-package integrating half-bridge gate driver and high-voltage GaN power transistors:

- QFN 9 x 9 x 1 mm package

- $R_{DS(ON)} = 225 \text{ m}\Omega$

- $I_{DS(MAX)} = 6.5 A$

- Reverse current capability

- Zero reverse recovery loss

- UVLO protection on low-side and high-side

- Internal bootstrap diode

- Interlocking function

- Dedicated pin for shutdown functionality

- Accurate internal timing match

- 3.3 V to 15 V compatible inputs with hysteresis and pull-down

- Overtemperature protection

- Bill of material reduction

- Very compact and simplified layout

- Flexible, easy and fast design.

#### **Application**

- Switch-mode power supplies

- Chargers and adapters

- High-voltage PFC, DC-DC and DC-AC converters

### **Product status link** MASTERGAN4

### Product label

### **Description**

The MASTERGAN4 is an advanced power system-in-package integrating a gate driver and two enhancement mode GaN power transistors.

The integrated GaN power transistors have 650 V drain-source blocking voltage and RDS(ON) of 225 m $\Omega$ , while the high-side of the embedded gate driver can be easily supplied by the integrated bootstrap diode

The MASTERGAN4 features UVLO protection on both the lower and upper driving sections, preventing the power switches from operating in low efficiency or dangerous conditions, and the interlocking function avoids cross-conduction conditions.

The input pins extended range allows easy interfacing with microcontrollers, DSP units or Hall effect sensors.

The MASTERGAN4 operates in the industrial temperature range, -40°C to 125°C.

The device is available in a compact 9x9 mm QFN package.

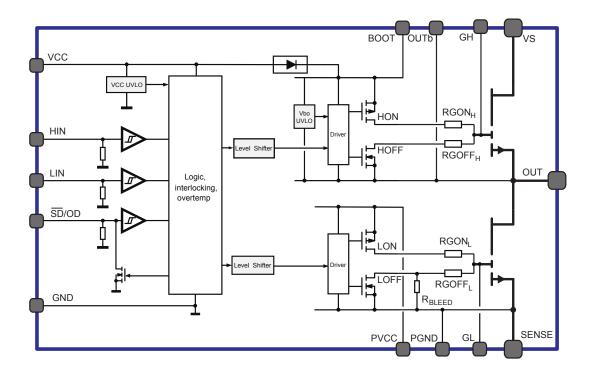

# 1 Block diagram

Figure 1. Block Diagram

DB4419 - Rev 1 page 2/14

## 2 Pin description and connection diagram

28 27 26 24 **GND** PVCC 1 22 BOOT EP1 21 OUTb GL 2 20 GH PGND 3 SENSE 4 19 VS SENSE 5 18 VS SENSE 6 **SENSE** OUT 17 VS EP2 EP3 SENSE 7 16 VS SENSE 8 15 VS SENSE 0 11 13 14 SENSE OUT OUT

Figure 2. Pin connection (top view)

#### 2.1 Pin list

Table 1. Pin description

| Pin Number                    | Pin Name | Туре         | Function                                                                                                         |

|-------------------------------|----------|--------------|------------------------------------------------------------------------------------------------------------------|

| 15, 16, 17, 18, 19            | VS       | Power Supply | High voltage supply (high-side GaN Drain)                                                                        |

| 12, 13, 14, EP3               | OUT      | Power Output | Half-bridge output                                                                                               |

| 4, 5, 6, 7, 8, 9, 10, 11, EP2 | SENSE    | Power Supply | Half-bridge sense (low-side GaN Source)                                                                          |

| 22                            | воот     | Power Supply | Gate driver high-side supply voltage                                                                             |

| 21                            | OUTb     | Power Supply | Gate driver high-side supply voltage, used only for Bootstrap capacitor connection. Internally connected to OUT. |

| 27                            | VCC      | Power Supply | Logic supply voltage                                                                                             |

| 1                             | PVCC     | Power Supply | Gate driver low-side supply voltage                                                                              |

DB4419 - Rev 1 page 3/14

| Pin Number     | Pin Name | Type               | Function                                                           |

|----------------|----------|--------------------|--------------------------------------------------------------------|

| 28, EP1        | GND      | Power Supply       | Gate driver ground                                                 |

| 3              | PGND     | Power Supply       | Gate driver low-side buffer ground. Internally connected to SENSE. |

| 26             | HIN      | Logic Input        | High-side driver logic input                                       |

| 24             | LIN      | Logic Input        | Low-side driver logic input                                        |

| 25             | SD/OD    | Logic Input-output | Driver shutdown input and fault open-drain                         |

| 2              | GL       | Output             | Low-side GaN gate.                                                 |

| 20             | GH       | Output             | High-side GaN gate.                                                |

| 23, 29, 30, 31 | N.C.     | Not connected      | Leave floating                                                     |

DB4419 - Rev 1 page 4/14

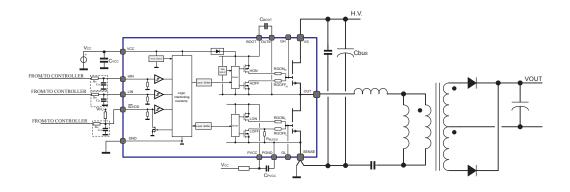

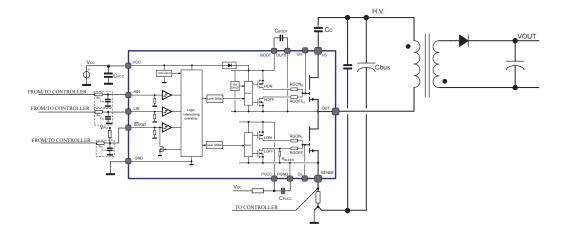

# 3 Typical application diagrams

Figure 3. Typical application diagram – Resonant LLC converter

Figure 4. Typical application diagram – Active clamp flyback

DB4419 - Rev 1 page 5/14

## 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

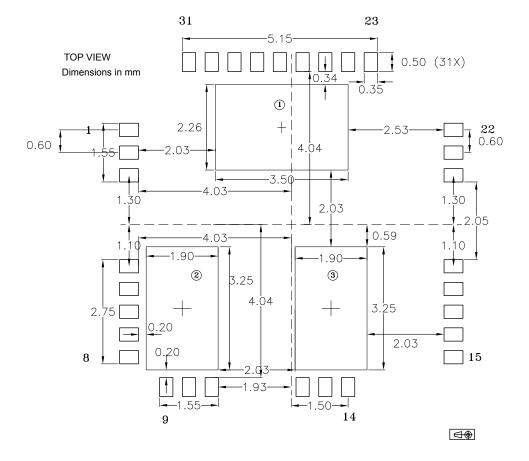

### 4.1 QFN 9 x 9 x 1 mm, 31 leads, pitch 0.6 mm package information

Table 2. QFN 9 x 9 x 1 mm package dimensions

| Symbol | Dimensions (mm) |      |      |  |

|--------|-----------------|------|------|--|

|        | Min.            | Тур. | Max. |  |

| A      | 0.90            | 0.95 | 1.00 |  |

| A3     |                 | 0.10 |      |  |

| b      | 0.25            | 0.30 | 0.35 |  |

| D      | 8.96            | 9.00 | 9.04 |  |

| Е      | 8.96            | 9.00 | 9.04 |  |

| D1     | 3.30            | 3.40 | 3.50 |  |

| E1     | 2.06            | 2.16 | 2.26 |  |

| D2     | 1.76            | 1.86 | 1.96 |  |

| E2     | 3.10            | 3.20 | 3.30 |  |

| D3     | 1.70            | 1.80 | 1.90 |  |

| E3     | 3.10            | 3.20 | 3.30 |  |

| е      |                 | 0.60 |      |  |

| К      |                 | 0.24 |      |  |

| L      | 0.35            | 0.45 | 0.55 |  |

| N      |                 | 31   |      |  |

| aaa    |                 | 0.10 |      |  |

| bbb    | 0.10            |      |      |  |

| CCC    | 0.10            |      |      |  |

| ddd    | 0.05            |      |      |  |

| eee    | 0.08            |      |      |  |

#### Note:

- 1. Dimensioning and tolerances conform to ASME Y14.5-2009.

- 2. All dimensions are in millimeters.

- 3. N total number of terminals.

- 4. Dimensions do not include mold protrusion, not to exceed 0.15 mm.

- 5. Package outline exclusive of metal burr dimensions.

DB4419 - Rev 1 page 6/14

**BOTTOM VIEW** bbb(M) C A B ddd(M) C 0.95±0.05 23 24 25 26 27 28 29 30 31 1.85 Ref. 1 - 2.10±0.10 1  $\subset$ 2 20 --- 2.40 BSC ---3 18 5 17  $\subset$ 6 7 16 15  $\Omega \Omega \Omega$ 1 10 0.0-0.05 l 1.05 Ref. SIDE **VIEW TOP VIEW** B 31 30 29 28 27 26 25 24 23 INDEX AREA 22 21 20 19 18 2 17 8 (] 15 9 10 11 12 13 14 A

Figure 5. QFN 9 x 9 x 1 mm package dimensions

DB4419 - Rev 1 \_\_\_\_\_\_ page 7/14

2x

△ 000 C

## 5 Suggested footprint

The MASTERGAN4 footprint for the PCB layout is usually defined based on several design factors like assembly plant technology capabilities and board component density. For easy device usage and evaluation, ST provides the following footprint design, which is suitable for the largest variety of PCBs.

The following footprint indicates the copper area which should be free from the solder mask, while the copper area is to extend beyond the indicated areas especially for EP2 and EP3. To aid thermal dissipation, it is recommended to add thermal vias under these EPADs to transfer and dissipate device heat to the other PCB copper layers. A PCB layout example is available with the MASTERGAN4 evaluation board.

Figure 6. Suggested footprint (top view drawing)

DB4419 - Rev 1 page 8/14

# 6 Ordering information

Table 3. Order codes

| Order code   | Package          | Package marking | Packaging     |

|--------------|------------------|-----------------|---------------|

| MASTERGAN4   | QFN 9 x 9 x 1 mm | MASTERGAN4      | Tray          |

| MASTERGAN4TR | QFN 9 x 9 x 1 mm | MASTERGAN4      | Tape and Reel |

DB4419 - Rev 1 page 9/14

# **Revision history**

Table 4. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 17-Feb-2021 | 1       | Initial release. |

DB4419 - Rev 1 page 10/14

### **Contents**

| 1    | Block diagram                                                    | 2  |

|------|------------------------------------------------------------------|----|

| 2    | Pin description and connection diagram                           | 3  |

|      | 2.1 Pin list                                                     | 3  |

| 3    | Typical application diagrams                                     | 5  |

| 4    | Package information                                              | 6  |

|      | 4.1 QFN 9 x 9 x 1 mm, 31 leads, pitch 0.6 mm package information | 6  |

| 5    | Suggested footprint                                              | 8  |

| 6    | Ordering information                                             | 9  |

| Rev  | rision history                                                   | 10 |

| Con  | ntents                                                           | 11 |

| List | of tables                                                        | 12 |

| List | of figures                                                       | 13 |

## **List of tables**

| Table 1. | Pin description                     | 3 |

|----------|-------------------------------------|---|

|          | QFN 9 x 9 x 1 mm package dimensions |   |

| Table 3. | Order codes                         | ć |

| Table 4. | Document revision history           | C |

DB4419 - Rev 1 page 12/14

# **List of figures**

| Figure 1. | Block Diagram                                        | 2 |

|-----------|------------------------------------------------------|---|

| Figure 2. | Pin connection (top view)                            | 3 |

| Figure 3. | Typical application diagram – Resonant LLC converter | 5 |

| Figure 4. | Typical application diagram – Active clamp flyback   | 5 |

| Figure 5. | QFN 9 x 9 x 1 mm package dimensions                  | 7 |

| Figure 6. | Suggested footprint (top view drawing)               | 8 |

DB4419 - Rev 1 page 13/14

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DB4419 - Rev 1 page 14/14