- Detects and Corrects Single-Bit Errors

- Detects and Flags Dual-Bit Errors

- Built-In Diagnostic Capability

- Fast Write and Read Cycle Processing Times

- Byte-Write Capability

- Dependable Texas Instruments Quality and Reliability

## description

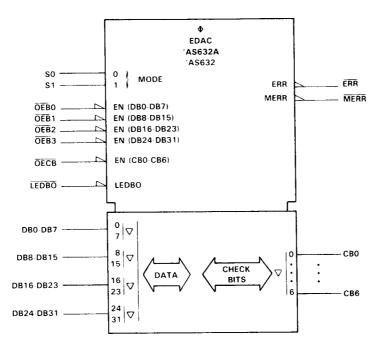

The 'AS632A device is a 32-bit parallel error detection and correction circuit (EDAC). This EDAC uses a modified Hamming code to generate a 7-bit check word from a 32-bit data word. This check word is stored along with the data word during the memory write cycle. During the memory read cycle, the 39-bit words from memory are processed by the EDAC to determine if errors have occurred in memory.

Single-bit errors in the 32-bit data word are flagged and corrected.

Single-bit errors in the 7-bit check word are flagged, and the CPU sends the EDAC through the correction cycle even though the 32-bit data word is not in error. The correction cycle will simply pass along the original 32-bit data word in this case and produce error syndrome bits to pinpoint the error-generating location.

Dual-bit errors are flagged but not corrected. These errors may occur in any two bits of the 39-bit data word from memory (two errors in the 32-bit data word, two errors in the 7-bit check word, or one error in each word). The gross-error condition of all lows or all highs from memory will be detected. Otherwise, errors in three or more bits of the 39-bit word are beyond the capabilities of this device to detect.

Read-modify-write (byte-control) operations can be performed by using output latch enable, LEDBO, and the individual OEBO thru OEB3 byte control pins.

Diagnostics are performed on the EDAC by controls and internal paths that allow the user to read the contents of the DB and CB input latches. These will determine if the failure occurred in memory or in the EDAC.

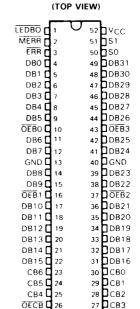

N OR JD PACKAGE

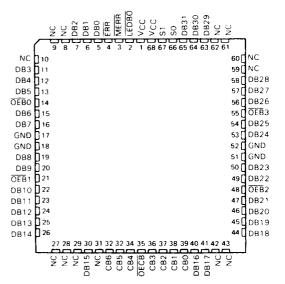

## FN PACKAGE (TOP VIEW)

NC No internal connection

Texas Instruments

## logic symbol†

<sup>&</sup>lt;sup>†</sup>This symbol is an accordance with ANSI/IEEE-Std 91-1984.

## for complete data sheet

The complete version of this data sheet and application information can be found in the *Cache Memory Management Data Book*, Literature #SCAD002. To obtain a copy of this data book, contact your local TI sales representative or call the TI Customer Response Center at 1-800-223-3200.