June 2011

# **FAB2200**

# Audio Subsystem with Stereo Class-G Headphone Amplifier and 1.2W Mono Class-D Speaker Amplifier

# **Features**

- Single Supply: 2.8V 5.25V

- Pop and Click Suppression

- Differential or Single-Ended Audio Inputs

- Rejects TDMA Noise from GSM Handsets

- Filterless Fully Differential Class-D Speaker Amplifier

- Programmable Edge-Rate Control and Spread Spectrum Minimize EMI

- 1.2W into 8Ω at 4.2V, THD+N < 10%

- 970mW into  $8\Omega$  at 4.2V, THD+N < 1%

- 90% Efficiency

- Automatic Gain Control Limits Distortion and Protects Speakers at All Battery Voltages

- Noise Gate Improves Audio Quality

- Headphone Amplifier

- Power-Saving Class-G Operation

- Audio Taper I<sup>2</sup>C Volume Control

- Capacitor-Free Outputs

- Integrated Regulated Charge Pump

- SGND Pin Eliminates Ground-Loop Noise

- Noise Gate Improves Audio Quality

- DPST Analog Bypass Switch

- I<sup>2</sup>C Control

- Low-Power Shutdown Mode

- Current Limit and Thermal Protection

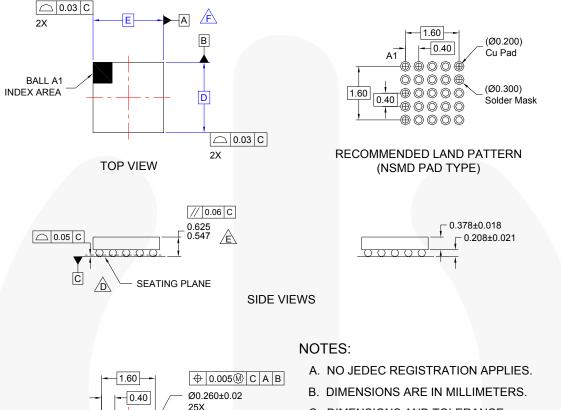

- 25-Bump, 0.4mm Pitch WLCSP Package

# Description

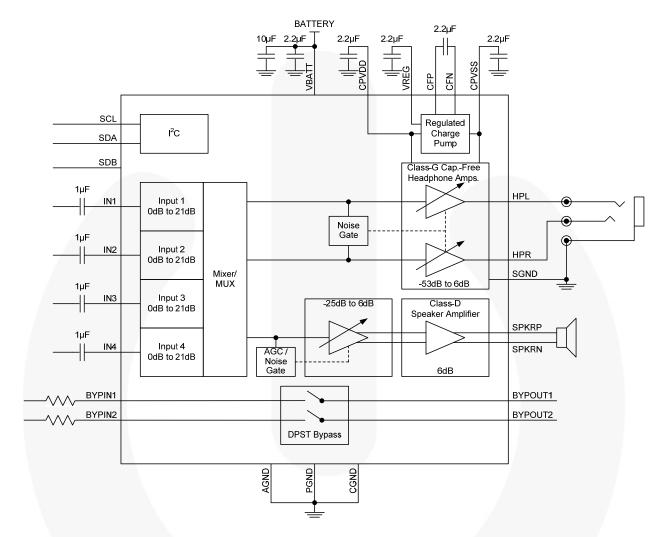

The FAB2200 combines a capacitor-free stereo headphone amplifier with a monolithic class-D speaker amplifier.

An integrated charge pump generates multiple supply rails for a ground-centered class-G headphone output. The charge pump is regulated for high Power Supply Rejection Ratio (PSRR).

The filterless class-D amplifier can be connected directly to a speaker without external filters.

The programmable Automatic Gain Control (AGC) limits maximum speaker output levels to protect speakers without introducing distortion. It can also dynamically limit clipping as the battery voltage falls.

The noise gate can automatically mute the speaker or headphone amplifiers to reduce noise when input signals are low.

# **Applications**

- Cellular Handsets

- Notebook Computers

- Tablet PCs

# Ordering Information

| Part Number | Operating Temperature Range | Package                                                      | Packing Method               |

|-------------|-----------------------------|--------------------------------------------------------------|------------------------------|

| FAB2200UCX  | -40 to +85°C                | 25-Bump, 0.4mm Pitch, Wafer-Level Chip-Scale Package (WLCSP) | 3000 Units on<br>Tape & Reel |

# **Typical Application Circuit**

Figure 1. Typical Application Circuit

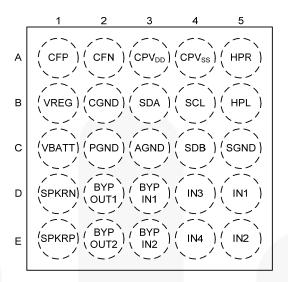

# **Pin Configuration**

Figure 2. Top-View (Bump-Side Down)

# **Pin Definitions**

| WLCSP | Name              | Description                                                               | Type          |

|-------|-------------------|---------------------------------------------------------------------------|---------------|

| C1    | VBATT             | Power supply for speaker amplifier                                        | Power         |

| B2    | PGND              | Charge pump ground                                                        | Power         |

| C2    | PGND              | Power ground                                                              | Power         |

| C3    | AGND              | Analog ground                                                             | Power         |

| B1    | VREG              | Charge pump regulator – do not connect to an external power supply        | Power         |

| A3    | $CPV_{DD}$        | Charge pump output – positive power supply for headphone amplifier        | Power         |

| A4    | CPV <sub>SS</sub> | Charge pump output – negative mirror of CPV <sub>DD</sub>                 | Power         |

| A1    | CFP               | Charge pump flying capacitor positive terminal                            | Power         |

| A2    | CFN               | Charge pump flying capacitor negative terminal                            | Power         |

| D5    | IN1               | Line level audio input                                                    | Input         |

| E5    | IN2               | Line level audio input                                                    | Input         |

| D4    | IN3               | Line level audio input                                                    | Input         |

| E4    | IN4               | Line level audio input                                                    | Input         |

| B5    | HPL               | Left headphone output                                                     | Output        |

| A5    | HPR               | Right headphone output                                                    | Output        |

| C5    | SGND              | Sense ground – connect to AGND close to shield terminal of headphone jack | Input         |

| E1    | SPKRP             | Positive speaker output                                                   | Output        |

| D1    | SPKRN             | Negative speaker output                                                   | Output        |

| D3    | BYPIN1            | Analog bypass switch input                                                | Input         |

| E3    | BYPIN2            | Analog bypass switch input                                                | Input         |

| D2    | BYPOUT1           | Analog bypass switch output                                               | Output        |

| E2    | BYPOUT2           | Analog bypass switch output                                               | Output        |

| C4    | SDB               | Shutdown control                                                          | Input         |

| B4    | SCL               | I <sup>2</sup> C clock input                                              | Input         |

| В3    | SDA               | I <sup>2</sup> C data I/O                                                 | Bi-directiona |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The Absolute Maximum Ratings are stress ratings only. All voltages are referenced to GND.

| Symbol          | Parameter                                              | Min.                   | Max.                   | Unit |

|-----------------|--------------------------------------------------------|------------------------|------------------------|------|

| $V_{BATT}$      | Voltage on VBATT Pin                                   | -0.3                   | 6.0                    | V    |

| V <sub>IN</sub> | Voltage on IN1, IN2, IN3, IN4, HPL, HPR Pins           | CPV <sub>SS</sub> -0.3 | CPV <sub>DD</sub> +0.3 | V    |

| $V_{SGND}$      | Voltage on SGND Pin                                    | -0.3                   | 0.3                    | V    |

| Vs              | Voltage on SDA, SCL, SDB Pins                          | -0.3                   | V <sub>BATT</sub> +0.3 | V    |

| $V_{SP}$        | Voltage on SPKRP, SPKRN Pins                           | -0.3                   | V <sub>BATT</sub> +0.3 | V    |

| $V_{BYP}$       | Voltage on BYPIN1, BYPIN2, BYPOUT1, BYPOUT2 Pins       | -0.3                   | V <sub>BATT</sub> +0.3 | V    |

|                 | Duration of SPKRP, SPKRN Short Circuit to GND or VBATT |                        | Continuous             |      |

|                 | Duration of Short Circuit Between SPKRP and SPKRN      |                        | Continuous             |      |

|                 | Duration of HPL, HPR Short Circuit to GND              |                        | Continuous             |      |

# **Reliability Information**

| Symbol           | Parameter                                                             | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------------------------------------------------|------|------|------|------|

| $T_J$            | Junction Temperature                                                  |      |      | +150 | °C   |

| T <sub>STG</sub> | Storage Temperature Range                                             | -65  |      | +150 | °C   |

| TL               | Peak Reflow Temperature                                               |      |      | +300 | °C   |

| $\theta_{JA}$    | Thermal Resistance, JEDEC Standard, Multilayer Test Boards, Still Air |      | 60   |      | °C/W |

| TSD              | Thermal Shutdown Threshold                                            |      | +150 |      | °C   |

| T <sub>HYS</sub> | Thermal Shutdown Hysteresis                                           |      | +35  |      | °C   |

# **ESD Protection**

| HBM Human Body Model (HBM) |                            | Condition                                                                                                       | Min. | Unit |

|----------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|------|------|

|                            |                            | JESD22-A114-B Level 2,<br>EC61340-3-1: 2002 Level 2,<br>ESD-STM5.1-2001 Level 2,<br>MIL-STD-883E 3015.7 Level 2 | 3    | kV   |

| CDM                        | Charged Device Model (CDM) | JESD22-C101-C Level III,<br>IEC61340-3-3 Level C4,<br>ESD-STM5.3.1-1999 Level C4                                | 2    | kV   |

#### Notes:

- 1. Device-use-level ESD tests are conducted at the connector pins.

- External ESD suppressor ASIP protects the amplifier outputs. Suppressor is between amplifier and connector; 15Ω serial resistance + 5nF capacitor and Zener diodes (14V breakdown voltage) connected to the ground. In addition, there is a ferrite bead in series between the suppressor and the connector.

- 3. The air discharge test can be ignored if the contact discharge test range is increased to the same voltages as air discharge (contact discharge is more stable and repeatable test than air discharge).

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol         | Parameter                   | Min. | Max. | Unit |

|----------------|-----------------------------|------|------|------|

| T <sub>A</sub> | Operating Temperature Range | -40  | +85  | °C   |

| $V_{BATT}$     | Supply Voltage Range        | 2.80 | 5.25 | V    |

# **Electrical Characteristics**

Unless otherwise noted: HPA uses stereo single-ended inputs, SPA uses differential input, unused inputs AC are grounded,  $f_{IN}$  = 1KHz, AGC off, PGAINxx = 0dB, HPxVOL = 0dB, PRESENTGAIN = 6dB, ERC = 1, SSMT = 000, SHDNB = 1, SDB = 1.8V, SDA and SCL pull-up voltage = 1.8V,  $Z_{SPK}$  = 8 $\Omega$ +68 $\mu$ H,  $R_{HP}$  = 32 $\Omega$ , speaker amplifier and headphone amplifier on. Typical values are at  $V_{BATT}$  = 3.7V,  $T_A$  = 25°C. Minimum and maximum values are at  $V_{BATT}$  = 2.8V to 5.25V,  $T_A$  = -40°C to 85°C.

| Symbol           | Parameter                                                  | Condition                                                                                             | ons                    | Min. | Тур.  | Max. | Unit        |

|------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------|------|-------|------|-------------|

|                  |                                                            | Headphone Amplifier<br>Speaker Amplifier Dis<br>DIFFIN43=1                                            |                        |      | 3.5   |      |             |

| I <sub>DD</sub>  | Quiescent Supply Current (Z <sub>SPK</sub> = Open)         | Headphone Amplifier<br>Speaker Amplifier En<br>DIFFIN21=1                                             |                        |      | 4.7   |      | mA          |

|                  |                                                            | Headphone and Spea                                                                                    | aker Amplifiers        |      | 6.2   |      |             |

|                  | Chutalaum Cumant                                           | SHDNB = 0, SDB = 1                                                                                    | .8V                    |      | 2.2   |      |             |

| I <sub>SD</sub>  | Shutdown Current                                           | SHDNB = 1, SDB = 0                                                                                    | GND                    |      | 2.2   |      | μA          |

| t <sub>ON</sub>  | Turn-On Time                                               | Time from Shutdown and Headphone Ope Ramps Disabled                                                   |                        | 1.25 |       | ms   |             |

| -                | L. (D. )                                                   | PGAINxx = 0dB                                                                                         |                        |      | 21.0  |      | 140         |

| R <sub>IN</sub>  | Input Resistance                                           | PGAINxx = 12dB                                                                                        |                        |      | 8.5   |      | ΚΩ          |

|                  | Maximum Input Signal Swing                                 | PGAINxx = 0dB                                                                                         |                        |      | 2.300 |      |             |

|                  | (V <sub>BATT</sub> = 2.8V to 5.25V,<br>Single-Ended Input) | PGAINxx = 12dB                                                                                        |                        |      | 0.575 |      | $V_{pk-pk}$ |

| Analog By        | pass Switch                                                |                                                                                                       |                        |      |       |      |             |

| R <sub>ON</sub>  | On Resistance                                              | I <sub>BYPOUTx</sub> = 20mA,<br>BYPx = 0V and<br>V <sub>BATT</sub> , BYPEN = 1                        | T <sub>A</sub> = 25°C  |      |       | 1    | Ω           |

| THD              | Total Harmonic Distortion                                  | $V_{DIF} = 2V_{PP}, V_{CM} = V_{BATT}/2, f = 1kHz, BYPEN = 1,$ Series Resistan 10 $\Omega$ per Switch |                        |      | 0.05  | 0.25 | %           |

|                  |                                                            | Load = $8\Omega$                                                                                      | No Series<br>Resistors |      | 0.10  |      |             |

| l <sub>OFF</sub> | Off Isolation                                              | BYPEN = 0, 10KHz 1<br>Wave Applied Across<br>BYPOUT2, BYPIN1 a<br>GND = $50\Omega$                    |                        | 94   |       | dB   |             |

Continued on the following page...

# **Electrical Characteristics** (Continued)

Unless otherwise noted: HPA uses stereo single-ended inputs, SPA uses differential input, unused inputs AC are grounded,  $f_{IN}$  = 1KHz, AGC off, PGAINxx = 0dB, HPxVOL = 0dB, PRESENTGAIN = 6dB, ERC = 1, SSMT = 000, SHDNB = 1, SDB = 1.8V, SDA and SCL pull-up voltage = 1.8V,  $Z_{SPK}$  = 8 $\Omega$ +68 $\mu$ H,  $R_{HP}$  = 32 $\Omega$ , speaker amplifier and headphone amplifier on. Typical values are at  $V_{BATT}$  = 3.7V,  $T_A$  = 25°C. Minimum and maximum values are at  $V_{BATT}$  = 2.80V to 5.25V,  $T_A$  = -40°C to 85°C.

| Symbol           | Parameter                               | Conditions                                                                         |                                          |     | Тур.  | Max.  | Unit              |

|------------------|-----------------------------------------|------------------------------------------------------------------------------------|------------------------------------------|-----|-------|-------|-------------------|

| Speaker A        | mplifier                                |                                                                                    |                                          |     |       |       | •                 |

|                  | Outrot Offert Veltere                   | PRESENTGAIN = Mute                                                                 |                                          |     | ±0.5  |       | \/                |

| $V_{OS}$         | Output Offset Voltage                   | PRESENTGAIN = 6dB                                                                  |                                          |     | ±2.5  |       | mV                |

|                  |                                         | Peak Voltage,                                                                      | Into Shutdown                            |     | -70   |       |                   |

| K <sub>CP</sub>  | Click-and-Pop Level                     | A-Weighted,<br>32 Samples per Second,<br>PRESENTGAIN = Mute,<br>Inputs AC Grounded | Out of Shutdown                          |     | -70   |       | dBV               |

|                  |                                         |                                                                                    | V <sub>BATT</sub> = 2.8V to 5.25V        |     | 74    |       |                   |

| PSRR             | Power-Supply Rejection Ratio            | Inputs AC Grounded                                                                 | f = 217Hz,<br>100mV <sub>PP</sub> Ripple |     | 77    |       | dB                |

|                  |                                         |                                                                                    | f = 1kHz,<br>100mV <sub>PP</sub> Ripple  |     | 75    |       |                   |

|                  |                                         | THD+N < 1%, ERC Disab<br>V <sub>BATT</sub> = 4.2V                                  | oled, SSMT = 100,                        |     | 970   |       |                   |

|                  |                                         | THD+N < 10%, ERC Disabled, SSMT = 100, V <sub>BATT</sub> = 4.2V                    |                                          |     | 1200  |       |                   |

| P <sub>out</sub> | Output Power                            | THD+N < 10%, ERC Disabled,<br>SSMT = 100, $V_{BATT}$ = 3.7V                        |                                          |     | 930   |       | mW                |

|                  |                                         | THD+N < 10%, ERC Enabled, SSMT = 000, V <sub>BATT</sub> = 3.7V                     |                                          |     | 945   |       |                   |

|                  |                                         | THD+N < 1%, ERC                                                                    | V <sub>BATT</sub> = 4.2V                 | 930 | 975   |       |                   |

|                  |                                         | Enabled, SSMT = 000                                                                | V <sub>BATT</sub> = 3.7V                 |     | 750   |       |                   |

| THD+N            | Total Harmonic<br>Distortion Plus Noise | P <sub>OUT</sub> = 350mW                                                           |                                          |     | 0.030 | 0.075 | %                 |

|                  |                                         | A-Weighted, P <sub>OUT</sub> =                                                     | DIFFINxx = 0<br>(Single-Ended)           |     | 97    | y     |                   |

| CND              | Circulto Naisa Datia                    | 720mW, Headphone<br>Amplifiers Off                                                 | DIFFINxx = 1<br>(Differential)           | 90  | 97    |       | 40                |

| SNR              | Signal-to-Noise Ratio                   | A-Weighted, P <sub>OUT</sub> =                                                     | DIFFINxx = 0<br>(Single-Ended)           |     | 97    |       | dB                |

|                  |                                         | 720mW, Headphone<br>Amplifiers On                                                  |                                          |     | 97    |       |                   |

| Vn               | Output Noise                            | A-Weighted, Headphone Amps Off,<br>DIFFINxx = 0, Inputs AC Grounded                |                                          |     | 32    |       | μV <sub>RMS</sub> |

|                  | Output Frequency                        | Spread Spectrum, SSMT                                                              | = 000                                    |     | 330   |       | KHz               |

|                  | Output Frequency                        | Fixed Frequency, SSMT = 100                                                        |                                          |     | 330   |       | KΠZ               |

| I <sub>OUT</sub> | Output Current Limit                    |                                                                                    |                                          |     | 1.3   |       | Α                 |

|                  | Efficiency                              | P <sub>OUT</sub> = 720mW, f = 1kHz                                                 |                                          |     | 90    |       | %                 |

|                  | Mute Attenuation                        |                                                                                    |                                          |     | 100   |       | dB                |

Continued on the following page...

# **Electrical Characteristics** (Continued)

Unless otherwise noted: HPA uses stereo single-ended inputs, SPA uses differential input, unused inputs AC are grounded,  $f_{IN}$  = 1KHz, AGC off, PGAINxx = 0dB, HPxVOL = 0dB, PRESENTGAIN = 6dB, ERC = 1, SSMT = 000, SHDNB = 1, SDB = 1.8V, SDA and SCL pull-up voltage = 1.8V,  $Z_{SPK}$  = 8 $\Omega$ +68 $\mu$ H,  $R_{HP}$  = 32 $\Omega$ , speaker amplifier and headphone amplifier on. Typical values are at  $V_{BATT}$  = 3.7V,  $T_A$  = 25°C. Minimum and maximum values are at  $V_{BATT}$  = 2.80V to 5.25V,  $T_A$  = -40°C to 85°C.

| Symbol           | Parameter                           | Conditions                                                               |                                                        |    | Тур.  | Max.  | Unit          |

|------------------|-------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------|----|-------|-------|---------------|

| Headpho          | ne Amplifiers                       |                                                                          |                                                        |    | _     |       |               |

|                  |                                     |                                                                          | $P_{OUT} = 2x50\mu W$<br>into 32Ω                      |    | 4.4   |       |               |

| $I_{VBATT}$      | Supply Current                      | IN1 and IN2 On,<br>IN3 and IN4 Off, DIFFIN43=1,<br>Speaker Amplifier Off | $P_{OUT}$ = 2x250μW into 32Ω                           |    | 5.8   |       | mA            |

|                  |                                     | opeaker Ampliner on                                                      | $P_{OUT} = 2x500\mu W$<br>into 32Ω                     |    | 6.8   |       |               |

| Vos              | Output Offset Voltage               | HPxVOL = Mute                                                            |                                                        |    | ±0.15 |       | mV            |

| K <sub>CP</sub>  | Click-and-Pop Level                 | Peak Voltage, A-Weighted,<br>32 Samples per Second,                      | Into Shutdown                                          |    | -70   |       | dBV           |

| J. /             |                                     | HPxVOL = Mute,<br>Inputs AC Grounded                                     | Out of Shutdown                                        |    | -70   |       |               |

|                  |                                     |                                                                          | $V_{BATT} = 2.8V \text{ to}$ 5.25V                     |    | 95    |       |               |

| PSRR             | Power-Supply Rejection Ratio        | Inputs AC Grounded                                                       | $f = 217Hz,$ $V_{RIPPLE} =$ $200mV_{PP}$               |    | 95    |       | dB            |

|                  |                                     |                                                                          | f = 1KHz, V <sub>RIPPLE</sub><br>= 200mV <sub>PP</sub> |    | 95    |       |               |

|                  | Output Power                        | $R_{HP} = 16\Omega$                                                      | $R_{HP} = 16\Omega$                                    |    | 39    |       |               |

| P <sub>out</sub> |                                     | THD+N < 1%                                                               | $R_{HP} = 32\Omega$<br>$HPxV_{OL} = 4dB$               | 27 | 27 31 | mW    |               |

|                  |                                     | THD+N < 10%                                                              | $R_{HP} = 32\Omega$<br>$HPxV_{OL} = 6dB$               |    | 41    |       |               |

| THD+N            | Total Harmonic                      | $R_{HP} = 32\Omega$ , $P_{OUT} = 20$ mW                                  |                                                        |    | 0.010 | 0.075 | %             |

| וחט+וז           | Distortion Plus Noise               | $R_{HP} = 16\Omega$ , $P_{OUT} = 10$ mW                                  |                                                        |    | 0.020 |       | 70            |

|                  |                                     | A-Weighted, P <sub>OUT</sub> = 32mW,<br>Speaker Amplifier Off            | DIFFINxx = 0<br>(Single-Ended)                         | 95 | 100   |       |               |

| SNR              | Signal-to-Noise Ratio               | HPxVOL = 4dB                                                             | DIFFINxx = 1<br>(Differential)                         |    | 100   | 4/    | dB            |

| SINIX            | Signal-to-Noise Ratio               | A-Weighted, P <sub>OUT</sub> = 32mW,<br>Speaker Amplifier On             | DIFFINxx = 0<br>(Single-Ended)                         |    | 100   |       | uв            |

|                  |                                     | HPxVOL = 4dB                                                             | DIFFINxx = 1<br>(Differential)                         |    | 103   |       |               |

|                  | Output Noise                        | A-Weighted, Speaker Amplifier                                            | Off, DIFFINxx = 0                                      |    | 6.5   |       | $\mu V_{RMS}$ |

| $C_L$            | Capacitive Drive                    |                                                                          |                                                        |    | 100   |       | pF            |

| $X_{TALK}$       | Crosstalk                           | HPL to HPR, HPR to HPL, P <sub>0</sub> = 15mW                            |                                                        |    | -85   |       | dB            |

| $f_{P}$          | Charge-Pump Frequency               | 1                                                                        |                                                        |    | 1.3   |       | MHz           |

| A <sub>V</sub>   | Headphone Gain<br>Accuracy          | Across All Gain Stages                                                   |                                                        |    | ±0.4  |       | dB            |

|                  | Channel-to-Channel<br>Gain Tracking | HPL to HPR, HPxVOL = 0dB                                                 |                                                        |    | ±0.3  |       | %             |

|                  | Channel-to-Channel<br>Gain Tracking | HPL to HPR Across Entire Pre<br>Volume Range                             | -Amplifier and                                         |    | ±1    |       | %             |

| ·                | Mute Attenuation                    |                                                                          |                                                        |    | 100   |       | dB            |

# I<sup>2</sup>C DC Electrical Characteristics

Unless otherwise noted,  $V_{BATT}$  = 2.80V to 5.25V and  $T_A$  = -40°C to 85°C.

| Comple of       | Downwater                   | Canditions                                            | Fast Mode (400kHz) |      |    |  |

|-----------------|-----------------------------|-------------------------------------------------------|--------------------|------|----|--|

| Symbol          | Symbol Parameter Conditions | Min.                                                  | Max.               | Unit |    |  |

| V <sub>IL</sub> | Low-Level Input Voltage     | V <sub>BATT</sub> 2.80V to 5.25V                      | -0.3               | 0.6  | V  |  |

| $V_{IH}$        | High-Level Input Voltage    | V <sub>BATT</sub> 2.80V to 5.25V                      | 1.3                |      | V  |  |

| V <sub>OL</sub> | Low-level Output Voltage    | at 3mA Sink Current<br>(Open-Drain or Open-Collector) | 0                  | 0.4  | ٧  |  |

| I <sub>IH</sub> | High-Level Input Current    | Each I/O Pin, Input Voltage = V <sub>BATT</sub>       | -1                 | 1    | μA |  |

| I <sub>IL</sub> | Low-Level Input Current     | Each I/O Pin, Input Voltage = 0V                      | -1                 | 1    | μA |  |

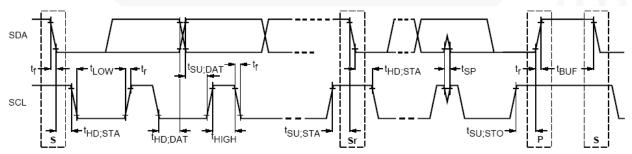

# I<sup>2</sup>C AC Electrical Characteristics

Unless otherwise noted,  $V_{BATT}$  = 2.80V to 5.25V and  $T_A$  = -40°C to 85°C.

| Comple al           | Devenueten                                                        | F                    | Fast Mode |      |  |  |

|---------------------|-------------------------------------------------------------------|----------------------|-----------|------|--|--|

| Symbol              | Parameter                                                         | Min.                 | Max.      | Unit |  |  |

| f <sub>SCL</sub>    | SCL Clock Frequency                                               | 0                    | 400       | kHz  |  |  |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition                              | 0.6                  |           | μs   |  |  |

| t <sub>LOW</sub>    | LOW Period of SCL Clock                                           | 1.3                  |           | μs   |  |  |

| t <sub>HIGH</sub>   | HIGH Period of SCL Clock                                          | 0.6                  |           | μs   |  |  |

| t <sub>SU;STA</sub> | Set-up Time for Repeated START Condition                          | 0.6                  |           | μs   |  |  |

| t <sub>HD;DAT</sub> | Data Hold Time                                                    | 0                    | 0.9       | μs   |  |  |

| t <sub>SU;DAT</sub> | Data Set-up Time <sup>(4)</sup>                                   | 100                  |           | ns   |  |  |

| t <sub>r</sub>      | Rise Time of SDA and SCL Signals <sup>(5)</sup>                   | 20+0.1C <sub>b</sub> | 300       | ns   |  |  |

| t <sub>f</sub>      | Fall Time of SDA and SCL Signals <sup>(5)</sup>                   | 20+0.1C <sub>b</sub> | 300       | ns   |  |  |

| t <sub>SU;STO</sub> | Set-up Time for STOP Condition                                    | 0.6                  |           | μs   |  |  |

| t <sub>BUF</sub>    | Bus Free Time between STOP and START Conditions                   | 1.3                  |           | μs   |  |  |

| t <sub>SP</sub>     | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0                    | 50        | ns   |  |  |

# Notes:

- 4. A fast-mode  $I^2C$ -Bus<sup>®</sup> device can be used in a standard-mode system, but the requirement  $t_{SU;DAT} \ge 250$ ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{r_max} + t_{SU;DAT} = 1000 + 250 = 1250$ ns (according to the standard-mode  $I^2C$  bus specification) before the SCL line is released.

- 5. C<sub>b</sub> equals the total capacitance of one bus line in pf. If mixed with high-speed mode devices, faster fall times are allowed according to the I<sup>2</sup>C specification.

Figure 3. Definition of Timing for Full-Speed Mode Devices on the I<sup>2</sup>C-Bus<sup>®</sup>

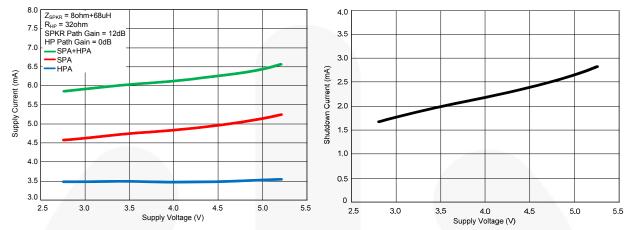

# **Typical Performance Characteristics**

# **System**

Figure 4. Quiescent Supply Current vs. Supply Voltage

Figure 5. Hardware and Software Shutdown Current vs. Supply Voltage

# **Speaker Amplifier**

100

90

80

50

40

30

20

10

0

**EFFICIENCY** (%) 60 V<sub>BATT</sub> = 3.7V

Z<sub>SPKR</sub>= 8ohm+68µH f = 1KHz

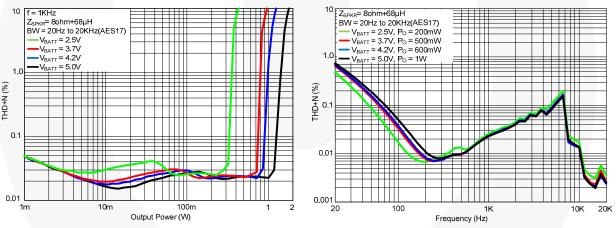

Figure 6. THD+N vs. Output Power

0.6

Output Power (W)

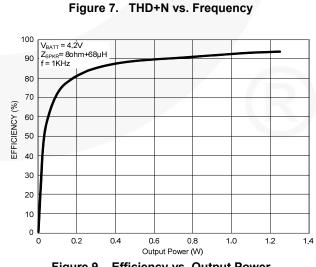

Figure 8. Efficiency vs. Output Power Figure 9. Efficiency vs. Output Power

1.0

# **Typical Performance Characteristics**

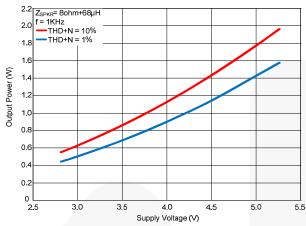

Figure 10. Output Power vs. Supply Voltage

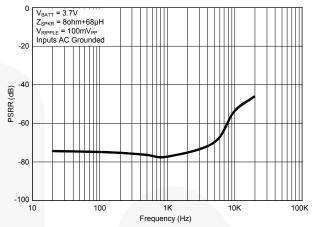

Figure 11. PSRR vs. Frequency

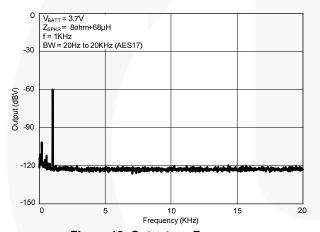

Figure 12. Output vs. Frequency

# **Headphone Amplifier**

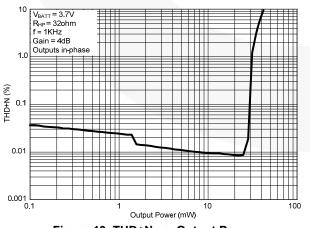

10 V<sub>BATT</sub> = 3.7V R<sub>HP</sub> = 160hm f = 1KHz Gain = 4dB Outputs in-phase Outputs in-phase Outputs in-phase Outputs in-phase Output Power (mW)

Figure 13. THD+N vs. Output Power

Figure 14. THD+N vs. Output Power

#### **Typical Performance Characteristics** 10 V<sub>BATT</sub> = 3.7V R<sub>HP</sub>= 320hm $V_{BATT} = 3.7V$ $R_{HP} = 160$ hm Gain = 4dB P<sub>0</sub> = 1mW P<sub>0</sub> = 20mW Gain = 4dB Po = 1mW $P_0 = 30 \text{mW}$ 1.0 THD+N (%) 0.1 0.01 0.01 0.001 0.001 10 Frequency (Hz) Frequency (Hz) Figure 15. THD+N vs. Frequency Figure 16. THD+N vs. Frequency $V_{BATT} = 3.7V$ Gain = 4dB $V_{BATT} = 3.7V$ $R_{HP} = 32ohm$ f=1KHz 120 V<sub>RIPPLE</sub> = 200mV<sub>PP</sub> Inputs AC Grounded R<sub>HP</sub>= 16ohm R<sub>HP</sub>= 32ohm -20 Output Power = PH (m) 100 -40 Dissipation (i (g PSRR -60 -80 40 20 -100 -120 10 20 40 50 60 30 10 100 10K Output Power (mW) Frequency (Hz) Figure 17. Power Dissipation vs. Total Output Power Figure 18. PSRR vs. Frequency $V_{BATT} = 3.7V$ $R_{HP} = 32$ ohm f = 1KHz $V_{BATT} = 3.7V$ $R_{HP} = 320$ hm $P_O = 15$ mW BW = 20Hz to 22KHz f = 1KHz -20 -60 Crosstalk (dB) Output (dBV) -90 -120 -80 -150 -100 L 10 20 0 15 100 1K 10K 100K 10 Frequency (KHz) Frequency (Hz) Figure 20. Output vs. Frequency Figure 19. Crosstalk vs. Frequency

# **Functional Description**

#### **Shutdown Mode**

When SHDNB bit is set to 0 or the SDB pin is grounded, the FAB2200 enters low-power Shutdown Mode.

While SHDNB=0 and SDB is HIGH, I<sup>2</sup>C communication is available. I<sup>2</sup>C values are preserved. Values are not reset on exiting Shutdown Mode.

If the SDB pin is grounded, I<sup>2</sup>C communication is unavailable. I<sup>2</sup>C values are not preserved. Values are reset to default values after SDB goes HIGH.

#### **Inputs During Shutdown**

To achieve low supply current during shutdown, all inputs must be at DC levels (except the BYPASS pins). Audio inputs must be AC grounded.  $V_{BATT}$  must be within recommended operating conditions.  $I^2C$  pins must be grounded or pulled HIGH with no toggling. If AC is presented to the inputs during shutdown, standby current may increase slightly, but there are no other negative effects.

#### **Thermal Shutdown**

If the junction temperature of the device exceeds the thermal shutdown threshold (see *Electrical Characteristics table*), the device protects itself by shutting down. The device remains shut down until the junction temperature falls below the thermal shutdown hysteresis.

The I<sup>2</sup>C port remains functional and the OVRTEMP bit is set to O. This bit remains set until it is read. If the device is still in thermal shutdown when the bit is read, it remains set to 1. Otherwise, the bit is cleared to 0.

# **Over-Current Shutdown**

If the output current limit of either amplifier is exceeded (see the Electrical Characteristics table), the amplifier in question shuts down for approximately one second. After one second, the amplifier is re-enabled. If the amplifier output current exceeds the limit again, the cycle repeats.

During current-limit shutdown, the  $I^2C$  port remains functional. If the current-limit shutdown was caused by the speaker amplifier, the OVRCURSP bit is set to 1. This bit remains set until it is read. If the speaker amplifier is still in current-limit shutdown when the bit is read, it remains set to 1. Otherwise, the bit is cleared to 0.

# Signal Path

The input channels have a pre-amplifier stage that can be set from 0dB to 21dB of gain. The headphone amplifiers have separate volume controls that range from -53dB to 6dB. The speaker amplifier has a volume control that ranges from -25dB to 6dB. In addition, the speaker amplifier has a fixed gain of 6dB.

A variety of combinations of these signals can be routed to the headphone amplifiers or the speaker amplifier (see Table 1). For example, to connect the left headphone amplifier channel to IN3 and IN1, set the SELHPL3 and SELHPL1 bits to 1. SELHPL4 and SELHPL2 should be set to 0.

The DIFFIN43 and DIFFIN21 bits configure the inputs as differential pairs. When configured as differential, the even-numbered selection bit should be 1 and the odd-numbered selection bit should be 0. For example, if channels 4 and 3 are a differential pair that should be connected to the speaker amplifier, DIFFIN43 and SELSPA4 should be set to 1. SELSPA3, SELSPA2, and SELSPA1 should be set to 0.

Amplifier channels that have no inputs selected should be muted (HPxVOL = 00000 or STARTGAIN = 000000). If an amplifier channel has no input selection bits set to 1, the amplifier channel is turned off. When the speaker amplifier is turned off, the SPKRP and SPKRN outputs stop switching.

Unused audio input pins must be AC grounded.

An integrated Dual-Pole Single-Throw (DPST) analog bypass switch can be used to route system audio signals. For example, baseband audio can be routed to the speaker by connecting the BYPOUTx pins to the SPKRx pins. Baseband audio outputs would then be connected to the BYPINx pins through optional external resistors if the baseband device expects a higher impedance than the existing speaker.

Gain for the headphone amplifier signal path is defined by PGAINxx + HPxVOL.

Gain for the speaker amplifier signal path is defined by PGAINxx + PRESENTGAIN + 6dB.

Internal signal amplitude should not exceed  $2.3V_{PP}$ . Extra caution should be taken when mixing signals. For example, if IN1 is mixed with IN3, the maximum peak to peak amplitude of IN1 plus the maximum peak to peak amplitude of IN3 should not exceed  $2.3V_{PP}$ .

**Table 1. Input Channel Selection**

| DIFFIN43 | DIFFIN21 | SELxxx4 | SELxxx3 | SELxxx2 | SELxxx1 | xxx Amplifier Input       |

|----------|----------|---------|---------|---------|---------|---------------------------|

| Х        | Х        | 0       | 0       | 0       | 0       | xxx Amplifier Channel Off |

| 0        | 0        | 0       | 0       | 0       | 1       | IN1                       |

| 0        | 0        | 0       | 0       | 1       | 0       | IN2                       |

| 0        | 0        | 0       | 0       | 1       | 1       | IN2 + IN1                 |

| 0        | 0        | 0       | 1       | 0       | 0       | IN3                       |

| 0        | 0        | 0       | 1       | 0       | 1       | IN3 + IN1                 |

| 0        | 0        | 0       | 1       | 1       | 0       | IN3 + IN2                 |

| 0        | 0        | 0       | 1       | 1       | 1       | IN3 + IN2 + IN1           |

| 0        | 0        | 1       | 0       | 0       | 0       | IN4                       |

| 0        | 0        | 1       | 0       | 0       | 1       | IN4 + IN1                 |

| 0        | 0        | 1       | 0       | 1       | 0       | IN4 + IN2                 |

|          |          |         |         | 1       | 1       |                           |

| 0        | 0        | 1       | 0       |         | · ·     | IN4 + IN2 + IN1           |

| 0        | 0        | 1       | 1       | 0       | 0       | IN4 + IN3                 |

| 0        | 0        | 1       | 1       | 0       | 1       | IN4 + IN3 + IN1           |

| 0        | 0        | 1       | 1       | 1       | 0       | IN4 + IN3 + IN2           |

| 0        | 0        | 1       | 1       | 1       | 1       | IN4 + IN3 + IN2 + IN1     |

| 0        | 1        | 0       | 0       | 0       | 0       | xxx Amplifier Channel Off |

| 0        | 1        | 0       | 0       | 0       | 1       | Not Supported             |

| 0        | 1        | 0       | 0       | 1       | 0       | IN2 - IN1                 |

| 0        | 1        | 0       | 0       | 1       | 1       | Not Supported             |

| 0        | 1        | 0       | 1       | 0       | 0       | IN3                       |

| 0        | 1        | 0       | 1       | 0       | 1       | Not Supported             |

| 0        | 1        | 0       | 1       | 1       | 0       | IN3 + (IN2 - IN1)         |

|          | -        |         |         |         | -       | Not Supported             |

| 0        | 1        | 0       | 1       | 1       | 1       |                           |

| 0        | 1        | 1       | 0       | 0       | 0       | IN4                       |

| 0        | 1        | 1       | 0       | 0       | 1       | Not Supported             |

| 0        | 1        | 1       | 0       | 1       | 0       | IN4 + (IN2 - IN1)         |

| 0        | 1        | 1       | 0       | 1       | 1       | Not Supported             |

| 0        | 1        | 1       | 1       | 0       | 0       | IN4 + IN3                 |

| 0        | 1        | 1       | 1       | 0       | 1       | Not Supported             |

| 0        | 1        | 1       | 1       | 1       | 0       | IN4 + IN3 + (IN2 - IN1)   |

| 0        | 1        | 1       | 1       | 1       | 1       | Not Supported             |

| 1        | 0        | 0       | 0       | 0       | 0       | xxx Amplifier Channel Off |

| 1        | 0        | 0       | 0       | 0       | 1       | IN1                       |

| 1        | 0        | 0       | 0       | 1       | 0       | IN2                       |

| 1        | 0        | 0       | 0       | 1       | 1       | IN2 + IN1                 |

|          |          |         |         |         |         |                           |

| 1        | 0        | 0       | 1       | 0       | 0       | Not Supported             |

| 1        | 0        | 0       | 1       | 0       | 1       | Not Supported             |

| 1        | 0        | 0       | 1       | 1       | 0       | Not Supported             |

| 1        | 0        | 0       | 1       | 1       | 1       | Not Supported             |

| 1        | 0        | 1       | 0       | 0       | 0       | IN4 - IN3                 |

| 1        | 0        | 1       | 0       | 0       | 1       | (IN4 - IN3) + IN1         |

| 1        | 0        | 1       | 0       | 1       | 0       | (IN4 - IN3) + IN2         |

| 1        | 0        | 1       | 0       | 1       | 1       | (IN4 - IN3) + IN2 + IN1   |

| 1        | 0        | 1       | 1       | 0       | 0       | Not Supported             |

| 1        | 0        | 1       | 1       | 0       | 1       | Not Supported             |

| 1        | 0        | 1       | 1       | 1       | 0       | Not Supported             |

| 1        | 0        | 1       | 1       | 1       | 1       | Not Supported             |

| 1        | 1        | 0       | 0       | 0       | 0       | xxx Amplifier Channel Off |

|          |          |         |         |         |         |                           |

| 1        | 1        | 0       | 0       | 0       | 1       | Not Supported             |

| 1        | 1        | 0       | 0       | 1       | 0       | IN2 - IN1                 |

| 1        | 1        | 0       | 0       | 1       | 1       | Not Supported             |

| 11       | 1        | 0       | 1       | 0       | 0       | Not Supported             |

| 1        | 1        | 0       | 1       | 0       | 1       | Not Supported             |

| 1        | 1        | 0       | 1       | 1       | 0       | Not Supported             |

| 1        | 1        | 0       | 1       | 1       | 1       | Not Supported             |

| 1        | 1        | 1       | 0       | 0       | 0       | IN4 - IN3                 |

| <br>1    | 1        | 1       | 0       | 0       | 1       | Not Supported             |

| <u> </u> | 1        | 1       | 0       | 1       | 0       | (IN4 - IN3) + (IN2 - IN1) |

| 1<br>1   | 1        | 1       | 0       | 1       | 1       | Not Supported             |

|          |          |         |         |         |         |                           |

| 1        | 1        | 1       | 1       | 0       | 0       | Not Supported             |

| 1        | 1        | 1       | 1       | 0       | 1       | Not Supported             |

| 1        | 1        | 1       | 1       | 1       | 0       | Not Supported             |

| 1        | 1        | 1       | 1       | 1       | 1       | Not Supported             |

# Class-G Headphone Amplifier with Capacitor Free Outputs

The FAB2200 includes a regulated charge pump that derives  $CPV_{DD}$  and  $CPV_{SS}$  (the headphone amplifier power supplies) from VBATT. When the headphone output amplitude is low, the  $CPV_{DD}$  is 1.3V and  $CPV_{SS}$  is -1.3V. When needed,  $CPV_{DD}$  and  $CPV_{SS}$  dynamically increase to 1.8V and -1.8V, respectively, to allow for higher output amplitudes. The combination of an efficient regulated charge pump and class-G operation allows low headphone amplifier power dissipation, resulting in longer battery run time.

The negative  $CPV_{SS}$  rail allows the headphone amplifier output to be centered at 0V and eliminates the need for output DC blocking capacitors.

The FAB2200 headphone outputs can be placed in High-Impedance Mode by setting the HIZx bits to 1 (see Table 2). This can be useful if the system's headphone jack is shared with other devices. For proper high-

impedance operation, the device must not be in Shutdown Mode. Voltages on HPL and HPR must not exceed ±1.8V.

Table 2. Headphone Amplifier Output Impedance, HIZx=1

| Output Impedance (Ω) | Frequency (KHz) |

|----------------------|-----------------|

| 11800                | 40              |

| 760                  | 6000            |

| 470                  | 13000           |

# Headphone Volume Control Ramp and Zero-Crossing Detection

The HPRAMP, HPRAMPSPEED, and HPZCD bits control the headphone amplifiers' volume controls when  $\mbox{HPxV}_{\mbox{OL}}$  is changed.

Table 3. Headphone Volume Change Behavior

|        | •     |                                                                                                                                                                                                                                                                        |

|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPRAMP | HPZCD | Behavior When HPxVOL Changes                                                                                                                                                                                                                                           |

| 0      | 0     | Volume changes immediately.                                                                                                                                                                                                                                            |

| 0      | 1     | For each channel, wait until a zero crossing occurs in the input before changing volume. If a zero crossing does not occur within HPRAMPSPEED, volume is forced to the new setting.                                                                                    |

| 1      | 0     | Volume is ramped to the new setting at a rate of HPRAMPSPEED per step.                                                                                                                                                                                                 |

| 1      | 1     | Volume is changed by one step when a zero crossing occurs. If a zero crossing does not occur within HPRAMPSPEED, a step is forced. Only the first zero crossing within HPRAMPSPEED triggers a volume change – volume does not change again until the next HPRAMPSPEED. |

Table 4. Headphone Volume Change Timing

| HPRAMPSPEED[1:0] | Ramp and ZCD Time Between Steps (ms) |

|------------------|--------------------------------------|

| 00               | 0.25                                 |

| 01               | 2.00                                 |

| 10               | 16.00                                |

| 11               | 128.00                               |

# Programmable Headphone Amplifier Noise Gate

The headphone noise gate automatically mutes the headphone amplifier when its input amplitudes are low to reduce noise during inactivity. This function is not recommended for music playback, but is effective for speech. The amplitude is measured after input preamplifiers and before the headphone amplifier volume controls. The headphone noise gate threshold level is set by the HPNGTHRESH register. The amplitudes of both channels must be less than the noise gate threshold for a time determined by the HPNGTIME register. When the noise gate mutes the amplifier, the HPNGTRIP bit is set to 1.

If either channel's input amplitude goes above the headphone noise gate threshold, both amplifiers are unmuted and the HPNGTRIP bit is set to 0. The amplifiers are returned to the former HPxVOL values.

If either channel is in High-Impedance Mode (HIZx=1), all inputs to that headphone should be deselected (SELHPxx=0) so the noise gate ignores the HIZ channel.

If the HPNGZRA bit is set to 0, the headphone noise gate attack (mute) function occurs immediately rather than waiting for zero-crossing detection or ramping. If the HPNGZRA bit is set to 1, the headphone noise gate attack function obeys headphone zero-crossing detection and ramp settings.

If the HPNGZRR bit is set to 0, the headphone noise gate release (un-mute) function occurs immediately rather than waiting for zero-crossing detection or ramping. If the HPNGZRR bit is set to 1, the headphone noise gate release (un-mute) function obeys headphone zero crossing detection and ramp settings.

Table 5. Headphone Noise Gate Threshold Voltage

| HPNGTHRESH<br>[2:0] | Noise Gate Threshold (mV <sub>pk</sub> ) |  |  |

|---------------------|------------------------------------------|--|--|

| 000                 | Headphone Noise Gate Disabled            |  |  |

| 001                 | 2.8                                      |  |  |

| 010                 | 5.7                                      |  |  |

| 011                 | 11.3                                     |  |  |

| 100                 | 22.6                                     |  |  |

| 101                 | 45.3                                     |  |  |

| 110                 | 90.5                                     |  |  |

| 111                 | 181.0                                    |  |  |

Table 7. Headphone Noise Gate Timing

| HPNGTIME [2:0] | Time (ms) |

|----------------|-----------|

| 000            | 10        |

| 001            | 20        |

| 010            | 40        |

| 011            | 80        |

| 100            | 160       |

| HPNGTIME [2:0] | Time (ms) |

|----------------|-----------|

| 101            | 320       |

| 110            | 640       |

| 111            | Reserved  |

Certain combinations of HPRAMP, HPZCD, HPNGZRA, and HPNGZRR are valid as shown in Table 8. Combinations not listed may produce unpredictable results (X = don't care).

Table 8. Valid Headphone Amplifier Ramp / Zero Crossing / Noise Gate Combinations

| HPRAMP | HPZCD | HPNGZRA | HPNGZRR |

|--------|-------|---------|---------|

| 0      | 0     | Х       | Х       |

| X      | Х     | 1       | 1       |

| 1      | Χ     | 1       | 0       |

# **Class-D Speaker Amplifier**

The class-D amplifier achieves greater than 90% efficiency.

Programmable spread spectrum and edge rate control minimize electromagnetic interference (EMI). Rise and fall times are limited to 20ns per transition at all power levels.

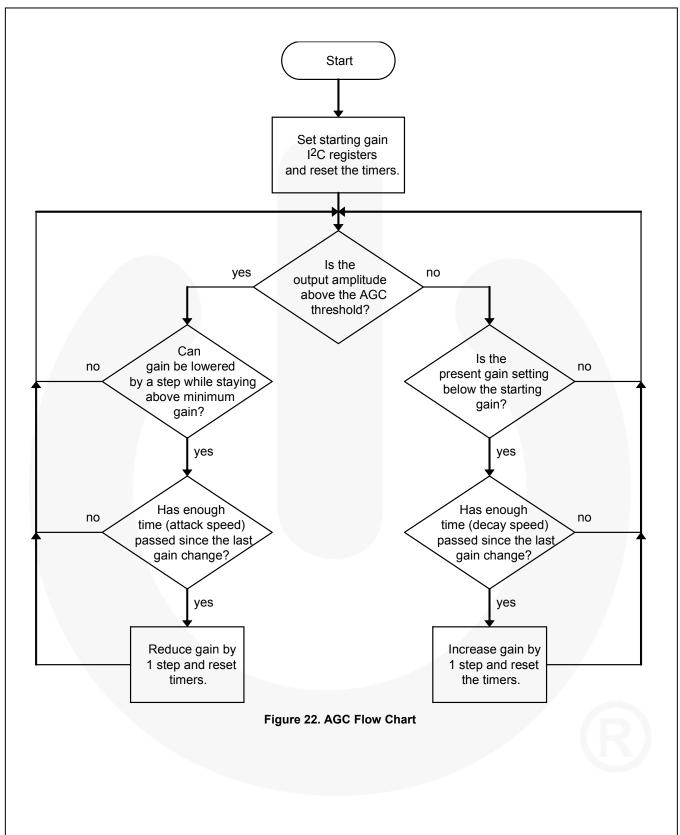

# Programmable Automatic Gain Control (AGC)

The speaker amplifier's AGC can be used to limit output amplitude and reduce clipping as supply voltage varies. The AGC allows high-volume settings while minimizing distortion and protecting the speaker element.

AGC works by comparing the threshold voltage against a proposed output amplitude (the signal's amplitude after all gain stages, before the PWM modulator). If the threshold is exceeded, gain is dynamically reduced until the output voltage level no longer exceeds the threshold or the minimum gain setting. When the output voltage level no longer exceeds the threshold, gain is slowly increased until either the output voltage level exceeds the threshold again or the starting gain is reached.

AGC settings should not be changed while the speaker amplifier is on. Before making changes to THMAX, THVBATT, AGCATTACK, AGCRELEASE, or AGCMIN; the speaker amplifier should be turned off by clearing all SELSPAn bits to 0 or clearing SHDNB to 0.

#### **AGC Threshold**

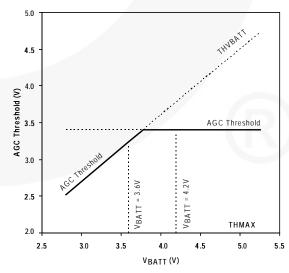

The AGC threshold can be thought of as a target for the maximum output amplitude. It is defined by the THMAX and THVBATT registers.

THMAX defines the maximum threshold value regardless of V<sub>BATT</sub> supply voltage. This is useful for protecting speakers from high amplitudes. Table 9 shows the THMAX threshold settings as well as the corresponding maximum RMS power (assuming a 1KHz sine wave into an  $8\Omega$  load).

Table 9. THMAX Threshold

| THMAX<br>[3:0] | Maximum<br>Output<br>Threshold<br>(V <sub>pk</sub> ) | Maximum Power with<br>Sine Wave and 8Ω<br>Load (mW) | THMAX<br>[3:0] | Maximum<br>Output<br>Threshold<br>(V <sub>pk</sub> ) | Maximum Power with Sine Wave and 8Ω Load (mW) |

|----------------|------------------------------------------------------|-----------------------------------------------------|----------------|------------------------------------------------------|-----------------------------------------------|

| 0000           | THMAX                                                | Threshold Disabled                                  | 1000           | 3.6                                                  | 810.0                                         |

| 0001           | 2.2                                                  | 302.5                                               | 1001           | 3.8                                                  | 902.5                                         |

| 0010           | 2.4                                                  | 360.0                                               | 1010           | 4.0                                                  | 1000.0                                        |

| 0011           | 2.6                                                  | 422.5                                               | 1011           | 4.2                                                  | 1102.5                                        |

| 0100           | 2.8                                                  | 490.0                                               | 1100           | 4.4                                                  | 1210.0                                        |

| 0101           | 3.0                                                  | 562.5                                               | 1101           | 4.6                                                  | 1322.5                                        |

| 0110           | 3.2                                                  | 640.0                                               | 1110           | 4.8                                                  | 1440.0                                        |

| 0111           | 3.4                                                  | 722.5                                               | 1111           | 5.0                                                  | 1562.5                                        |

THVBATT limits the amount of clipping allowed by the AGC. As  $V_{BATT}$  falls, the maximum output amplitude falls. THVBATT defines the threshold as a fraction of the  $V_{BATT}$  supply voltage. When the fraction is less than 1,

the AGC attempts to adjust gain to prevent clipping. For values greater than 1, some clipping is allowed before the AGC reduces gain (see *Table 10*).

**Table 10. THVBATT Threshold**

| THVBATT [4:0] | V <sub>BATT</sub> Fraction<br>(V/V) | THD with 1KHz Sine Wave (%) ( $V_{BATT}$ =3.7V, $8\Omega$ Load) | THVBATT [4:0] | V <sub>BATT</sub> Fraction<br>(V/V) | THD with 1KHz Sine Wave (%) ( $V_{BATT}$ =3.7V, $8\Omega$ Load) |

|---------------|-------------------------------------|-----------------------------------------------------------------|---------------|-------------------------------------|-----------------------------------------------------------------|

| 0000          | THVBATT Thre                        | eshold Disabled                                                 | 1000          | 1.25                                | 13.0                                                            |

| 0001          | 0.90                                | 1.0                                                             | 1001          | 1.30                                | 14.4                                                            |

| 0010          | 0.95                                | 3.0                                                             | 1010          | 1.35                                | 15.6                                                            |

| 0011          | 1.00                                | 4.9                                                             | 1011          | 1.40                                | 16.7                                                            |

| 0100          | 1.05                                | 6.7                                                             | 1100          | 1.45                                | 17.7                                                            |

| 0101          | 1.10                                | 8.5                                                             | 1101          | 1.50                                | 18.7                                                            |

| 0110          | 1.15                                | 10.0                                                            | 1110          | 1.55                                | 19.6                                                            |

| 0111          | 1.20                                | 11.6                                                            | 1111          | 1.60                                | 20.5                                                            |

Ultimately, the AGC threshold is whichever voltage is lower between THVBATT and THMAX. For example, if THMAX = 0111, THVBATT = 0001, and  $V_{BATT}$  = 4.2V, the AGC threshold is 3.4V as defined by THMAX. If  $V_{BATT}$  falls to 3.6V, the AGC threshold falls to 3.24V as defined by THVBATT (see Figure 21). If THVBATT and THMAX are both set to 0, the AGC is disabled.

Figure 21. AGC Threshold, THMAX = 0111, THVBATT = 0001

# **Starting Gain**

Starting gain is the amount of speaker gain applied when the AGC is not active. It can also be thought of as maximum gain when the AGC is active. Starting gain is controlled by the STARTGAIN register (see Table 11).

Table 11. Speaker Gain Values

| Gain Register [5:0] | Gain (dB) | Gain Register [5:0] | Gain (dB) |

|---------------------|-----------|---------------------|-----------|

| 000000              | Mute      | 100000              | -9.5      |

| 000001              | -25.0     | 100001              | -9.0      |

| 000010              | -24.5     | 100010              | -8.5      |

| 000011              | -24.0     | 100011              | -8.0      |

| 000100              | -23.5     | 100100              | -7.5      |

| 000101              | -23.0     | 100101              | -7.0      |

| 000110              | -22.5     | 100110              | -6.5      |

| 000111              | -22.0     | 100111              | -6.0      |

| 001000              | -21.5     | 101000              | -5.5      |

| 001001              | -21.0     | 101001              | -5.0      |

| 001010              | -20.5     | 101010              | -4.5      |

| 001011              | -20.0     | 101011              | -4.0      |

| 001100              | -19.5     | 101100              | -3.5      |

| 001101              | -19.0     | 101101              | -3.0      |

| 001110              | -18.5     | 101110              | -2.5      |

| 001111              | -18.0     | 101111              | -2.0      |

| 010000              | -17.5     | 110000              | -1.5      |

| 010001              | -17.0     | 110001              | -1.0      |

| 010010              | -16.5     | 110010              | -0.5      |

| 010011              | -16.0     | 110011              | 0         |

| 010100              | -15.5     | 110100              | 0.5       |

| 010101              | -15.0     | 110101              | 1.0       |

| 010110              | -14.5     | 110110              | 1.5       |

| 010111              | -14.0     | 110111              | 2.0       |

| 011000              | -13.5     | 111000              | 2.5       |

| 011001              | -13.0     | 111001              | 3.0       |

| 011010              | -12.5     | 111010              | 3.5       |

| 011011              | -12.0     | 111011              | 4.0       |

| 011100              | -11.5     | 111100              | 4.5       |

| 011101              | -11.0     | 111101              | 5.0       |

| 011110              | -10.5     | 111110              | 5.5       |

| 011111              | -10.0     | 111111              | 6.0       |

# **AGC Attack**

AGC attack occurs when the AGC determines that, after applying present gain, the output signal amplitude would be too high and gain should be stepped down by 1dB. The AGC checks an approximation of the amplitude of the output signal that includes present gain, but excludes clipping that may occur in the final output stage. All of the following conditions must be true to trigger an AGC attack:

- The amplitude is above the AGC threshold, AND

- Present gain is above the minimum gain point, AND

- Attack speed is not exceeded.

The minimum gain is determined by the AGCMIN register. The rate of gain reduction is determined by the AGCATTACK register.

# **AGC Release**

When the output signal is below the AGC threshold, gain is stepped up by 1dB. The rate of gain increase is determined by the AGCRELEASE registers. Gain is increased until it reaches the starting gain or an AGC attack is triggered again.

Table 12. AGC Attack Speed

| AGCATTACK [2:0] | AGC Attack Speed (µs/Step) | AGCATTACK [2:0] | AGC Attack Speed (µs/Step) |

|-----------------|----------------------------|-----------------|----------------------------|

| 000             | 12.5                       | 100             | 200                        |

| 001             | 25.0                       | 101             | 400                        |

| 010             | 50.0                       | 110             | 800                        |

| 011             | 100.0                      | 111             | 1600                       |

Table 13. AGC Release Speed

| The state of the s |                             |                  |                             |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------------------------|--|--|

| AGCRELEASE [2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AGC Release Speed (ms/Step) | AGCRELEASE [2:0] | AGC Release Speed (ms/Step) |  |  |

| 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12.5                        | 100              | 200                         |  |  |

| 001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25.0                        | 101              | 400                         |  |  |

| 010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50.0                        | 110              | 800                         |  |  |