# **Five-Channel Power Supply Supervisors**

### **FEATURES**

- **■** Five-channel supply voltage detection

- 2 V<sub>DD</sub> inputs allow monitoring of +5.0V, +3.3V, +3.0V, +2.5V or +1.8V supplies

- 3 adjustable voltage inputs allow monitoring supplies > 0.6V

- 70ms minimum reset delay

- Manual reset capability

- Reset signals valid down to V<sub>DD</sub> = 1V

- Accurate ± < 2% voltage threshold

- Power-supply transients suppressed

- Low 2µA maximum supply current at 5V

- RoHS-compliant MSOP package

# **APPLICATIONS**

- Telecom & datacom systems

- Routers & servers

- Data storage equipment

- Set-top boxes

- Multi-voltage systems

### DESCRIPTION

The CAT885 is a five-channel power supply supervisory circuit with high reset thereshold accuracy and very low power consumption. The device features an open-drain output, active-low function with manual reset to perform basic system reset and monitoring functions for a wide range of electronic products. The CAT885 monitors five system voltages by maintaining a reset output active until all the power supply voltages exceed the specified trip values. The device then maintains the reset output in an active condition until the internal timer times out, which allows the system power supplies to stabilize.

Two of the five voltage detectors are factory set for standard supplies, while the threshold voltages of the third, fourth, and fifth voltage monitors can be adjusted for specific system design requirements using external resistors.

The CAT885 lowers system costs and saves board space by integrating five channels into a single, small MSOP 8-lead package.

For Ordering Information details see page 7.

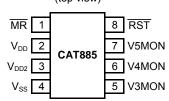

## PIN CONFIGURATION

See page 2 for pin functions

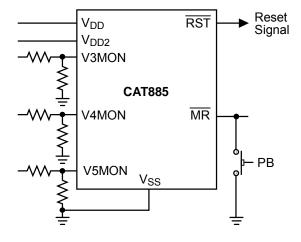

## **TYPICAL APPLICATION**

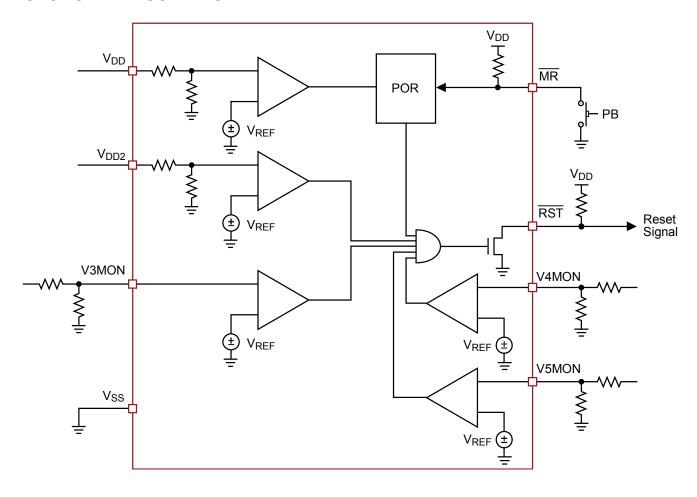

# **FUNCTIONAL BLOCK DIAGRAM**

# **PIN FUNCTIONS**

| Pin# | Pin       | Function                                                     |

|------|-----------|--------------------------------------------------------------|

| 1    | MR        | Active-low manual reset Input with internal pull-up resistor |

| 2    | $V_{DD}$  | Chip supply, first preset under-voltage detector input       |

| 3    | $V_{DD2}$ | Second preset under-voltage detector input                   |

| 4    | $V_{SS}$  | Ground                                                       |

| 5    | V3MON     | Adjustable third under-voltage detector input                |

| 6    | V4MON     | Adjustable fourth under-voltage detector input               |

| 7    | V5MON     | Adjustable fifth under-voltage detector input                |

| 8    | RST       | Active-low open drain reset output, use external resistor    |

2

# **ABSOLUTE MAXIMUM RATINGS(1)**

| Parameters                                                         | Ratings      | Units |

|--------------------------------------------------------------------|--------------|-------|

| Temperature under Bias                                             | -40 to +125  | °C    |

| Voltage on any Pin with Respect to V <sub>SS</sub>                 | -1.0 to +7.0 | V     |

| DC Output Current                                                  | 5            | mA    |

| Thermal Resistance Θ <sub>JA</sub> for MSOP Package <sup>(2)</sup> | 145          | °C/W  |

# RECOMMENDED OPERATING CONDITIONS

| Parameters                               | Ratings     | Units |

|------------------------------------------|-------------|-------|

| Operating Temperature Range (Industrial) | -40 to +85  | °C    |

| Storage Temperature                      | -65 to +150 | °C    |

| Lead Soldering Temperature (10 seconds)  | +300        | °C    |

### **ELECTRICAL CHARACTERISTICS**

Over the recommended operating conditions unless otherwise specified.

| Symbol               | Parameter                                           | Conditions                        | Min   | Тур.  | Max   | Units |

|----------------------|-----------------------------------------------------|-----------------------------------|-------|-------|-------|-------|

| $V_{DD}$             | Supply Voltage Range                                |                                   | 1.5   |       | 5.5   | V     |

| $I_{DD1}$            | V <sub>DD</sub> Supply Current                      | V <sub>DD</sub> = 5.0V            |       | 2     | 9     | μA    |

| $I_{DD2}$            | V <sub>DD2</sub> Input Current                      | $V_{DD2} = 3.3V$                  |       | 0.5   | 3     | μA    |

| I <sub>DDX</sub>     | V3, V4, V5MON Input Current                         | V3, V4, V5MON = 1.0V              |       | 15    | 50    | nA    |

| Voltage T            | Thresholds                                          |                                   |       |       |       |       |

| \/                   | Fixed Voltage Trip Doint for V                      | CAT885Lx                          | 4.55  | 4.63  | 4.72  | V     |

| $V_{TH1}$            | Fixed Voltage Trip Point for V <sub>DD</sub>        | CAT885Sx                          | 2.81  | 2.87  | 2.92  | V     |

| \/                   | Liveteresis of V                                    | V <sub>TH1</sub> = 4.63V          |       | 50    |       | mV    |

| $V_{TH1HYST}$        | Hysteresis of V <sub>TH1</sub>                      | V <sub>TH1</sub> = 2.87V          |       | 30    |       | mV    |

|                      |                                                     | CAT885xT                          | 3.02  | 3.08  | 3.13  | V     |

| V                    | Fixed Voltage Trip Point for V <sub>DD2</sub>       | CAT885xS                          | 2.90  | 2.95  | 3.01  | V     |

| $V_{TH2}$            |                                                     | CAT885xZ                          | 2.29  | 2.33  | 2.37  | V     |

|                      |                                                     | CAT885xA                          | 1.65  | 1.68  | 1.71  | V     |

|                      |                                                     | V <sub>TH2</sub> = 3.08V          |       | 40    |       | mV    |

| \                    | Hysteresis of V <sub>TH2</sub>                      | V <sub>TH2</sub> = 2.95V          |       | 30    |       | mV    |

| $V_{\text{TH2HYST}}$ |                                                     | V <sub>TH2</sub> = 2.33V          |       | 25    |       | mV    |

|                      |                                                     | V <sub>TH2</sub> = 1.68V          |       | 20    |       | mV    |

| $V_{REF}$            | V3MON, V4MON, V5MON Adj.<br>Reset Threshold Voltage | V <sub>TH</sub> for V3, V4, V5MON | 0.585 | 0.598 | 0.611 | V     |

| $V_{REFHYST}$        | Hysteresis Voltage                                  |                                   |       | 3     |       | mV    |

#### Notes

<sup>(1)</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the devices at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

<sup>(2)</sup>  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air.

## **ELECTRICAL CHARACTERISTICS (continued)**

| Symbol           | Parameter                               | Conditions                        | Min                   | Тур. | Max  | Units |

|------------------|-----------------------------------------|-----------------------------------|-----------------------|------|------|-------|

| Reset            |                                         |                                   |                       |      |      |       |

| $V_{OL}$         | Reset Output Voltage Low                | $V_{DD} \ge 3.3V$ , Sinking 2.5mA |                       | 0.05 | 0.40 | V     |

| <b>V</b> OL      |                                         | $V_{DD}$ < 3.3V, Sinking 1.5mA    |                       | 0.05 | 0.40 | V     |

| t <sub>RPD</sub> | V <sub>TH</sub> to Reset Asserted Delay |                                   | 1                     | 6    |      | μs    |

| t <sub>PD</sub>  | POR Timeout Delay                       |                                   | 70                    | 120  | 240  | ms    |

| $C_{LOAD}$       | Load Capacitance on Reset Pin           |                                   |                       | 5    |      | pF    |

| Manual R         | eset                                    |                                   |                       |      |      |       |

| $V_{THL}$        | MR Input Voltage Low                    |                                   |                       |      | 8.0  | V     |

| $V_{THH}$        | MR Input Voltage High                   |                                   | V <sub>DD</sub> - 0.6 |      |      | V     |

| $T_PW$           | MR Minimum Pulse Width                  |                                   | 1                     |      |      | μs    |

| R <sub>IN</sub>  | Internal Pull-Up Resistor               |                                   | 8                     |      | 16   | kΩ    |

#### **OPERATION**

The CAT885 is designed to monitor critical supply voltages in line driven and battery powered microprocessor systems, providing Supply Voltage Supervision, Power On Reset control and Manual Reset Assertion. These features along with excellent threshold accuracy and low power consumption make the CAT885 device suitable for a wide variety of applications needing multi-voltage monitoring.

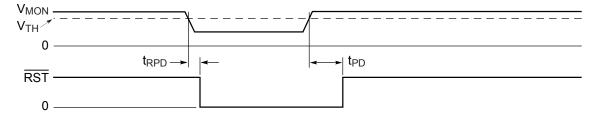

During normal operation, the CAT885 monitors the voltage levels of  $V_{DD}$ , V2MON, V3MON, V4MON, and V5MON. If the voltage on any of these five inputs falls below their respective voltage trip points, a reset is asserted ( $\overline{RST}$  = low) to prevent the microprocessor from operating during a power failure or brownout condition. This reset signal remains low until the voltages exceeds the voltage threshold settings for the reset time delay period  $t_{PD}$ .

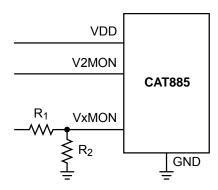

CAT885 allows users to adjust the minimum voltage sense level for three of the five monitored voltages. For example, the user can adjust the voltage input trip point for  $V_{3MON}$ ,  $V_{4MON}$  and  $V_{5MON}$  inputs. This is done by connecting an external resistor divider network to the  $V_{xMON}$  pin in order to set the trip point to a voltage above 600mV. Resistors  $R_1$  and  $R_2$  in Figure 1 are selected by the formula:  $V_{TRIP} = 0.6V \times (R_1 + R_2) / R_2$ .

Figure 1. CAT885 Programming Trip Voltage

#### **POWER ON RESET (POR)**

Applying power to the CAT885 activates a POR circuit which activates the reset output (active LOW). At power-up POR prevents the system microprocessor from starting to operate with insufficient voltage and prior to stabilization of the clock oscillator. It ensures that operation is precluded until internal registers are properly loaded, FPGA's have downloaded their configuration data prior and all system power supplies are above minimum operating levels and stable. The reset signal remains active until  $V_{\text{DD}}$  rises above the minimum preset voltage level for time period  $t_{\text{PD}}$ .

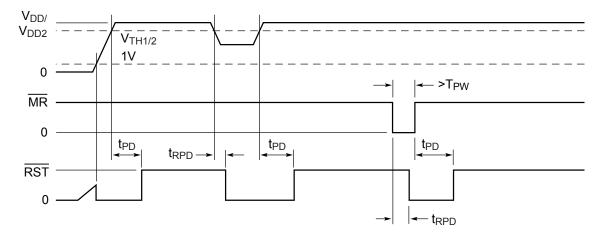

#### MANUAL RESET

The manual-reset input  $(\overline{MR})$  allows the user to trigger a reset by using a push-button switch or by electronically driving the input low. The  $\overline{MR}$  input is an active LOW debounced input. Reset is asserted anytime the  $\overline{MR}$  pin is pulled low to less than 100mV for the minimum  $\overline{MR}$  pulse width or longer. The reset output remains asserted low for  $t_{PD}$ , typically 120ms and then is released. Figures 2 and 3 illustrate the CAT885's operation and  $\overline{RST}$  output response times.

Figure 2. Power Supply Monitoring Diagram

Figure 3. Auxillary Voltage Monitoring Diagram

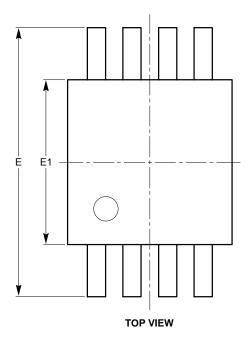

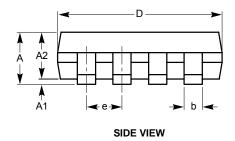

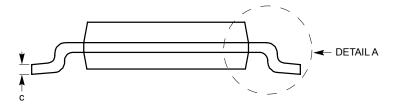

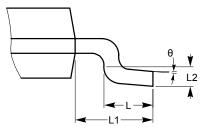

# **PACKAGE OUTLINE DRAWING**

MSOP 8-Lead 3 x 3mm (Z) (1)(2)

| SYMBOL | MIN  | NOM      | MAX  |

|--------|------|----------|------|

| А      |      |          | 1.10 |

| A1     | 0.05 | 0.10     | 0.15 |

| A2     | 0.75 | 0.85     | 0.95 |

| b      | 0.22 |          | 0.38 |

| С      | 0.13 |          | 0.23 |

| D      | 2.90 | 3.00     | 3.10 |

| Е      | 4.80 | 4.90     | 5.00 |

| E1     | 2.90 | 3.00     | 3.10 |

| е      |      | 0.65 BSC |      |

| L      | 0.40 | 0.60     | 0.80 |

| L1     |      | 0.95 REF |      |

| L2     |      | 0.25 BSC |      |

| θ      | 0°   |          | 6°   |

**END VIEW**

DETAIL A

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf.

## Notes:

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Complies with JEDEC standard MO-187.

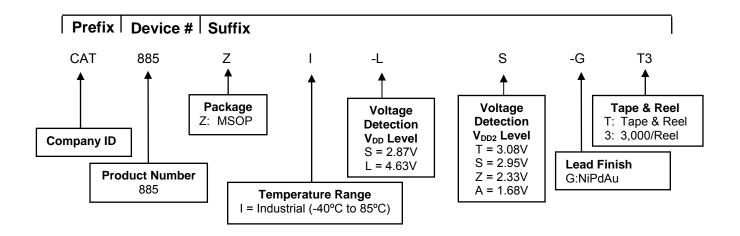

## **EXAMPLE OF ORDERING INFORMATION**

## ORDERING INFORMATION

| Part Number     | V <sub>DD</sub> | $V_{DD2}$ | Package |

|-----------------|-----------------|-----------|---------|

| CAT885ZI-ST-GT3 | 2.87V           | 3.08V     | MSOP    |

| CAT885ZI-SS-GT3 | 2.87V           | 2.95V     | MSOP    |

| CAT885ZI-SZ-GT3 | 2.87V           | 2.33V     | MSOP    |

| CAT885ZI-SA-GT3 | 2.87V           | 1.68V     | MSOP    |

| CAT885ZI-LT-GT3 | 4.63V           | 3.08V     | MSOP    |

| CAT885ZI-LS-GT3 | 4.63V           | 2.95V     | MSOP    |

| CAT885ZI-LZ-GT3 | 4.63V           | 2.33V     | MSOP    |

| CAT885ZI-LA-GT3 | 4.63V           | 1.68V     | MSOP    |

For Product Top Mark Codes, click here: http://www.catsemi.com/techsupport/producttopmark.asp

#### Notes:

- (1) All packages are RoHS-compliant (Lead-free, Halogen-free).

- (2) The standard finish is NiPdAu.

- (3) The device used in the above example is a CAT885ZI-LS-GT3 (MSOP, Industrial Temperature, 4.63V (V<sub>DD</sub>) and 2.95V (V<sub>DD2</sub>) Detection Levels, NiPdAu, Tape & Reel, 3,000/Reel).

- (4) For additional detection voltage, package and temperature options, please contact your nearest Catalyst Semiconductor Sales office.

#### **REVISION HISTORY**

| Date      | Rev. | Reason          |

|-----------|------|-----------------|

| 05-May-08 | Α    | Initial Release |

#### Copyrights, Trademarks and Patents

© Catalyst Semiconductor, Inc.

Trademarks and registered trademarks of Catalyst Semiconductor include each of the following:

Adaptive Analog™, Beyond Memory™, DPP™, EZDim™, LDD™, MiniPot™, Quad-Mode™ and Quantum Charge Programmable™

Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products.

CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.

Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.

Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.

Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.

Catalyst Semiconductor, Inc. Corporate Headquarters 2975 Stender Way Santa Clara, CA 95054 Phone: 408.542.1000

Fax: 408.542.1200 www.catsemi.com

Document No: MD-3028

Revision: A

Issue date: 05/05/08