# National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

12-bit plus sign

33 mW (max)

100 μW (typ)

# ADC12130/ADC12132/ADC12138 Self-Calibrating 12-Bit Plus Sign Serial I/O A/D Converters with MUX and Sample/Hold

### **General Description**

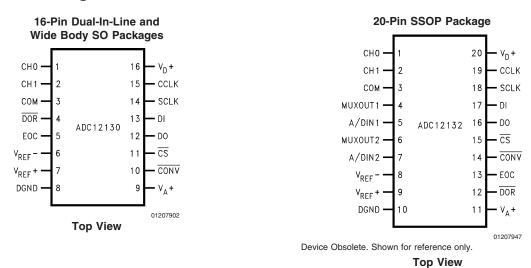

NOTE: All versions of the ADC12132 are obsolete and shown here for reference only.

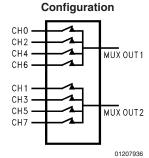

The ADC12130, ADC12132 and ADC12138 are 12-bit plus sign successive approximation A/D converters with serial I/O and configurable input multiplexer. The ADC12132 and ADC12138 have a 2 and an 8 channel multiplexer, respectively. The differential multiplexer outputs and A/D inputs are available on the MUXOUT1, MUXOUT2, A/DIN1 and A/DIN2 pins. The ADC12130 has a two channel multiplexer with the multiplexer outputs and A/D inputs internally connected. The ADC12130 family is tested and specified with a 5 MHz clock. On request, these A/Ds go through a self calibration process that adjusts linearity, zero and full-scale errors to typically less than ±1 LSB each.

The analog inputs can be configured to operate in various combinations of single-ended, differential, or pseudo-differential modes. A fully differential unipolar analog input range (0V to +5V) can be accommodated with a single +5V supply. In the differential modes, valid outputs are obtained even when the negative inputs are greater than the positive because of the 12-bit plus sign output data format.

The ADC12132 is obsolete and described in this document for reference only.

The serial I/O is configured to comply with NSC MICROW-IRE $^{\text{TM}}$ . For voltage references, see the LM4040, LM4050 or LM4041.

### **Features**

- Serial I/O (MICROWIRE, SPI and QSPI Compatible)

- Power down mode

- Programmable acquisition time

- Variable digital output word length and format

- No zero or full scale adjustment required

- 0V to 5V analog input range with single 5V power supply

### **Key Specifications**

| ■ 12-Bit plus sign conversion time | 8.8 µs (max)    |

|------------------------------------|-----------------|

| ■ 12-Bit plus sign throughput time | 14 µs (max)     |

| ■ Integral Linearity Error         | ±2 LSB (max)    |

| ■ Single Supply                    | 3.3V or 5V ±10% |

| ■ Power Consumption                |                 |

| +3.3V                              | 15 mW (max)     |

| +3.3V power down                   | 40 μW (typ)     |

|                                    |                 |

### **Applications**

+5V

- Pen-based computers

- Digitizers

- Global positioning systems

+5V power down

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

COPS™ microcontrollers, HPC™ and MICROWIRE™ are trademarks of National Semiconductor Corporation

### **ADC12138 Simplified Block Diagram** CONV CCLK SCLK 早 7 口 口 口 Address Latch Control Timing **►**□ EOC **▶** DOR СНО CH1 SAR Output Output CH2 **→**□ D0 Shift Logic CH3 Analog Register and Input Buffer ALU RAM CH4 Multiplexer CH5 CH6 CH7 сом MUXOUT1 □◀ A/DIN1 MUXOUT2 □ -Correction A/DIN2 DAC V<sub>A</sub>+ □ DAC V<sub>D</sub>+ □ 白 $V_{\mathsf{REF}}$ + V<sub>REF</sub>-

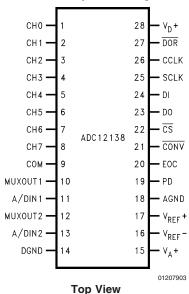

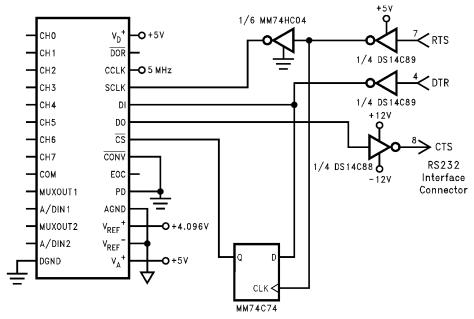

### **Connection Diagrams**

01207901

### Connection Diagrams (Continued)

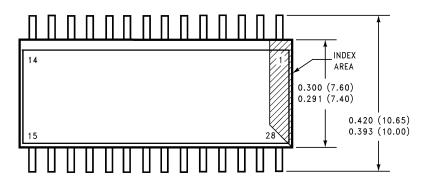

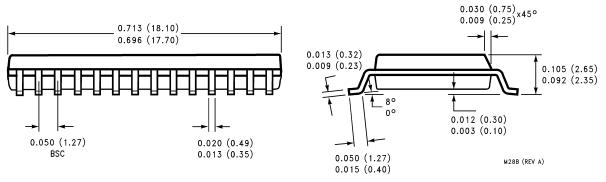

# 28-Pin Dual-In-Line, SSOP and Wide Body SO Packages

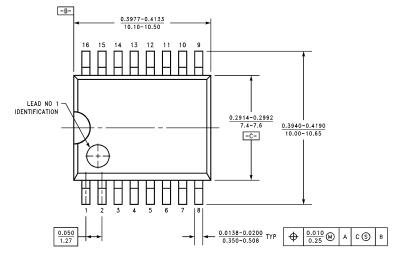

### **Ordering Information**

| Industrial Temperature Range<br>-40°C ≤ T <sub>A</sub> ≤ +85°C | NS Package Number                |  |  |  |  |  |  |

|----------------------------------------------------------------|----------------------------------|--|--|--|--|--|--|

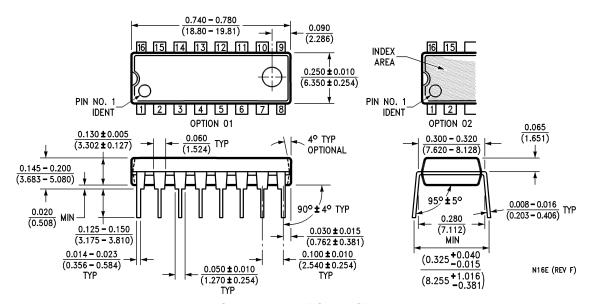

| ADC12130CIN                                                    | N16E, Dual-In-Line               |  |  |  |  |  |  |

| ADC12130CIWM                                                   | M16B, Wide Body SO               |  |  |  |  |  |  |

| ADC12130CIWMX                                                  | M16B, Wide Body SO - Tape & Reel |  |  |  |  |  |  |

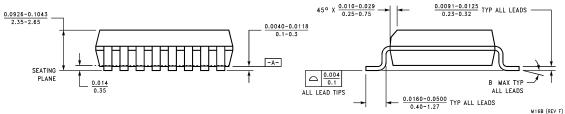

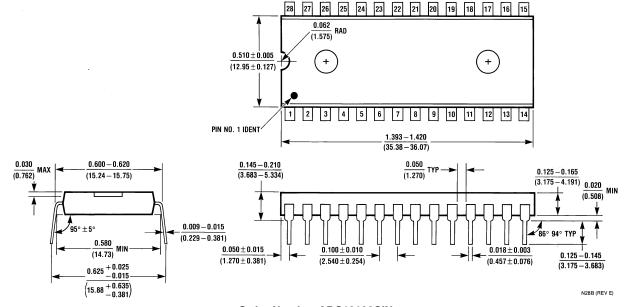

| ADC12132CIMSA *                                                | MSA20, SSOP                      |  |  |  |  |  |  |

| ADC12132CIMSAX *                                               | MSA20, SSOP - Tape & Reel        |  |  |  |  |  |  |

| ADC12138CIN                                                    | N28B, Dual-In-Line               |  |  |  |  |  |  |

| ADC12138CIWM                                                   | M28B                             |  |  |  |  |  |  |

| ADC12138CIWMX                                                  | M28B - Tape & Reel               |  |  |  |  |  |  |

| ADC12138CIMSA                                                  | MSA28, SSOP                      |  |  |  |  |  |  |

| ADC12138CIMSA                                                  | MSA28, SSOP - Tape & Reel        |  |  |  |  |  |  |

<sup>\*</sup> The ADC12132 is obsolete and shown in this document for reference only.

### **Pin Descriptions**

**CCLK**

The clock applied to this input controls the successive approximation conversion time interval and the acquisition time. The rise and fall times of the clock edges should not exceed 1  $\mu$ s.

SCLK

This is the serial data clock input. The clock applied to this input controls the rate at which the serial data exchange occurs. The rising edge loads the information at the DI pin into the multiplexer address and mode select shift register. This address controls which channel of the analog input multiplexer (MUX) is selected

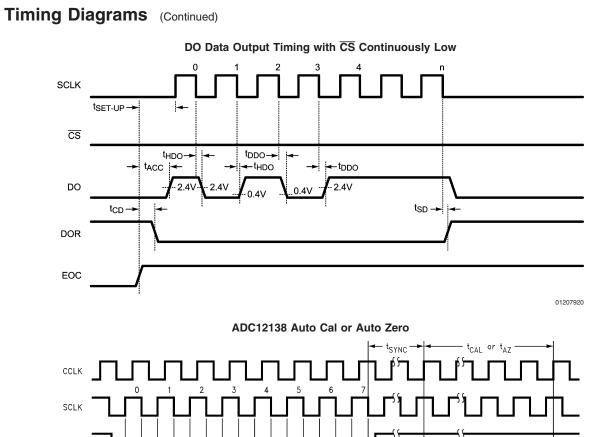

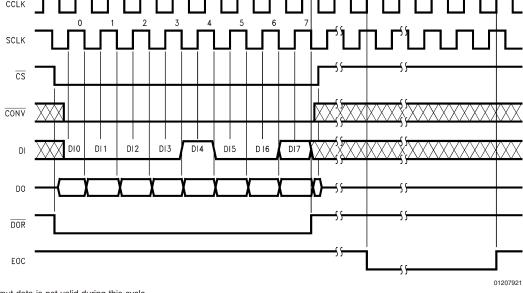

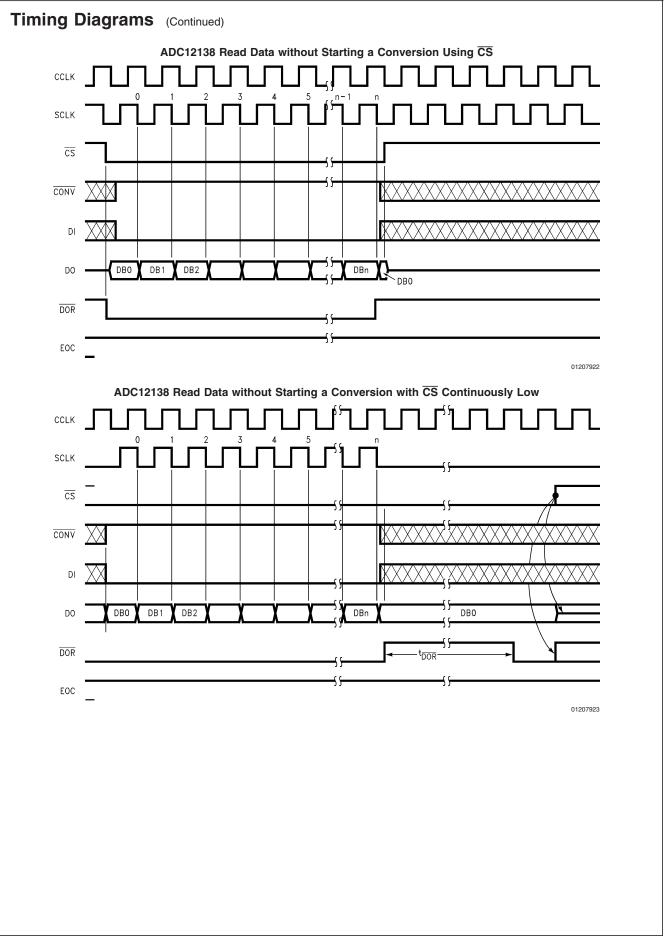

and the mode of operation for the A/D. With  $\overline{\text{CS}}$  low, the falling edge of SCLK shifts the data resulting from the previous ADC conversion out on DO, with the exception of the first bit of data. When  $\overline{\text{CS}}$  is low continuously, the first bit of the data is clocked out on the rising edge of  $\overline{\text{EOC}}$  (end of conversion). When  $\overline{\text{CS}}$  is toggled, the falling edge of  $\overline{\text{CS}}$  always clocks out the first bit of data.  $\overline{\text{CS}}$  should be brought low when SCLK is low. The rise and fall times of the clock edges should not exceed 1  $\mu$ s.

DO

CS

### Pin Descriptions (Continued)

DI This is the serial data input pin. The data applied to this pin is shifted at the rising edge of SCLK into the multiplexer address and mode select register. *Table 2* through *Table 4* show the assignment of the multiplexer address and the mode select data.

The data output pin. This pin is an active push/pull output when  $\overline{CS}$  is low. When  $\overline{CS}$  is high, this output is TRI-STATE®. The A/D conversion result (DB0-DB12) and converter status data are clocked out at the falling edge of SCLK on this pin. The word length and format of this result can vary (see *Table 1*). The word length and format are controlled by the data shifted into the multiplexer address and mode select register (see *Table 4*).

EOC This pin is an active push/pull output and indicates the status of the ADC12130/2/8. When low, it signals that the A/D is busy with a conversion, auto-calibration, auto-zero or power down cycle. The rising edge of EOC signals the end of one of these cycles.

This is the chip select pin. When a logic low is applied to this pin, the rising edge of SCLK shifts the data on DI into the address register. This low also brings DO out of TRI-STATE. With  $\overline{\text{CS}}$  low, the falling edge of SCLK shifts the data resulting from the previous ADC conversion out on DO, with the exception of the first bit of data. When  $\overline{\text{CS}}$  is low continuously, the first bit of the data is clocked out on the rising edge of EOC (end of conversion). When  $\overline{CS}$  is toggled, the falling edge of  $\overline{\text{CS}}$  always clocks out the first bit of data.

CS should be brought low when SCLK is low. The falling edge of  $\overline{\text{CS}}$ resets a conversion in progress and starts the sequence for a new conversion. When  $\overline{\text{CS}}$  is brought back low during a conversion, that conversion is prematurely terminated. The data in the output latches may be corrupted. Therefore, when CS is brought back low during a conversion in progress the data output at that time should be ignored. CS may also be left continuously low. In this case it is imperative that the correct number of SCLK pulses be applied to the ADC in order to remain synchronous. After the ADC supply power is applied it expects to see 13 clock pulses for each I/O sequence. The number of clock pulses the ADC expects is the same as the digital output word length. This word length can be modified by the data shifted in at the DO pin. Table 4 details the data required.

This is the data output ready pin. This pin is an active push/pull output. It is low when the conversion result is being shifted out and goes high to signal that all the data has been shifted out.

CONV

A logic low is required on this pin to program

A logic low is required on this pin to program any mode or change the ADC's configuration as listed in the Mode Programming Table

4

(*Table 4*) such as 12-bit conversion, Auto Cal, Auto Zero etc. When this pin is high the ADC is placed in the read data only mode. While in the read data only mode, bringing  $\overline{CS}$  low and pulsing SCLK will only clock out on DO any data stored in the ADCs output shift register. The data on DI will be neglected. A new conversion will not be started and the ADC will remain in the mode and/or configuration previously programmed. Read data only cannot be performed while a conversion, Auto-Cal or Auto-Zero are in progress.

PD This is the power down pin. When PD is high the A/D is powered down; when PD is low the A/D is powered up. The A/D takes a maximum of 700 µs to power up after the command is given.

CH0-CH7 These are the analog inputs of the MUX. A channel input is selected by the address information at the DI pin, which is loaded on the rising edge of SCLK into the address register (see *Table 2* and *Table 3*).

The voltage applied to these inputs should not exceed  $V_A+$  or go below GND. Exceeding this range on an unselected channel will corrupt the reading of a selected channel.

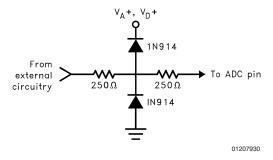

COM This pin is another analog input pin. It is used as a pseudo ground when the analog multiplexer is single-ended.

MUXOUT1, MUXOUT2

These are the multiplexer output pins.

A/DIN1, A/DIN2

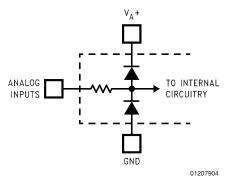

These are the converter input pins. MUXOUT1 is usually tied to A/DIN1. MUXOUT2 is usually tied to A/DIN2. If external circuitry is placed between MUXOUT1 and A/DIN1, or MUXOUT2 and A/DIN2 it may be necessary to protect these pins. The voltage at these pins should not exceed  $V_A^+$  or go below AGND (see *Figure 6*).

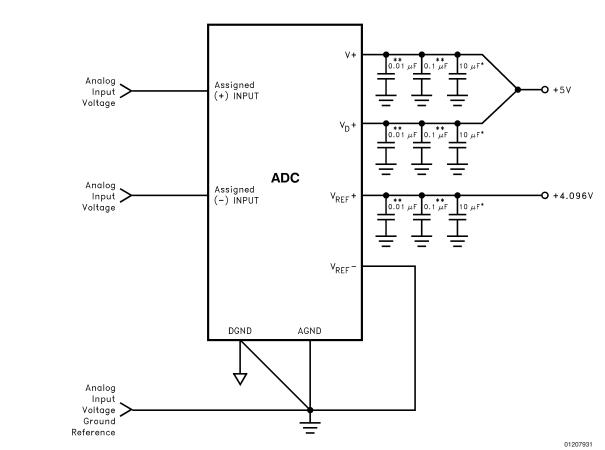

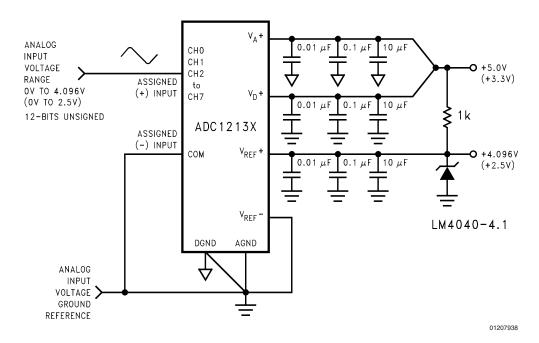

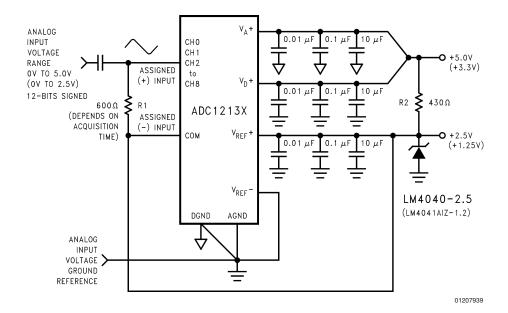

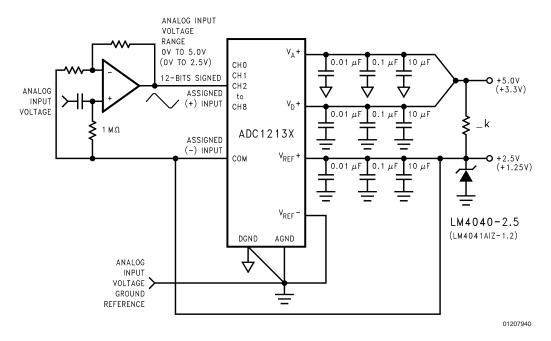

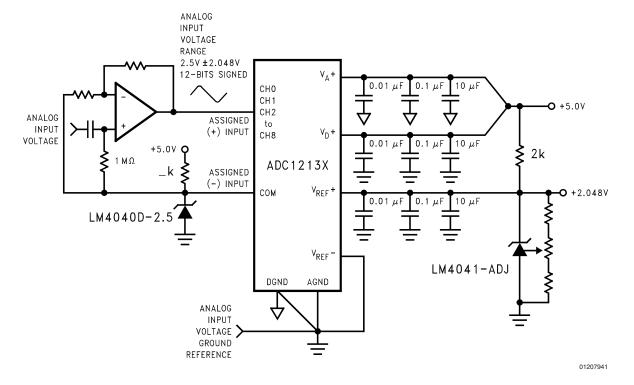

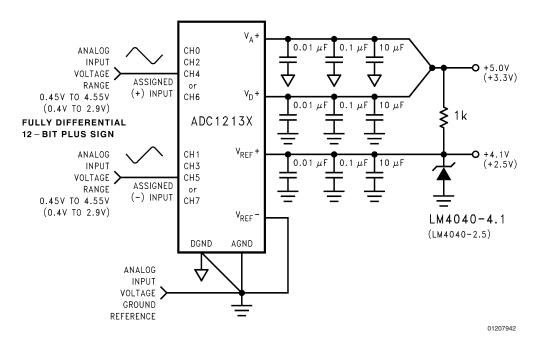

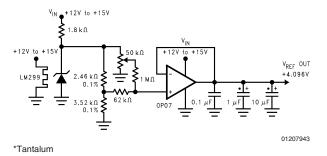

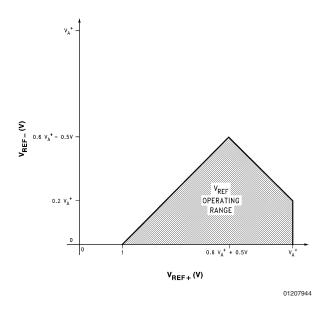

$V_{REF}+$  This is the positive analog voltage reference input. In order to maintain accuracy, the voltage range of  $V_{REF}$  ( $V_{REF}=V_{REF}+-V_{REF}-$ ) is 1  $V_{DC}$  to 5.0  $V_{DC}$  and the voltage at  $V_{REF}+$  cannot exceed  $V_{A}+$ . See *Figure 5* for recommended bypassing.

V<sub>REF</sub>- The negative voltage reference input. In order to maintain accuracy, the voltage at this pin must not go below GND or exceed V<sub>A</sub>+. (See *Figure 5*).

$V_{A^+}$ ,  $V_{D^+}$  These are the analog and digital power supply pins.  $V_{A^+}$  and  $V_{D^+}$  are not connected together on the chip. These pins should be tied to the same power supply and bypassed separately (see *Figure 5*). The operating voltage range of  $V_{A^+}$  and  $V_{D^+}$  is 3.0  $V_{DC}$  to 5.5  $V_{DC}$ .

DGND This is the digital ground pin (see *Figure 5*).

AGND This is the analog ground pin (see *Figure 5*).

### **Absolute Maximum Ratings**

(Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Positive Supply Voltage           |                        |

|-----------------------------------|------------------------|

| $(V^+ = V_A + = V_D +)$           | 6.5V                   |

| Voltage at Inputs and Outputs     |                        |

| except CH0-CH7 and COM            | $-0.3V$ to $V^+ +0.3V$ |

| Voltage at Analog Inputs          |                        |

| CH0-CH7 and COM                   | GND $-5V$ to $V^+ +5V$ |

| $ V_A + - V_D +  $                | 300 mV                 |

| Input Current at Any Pin (Note 3) | ±30 mA                 |

| Package Input Current (Note 3)    | ±120 mA                |

| Package Dissipation at            |                        |

| $T_A = 25^{\circ}C$ (Note 4)      | 500 mW                 |

| ESD Susceptibility (Note 5)       |                        |

| Human Body Model                  | 1500V                  |

| Soldering Information             |                        |

| N Packages (10 seconds)           | 260°C                  |

| SO Package (Note 6):              |                        |

| Vapor Phase (60 seconds)          | 215°C                  |

| Infrared (15 seconds)             | 220°C                  |

| Storage Temperature               | -65°C to +150°C        |

### Operating Ratings (Notes 1, 2)

| Operating Temperature Range                | $T_{MIN} \leq T_A \leq T_{MAX}$                                       |

|--------------------------------------------|-----------------------------------------------------------------------|

|                                            | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$ |

| Supply Voltage $(V^+ = V_A + = V_D +)$     | +3.0V to +5.5V                                                        |

| $ V_A^+ - V_D^+ $                          | ≤ 100 mV                                                              |

| V <sub>REF</sub> +                         | 0V to V <sub>A</sub> +                                                |

| V <sub>REF</sub> -                         | $0V$ to $(V_{REF} + -1V)$                                             |

| $V_{REF} (V_{REF} + - V_{REF} -)$          | 1V to V <sub>A</sub> +                                                |

| V <sub>REF</sub> Common Mode Voltage Range |                                                                       |

| $[(V_{REF}+) - (V_{REF}-)] / 2$            | 0.1 $V_A$ + to 0.6 $V_A$ +                                            |

| A/DIN1, A/DIN2, MUXOUT1                    |                                                                       |

| and MUXOUT2 Voltage Range                  | 0V to V <sub>A</sub> +                                                |

| A/D IN Common Mode                         |                                                                       |

| Voltage Range                              |                                                                       |

| $[(V_{IN}+) - (V_{IN}-)] / 2$              | 0V to $V_A$ +                                                         |

### **Package Thermal Resistance**

| Part Number     | Thermal<br>Resistance (θ <sub>JA</sub> ) |

|-----------------|------------------------------------------|

| ADC12130CIN     | 53°C/W                                   |

| ADC12130CIWM    | 70°C/W                                   |

| ADC12132CIMSA * | 134°C/W                                  |

| ADC12132CIWM *  | 64°C/W                                   |

| ADC121038CIN    | 40°C/W                                   |

| ADC121038CIMSA  | 97°C/W                                   |

| ADC12138CIWM    | 50°C/W                                   |

<sup>\*</sup> The ADC12132 is obsolete and is shown for reference only.

### **Converter Electrical Characteristics**

The following specifications apply for  $(V^+ = V_A + = V_D + = +5V, V_{REF} + = +4.096V, and fully differential input with fixed 2.048V common-mode voltage) or <math>(V^+ = V_A + = V_D + = 3.3V, V_{REF} + = 2.5V)$  and fully-differential input with fixed 1.250V common-mode voltage),  $V_{REF} - = 0V$ , 12-bit + sign conversion mode, source impedance for analog inputs,  $V_{REF} - = 0V$  acquisition time unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A = T_J = 25^{\circ}C$ . (Notes 7, 8, 9)

| Symbol   | Parameter                         | Conditions                                                       | Typical<br>(Note 10) | Limits<br>(Note 11) | Units<br>(Limits) |  |  |  |  |  |  |  |  |

|----------|-----------------------------------|------------------------------------------------------------------|----------------------|---------------------|-------------------|--|--|--|--|--|--|--|--|

| STATIC ( | STATIC CONVERTER CHARACTERISTICS  |                                                                  |                      |                     |                   |  |  |  |  |  |  |  |  |

|          | Resolution with No Missing Codes  |                                                                  |                      | 12 + sign           | Bits (min)        |  |  |  |  |  |  |  |  |

| ILE      | Integral Linearity Error          | After Auto-Cal (Notes 12, 18)                                    | ±1/2                 | ±2                  | LSB (max)         |  |  |  |  |  |  |  |  |

| DNL      | Differential Non-Linearity        | After Auto-Cal                                                   |                      | ±1.5                | LSB (max)         |  |  |  |  |  |  |  |  |

|          | Positive Full-Scale Error         | After Auto-Cal (Notes 12, 18)                                    | ±1/2                 | ±3.0                | LSB (max)         |  |  |  |  |  |  |  |  |

|          | Negative Full-Scale Error         | After Auto-Cal (Notes 12, 18)                                    | ±1/2                 | ±3.0                | LSB (max)         |  |  |  |  |  |  |  |  |

|          | Offset Error                      | After Auto-Cal (Notes 5, 18)<br>$V_{IN}(+) = V_{IN}(-) = 2.048V$ | ±1/2                 | ±2                  | LSB (max)         |  |  |  |  |  |  |  |  |

|          | DC Common Mode Error              | After Auto-Cal (Note 15)                                         | ±2                   |                     | LSB (max)         |  |  |  |  |  |  |  |  |

| TUE      | Total Unadjusted Error            | After Auto-Cal (Notes 12, 13, 14)                                | ±1                   |                     | LSB               |  |  |  |  |  |  |  |  |

|          | Multiplexer Chan-to-Chan Matching | $V^+ = +5V \pm 10\%, V_{REF} = +4.096V$                          | ±0.05                |                     | LSB               |  |  |  |  |  |  |  |  |

|          | Power Supply Sensitivity          |                                                                  |                      |                     |                   |  |  |  |  |  |  |  |  |

|          | Offset Error                      |                                                                  | ±0.5                 |                     | LSB               |  |  |  |  |  |  |  |  |

|          | + Full-Scale Error                |                                                                  | ±0.5                 |                     | LSB               |  |  |  |  |  |  |  |  |

|          | - Full-Scale Error                |                                                                  | ±0.5                 |                     | LSB               |  |  |  |  |  |  |  |  |

|          | Integral Linearity Error          |                                                                  | ±0.5                 |                     | LSB               |  |  |  |  |  |  |  |  |

### **Converter Electrical Characteristics** (Continued)

The following specifications apply for  $(V^+ = V_A + = V_D + = +5V, V_{REF} + = +4.096V, and fully differential input with fixed 2.048V common-mode voltage) or <math>(V^+ = V_A + = V_D + = 3.3V, V_{REF} + = 2.5V)$  and fully-differential input with fixed 1.250V common-mode voltage),  $V_{REF} - = 0V$ , 12-bit + sign conversion mode, source impedance for analog inputs,  $V_{REF} - and V_{REF} + 2.5V$ ,  $V_{REF} - and V_{$

| Symbol              | Parameter                                         | Conditions                                                               | Typical<br>(Note 10)                    | Limits<br>(Note 11) | Units<br>(Limits)  |

|---------------------|---------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------|---------------------|--------------------|

| UNIPOLA             | AR DYNAMIC CONVERTER CHARAC                       | TERISTICS                                                                |                                         |                     |                    |

|                     |                                                   | $f_{IN} = 1 \text{ kHz}, V_{IN} = 5 V_{PP}, V_{REF}^{+} = 5.0V$          | 69.4                                    |                     | dB                 |

| S/(N+D)             | Signal-to-Noise Plus Distortion Ratio             | $f_{IN} = 20 \text{ kHz}, V_{IN} = 5 V_{PP}, V_{REF}^{+} = 5.0 \text{V}$ | 68.3                                    |                     | dB                 |

|                     |                                                   | $f_{IN} = 40 \text{ kHz}, V_{IN} = 5 V_{PP}, V_{REF} + = 5.0V$           | 65.7                                    |                     | dB                 |

|                     | -3 dB Full Power Bandwidth                        | $V_{IN} = 5 V_{PP}$ , where S/(N+D) drops 3 dB                           | 31                                      |                     | kHz                |

| DIFFERE             | NTIAL DYNAMIC CONVERTER CHA                       | RACTERISTICS                                                             | 1                                       |                     |                    |

|                     |                                                   | $f_{IN} = 1 \text{ kHz}, V_{IN} = \pm 5V, V_{REF}^{+} = 5.0V$            | 77.0                                    |                     | dB                 |

| S/(N+D)             | Signal-to-Noise Plus Distortion Ratio             | $f_{IN} = 20 \text{ kHz}, V_{IN} = \pm 5V, V_{REF}^{+} = 5.0V$           | 73.9                                    |                     | dB                 |

|                     |                                                   | $f_{IN} = 40 \text{ kHz}, V_{IN} = \pm 5V, V_{REF}^{+} = 5.0V$           | 67.0                                    |                     | dB                 |

|                     | -3 dB Full Power Bandwidth                        | $V_{IN} = \pm 5V$ , where S/(N+D) drops 3 dB                             | 40                                      |                     | kHz                |

| REFERE              | NCE INPUT, ANALOG INPUTS AND                      | MULTIPLEXER CHARACTERISTICS                                              | 1                                       |                     |                    |

| C <sub>REF</sub>    | Reference Input Capacitance                       |                                                                          | 85                                      |                     | pF                 |

| C <sub>A/D</sub>    | A/DIN1 and A/DIN2 Analog Input Capacitance        |                                                                          | 75                                      |                     | pF                 |

|                     | A/DIN1 and A/DIN2 Analog Input<br>Leakage Current | V <sub>IN</sub> = +5.0V or V <sub>IN</sub> = 0V                          | ±0.1                                    |                     | μΑ                 |

|                     | CH0-CH7 and COM Input Voltage                     |                                                                          | GND - 0.05<br>(V <sub>A</sub> +) + 0.05 |                     | V (min)<br>V (max) |

| ССН                 | CH0-CH7 and COM Input Capacitance                 |                                                                          | 10                                      |                     | pF                 |

| C <sub>MUXOUT</sub> | MUX Output Capacitance                            |                                                                          | 20                                      |                     | pF                 |

|                     | Off Channel Leakage (Note 16)                     | On Channel = 5V and<br>Off Channel = 0V                                  | -0.01                                   |                     | μΑ                 |

|                     | CH0-CH7 and COM Pins                              | On Channel = 0V and<br>Off Channel = 5V                                  | 0.01                                    |                     | μΑ                 |

|                     | On Channel Leakage (Note 16)                      | On Channel = 5V and<br>Off Channel = 0V                                  | 0.01                                    |                     | μA                 |

|                     | CH0-CH7 and COM Pins                              | On Channel = 0V and<br>Off Channel = 5V                                  | -0.01                                   |                     | μA                 |

|                     | MUXOUT1 and MUXOUT2 Leakage Current               | $V_{MUXOUT} = 5.0V \text{ or } V_{MUXOUT} = 0V$                          | 0.01                                    |                     | μA                 |

| R <sub>ON</sub>     | MUX On Resistance                                 | $V_{IN} = 2.5V$ and $V_{MUXOUT} = 2.4V$                                  | 850                                     | 1900                | Ω (max)            |

|                     | R <sub>ON</sub> Matching Channel to Channel       | $V_{IN} = 2.5V$ and $V_{MUXOUT} = 2.4V$                                  | 5                                       |                     | %                  |

|                     | Channel-to-Channel Crosstalk                      | $V_{IN} = 5 V_{PP}, f_{IN} = 40 \text{ kHz}$                             | -72                                     |                     | dB                 |

|                     | MUX Bandwidth                                     |                                                                          | 90                                      |                     | kHz                |

# **DC and Logic Electrical Characteristics**

The following specifications apply for  $(V^+ = V_A + = V_D + = +5V, V_{REF} + = +4.096V)$ , and fully-differential input with fixed 2.048V common-mode voltage) or  $(V^+ = V_A + = V_D + = +3.3V, V_{REF} + = +2.5V)$  and fully-differential input with fixed 1.250V common-mode voltage),  $V_{REF} - = 0V$ , 12-bit + sign conversion mode, source impedance for analog inputs,  $V_{REF} - = 0V$ , 12-bit + sign conversion mode, source impedance for analog inputs,  $V_{REF} - = 0V$ ,  $V_{REF} - = 0V$ , 12-bit + sign conversion mode, source impedance for analog inputs,  $V_{REF} - = 0V$ ,  $V_{REF} - = 0$

| Symbol              | Parameter                                             | Conditions                                                 | Typical<br>(Note 10) | $V^+ = V_A + =$ $V_D + = 3.3V$ Limits (Note 11) | $V^+ = V_A + =$ $V_D + = 5V$ Limits (Note 11) | Units<br>(Limits)    |  |  |  |  |  |  |  |  |

|---------------------|-------------------------------------------------------|------------------------------------------------------------|----------------------|-------------------------------------------------|-----------------------------------------------|----------------------|--|--|--|--|--|--|--|--|

| CCLK, C             | CCLK, CS, CONV, DI, PD AND SCLK INPUT CHARACTERISTICS |                                                            |                      |                                                 |                                               |                      |  |  |  |  |  |  |  |  |

| $V_{IN(1)}$         | Logical "1" Input Voltage                             | $V_A + = V_D + = V^+ + 10\%$                               |                      | 2.0                                             | 2.0                                           | V (min)              |  |  |  |  |  |  |  |  |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage                             | $V_A + = V_D + = V^+ - 10\%$                               |                      | 0.8                                             | 0.8                                           | V (max)              |  |  |  |  |  |  |  |  |

| I <sub>IN(1)</sub>  | Logical "1" Input Current                             | $V_{IN} = V^+$                                             | 0.005                | 1.0                                             | 1.0                                           | μA (max)             |  |  |  |  |  |  |  |  |

| I <sub>IN(0)</sub>  | Logical "0" Input Current                             | $V_{IN} = 0V$                                              | -0.005               | -1.0                                            | -1.0                                          | μA (min)             |  |  |  |  |  |  |  |  |

| DO, EO              | C AND DOR DIGITAL OUTPUT CHAR                         | ACTERISTICS                                                |                      |                                                 |                                               |                      |  |  |  |  |  |  |  |  |

| V                   | Logical "1" Output Voltage                            | $V_A + = V_D + = V^+ - 10\%,$<br>$I_{OUT} = -360 \mu A$    |                      | 2.4                                             | 2.4                                           | V (min)              |  |  |  |  |  |  |  |  |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage                            | $V_A + = V_D + = V^+ - 10\%,$<br>$I_{OUT} = -10 \mu A$     |                      | 2.9                                             | 4.25                                          | V (min)              |  |  |  |  |  |  |  |  |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage                            | $V_A + = V_D + = V^+ - 10\%$<br>$I_{OUT} = 1.6 \text{ mA}$ |                      | 0.4                                             | 0.4                                           | V (max)              |  |  |  |  |  |  |  |  |

| I <sub>OUT</sub>    | TRI-STATE Output Current                              | $V_{OUT} = 0V$<br>$V_{OUT} = V^{+}$                        | -0.1<br>-0.1         | -3.0<br>3.0                                     | -3.0<br>3.0                                   | μΑ (max)<br>μΑ (max) |  |  |  |  |  |  |  |  |

| +l <sub>sc</sub>    | Output Short Circuit Source Current                   | V <sub>OUT</sub> = 0V                                      | -14                  |                                                 |                                               | mA                   |  |  |  |  |  |  |  |  |

| -I <sub>SC</sub>    | Output Short Circuit Sink Current                     | $V_{OUT} = V_D +$                                          | 16                   |                                                 |                                               | mA                   |  |  |  |  |  |  |  |  |

| POWER               | SUPPLY CHARACTERISTICS                                |                                                            |                      |                                                 |                                               | <u> </u>             |  |  |  |  |  |  |  |  |

| I <sub>D</sub> +    | Digital Supply Current                                | Awake (Active)  CS = HIGH, Powered Down,  CCLK on          | 600                  | 1.5                                             | 2.5                                           | mA (max)<br>μA       |  |  |  |  |  |  |  |  |

|                     |                                                       | CS = HIGH, Powered Down, CCLK off                          | 20                   |                                                 |                                               | μΑ                   |  |  |  |  |  |  |  |  |

| I <sub>A</sub> +    | Positive Analog Supply Current                        | Awake (Active)  CS = HIGH, Powered Down,  CCLK on          | 10                   | 3.0                                             | 4.0                                           | mA (max)<br>μA       |  |  |  |  |  |  |  |  |

|                     |                                                       | CS = HIGH, Powered Down, CCLK off                          | 0.1                  |                                                 |                                               | μΑ                   |  |  |  |  |  |  |  |  |

| I <sub>REF</sub>    | Reference Input Current                               | CS = HIGH, Powered Down, CCLK on                           | 70                   |                                                 |                                               | μΑ                   |  |  |  |  |  |  |  |  |

| 'HEF                | Tions input duriont                                   | CS = HIGH, Powered Down, CCLK off                          | 0.1                  |                                                 |                                               | μΑ                   |  |  |  |  |  |  |  |  |

### **AC Electrical Characteristics**

The following specifications apply for  $(V^+ = V_A^+ = V_D^+ = +5V, V_{REF}^+ = +4.096V, and fully-differential input with fixed 2.048V common-mode voltage) or <math>(V^+ = V_A^+ = V_D^+ = +3.3V, V_{REF}^+ = +2.5V)$  and fully-differential input with fixed 1.250V common-mode voltage),  $V_{REF}^- = 0V$ , 12-bit + sign conversion mode, source impedance for analog inputs,  $V_{REF}^- = 0V$ , 12-bit + sign conversion mode, source impedance for analog inputs,  $V_{REF}^- = 0V$ ,  $V_{REF}^- = 0V$ , 12-bit + sign conversion mode, source impedance for analog inputs,  $V_{REF}^- = 0V$ ,  $V_{REF}^- = 0V$ , 12-bit + sign conversion mode, source impedance for analog inputs,  $V_{REF}^- = 0V$ ,  $V_{REF}^- = 0V$ , 12-bit + sign conversion mode, source impedance for analog inputs,  $V_{REF}^- = 0V$ ,  $V_{REF}^- = 0V$ , 12-bit + sign conversion mode, source impedance for analog inputs,  $V_{REF}^- = 0V$ ,  $V_{REF}^- =$

| Symbol            | Parameter                                             | Conditions              | Typical<br>(Note 10)   | Limits (Note 11)       | Units (Limits) |

|-------------------|-------------------------------------------------------|-------------------------|------------------------|------------------------|----------------|

| f <sub>CK</sub>   | Conversion Clock (CCLK) Frequency                     |                         | 10                     | 5                      | MHz (max)      |

| -CK               | Controller Clock (CCER) Frequency                     |                         | 1                      |                        | MHz (min)      |

| $f_{SK}$          | Serial Data Clock SCLK Frequency                      |                         | 10                     | 5                      | MHz (max)      |

|                   |                                                       |                         | 0                      |                        | Hz (min)       |

|                   | Conversion Clock Duty Cycle                           |                         |                        | 40                     | % (min)        |

|                   | , ,                                                   |                         |                        | 60                     | % (max)        |

|                   | Serial Data Clock Duty Cycle                          |                         |                        | 40                     | % (min)        |

|                   |                                                       |                         |                        | 60                     | % (max)        |

| t <sub>C</sub>    | Conversion Time                                       | 12-Bit + Sign or 12-Bit | 44(t <sub>CK</sub> )   | 44(t <sub>CK</sub> )   | (max)          |

|                   |                                                       |                         |                        | 8.8                    | μs (max)       |

|                   |                                                       |                         | 6(t <sub>CK</sub> )    | 6(t <sub>CK</sub> )    | (min)          |

|                   |                                                       | 6 Cycles Programmed     |                        | 7(t <sub>CK</sub> )    | (max)          |

|                   |                                                       | c c, c.c. c c g. a      |                        | 1.2                    | μs (min)       |

|                   |                                                       |                         |                        | 1.4                    | μs (max)       |

|                   |                                                       |                         | 10(t <sub>CK</sub> )   | 10(t <sub>CK</sub> )   | (min)          |

|                   |                                                       | 10 Cycles Programmed    |                        | 11(t <sub>CK</sub> )   | (max)          |

|                   |                                                       | To Cycles i regianimed  |                        | 2.0                    | μs (min)       |

| t <sub>A</sub>    | Acquisition Time (Note 19)                            |                         |                        | 2.2                    | μs (max)       |

|                   | Acquisition Time (Note 19)                            |                         | 18(t <sub>CK</sub> )   | 18(t <sub>CK</sub> )   | (min)          |

|                   |                                                       | 18 Cycles Programmed    |                        | 19(t <sub>CK</sub> )   | (max)          |

|                   |                                                       | To Cycles Flogrammed    |                        | 3.6                    | μs (min)       |

|                   |                                                       |                         |                        | 3.8                    | μs (max)       |

|                   |                                                       |                         | 34(t <sub>CK</sub> )   | 34(t <sub>CK</sub> )   | (min)          |

|                   |                                                       | 0.4 Cycles Dromanon     |                        | 35(t <sub>CK</sub> )   | (max)          |

|                   |                                                       | 34 Cycles Programmed    |                        | 6.8                    | μs (min)       |

|                   |                                                       |                         |                        | 7.0                    | μs (max)       |

|                   | 0.11.0.12                                             |                         | 4944(t <sub>CK</sub> ) | 4944(t <sub>CK</sub> ) | (max)          |

| t <sub>CAL</sub>  | Self-Calibration Time                                 |                         |                        | 988.8                  | μs (max)       |

|                   | A . 7 T                                               |                         | 76(t <sub>CK</sub> )   | 76(t <sub>CK</sub> )   | (max)          |

| t <sub>AZ</sub>   | Auto-Zero Time                                        |                         |                        | 15.2                   | μs (max)       |

|                   |                                                       |                         | 2(t <sub>CK</sub> )    | 2(t <sub>CK</sub> )    | (min)          |

|                   | Self-Calibration or Auto-Zero                         |                         |                        | 3(t <sub>CK</sub> )    | (max)          |

| t <sub>SYNC</sub> | Synchronization Time from DOR                         |                         |                        | 0.40                   | μs (min)       |

|                   |                                                       |                         |                        | 0.60                   | μs (max)       |

|                   | DOR High Time when $\overline{\text{CS}}$ is Low      |                         | 9(t <sub>SK</sub> )    | 9(t <sub>sk</sub> )    | (max)          |

| t <sub>DOR</sub>  | Continuously for Read Data and Software Power Up/Down |                         |                        | 1.8                    | μs (max)       |

|                   |                                                       |                         | 8(t <sub>SK</sub> )    | 8(t <sub>SK</sub> )    | (max)          |

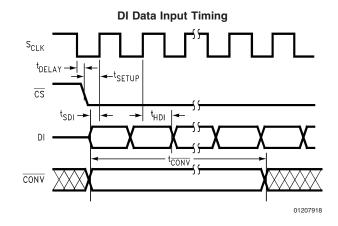

| $t_{CONV}$        | CONV Valid Data Time                                  |                         |                        | 1.6                    | μs (max)       |

### **AC Electrical Characteristics**

The following specifications apply for (V<sup>+</sup> = V<sub>A</sub>+ = V<sub>D</sub>+ = +5V, V<sub>REF</sub>+ = +4.096V, and fully-differential input with fixed 2.048V common-mode voltage) or (V<sup>+</sup> = V<sub>A</sub>+ = V<sub>D</sub>+ = +3.3V, V<sub>REF</sub>+ = +2.5V and fully-differential input with fixed 1.250V common-mode voltage), V<sub>REF</sub>- = 0V, 12-bit + sign conversion mode, source impedance for analog inputs, V<sub>REF</sub>- and V<sub>REF</sub>+  $\leq$  25 $\Omega$ , f<sub>CK</sub> = f<sub>SK</sub> = 5 MHz, and 10 (t<sub>CK</sub>) acquisition time unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> = 25°C. (Note 17) (Continued)

| Symbol                            | Parameter                                                                                 | Conditions               | Typical<br>(Note 10) | Limits<br>(Note 11) | Units<br>(Limits)    |

|-----------------------------------|-------------------------------------------------------------------------------------------|--------------------------|----------------------|---------------------|----------------------|

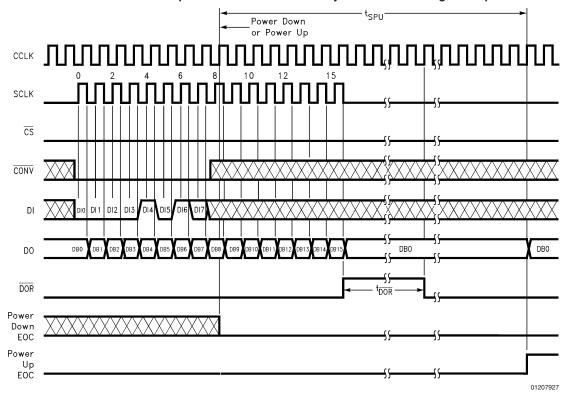

| t <sub>HPU</sub>                  | Hardware Power-Up Time, Time from PD Falling Edge to EOC Rising Edge                      |                          | 500                  | 700                 | μs (max)             |

| t <sub>SPU</sub>                  | Software Power-Up Time, Time from<br>Serial Data Clock Falling Edge to EOC<br>Rising Edge |                          | 500                  | 700                 | μs (max)             |

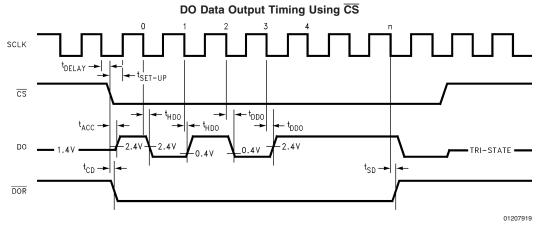

| t <sub>ACC</sub>                  | Access Time Delay from $\overline{\text{CS}}$ Falling Edge to DO Data Valid               |                          | 25                   | 60                  | ns (max)             |

| t <sub>SET-UP</sub>               | Set-Up Time of $\overline{\text{CS}}$ Falling Edge to Serial Data Clock Rising Edge       |                          |                      | 50                  | ns (min)             |

| t <sub>DELAY</sub>                | Delay from SCLK Falling Edge to $\overline{\text{CS}}$ Falling Edge                       |                          | 0                    | 5                   | ns (min)             |

| t <sub>1H</sub> , t <sub>OH</sub> | Delay from CS Rising Edge to DO TRI-STATE                                                 | $R_L = 3k, C_L = 100 pF$ | 70                   | 100                 | ns (max)             |

| t <sub>HDI</sub>                  | DI Hold Time from Serial Data Clock<br>Rising Edge                                        |                          | 5                    | 15                  | ns (max)             |

| t <sub>SDI</sub>                  | DI Set-Up Time from Serial Data Clock<br>Rising Edge                                      |                          | 5                    | 10                  | ns (min)             |

| t <sub>HDO</sub>                  | DO Hold Time from Serial Data Clock<br>Falling Edge                                       | $R_L = 3k, C_L = 100 pF$ | 35                   | 65<br>5             | ns (max)<br>ns (min) |

| t <sub>DDO</sub>                  | Delay from Serial Data Clock Falling Edge to DO Data Valid                                |                          | 50                   | 90                  | ns (max)             |

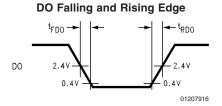

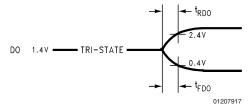

| t <sub>RDO</sub>                  | DO Rise Time, TRI-STATE to High DO Rise Time, Low to High                                 | $R_L = 3k, C_L = 100 pF$ | 10<br>10             | 40<br>40            | ns (max)<br>ns (max) |

| t <sub>FDO</sub>                  | DO Fall Time, TRI-STATE to Low DO Fall Time, High to Low                                  | $R_L = 3k, C_L = 100 pF$ | 15<br>15             | 40<br>40            | ns (max)<br>ns (max) |

| t <sub>CD</sub>                   | Delay from CS Falling Edge to DOR Falling Edge                                            |                          | 45                   | 80                  | ns (max)             |

| t <sub>SD</sub>                   | Delay from Serial Data Clock Falling Edge to DOR Rising Edge                              |                          | 45                   | 80                  | ns (max)             |

| C <sub>IN</sub>                   | Capacitance of Logic Inputs                                                               |                          | 20                   |                     | pF                   |

| C <sub>OUT</sub>                  | Capacitance of Logic Outputs                                                              |                          | 20                   |                     | pF                   |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

**Note 3:** When the input voltage  $(V_{IN})$  at any pin exceeds the power supplies  $(V_{IN} < GND \text{ or } V_{IN} > V_{A^+} \text{ or } V_{D^+})$ , the current at that pin should be limited to 30 mA. The 120 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 30 mA to four.

**Note 4:** The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_J$ max,  $\theta_{JA}$  and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_J$ max  $- T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For this device,  $T_J$ max = 150°C.

Note 5: The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin.

Note 6: See AN450 "Surface Mounting Methods and Their Effect on Product Reliability" or the section titled "Surface Mount" found in any post 1986 National Semiconductor Linear Data Book for other methods of soldering surface mount devices.

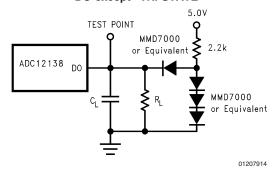

Note 7: Two on-chip diodes are tied to each analog input through a series resistor as shown below. Input voltage magnitude up to 5V above  $V_A+$  or 5V below GND will not damage this device. However, errors in the A/D conversion can occur (if these diodes are forward biased by more than 50 mV) if the input voltage magnitude of selected or unselected analog input go above  $V_A+$  or below GND by more than 50 mV. As an example, if  $V_A+$  is 4.5  $V_{DC}$ , full-scale input voltage must be  $\leq$ 4.55  $V_{DC}$  to ensure accurate conversions.

### AC Electrical Characteristics (Continued)

Note 8: To guarantee accuracy, it is required that the V<sub>A</sub>+ and V<sub>D</sub>+ be connected together to the same power supply with separate bypass capacitors at each V<sup>+</sup> pin.

Note 9: With the test condition for  $V_{REF}$  ( $V_{REF^+}$  –  $V_{REF^-}$ ) given as +4.096V, the 12-bit LSB is 1.0 mV. For  $V_{REF}$  = 2.5V, the 12-bit LSB is 610  $\mu$ V.

Note 10: Typical figures are at  $T_J = T_A = 25$ °C and represent most likely parametric norm.

Note 11: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

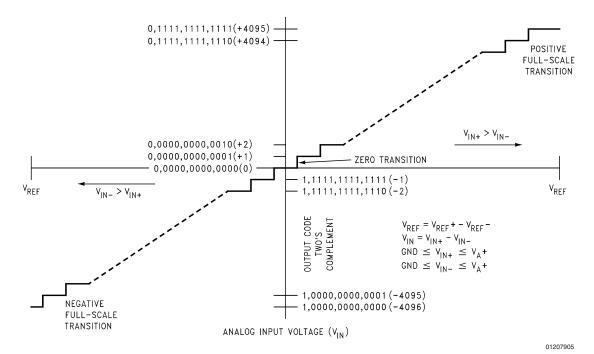

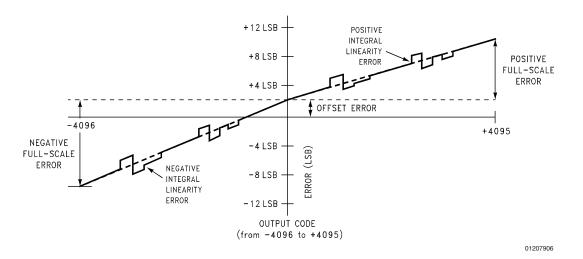

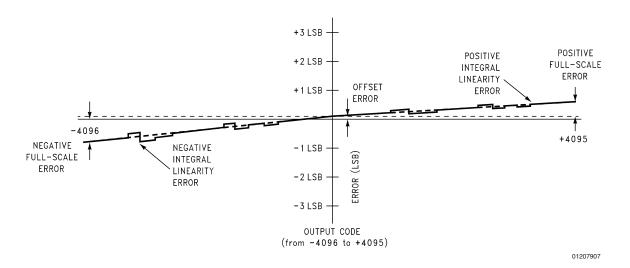

Note 12: Positive integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive full-scale and zero. For negative integral linearity error, the straight line passes through negative full-scale and zero (see Figure 2 and Figure 3).

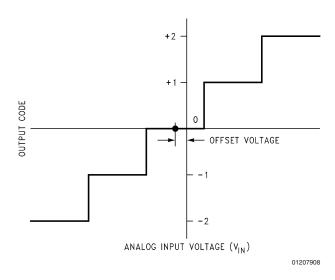

Note 13: Zero error is a measure of the deviation from the mid-scale voltage (a code of zero), expressed in LSB. It is the average value of the code transitions between -1 to 0 and 0 to +1 (see Figure 4).

Note 14: Total unadjusted error includes offset, full-scale, linearity and multiplexer errors.

Note 15: The DC common-mode error is measured in the differential multiplexer mode with the assigned positive and negative input channels shorted together.

Note 16: Channel leakage current is measured after the channel selection.

Note 17: Timing specifications are tested at the TTL logic levels, V<sub>OL</sub> = 0.4V for a falling edge and V<sub>OL</sub> = 2.4V for a rising edge. TRI-STATE output voltage is forced to 1.4V.

Note 18: The ADC12130 family's self-calibration technique ensures linearity and offset errors as specified, but noise inherent in the self-calibration process will result in a maximum repeatability uncertainty of 0.2 LSB.

Note 19: If SCLK and CCLK are driven from the same clock source, then t<sub>A</sub> is 6, 10, 18 or 34 clock periods minimum and maximum.

Note 20: The "12-Bit Conversion of Offset" and "12-Bit Conversion of Full-Scale" modes are intended to test the functionality of the device. Therefore, the output data from these modes are not an indication of the accuracy of a conversion result.

FIGURE 1. Transfer Characteristic

### AC Electrical Characteristics (Continued)

FIGURE 2. Simplified Error Curve vs. Output Code without Auto-Calibration or Auto-Zero Cycles

FIGURE 3. Simplified Error Curve vs. Output Code after Auto-Calibration Cycle

### AC Electrical Characteristics (Continued)

FIGURE 4. Offset or Zero Error Voltage

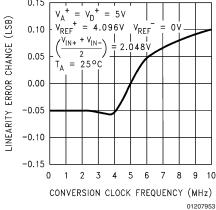

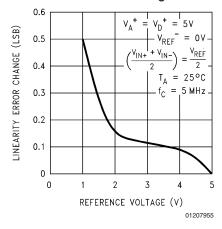

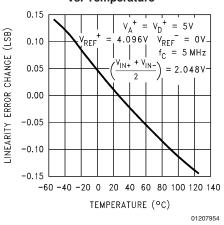

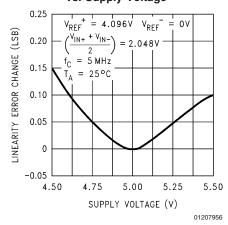

**Typical Performance Characteristics** The following curves apply for 12-bit + sign mode after autocalibration unless otherwise specified.

Linearity Error Change vs. Reference Voltage

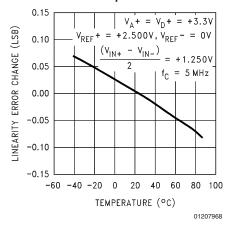

Linearity Error Change vs. Temperature

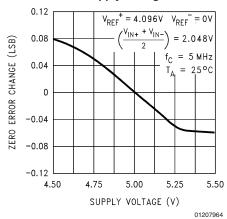

Linearity Error Change vs. Supply Voltage

### Typical Performance Characteristics The following curves apply for 12-bit + sign mode after auto-calibration unless otherwise specified. (Continued)

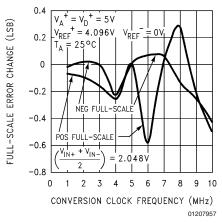

### **Full-Scale Error Change** vs. Clock Frequency

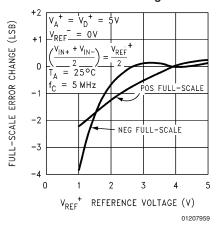

### **Full-Scale Error Change** vs. Reference Voltage

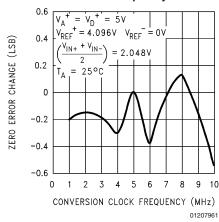

### **Zero Error Change** vs. Clock Frequency

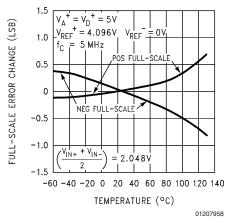

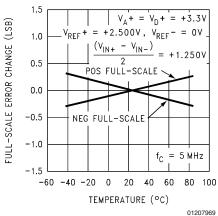

### **Full-Scale Error Change** vs. Temperature

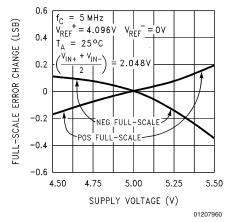

### **Full-Scale Error Change** vs. Supply Voltage

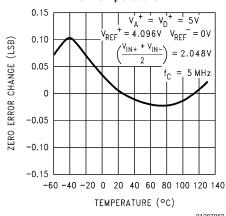

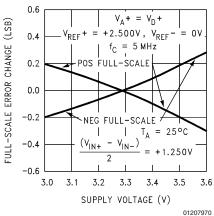

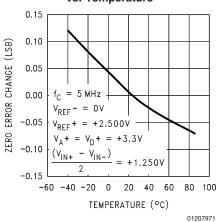

### **Zero Error Change** vs. Temperature

01207962

# **Typical Performance Characteristics** The following curves apply for 12-bit + sign mode after auto-calibration unless otherwise specified. (Continued)

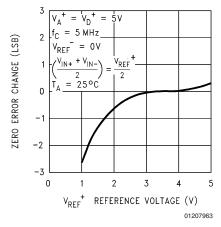

# Zero Error Change vs. Reference Voltage

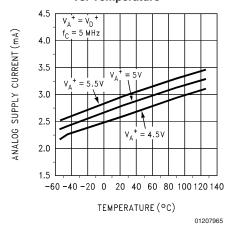

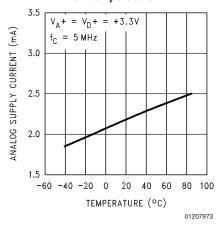

# Analog Supply Current vs. Temperature

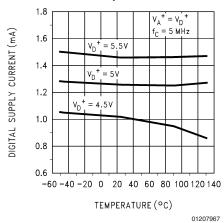

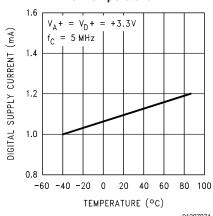

# Digital Supply Current vs. Temperature

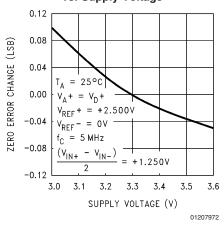

# Zero Error Change vs. Supply Voltage

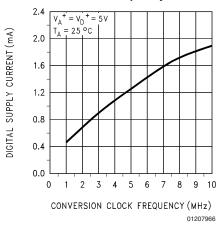

# Digital Supply Current vs. Clock Frequency

# Linearity Error Change vs. Temperature

### Typical Performance Characteristics The following curves apply for 12-bit + sign mode after auto-calibration unless otherwise specified. (Continued)

### **Full-Scale Error Change** vs. Temperature

### **Full-Scale Error Change** vs. Supply Voltage

**Zero Error Change** vs. Temperature

**Zero Error Change** vs. Supply Voltage

**Analog Supply Current** vs. Temperature

### **Digital Supply Current** vs. Temperature

01207974

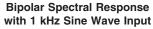

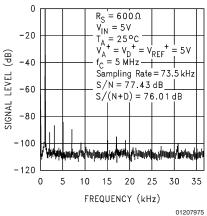

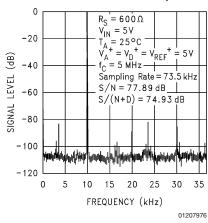

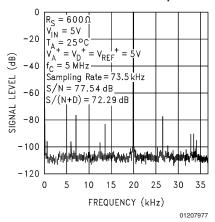

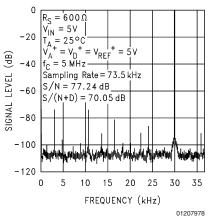

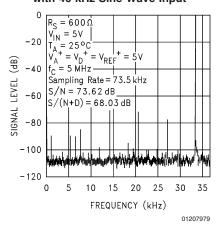

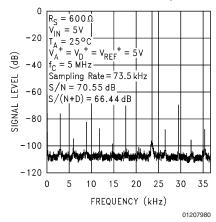

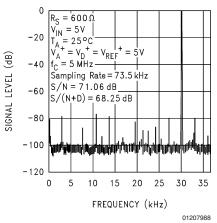

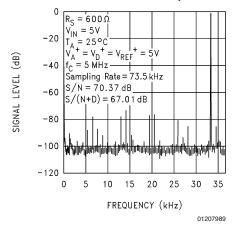

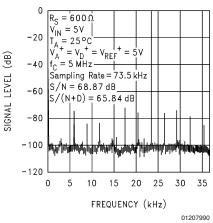

### Typical Dynamic Performance Characteristics The following curves apply for 12-bit + sign

mode after auto-calibration unless otherwise specified.

### **Bipolar Spectral Response** with 10 kHz Sine Wave Input

### **Bipolar Spectral Response** with 20 kHz Sine Wave Input

### **Bipolar Spectral Response** with 30 kHz Sine Wave Input

### **Bipolar Spectral Response** with 40 kHz Sine Wave Input

### **Bipolar Spectral Response** with 50 kHz Sine Wave Input

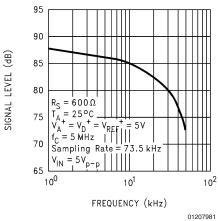

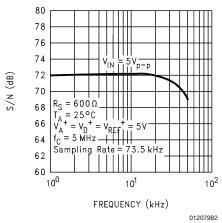

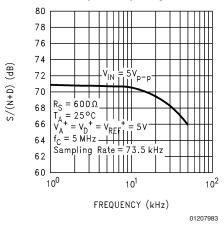

# **Typical Dynamic Performance Characteristics** The following curves apply for 12-bit + sign mode after auto-calibration unless otherwise specified. (Continued)

# Unipolar Signal-to-Noise Ratio vs. Input Frequency

### Unipolar Signal-to-Noise + Distortion Ratio vs. Input Frequency

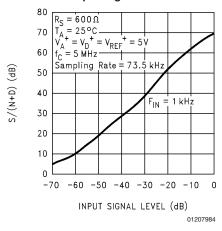

### Unipolar Signal-to-Noise + Distortion Ratio vs. Input Signal Level

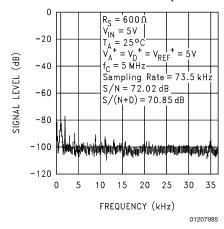

# Unipolar Spectral Response with 1 kHz Sine Wave Input

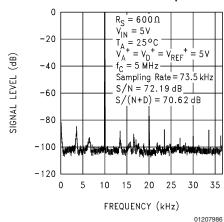

# Unipolar Spectral Response with 10 kHz Sine Wave Input

# **Typical Dynamic Performance Characteristics** The following curves apply for 12-bit + sign mode after auto-calibration unless otherwise specified. (Continued)

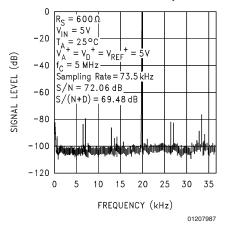

# Unipolar Spectral Response with 20 kHz Sine Wave Input

# Unipolar Spectral Response with 30 kHz Sine Wave Input

# Unipolar Spectral Response with 40 kHz Sine Wave Input

# Unipolar Spectral Response with 50 kHz Sine Wave Input

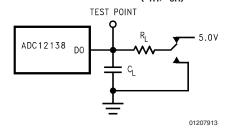

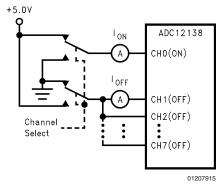

### **Test Circuits**

### DO "TRI-STATE" (t<sub>1H</sub>, t<sub>0H</sub>)

### DO except "TRI-STATE"

### Test Circuits (Continued)

### **Leakage Current**

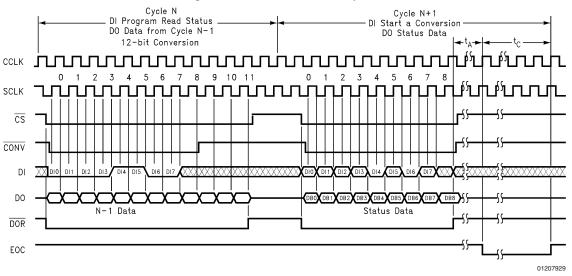

## **Timing Diagrams**

### DO "TRI-STATE" Falling and Rising Edge

Note: DO output data is not valid during this cycle.

### Timing Diagrams (Continued)

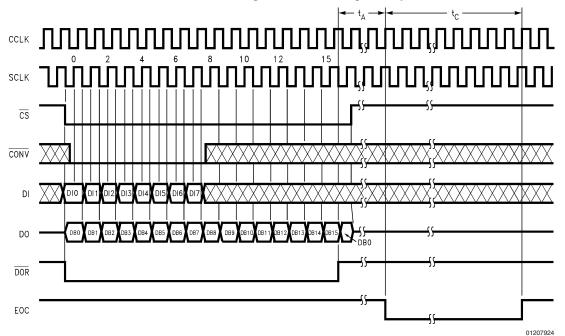

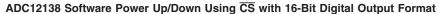

### ADC12138 Conversion Using $\overline{\text{CS}}$ with 16-Bit Digital Output Format

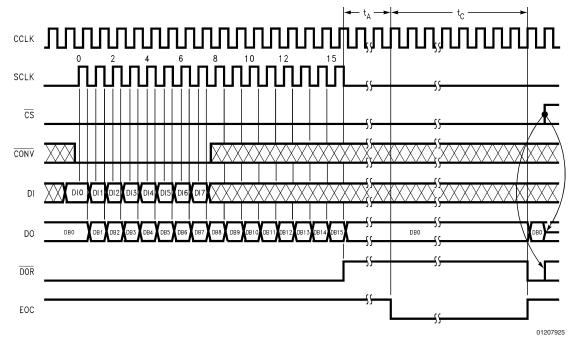

### ADC12138 Conversion with $\overline{\text{CS}}$ Continuously Low and 16-Bit Digital Output Format

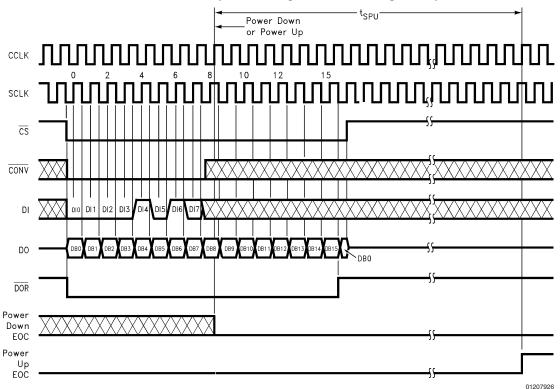

### ADC12138 Software Power Up/Down with $\overline{\text{CS}}$ Continuously Low and 16-Bit Digital Output Format

23

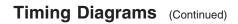

### Timing Diagrams (Continued)

### ADC12138 Hardware Power Up/Down

Note: Hardware power up/down may occur at any time. If PD is high while a conversion is in progress that conversion will be corrupted and erroneous data will be stored in the output shift register.

### ADC12138 Configuration Modification — Example of a Status Read

\*Tantalum

FIGURE 5. Recommended Power Supply Bypassing and Grounding

FIGURE 6. Protecting the MUXOUT1, MUXOUT2, A/DIN1 and A/DIN2 Analog Pins

<sup>\*\*</sup>Monolithic Ceramic or better

# Format and Set-Up Tables

### **TABLE 1. Data Out Formats**

| DO Formats |       | DB0                      | DB1  | DB2 | DB3 | DB4 | DB5  | DB6 | DB7 | DB8 | DB9 | DB10 | DB11 | DB12 | DB13 | DB14 | DB15 | DB16 |     |

|------------|-------|--------------------------|------|-----|-----|-----|------|-----|-----|-----|-----|------|------|------|------|------|------|------|-----|

|            | MSB   | 17<br>Bits               | Х    | Х   | Х   | Х   | Sign | MSB | 10  | 9   | 8   | 7    | 6    | 5    | 4    | 3    | 2    | 1    | LSB |

| with       | First | 13<br>Bits               | Sing | MSB | 10  | 9   | 8    | 7   | 6   | 5   | 4   | 3    | 2    | 1    | LSB  |      |      |      |     |

| Sign       | LSB   | 17<br>Bits               | LSB  | 1   | 2   | 3   | 4    | 5   | 6   | 7   | 8   | 9    | 10   | MSB  | Sign | Х    | Х    | Х    | Х   |

|            | First | 13<br>Bits               | LSB  | 1   | 2   | 3   | 4    | 5   | 6   | 7   | 8   | 9    | 10   | MSB  | Sign |      |      |      |     |

|            | MSB   | 16                       | 0    | 0   | 0   | 0   | MSB  | 10  | 9   | 8   | 7   | 6    | 5    | 4    | 3    | 2    | 1    | LSB  |     |

| without    | First | 12<br>Bits               | MSB  | 10  | 9   | 8   | 7    | 6   | 5   | 4   | 3   | 2    | 1    | LSB  |      |      |      |      |     |

| Sign       | LSB   | 16<br>Bits               | LSB  | 1   | 2   | 3   | 4    | 5   | 6   | 7   | 8   | 9    | 10   | MSB  | 0    | 0    | 0    | 0    |     |

|            | First | 12<br>Bits               | LSB  | 1   | 2   | 3   | 4    | 5   | 6   | 7   | 8   | 9    | 10   | MSB  |      |      |      |      |     |

|            |       | 16<br>Bits<br>12<br>Bits |      | •   |     |     |      |     |     |     |     |      |      |      | 0    | 0    | 0    | 0    |     |

X = High or Low state.

### TABLE 2. ADC12138 Multiplexer Addressing

| М   | MUX Address |     |     |     | Analog Channel Addressed and Assignment with A/DIN1 tied to MUXOUT1 and A/DIN2 tied to MUXOUT2 |     |     |     |     |     |     |     | Pola   | Input<br>arity<br>nment | Cha     | er Output<br>nnel<br>nment | Mode         |

|-----|-------------|-----|-----|-----|------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--------|-------------------------|---------|----------------------------|--------------|

| DI0 | DI1         | DI2 | DI3 | CH0 | CH1                                                                                            | CH2 | СНЗ | CH4 | CH5 | СН6 | CH7 | СОМ | A/DIN1 | A/DIN2                  | MUXOUT1 | MUXOUT2                    |              |

| L   | L           | L   | L   | +   | _                                                                                              |     |     |     |     |     |     |     | +      | _                       | CH0     | CH1                        |              |

| L   | L           | L   | Н   |     |                                                                                                | +   | _   |     |     |     |     |     | +      | _                       | CH2     | CH3                        |              |

| L   | L           | Н   | L   |     |                                                                                                |     |     | +   | _   |     |     |     | +      | _                       | CH4     | CH5                        |              |

| L   | L           | Н   | Н   |     |                                                                                                |     |     |     |     | +   | _   |     | +      | _                       | CH6     | CH7                        | Differential |

| L   | Н           | L   | L   | _   | +                                                                                              |     |     |     |     |     |     |     | _      | +                       | CH0     | CH1                        | Dillerential |

| L   | Н           | L   | Н   |     |                                                                                                | _   | +   |     |     |     |     |     | _      | +                       | CH2     | CH3                        |              |

| L   | Н           | Н   | L   |     |                                                                                                |     |     | _   | +   |     |     |     | _      | +                       | CH4     | CH5                        |              |

| L   | Н           | Н   | Н   |     |                                                                                                |     |     |     |     | _   | +   |     | _      | +                       | CH6     | CH7                        |              |

| Н   | L           | L   | L   | +   |                                                                                                |     |     |     |     |     |     | _   | +      | _                       | CH0     | COM                        |              |

| Н   | L           | L   | Н   |     |                                                                                                | +   |     |     |     |     |     | _   | +      | _                       | CH2     | СОМ                        |              |

| Н   | L           | Н   | L   |     |                                                                                                |     |     | +   |     |     |     | _   | +      | _                       | CH4     | СОМ                        |              |

| Н   | L           | Н   | Н   |     |                                                                                                |     |     |     |     | +   |     | _   | +      | _                       | CH6     | СОМ                        | Cinals Ended |

| Н   | Н           | L   | L   |     | +                                                                                              |     |     |     |     |     |     | _   | +      | _                       | CH1     | СОМ                        | Single-Ended |

| Н   | Н           | L   | Н   |     |                                                                                                |     | +   |     |     |     |     | _   | +      | _                       | CH3     | СОМ                        |              |

| Н   | Н           | Н   | L   |     |                                                                                                |     |     |     | +   |     |     | _   | +      | _                       | CH5     | COM                        |              |

| Н   | Н           | Н   | Н   |     |                                                                                                |     |     |     |     |     | +   | -   | +      | -                       | CH7     | СОМ                        |              |

### Format and Set-Up Tables (Continued)

TABLE 3. ADC12130 and ADC12132\* Multiplexer Addressing

|     | UX<br>Iress | Analog Channel Addressed and Assignment with A/DIN1 tied to MUXOUT1 and A/DIN2 tied to MUXOUT2 |     |     | t Polarity<br>nment | Multiplex<br>Channel A | Mode    |         |              |  |

|-----|-------------|------------------------------------------------------------------------------------------------|-----|-----|---------------------|------------------------|---------|---------|--------------|--|

| DI0 | DI1         | CH0                                                                                            | CH1 | СОМ | A/DIN1              | A/DIN2                 | MUXOUT1 | MUXOUT2 |              |  |

| L   | L           | +                                                                                              | _   |     | +                   | -                      | CH0     | CH1     | Differential |  |

| L   | н           | _                                                                                              | +   |     | _                   | +                      | CH0     | CH1     | Differential |  |

| Н   | L           | +                                                                                              |     | -   | +                   | -                      | CH0     | COM     | Cingle Ended |  |

| Н   | н           |                                                                                                | +   | _   | +                   | _                      | CH1     | СОМ     | Single-Ended |  |

Note: ADC12130 do not have A/DIN1, A/DIN2, MUXOUT1 and MUXOUT2 pins.

**TABLE 4. Mode Programming**

| ADC12138                      | DI0 | DI1     | DI2    | DI3   | DI4 | DI5 | DI6 | DI7 |                                              | DO Format                  |  |

|-------------------------------|-----|---------|--------|-------|-----|-----|-----|-----|----------------------------------------------|----------------------------|--|

| ADC12130<br>and<br>ADC12132 * | DI0 | DI1     |        |       | DI2 | DI3 | DI4 | DI5 | Mode Selected<br>(Current)                   | (next Conversion<br>Cycle) |  |

|                               | See | Table 2 | or Tab | ole 3 | L   | L   | L   | L   | 12 Bit Conversion                            | 12 or 13 Bit MSB First     |  |

|                               | See | Table 2 | or Tab | ole 3 | L   | L   | L   | Н   | 12 Bit Conversion                            | 16 or 17 Bit MSB First     |  |

|                               | See | Table 2 | or Tab | ole 3 | L   | Н   | L   | L   | 12 Bit Conversion                            | 12 or 13 Bit LSB First     |  |

|                               | See | Table 2 | or Tab | ole 3 | L   | Н   | L   | Н   | 12 Bit Conversion                            | 16 or 17 Bit LSB First     |  |

|                               | L   | L       | L      | L     | Н   | L   | L   | L   | Auto Cal                                     | No Change                  |  |

|                               | L   | L       | L      | L     | Н   | L   | L   | Н   | Auto Zero                                    | No Change                  |  |

|                               | L   | L       | L      | L     | Н   | L   | Η   | L   | Power Up                                     | No Change                  |  |

|                               | L   | L       | L      | L     | Н   | L   | Н   | Н   | Power Down                                   | No Change                  |  |

|                               | L   | L       | L      | L     | Н   | Н   | L   | L   | Read Status Register                         | No Change                  |  |

|                               | L   | L       | L      | L     | Н   | Н   | L   | Н   | Data Out without Sign                        | No Change                  |  |

|                               | Н   | L       | L      | L     | Н   | Н   | L   | Н   | Data Out with Sign                           | No Change                  |  |

|                               | L   | L       | L      | L     | Н   | Н   | Η   | L   | Acquisition Time — 6 CCLK Cycles             | No Change                  |  |

|                               | L   | Н       | L      | L     | Н   | Н   | Η   | L   | Acquisition Time — 10 CCLK Cycles            | No Change                  |  |

|                               | Н   | L       | L      | L     | Н   | Н   | Η   | L   | Acquisition Time — 18 CCLK Cycles            | No Change                  |  |

|                               | Н   | Н       | L      | L     | Н   | Н   | Η   | L   | Acquisition Time — 34 CCLK Cycles            | No Change                  |  |

|                               | L   | L       | L      | L     | Н   | Н   | Н   | Н   | User Mode                                    | No Change                  |  |

|                               | Н   | Х       | Х      | Х     | Н   | Н   | Н   | Н   | Test Mode<br>(CH1-CH7 become Active Outputs) | No Change                  |  |

Note: The A/D powers up with no Auto Cal, no Auto Zero, 10 CCLK acquisition time, 12-bit + sign conversion, power up, 12- or 13-bit MSB First, and user mode. X = Don't Care

TABLE 5. Conversion/Read Data Only Mode Programming

| CS | CONV | PD | Mode                                           |

|----|------|----|------------------------------------------------|

| L  | L    | L  | See Table 4 for Mode                           |

| L  | Н    | L  | Read Only (Previous DO Format). No Conversion. |

| Н  | Χ    | L  | Idle                                           |

| X  | Х    | Н  | Power Down                                     |

X = Don't Care

<sup>\*</sup> ADC12132 is obsolete; shown for reference only.

<sup>\*</sup> ADC12132 is obsolete; shown for reference only.

# Format and Set-Up Tables (Continued)

### TABLE 6. Status Register

| Status Bit | DB0         | DB1          | DB2       | DB3      | DB4                     | DB5         | DB6         | DB7            | DB8        |  |  |  |  |

|------------|-------------|--------------|-----------|----------|-------------------------|-------------|-------------|----------------|------------|--|--|--|--|

| Location   |             |              |           |          |                         |             |             |                |            |  |  |  |  |

| Status Bit | PU          | PD           | Cal       |          | 12 or 13                | 16 or 17    | Sign        | Justification  | Test Mode  |  |  |  |  |

|            | [           | Device Statu | s         |          | DO Output Format Status |             |             |                |            |  |  |  |  |

|            | "High"      | "High"       | "High"    | Not used | "High"                  | "High"      | "High"      | When "High"    | When       |  |  |  |  |

| Function   | indicates a | indicates a  | indicates |          | indicates a             | indicates a | indicates   | the            | "High" the |  |  |  |  |

|            | Power Up    | Power        | an        |          | 12 or 13                | 16 or 17    | that the    | conversion     | device is  |  |  |  |  |

|            | Sequence    | Down         | Auto-Cal  |          | bit format              | bit format  | sign bit is | result will be | in test    |  |  |  |  |

|            | is in       | Sequence     | Sequence  |          |                         |             | included.   | output MSB     | mode.      |  |  |  |  |

|            | progress    | is in        | is in     |          |                         |             | When        | first. When    | When       |  |  |  |  |

|            |             | progress     | progress  |          |                         |             | "Low" the   | "Low" the      | "Low" the  |  |  |  |  |

|            |             |              |           |          |                         |             | sign bit is | result will be | device is  |  |  |  |  |

|            |             |              |           |          |                         |             | not         | output LSB     | in user    |  |  |  |  |

|            |             |              |           |          |                         |             | included.   | first.         | mode.      |  |  |  |  |

### **Application Information**

### 1.0 DIGITAL INTERFACE

### 1.1 Interface Concepts

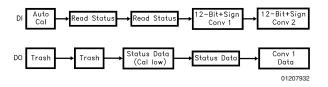

The example in *Figure 7* shows a typical sequence of events after the power is applied to the ADC12130/2/8:

FIGURE 7. Typical Power Supply Power Up Sequence

The first instruction input to the A/D via DI initiates Auto Cal. The data output on DO at that time is meaningless and is completely random. To determine whether the Auto Cal has been completed, a read status instruction is issued to the A/D. Again the data output at that time has no significance since the Auto Cal procedure modifies the data in the output shift register. To retrieve the status information, an additional read status instruction is issued to the A/D. At this time the status data is available on DO. If the Cal signal in the status word, is low Auto Cal has been completed. Therefore, the next instruction issued can start a conversion. The data output at this time is again status information. To keep noise from corrupting the A/D conversion, status can not be read during a conversion. If  $\overline{\text{CS}}$  is strobed and is brought low during a conversion, that conversion is prematurely ended. EOC can be used to determine the end of a conversion or the A/D controller can keep track in software of when it would be appropriate to communicate to the A/D again. Once it has been determined that the A/D has completed a conversion, another instruction can be transmitted to the A/D. The data from this conversion can be accessed when the next instruction is issued to the A/D.

Note, when  $\overline{CS}$  is low continuously it is important to transmit the exact number of SCLK cycles, as shown in the timing diagrams. Not doing so will desynchronize the serial communication to the A/D. (See Section 1.3.)

### 1.2 Changing Configuration

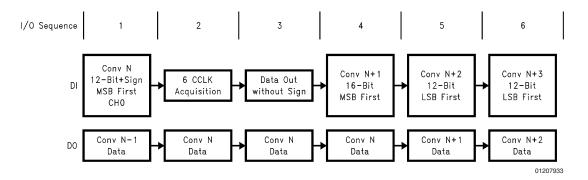

The configuration of the ADC12130/2/8 on power up defaults to 12-bit plus sign resolution, 12- or 13-bit MSB First, 10 CCLK acquisition time, user mode, no Auto Cal, no Auto Zero, and power up mode. Changing the acquisition time and turning the sign bit on and off requires an 8-bit instruction to be issued to the ADC. This instruction will not start a conversion. The instructions that select a multiplexer address and format the output data do start a conversion. Figure 8 describes an example of changing the configuration of the ADC12130/2/8.

During I/O sequence 1, the instruction on DI configures the ADC12130/2/8 to do a conversion with 12-bit +sign resolution. Notice that when the 6 CCLK Acquisition and Data Out without Sign instructions are issued to the ADC, I/O sequences 2 and 3, a new conversion is not started. The data output during these instructions is from conversion N which was started during I/O sequence 1. The Configuration Modification timing diagram describes in detail the sequence of events necessary for a Data Out without Sign, Data Out with Sign, or 6/10/18/34 CCLK Acquisition time mode selection. Table 4 describes the actual data necessary to be input to

the ADC to accomplish this configuration modification. The next instruction, shown in *Figure 8*, issued to the A/D starts conversion N+1 with 16-bit format and 12 bits of resolution formatted MSB first. Again the data output during this I/O cycle is the data from conversion N.

The number of SCLKs applied to the A/D during any conversion I/O sequence should vary in accord with the data out word format chosen during the previous conversion I/O sequence. The various formats and resolutions available are shown in *Table 1*. In *Figure 8*, since 16-bit without sign MSB first format was chosen during I/O sequence 4, the number of SCLKs required during I/O sequence 5 is 16. In the following I/O sequence the format changes to 12-bit without sign MSB first; therefore the number of SCLKs required during I/O sequence 6 changes accordingly to 12.

### 1.3 CS Low Continuously Considerations

When  $\overline{\text{CS}}$  is continuously low, it is important to transmit the exact number of SCLK pulses that the ADC expects. Not doing so will desynchronize the serial communications to the ADC. When the supply power is first applied to the ADC, it will expect to see 13 SCLK pulses for each I/O transmission. The number of SCLK pulses that the ADC expects to see is the same as the digital output word length. The digital output word length is controlled by the Data Out (DO) format. The DO format maybe changed any time a conversion is started or when the sign bit is turned on or off. The table below details out the number of clock periods required for different DO formats:

| DO Format                |          | Number of<br>SCLKs<br>Expected |

|--------------------------|----------|--------------------------------|

| 12-Bit MSB or LSB First  | SIGN OFF | 12                             |

| 12-DIL WISD OF LSD FIISL | SIGN ON  | 13                             |

| 16-Bit MSB or LSB first  | SIGN OFF | 16                             |

| 10-DIL WISD OF LSD IIISL | SIGN ON  | 17                             |

If erroneous SCLK pulses desynchronize the communications, the simplest way to recover is by cycling the power supply to the device. Not being able to easily resynchronize the device is a shortcoming of leaving  $\overline{CS}$  low continuously.

The number of clock pulses required for an I/O exchange may be different for the case when  $\overline{\text{CS}}$  is left low continuously vs. the case when  $\overline{\text{CS}}$  is cycled. Take the I/O sequence detailed in Figure 7 (Typical Power Supply Sequence) as an example. The table below lists the number of SCLK pulses required for each instruction:

| Instruction          | CS Low<br>Continuously | CS Strobed |

|----------------------|------------------------|------------|

| Auto Cal             | 13 SCLKs               | 8 SCLKs    |

| Read Status          | 13 SCLKs               | 8 SCLKs    |

| Read Status          | 13 SCLKs               | 8 SCLKs    |

| 12-Bit + Sign Conv 1 | 13 SCLKs               | 8 SCLKs    |

| 12-Bit + Sign Conv 2 | 13 SCLKs               | 13 SCLKs   |

### 1.4 Analog Input Channel Selection

The data input on DI also selects the channel configuration (see *Table 2*, *Table 3* and *Table 4*). In *Figure 8* the only times when the channel configuration could be modified would be during I/O sequences 1, 4, 5 and 6. Input channels are reselected before the start of each new conversion. Shown