## SN74ALVCHG162280 16-BIT TO 32-BIT REGISTERED BUS EXCHANGER WITH BYTE MASKS AND 3-STATE OUTPUTS

SCES093D-FEBRUARY 1997-REVISED OCTOBER 2004

#### **FEATURES**

- Member of the Texas Instruments Widebus™

Family

- EPIC<sup>™</sup> (Enhanced-Performance Implanted CMOS) Sub-Micron Process

- A-Port Outputs Have Equivalent 50- $\Omega$  Series Resistors and B-Port Outputs Have Equivalent 20- $\Omega$  Series Resistors, So No External Resistors Are Required

- ESD Protection Exceeds 2000 V Per MIL-STD-883, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R = 0)

- Latch-Up Performance Exceeds 250 mA Per JESD 17

- Bus Hold on Data Inputs Eliminates the Need for External Pullup/Pulldown Resistors

- Packaged in Thin Very Small-Outline Package

NOTE: For order entry, the DBB package is abbreviated to G. For tape and reel, the DBBR package is abbreviated to GR.

#### **DESCRIPTION**

The SN74ALVCHG162280 is a 16-bit to 32-bit registered bus exchanger. This device is intended for use in applications where data must be transferred from a narrow high-speed bus to a wide lower-frequency bus. It is designed specifically for low-voltage (3.3-V)  $V_{\rm CC}$  operation.

The device provides synchronous data exchange between the two ports, A and B. Data is stored in the internal registers on the low-to-high transition of the clock (CLK) input. For data transfer in the B-to-A direction, the select (SEL) input selects 1B or 2B data for the A outputs.

For data transfer in the A-to-B direction, a two-stage pipeline is provided in the 1B path, with a single storage register in the 2B path. Data flow is controlled by the active-low output-enable ( $\overline{OE}$ ) and direction-control (DIR) inputs. DIR is registered to synchronize the bus direction changes with the clock.

Two mask bits are provided for both data bytes. The data (D) outputs are controlled by  $\overline{\text{OE}}$ .

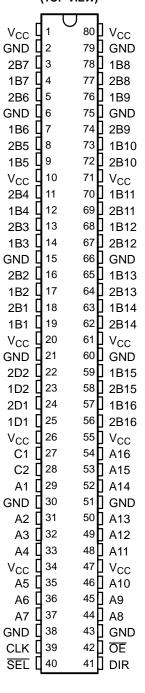

# DBB PACKAGE (TOP VIEW)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Widebus, EPIC are trademarks of Texas Instruments.

## SN74ALVCHG162280 16-BIT TO 32-BIT REGISTERED BUS EXCHANGER WITH BYTE MASKS AND 3-STATE OUTPUTS

SCES093D-FEBRUARY 1997-REVISED OCTOBER 2004

## **DESCRIPTION (CONTINUED)**

The A-port N-channel output transistors are sized at 450  $\mu$ m, and the P-channel output transistors are sized at 700  $\mu$ m. All A-port outputs have equivalent 50- $\Omega$  series resistors. The B-port N-channel output transistors are sized at 225  $\mu$ m, and the P-channel output transistors are sized at 560  $\mu$ m. All B-port outputs have equivalent 20- $\Omega$  series resistors.

To ensure the high-impedance state during power up or power down,  $\overline{OE}$  should be tied to  $V_{CC}$  through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

The switching characteristics are based on 25-pF (A port) and 80-pF (B and D ports) loads, but are tested with the standard 50-pF load.

The SN74ALVCHG162280 is characterized for operation from 0°C to 70°C.

SCES093D-FEBRUARY 1997-REVISED OCTOBER 2004

#### **FUNCTION TABLES**

### A-TO-B STORAGE (OE = L, DIR = H)

| INPUTS |            |   | OUTI                           | PUTS                           |

|--------|------------|---|--------------------------------|--------------------------------|

| SEL    | CLK        | Α | 1B                             | 2B                             |

| Н      | Х          | Х | 1B <sub>0</sub> <sup>(1)</sup> | 2B <sub>0</sub> <sup>(1)</sup> |

| L      | $\uparrow$ | L | L <sup>(2)</sup>               | L                              |

| L      | $\uparrow$ | Н | H <sup>(2)</sup>               | Н                              |

- Output level before indicated steady-state input conditions were established

- (2) Two CLK edges are needed to propagate the data.

#### B-TO-A STORAGE (OE = L, DIR = L)

|     | INPUTS |    |    |                  |  |

|-----|--------|----|----|------------------|--|

| CLK | SEL    | 1B | 2B | Α                |  |

| 1   | Н      | Х  | L  | L(1)             |  |

| 1   | Н      | Χ  | Н  | H <sup>(1)</sup> |  |

| 1   | L      | L  | Χ  | L                |  |

| 1   | L      | Н  | Χ  | Н                |  |

(1) Two CLK edges are needed to propagate the data. The data is loaded in the first register when SEL is low and propagates to the second register when SEL is high.

## C-TO-D STORAGE (OE = L)

| INPUTS |            |   | OUTI                           | PUTS                           |

|--------|------------|---|--------------------------------|--------------------------------|

| SEL    | CLK        | С | 1D                             | 2D                             |

| Н      | Х          | Х | 1D <sub>0</sub> <sup>(1)</sup> | 2D <sub>0</sub> <sup>(1)</sup> |

| L      | $\uparrow$ | L | L <sup>(2)</sup>               | L                              |

| L      | $\uparrow$ | Н | H <sup>(2)</sup>               | Н                              |

- Output level before indicated steady-state input conditions were established

- (2) Two CLK edges are needed to propagate the data.

## **OUTPUT ENABLE**

| INPUTS     |    |     |        | OUTPUTS |        |

|------------|----|-----|--------|---------|--------|

| CLK        | ŌĒ | DIR | Α      | 1B, 2B  | 1D, 2D |

| 1          | Н  | Х   | Z      | Z       | Z      |

| $\uparrow$ | L  | Н   | Z      | Active  | Active |

| $\uparrow$ | L  | L   | Active | Z       | Active |

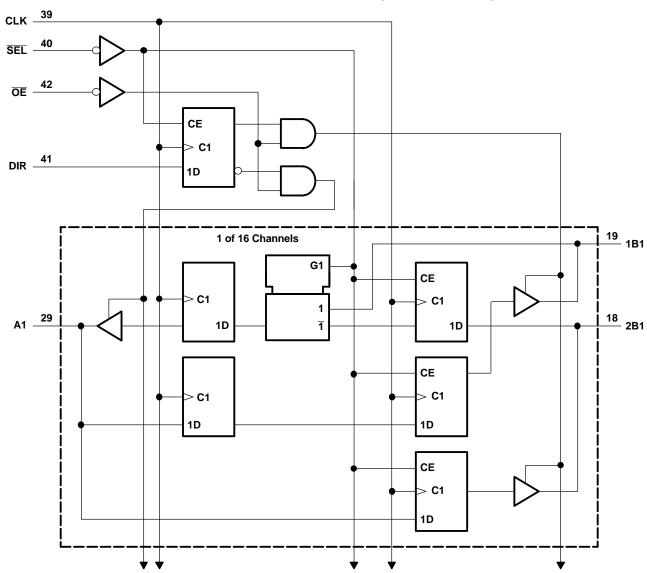

## LOGIC DIAGRAM, A AND B PORTS (POSITIVE LOGIC)

SCES093D-FEBRUARY 1997-REVISED OCTOBER 2004

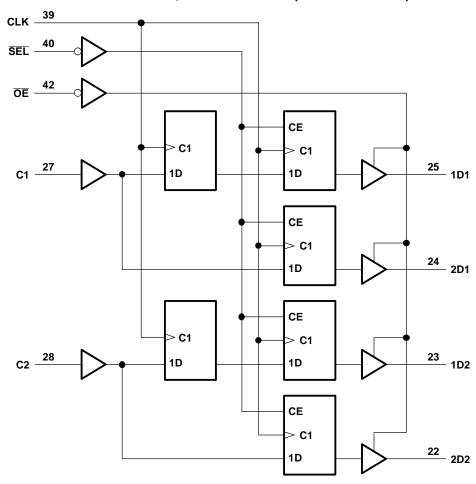

## LOGIC DIAGRAM, C AND D PORTS (POSITIVE LOGIC)

## ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                  |                                          |                                 | MIN  | MAX                   | UNIT |

|------------------|------------------------------------------|---------------------------------|------|-----------------------|------|

| V <sub>CC</sub>  | Supply voltage range                     |                                 | -0.5 | 4.6                   | V    |

| .,               | Input voltage range                      | Except I/O ports <sup>(2)</sup> | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| V <sub>I</sub>   |                                          | I/O ports <sup>(2)(3)</sup>     | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Vo               | Output voltage range (2) (3)             |                                 | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| I <sub>OK</sub>  | Output clamp current                     | V <sub>O</sub> < 0              |      | -50                   | mA   |

| Io               | Continuous output current                |                                 |      | ±50                   | mA   |

| $\theta_{JA}$    | Package thermal impedance <sup>(4)</sup> |                                 |      | 106                   | °C/W |

| T <sub>stg</sub> | Storage temperature rang                 | е                               | -65  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

<sup>3)</sup> This value is limited to 4.6 V maximum.

<sup>(4)</sup> The package thermal impedance is calculated in accordance with JESD 51.

SCES093D-FEBRUARY 1997-REVISED OCTOBER 2004

## **RECOMMENDED OPERATING CONDITIONS<sup>(1)</sup>**

|                     |                                    |        |                                          | MIN | MAX      | UNIT |

|---------------------|------------------------------------|--------|------------------------------------------|-----|----------|------|

| V <sub>CC</sub>     | Supply voltage                     |        |                                          | 3   | 3.6      | V    |

| $V_{IH}$            | High-level input voltage           |        | $V_{CC} = 3 \text{ V to } 3.6 \text{ V}$ | 2   |          | V    |

| $V_{IL}$            | Low-level input voltage            |        | $V_{CC} = 3 \text{ V to } 3.6 \text{ V}$ |     | 8.0      | V    |

| $V_{I}$             | Input voltage                      |        |                                          | 0   | $V_{CC}$ | V    |

| Vo                  | Output voltage                     |        |                                          | 0   | $V_{CC}$ | V    |

| 1                   | High-level output current          | A to B | V <sub>CC</sub> = 3 V                    |     | 8        | mA   |

| I <sub>OH</sub>     | riigii-ievei output current        | B to A | $V_{CC} = 3 V$                           |     | 6        | ША   |

|                     | Low-level output current           | A to B | $V_{CC} = 3 V$                           |     | 8        | mA   |

| IOL                 | Low-level output current           | B to A | V <sub>CC</sub> = 3 V                    |     | 6        | ША   |

| $\Delta t/\Delta v$ | Input transition rise or fall rate |        |                                          |     | 10       | ns/V |

| T <sub>A</sub>      | Operating free-air temperature     |        |                                          | 0   | 70       | °C   |

<sup>(1)</sup> All unused control inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

#### **ELECTRICAL CHARACTERISTICS**

over recommended operating free-air temperature range (unless otherwise noted)

| Р                    | ARAMETER       | ER TEST CONDITIONS                                             |              | MIN                   | TYP <sup>(1)</sup> | MAX  | UNIT |

|----------------------|----------------|----------------------------------------------------------------|--------------|-----------------------|--------------------|------|------|

|                      |                | I <sub>OH</sub> = -100 μA                                      | 3 V to 3.6 V | V <sub>CC</sub> - 0.2 |                    |      |      |

| $V_{OH}$             | A to B         | I <sub>OH</sub> = -8 mA                                        | 3 V          | 2                     |                    |      | V    |

|                      | B to A         | I <sub>OH</sub> = -6 mA                                        | 3 V          | 2                     |                    |      |      |

|                      |                | I <sub>OL</sub> = 100 μA                                       | 3 V to 3.6 V |                       |                    | 0.2  |      |

| $V_{OL}$             | A to B         | I <sub>OL</sub> = 8 mA                                         | 3 V          |                       |                    | 0.8  | V    |

|                      | B to A         | I <sub>OL</sub> = 6 mA                                         | 3 V          |                       |                    | 0.8  |      |

| II                   |                | $V_I = V_{CC}$ or GND                                          | 3.6 V        |                       |                    | ±5   | μΑ   |

|                      |                | V <sub>I</sub> = 0.8 V                                         | 3 V          | 75                    |                    |      |      |

| I <sub>I(hold)</sub> |                | V <sub>I</sub> = 2 V                                           | 3 V          | -75                   |                    |      | μΑ   |

|                      |                | V <sub>I</sub> = 0 to 3.6 V <sup>(2)</sup>                     | 3.6 V        |                       |                    | ±500 |      |

| I <sub>OZ</sub> (3)  |                | $V_O = V_{CC}$ or GND                                          | 3.6 V        |                       |                    | ±10  | μΑ   |

| Icc                  |                | $V_I = V_{CC}$ or GND, $I_O = 0$                               | 3.6 V        |                       |                    | 40   | μΑ   |

| $\Delta I_{CC}$      |                | One input at $V_{CC}$ - 0.6 V, Other inputs at $V_{CC}$ or GND | 3 V to 3.6 V |                       |                    | 750  | μΑ   |

| ^                    | Control inputs |                                                                | 0.01/        |                       | 4                  |      |      |

| Ci                   | C port         | $V_{I} = V_{CC}$ or GND                                        | 3.3 V        |                       | 8.5                |      | pF   |

| Co                   | D port         | $V_O = V_{CC}$ or GND                                          | 3.3 V        |                       | 7                  |      | pF   |

| Cio                  | A or B ports   | $V_O = V_{CC}$ or GND                                          | 3.3 V        |                       | 8.5                |      | pF   |

<sup>(1)</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

<sup>(2)</sup> This is the bus-hold maximum dynamic current. It is the minimum overdrive current required to switch the input from one state to another.

<sup>(3)</sup> For I/O ports, the parameter  $I_{OZ}$  includes the input leakage current.

## SN74ALVCHG162280 16-BIT TO 32-BIT REGISTERED BUS EXCHANGER WITH BYTE MASKS AND 3-STATE OUTPUTS

SCES093D-FEBRUARY 1997-REVISED OCTOBER 2004

## **TIMING REQUIREMENTS**

over recommended operating free-air temperature range (unless otherwise noted) (see Figure 1)

|                    |                                 |                    | V <sub>CC</sub> = ± 0.3 | V <sub>CC</sub> = 3.3 V<br>± 0.3 V |     |  |

|--------------------|---------------------------------|--------------------|-------------------------|------------------------------------|-----|--|

|                    |                                 |                    | MIN                     | MAX                                |     |  |

| f <sub>clock</sub> | Clock frequency                 |                    |                         | 160                                | MHz |  |

| t <sub>w</sub>     | Pulse duration, CLK high or low |                    | 2.3                     |                                    | ns  |  |

|                    |                                 | A data before CLK↑ | 1.4                     |                                    |     |  |

|                    | Setup time, high or low         | B data before CLK↑ | 2                       |                                    |     |  |

| t <sub>su</sub>    |                                 | C data before CLK↑ | 1.3                     |                                    | ns  |  |

|                    |                                 | DIR before CLK↑    | 2                       |                                    |     |  |

|                    |                                 | SEL before CLK↑    | 2                       |                                    |     |  |

|                    |                                 | A data after CLK↑  | 0.3                     |                                    |     |  |

|                    |                                 | B data after CLK↑  | 0.3                     |                                    |     |  |

| t <sub>h</sub>     | Hold time, high or low          | C data after CLK↑  | 0.3                     |                                    | ns  |  |

|                    |                                 | DIR after CLK↑     | 0.3                     |                                    |     |  |

|                    |                                 | SEL after CLK↑     | 0.3                     |                                    |     |  |

## **SWITCHING CHARACTERISTICS**

over recommended operating free-air temperature range,  $C_L = 25 \text{ pF}$  (A port), 80 pF (B and D ports) (unless otherwise noted) (see Figure 1)

| PARAMETER        | R FROM (INPUT) | TO       | $V_{CC}$ = 3.3 V $\pm$ 0.3 V |     | UNIT |

|------------------|----------------|----------|------------------------------|-----|------|

|                  | (INPUT)        | (OUTPUT) | MIN                          | MAX |      |

| f <sub>max</sub> |                |          | 160                          |     | MHz  |

|                  |                | A        | 1.5                          | 5   | ns   |

| t <sub>pd</sub>  | CLK            | В        | 1.5                          | 7.4 |      |

|                  |                | D        | 1.5                          | 7.2 |      |

|                  | CLK            | A        | 1.5                          | 6.2 |      |

|                  | CLK            | В        | 1.5                          | 9.4 |      |

| t <sub>en</sub>  |                | A        | 1.5                          | 6   | ns   |

|                  | ŌĒ             | В        | 1.5                          | 9.5 |      |

|                  |                | D        | 1.5                          | 7.9 |      |

|                  | CLK            | A        | 1.5                          | 6.4 |      |

| t <sub>dis</sub> | CLK            | В        | 1.5                          | 7.8 |      |

|                  |                | A        | 1.5                          | 5   | ns   |

|                  | ŌĒ             | В        | 1.5                          | 7.6 |      |

|                  |                | D        | 1.5                          | 6.7 |      |

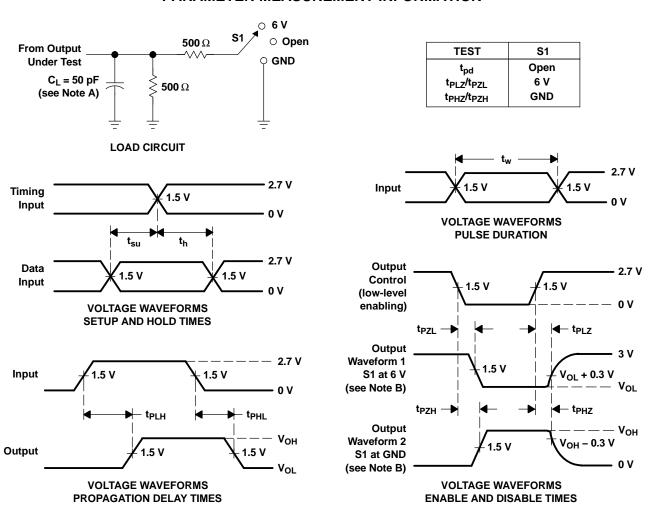

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A.  $C_L$  includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O$  = 50  $\Omega$ ,  $t_f \leq$  2.5 ns.  $t_f \leq$  2.5 ns.

- D. The output is measured with one input transition per measurement.

- E.  $t_{PLZ}$  and  $t_{PHZ}$  are the same as  $t_{dis}$ .

- F. t<sub>PZL</sub> and t<sub>PZH</sub> are the same as t<sub>en</sub>.

- G. t<sub>PLH</sub> and t<sub>PHL</sub> are the same as t<sub>pd</sub>.

Figure 1. Load Circuit and Voltage Waveforms

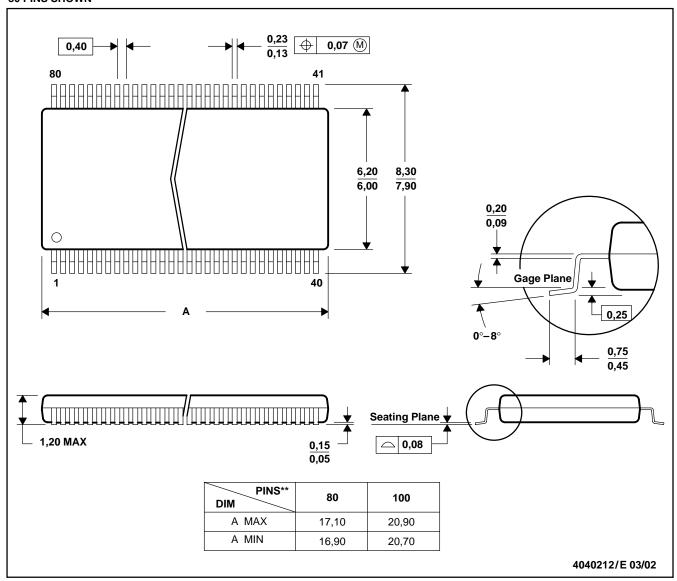

## DBB (R-PDSO-G\*\*)

#### **80 PINS SHOWN**

### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Falls within JEDEC: 80 Pin - MO-153 Variation FF

100 Pin - MO-194 Variation BB

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| e               |

|-----------------|

| d               |

| trol            |

|                 |

| work            |

|                 |

|                 |

|                 |

|                 |

| d<br>trol<br>wo |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated