TLIN1431-Q1

SLLSFE4A - MAY 2022 - REVISED DECEMBER 2022

# TLIN1431-Q1 Automotive LIN SBC with Integrated High-Side Switch and Watchdog

### 1 Features

- AEC-Q100 (Grade 1): Qualified for automotive applications

- Functional safety-capable

- Documentation available to aid functional safety system design

- Local interconnect network (LIN) physical layer specification LIN 2.2A, ISO 17987-4:2016 and SAE J2602:2021 compliant

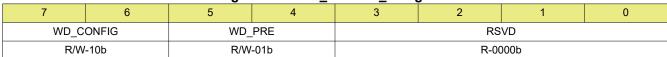

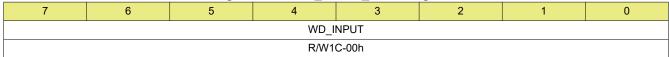

- Integrated watchdog supervisor configurable by pin or serial peripheral interface, SPI

- Enhanced features supporting 12-V applications

- ±58 V LIN bus fault protection

- 3.3 V (TLIN14313-Q1) or 5 V (TLIN14315-Q1) LDO output supporting 125 mA from 12 V supply

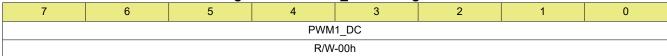

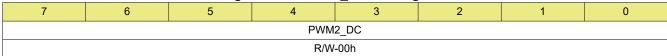

- High-side switch with open load and short circuit detection controlled by 10-bit PWM or timer

- LIMP pin configurable as a high-side switch

- Configurable WAKE pin supporting different input thresholds or methods

- Sleep mode: ultra-low current consumption allows wake up event from:

- LIN bus

- Local wake up through WAKE

- Cyclic and static sensing

- **Protection Features:**

- ESD protection

- Under voltage protection on V<sub>SUP</sub> and V<sub>CC</sub>

- TXD dominant time out (DTO) protection

- Thermal shutdown protection

- Integrated battery voltage monitor

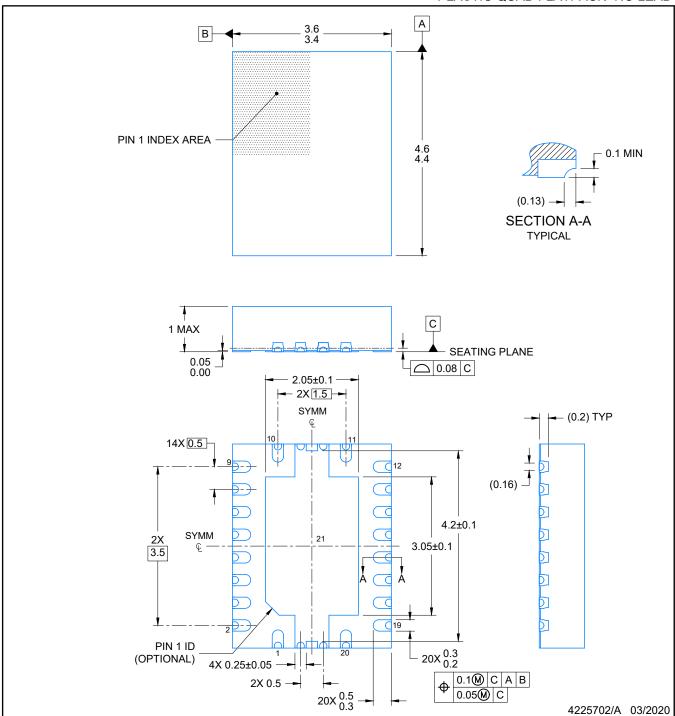

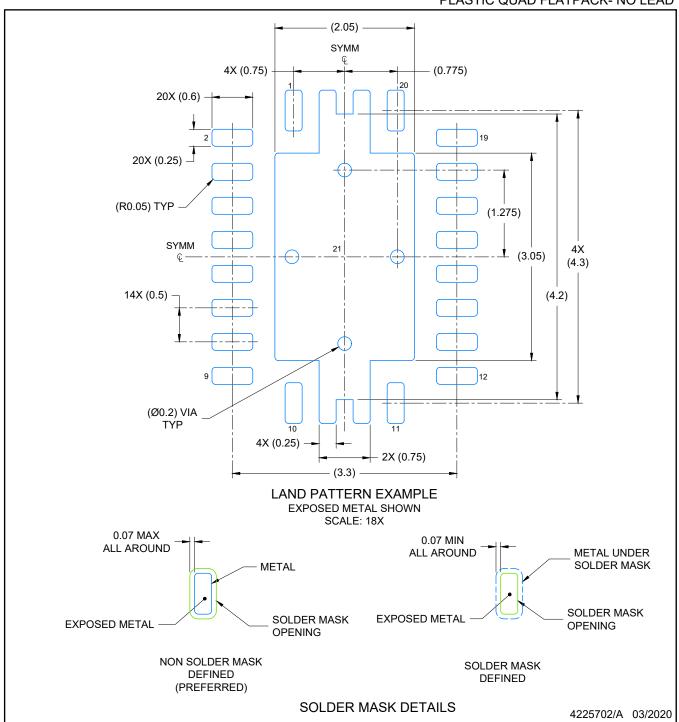

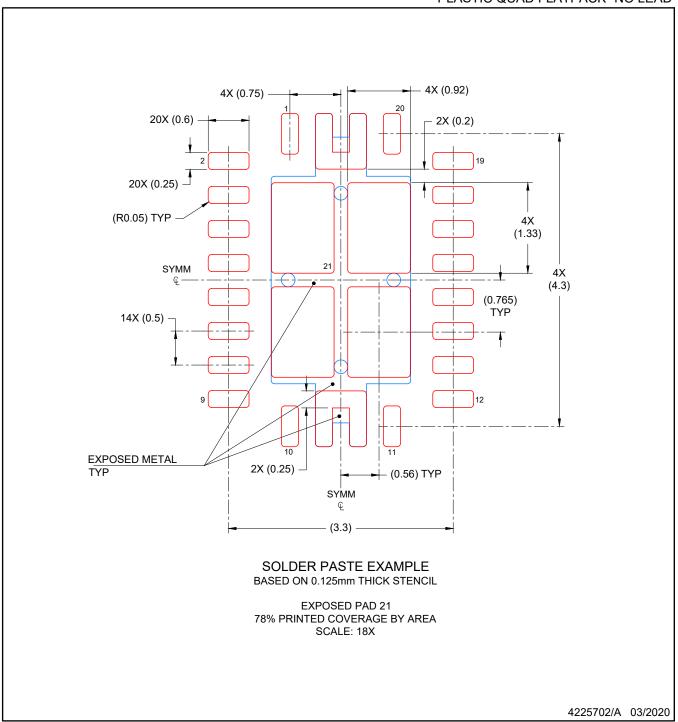

- Available in leadless QFN (20) package with improved automated optical inspection (AOI) capability

### 2 Applications

- Body electronics and lighting

- Hybrid, electric and powertrain systems

- Infotainment and cluster

- **Appliances**

### 3 Description

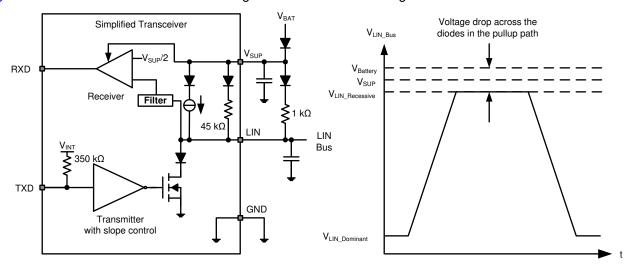

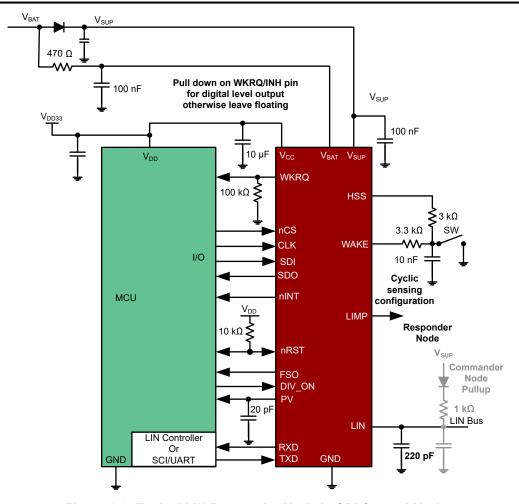

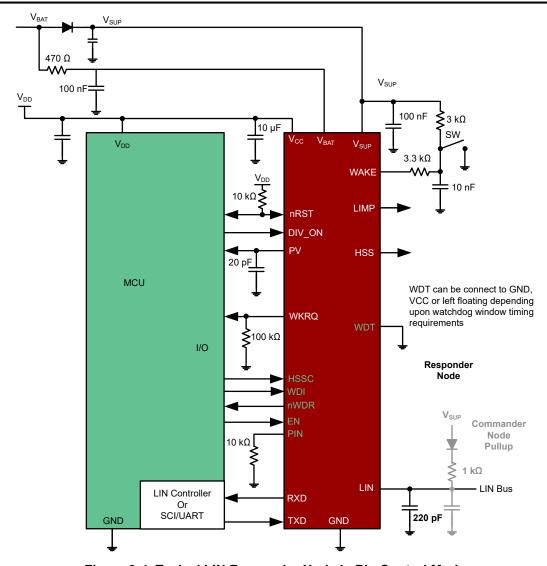

The TLIN1431x-Q1 is a local interconnect network (LIN) system basis chip (SBC) that integrates a watchdog, high-side switch, limp home capability and highly configurable WAKE input pin. The device selfdetermines the control method, pin or serial peripheral interface (SPI), at power up. The watchdog defaults to a window watchdog for both control methods but for flexibility the device can be configured as a window or timeout watchdog with greater than 20 different time windows when SPI control is used.

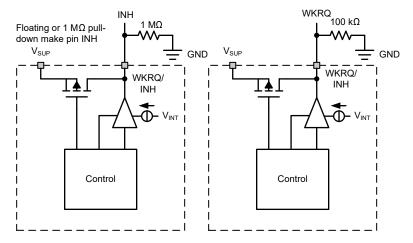

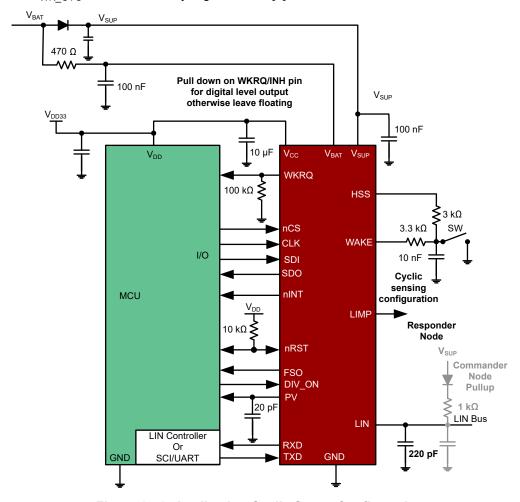

The LIN transceiver provides a 200 kbps fast mode for end of line programming. A high-side switch with diagnostic capability is provided for on board LED. The highly configurable WAKE pin can be used with the high-side switch for cyclic sensing, thus, reducing the ECU sleep current. The WKRQ/INH pin can be configured for a digital wake output (WKRQ) or a VSUP based inhibit (INH) enable pin for an external supply.

#### **Device Information**

| PART NUMBER  | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |

|--------------|------------------------|-------------------|

| TLIN1431x-Q1 | VQFN (RGY)(20)         | 4.50 mm x 3.50 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

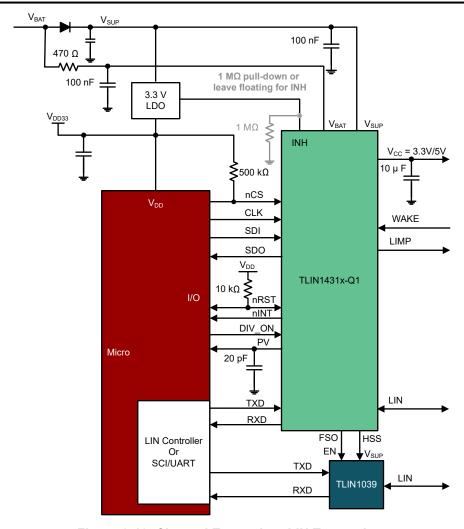

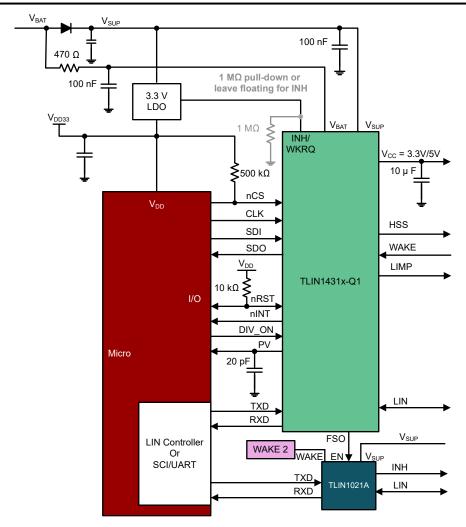

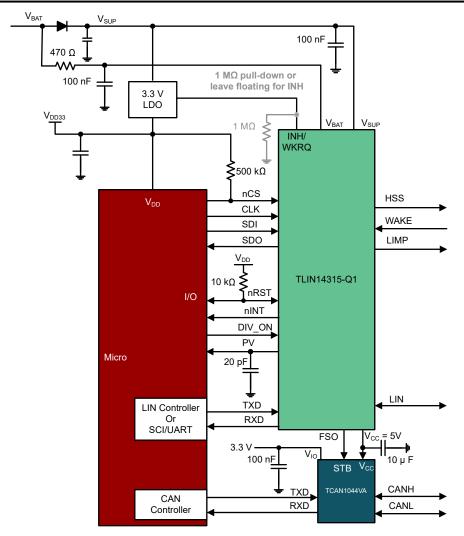

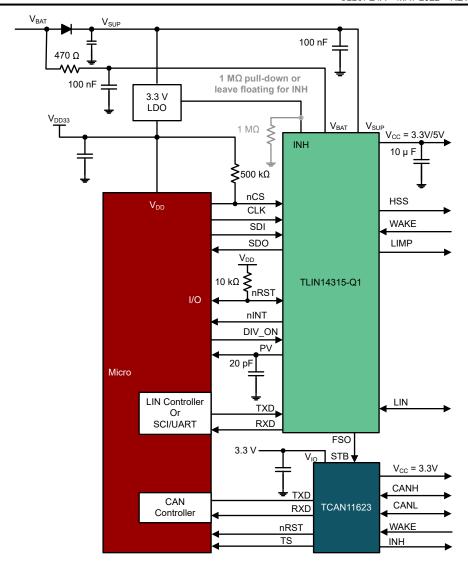

Simplified Schematics, SPI Control

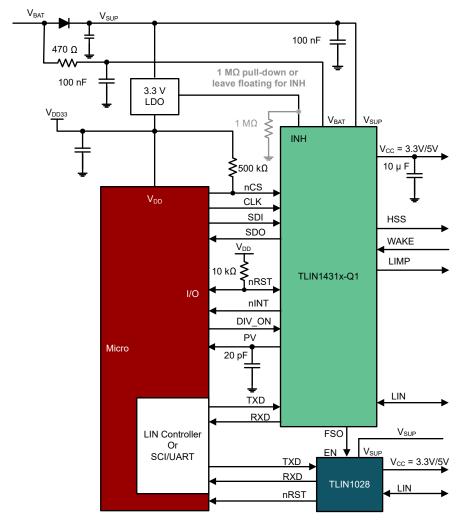

**Simplified Schematics, Pin Control**

# **Table of Contents**

| 1 Features                               | 1        | 8.2 Functional Block Diagram                         | 23  |

|------------------------------------------|----------|------------------------------------------------------|-----|

| 2 Applications                           |          | 8.3 Feature Description                              |     |

| 3 Description                            |          | 8.4 Device Functional Modes                          |     |

| 4 Revision History                       |          | 8.5 Programming                                      |     |

| 5 Pin Configuration and Functions        | 3        | 8.6 Registers                                        |     |

| 6 Specifications                         |          | 9 Application and Implementation                     |     |

| 6.1 Absolute Maximum Ratings             |          | 9.1 Application Information                          |     |

| 6.2 ESD Ratings                          |          | 9.2 Typical Application                              |     |

| 6.3 ESD Ratings, IEC Specification       |          | 9.3 Power Supply Recommendations                     |     |

| 6.4 Recommended Operating Conditions     |          | 9.4 Layout                                           |     |

| 6.5 Thermal Information                  |          | 10 Device and Documentation Support                  |     |

| 6.6 Power Supply Characteristics         | <b>5</b> | 10.1 Documentation Support                           |     |

| 6.7 Electrical Characteristics           |          | 10.2 Receiving Notification of Documentation Updates |     |

| 6.8 AC Switching Characteristics         | 11       | 10.3 Support Resources                               |     |

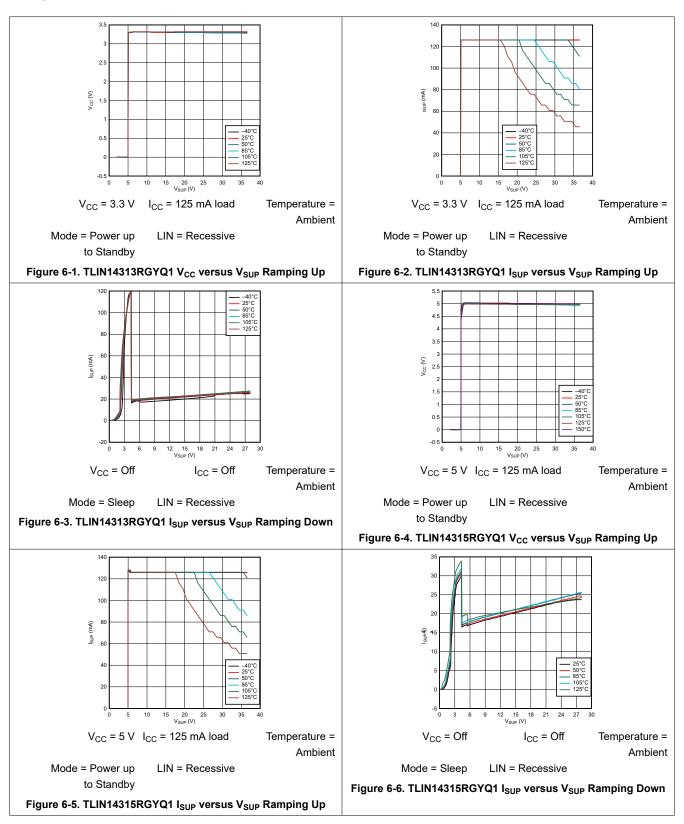

| 6.9 Typical Characteristics              | 14       | 10.4 Trademarks                                      |     |

| 7 Parameter Measurement Information      | 15       | 10.5 Electrostatic Discharge Caution                 | 100 |

| 7.1 Test Circuit: Diagrams and Waveforms | 15       | 10.6 Glossary                                        |     |

| 8 Detailed Description                   |          | 11 Mechanical, Packaging, and Orderable              |     |

| 8.1 Overview                             | 22       | Information                                          | 100 |

|                                          |          |                                                      |     |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | Changes from Revision * (May 2022) to Revision A (December 2022)    | Page |

|---|---------------------------------------------------------------------|------|

| • | Changed the data sheet from Advanced Information to Production data | 1    |

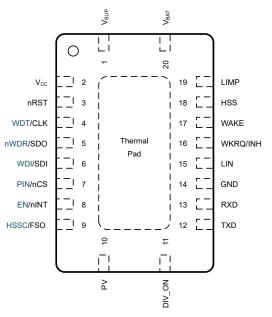

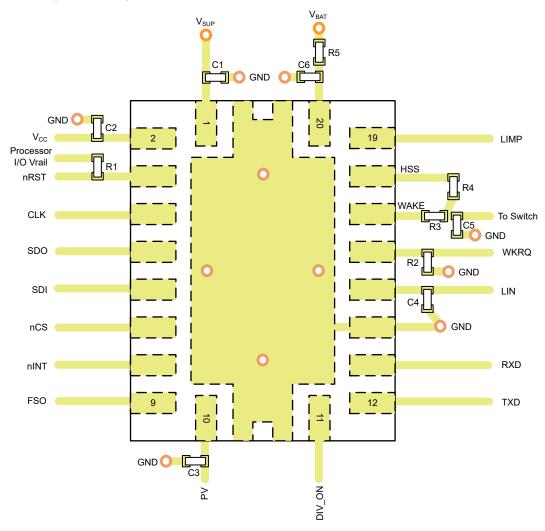

# **5 Pin Configuration and Functions**

Figure 5-1. RGY Package, 20-Pin QFN (Top View)

**Table 5-1. Pin Functions**

| P                | NI  | TYPE | DESCRIPTION                                                                                                                                                    |  |  |

|------------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME             | NO. | ITPE | DESCRIPTION                                                                                                                                                    |  |  |

| V <sub>SUP</sub> | 1   | ı    | Device supply voltage (connected to battery in series with external reverse blocking diode)                                                                    |  |  |

| V <sub>CC</sub>  | 2   | 0    | Output voltage from integrated voltage regulator                                                                                                               |  |  |

| nRST             | 3   | I/O  | Reset input/output (active low)                                                                                                                                |  |  |

| WDT/CLK          | 4   | 1    | Pin control: WDT - Programmable watchdog window set input (3 levels) SPI control: CLK - SPI clock input                                                        |  |  |

| nWDR/SDO         | 5   | 0    | Pin control: nWDR - Watchdog failure output trigger<br>SPI control: SDO - SPI serial data output                                                               |  |  |

| WDI/SDI          | 6   | I    | Pin control: WDI - Watchdog timer trigger input active on both rising and falling edges (Must be driven at all times) SPI control: SDI - SPI serial data input |  |  |

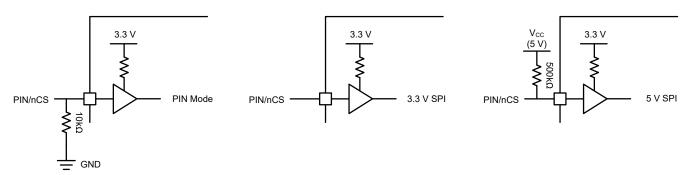

| PIN/nCS          | 7   | I    | Pin or SPI control selection pin at power up. Pin control: does not change SPI control: nCS - SPI chip select (active low)                                     |  |  |

| EN/nINT          | 8   | I/O  | Pin control: EN - Device mode change input pin SPI control: nINT - Device interrupt output pin                                                                 |  |  |

| HSSC/FSO         | 9   | I/O  | Pin control: HSSC - High side switch control input pin SPI control: FSO - Function output pin                                                                  |  |  |

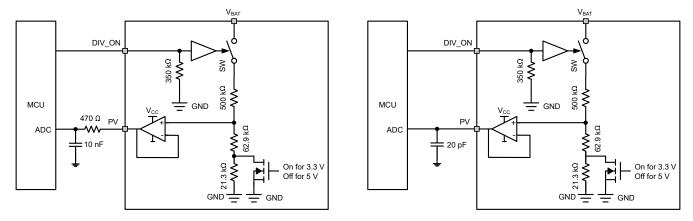

| PV               | 10  | 0    | Internal V <sub>BAT</sub> voltage divider output                                                                                                               |  |  |

| DIV_ON           | 11  | I    | Input to turn on the internal V <sub>BAT</sub> voltage divider, active high                                                                                    |  |  |

| TXD              | 12  | I    | TXD input interface to control state of LIN output                                                                                                             |  |  |

| RXD              | 13  | 0    | RXD output interface reporting state of LIN bus voltage                                                                                                        |  |  |

| GND, Pad         | 14  | _    | Ground                                                                                                                                                         |  |  |

| LIN              | 15  | I/O  | LIN bus single-wire transmitter and receiver                                                                                                                   |  |  |

| WKRQ/INH         | 16  | 0    | Digital output for wake or high voltage inhibit output depending upon state of pin at power up                                                                 |  |  |

| WAKE             | 17  | ı    | High voltage local wake up (LWU) pin                                                                                                                           |  |  |

| HSS              | 18  | 0    | High side switch                                                                                                                                               |  |  |

| LIMP             | 19  | 0    | Used for LIMP home, watchdog event causes this pin to switch V <sub>SUP</sub>                                                                                  |  |  |

| V <sub>BAT</sub> | 20  | I    | Supply voltage divider sense input (connected to battery)                                                                                                      |  |  |

# **6 Specifications**

### 6.1 Absolute Maximum Ratings

Over recommended operating range (unless otherwise noted)(1)

|                                       |                                           | MIN  | MAX                                             | UNIT |

|---------------------------------------|-------------------------------------------|------|-------------------------------------------------|------|

| V <sub>SUP</sub>                      | Supply voltage range (ISO/DIS 17987)      | -0.3 | 42                                              | V    |

| V <sub>BAT</sub>                      | Battery sense input                       | -24  | 42                                              | V    |

| V <sub>LIN</sub>                      | LIN Bus input voltage (ISO/DIS 17987)     | -58  | 58                                              | V    |

| V <sub>CC50</sub>                     | Regulated 5 V Output Supply               | -0.3 | 6                                               | V    |

| V <sub>CC33</sub>                     | Regulated 3.3 V Output Supply             | -0.3 | 4.5                                             | V    |

| $V_{WAKE}$                            | WAKE pin input voltage range              | -0.3 | 42                                              | V    |

| V <sub>HSS</sub>                      | High side switch pin output voltage range | -0.3 | 42 and V <sub>O</sub><br>≤V <sub>SUP</sub> +0.3 | V    |

| V <sub>INH</sub>                      | Inhibit pin output voltage range          | -0.3 | 42 and V <sub>O</sub><br>≤V <sub>SUP</sub> +0.3 | V    |

| V <sub>LIMP</sub>                     | LIMP pin output voltage range             | -0.3 | 42 and V <sub>O</sub><br>≤V <sub>SUP</sub> +0.3 | V    |

| V <sub>nRST</sub>                     | Reset output voltage                      | -0.3 | V <sub>CC</sub> + 0.3                           | V    |

| V <sub>LOGIC_INPUT</sub>              | Logic input voltage                       | -0.3 | 6                                               | V    |

| V <sub>LOGIC_OUTPUT</sub>             | Logic output voltage                      | -0.3 | 6                                               | V    |

| Io                                    | Digital pin output current                |      | 8                                               | mA   |

| I <sub>O(nRST)</sub>                  | Reset output current                      | -5   | 5                                               | mA   |

| T <sub>J</sub>                        | Junction temperature                      | -40  | 160                                             | °C   |

| Storage temperature, T <sub>stg</sub> | Storage temperature range                 | -65  | 165                                             | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|                    |                         |                                                                         |                                       | VALUE  | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------|---------------------------------------|--------|------|

|                    |                         | Human body model (HBM) classification level H2: with respect to ground  | $V_{BAT}$ , $V_{SUP}$ , LIN, and WAKE | ±10000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM) classification level 3A: Q100-002 <sup>(1)</sup> | all other pins, per AEC               | ±4000  | V    |

|                    |                         | Charged device model (CDM) classification level C5, per AEC Q100-011    | All pins                              | ±750   |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 ESD Ratings, IEC Specification

|                    |                                                                  |                                                | VALUE  | UNIT |  |

|--------------------|------------------------------------------------------------------|------------------------------------------------|--------|------|--|

| V <sub>(ESD)</sub> | Electrostatic discharge per IEC 62228-2 (1)                      | Contact discharge (VSUP, WAKE, HSS, LIMP, LIN) | ±8000  | V    |  |

|                    |                                                                  | Indirect ESD discharge (LIN)                   | ±14000 |      |  |

| V                  | (ESD) Powered electrostatic discharge SAE J2962-1 <sup>(3)</sup> | Contact discharge                              | ±8000  | V    |  |

| V <sub>(ESD)</sub> |                                                                  | Air discharge                                  | ±25000 | v    |  |

|                    |                                                                  | Pulse 1                                        | -100   |      |  |

| Iranciant          |                                                                  | Pulse 2a                                       | 75     | V    |  |

|                    | according to IBEE LIN EMC test spec <sup>(2)</sup>               | Pulse 3a                                       | -150   |      |  |

|                    |                                                                  | Pulse 3b                                       | 100    |      |  |

Product Folder Links: TLIN1431-Q1

# 6.3 ESD Ratings, IEC Specification (continued)

|           |                                      |                                                                                           | VALUE | UNIT |

|-----------|--------------------------------------|-------------------------------------------------------------------------------------------|-------|------|

| Transient | ISO /63/-3 Slow Transients Pulse (*) | Direct coupling capacitor "slow transient pulse" with 100 nF coupling capacitor - powered | ±30   | V    |

- (1) IEC 62228-2 ESD testing performed at third party. Different system-level configurations may lead to different results.

- (2) ISO 7637-2 according to IEC 62228-2 are system-level transient tests. Different system-level configurations may lead to different results.

- (3) SAE J2962-1 Testing performed at 3rd party US3 approved EMC test facility.

- (4) ISO 7637-3 is a system-level transient test. Different system-level configurations may lead to different results.

# **6.4 Recommended Operating Conditions**

parameters valid over –40°C ≤ T<sub>J</sub> ≤ 150 °C range (unless otherwise noted)

|                      |                                                                                          | MIN   | NOM | MAX   | UNIT |

|----------------------|------------------------------------------------------------------------------------------|-------|-----|-------|------|

| V <sub>SUP</sub>     | Supply voltage                                                                           | 5.5   |     | 28    | V    |

| V <sub>BAT</sub>     | Supply voltage                                                                           | 5.5   |     | 28    | V    |

| V <sub>LIN</sub>     | LIN bus input voltage                                                                    | 0     |     | 28    | V    |

| V <sub>LOGIC5</sub>  | Logic pin voltage                                                                        | 0     |     | 5.25  | V    |

| V <sub>LOGIC33</sub> | Logic pin voltage                                                                        | 0     |     | 3.465 | V    |

| I <sub>OH(DO)</sub>  | Digital terminal HIGH level output current                                               | -2    |     |       | mA   |

| I <sub>OL(DO)</sub>  | Digital terminal LOW level output current                                                |       |     | 2     | mA   |

| I <sub>O(LIMP)</sub> | LIMP output current when configured as LIMP                                              |       |     | 1     | mA   |

| I <sub>O(HSS)</sub>  | High side switch output current; LIMP output current when configured as high side switch |       |     | 100   | mA   |

| I <sub>O(INH)</sub>  | Inhibit output current                                                                   |       |     | 6     | mA   |

| C <sub>(VSUP)</sub>  | V <sub>SUP</sub> supply capacitance                                                      | 100   | ,   |       | nF   |

| C <sub>(VCC)</sub>   | V <sub>CC</sub> supply capacitance; no load to full load                                 | 10    | ,   |       | μF   |

| ESR <sub>CO</sub>    | Output ESR capacitance requirements                                                      | 0.001 | ,   | 2     | Ω    |

| Δt/ΔV                | Input transition rise and fall rate (WDI, WDT, WDR)                                      |       |     | 100   | ns/V |

| T <sub>J</sub>       | Operating junction temperature range                                                     | -40   | ,   | 150   | °C   |

#### 6.5 Thermal Information

|                       |                                              | TLIN1431x |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC(1)                            | RGY       | UNIT |

|                       |                                              | 20 PINS   |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 37.8      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 32.4      | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 15.7      | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.6       | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 15.7      | °C/W |

| $R_{\theta JC(bot)}$  | Junction-to-case (bottom) thermal resistance | 4.3       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.6 Power Supply Characteristics

parameters valid over –40°C ≤ T<sub>J</sub> ≤ 150 °C range (unless otherwise noted)

|                    | PARAMETER                          | TEST CONDITIONS                                       | MIN | TYP MAX | UNIT |

|--------------------|------------------------------------|-------------------------------------------------------|-----|---------|------|

| Supply Voltage and | Current                            |                                                       |     |         |      |

| V <sub>BAT</sub>   | V <sub>BAT</sub> sense pin voltage | $470~\Omega$ series resistor with 100nF cap to ground | 5.5 | 28      | V    |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

# **6.6 Power Supply Characteristics (continued)**

parameters valid over –40°C ≤ T<sub>.1</sub> ≤ 150 °C range (unless otherwise noted)

|                               | PARAMETER                                                             | TEST CONDITIONS                                                                                                                                                                              | MIN  | TYP  | MAX | UNIT |

|-------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| I <sub>BAT</sub>              | V <sub>BAT</sub> sense pin current                                    | 470 $\Omega$ series resistor with 100nF cap to ground with DIV_ON high, V <sub>BAT</sub> = 5.5 V to 28 V                                                                                     |      |      | 220 | μA   |

| I <sub>BATREV</sub>           | V <sub>BAT</sub> sense pin reverse current                            | 470 Ω series resistor with 100nF cap to ground with DIV_ON high $V_{BAT} = -24 \text{ V}$                                                                                                    | -1   |      |     | mA   |

| $V_{SUP}$                     | Operational supply voltage (ISO/DIS 17987 Param 10)                   | Device is operational beyond the LIN defined nominal supply voltage range                                                                                                                    | 5.5  |      | 36  | V    |

| $V_{SUP}$                     | Nominal supply voltage (ISO/DIS 17987                                 | Normal <sup>(2)</sup> and Standby Modes                                                                                                                                                      | 5.5  |      | 28  | V    |

| ▼ SUP                         | Param 10):                                                            | Sleep Mode                                                                                                                                                                                   | 5.5  |      | 28  | V    |

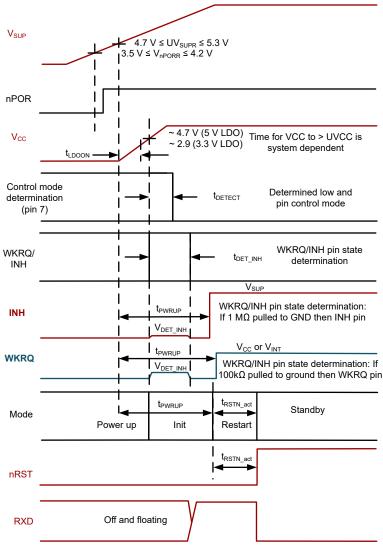

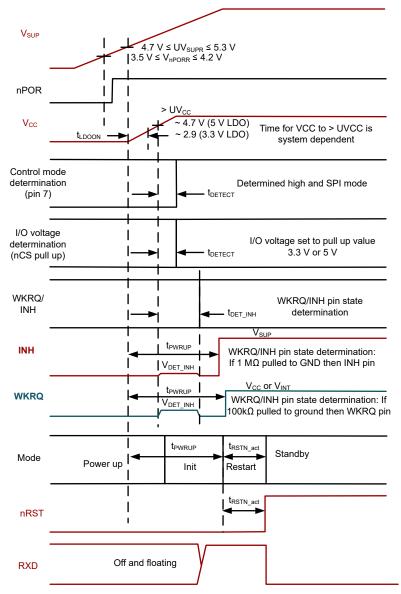

| UV <sub>SUPR</sub>            | Under voltage V <sub>SUP</sub> threshold                              | Ramp Up                                                                                                                                                                                      | 4.7  |      | 5.3 | V    |

| UV <sub>SUPF</sub>            | Under voltage V <sub>SUP</sub> threshold                              | Ramp Down                                                                                                                                                                                    | 4    |      | 4.6 | V    |

| U <sub>VHYS</sub>             | Delta hysteresis voltage for V <sub>SUP</sub> under voltage threshold |                                                                                                                                                                                              |      | 0.70 |     | V    |

| $V_{nPORR}$                   | V <sub>SUP</sub> power on reset release rising threshold              | Ramp Up                                                                                                                                                                                      | 3.5  |      | 4.2 | V    |

| $V_{nPORF}$                   | V <sub>SUP</sub> power on reset falling threshold                     | Ramp down                                                                                                                                                                                    | 1.9  |      | 2.9 | V    |

| I <sub>SUP</sub>              | Transceiver and LDO supply current                                    | Transceiver normal mode dominant plus<br>LDO output; where LDO load current is 125<br>mA                                                                                                     |      |      | 135 | mA   |

|                               | Supply current                                                        | Normal Mode: EN = $V_{CC}$ (Pin control mode otherwise SPI enabled), bus dominant: total bus load where $R_{LIN} \ge 500~\Omega$ and $C_{LIN} \le 10$ nF, LDO = no load                      |      | 2.3  | 5.2 | mA   |

| ISUPTRXDOM                    | Зирру ситен:<br>-                                                     | Standby Mode: EN = 0 V (Pin control mode otherwise SPI disabled), bus dominant: total bus load where R <sub>LIN</sub> $\geq$ 500 $\Omega$ and C <sub>LIN</sub> $\leq$ 10 nF, LDO = no load   |      | 1    | 1.9 | mA   |

| I <sub>SUPTRXREC</sub>        | Normal mode recessive supply current                                  | Normal Mode: EN = V <sub>CC</sub> ,<br>Bus recessive: LIN = V <sub>SUP</sub> , LDO = no load                                                                                                 |      | 0.9  | 1.3 | mA   |

| SUPTRXREC                     | Standby mode recessive supply current                                 | Standby Mode: EN = 0 V (Pin control mode otherwise SPI disabled), LIN = recessive = V <sub>SUP</sub> , LDO = no load                                                                         |      | 210  | 350 | μA   |

|                               | Sleep mode supply current                                             | 5.5 V < V <sub>SUP</sub> ≤ 14 V, LIN = V <sub>SUP</sub> , WAKE = GND, EN = 0 V (Pin control mode otherwise SPI disabled), TXD and RXD floating, LDO = no load                                |      | 20   | 32  | μА   |

| ISUPTRXSLP                    | Зіеер тіоде ѕарріу сапені                                             | $ \begin{array}{l} 14~V < V_{SUP} \leq 28~V, LIN = V_{SUP}, WAKE \\ = _{GND}, EN = 0~V~(Pin~control~mode \\ otherwise~SPI~disabled), TXD~and~RXD \\ floating, LDO = no~load \\ \end{array} $ |      | 25   | 36  | μA   |

| I <sub>SUPHSS</sub>           | High side switch current - no load                                    | Additional standby mode current from high side switch, no load.                                                                                                                              |      |      | 110 | μΑ   |

| Isupwkrq_inh                  | WKRQ/INH current due to pull-down                                     | Additional standby mode current due to the pull-down resister on the WKRQ/INH pin to determine pin function, 100 k $\Omega$ for WKRQ or 1 M $\Omega$ for INH.                                |      |      | 95  | μA   |

| Regulated Outpu               | t V <sub>cc</sub>                                                     |                                                                                                                                                                                              |      |      |     |      |

| V <sub>CC</sub>               | Regulated output                                                      | V <sub>SUP</sub> = 5.5 to 28 V, I <sub>CC</sub> = 1 to 125 mA                                                                                                                                | -2.5 |      | 2.5 | %    |

| $\Delta V_{CC(\Delta VSUP)}$  | Line regulation                                                       | $V_{SUP}$ = 5.5 to 28 V, $\Delta V_{CC}$ , $I_{CC}$ = 10 mA                                                                                                                                  |      |      | 50  | mV   |

| $\Delta V_{CC(\Delta VSUPL)}$ | Load regulation                                                       | $I_{CC}$ = 1 to 125 mA, $V_{SUP}$ = 14 V, $\Delta V_{CC}$                                                                                                                                    |      |      | 50  | mV   |

| V <sub>DROP1</sub>            | Dropout voltage (5 V LDO output)                                      | $V_{SUP} - V_{CC}$ , $I_{CC} = 15 \text{ mA}$                                                                                                                                                |      | 100  | 150 | mV   |

| V <sub>DROP2</sub>            | Dropout voltage (5 V LDO output)                                      | $V_{SUP} - V_{CC}$ , $I_{CC} = 125 \text{ mA}$                                                                                                                                               |      | 550  | 650 | mV   |

| V <sub>SC</sub>               | V <sub>CC</sub> short circuit threshold to enter sleep mode           | V <sub>SUP</sub> ≥ V <sub>POR</sub>                                                                                                                                                          |      | 2    | 2.5 | V    |

| UV <sub>CC5R</sub>            | Under voltage 5 V V <sub>CC</sub> threshold                           | Ramp Up                                                                                                                                                                                      |      | 4.7  | 4.9 | V    |

| UV <sub>CC5F</sub>            | Under voltage 5 V V <sub>CC</sub> threshold                           | Ramp Down                                                                                                                                                                                    | 4.1  | 4.45 |     | V    |

| UV <sub>CC33R</sub>           | Under voltage 3.3 V V <sub>CC</sub> threshold                         | Ramp Up                                                                                                                                                                                      |      | 2.9  | 3.1 | V    |

| UV <sub>CC33F</sub>           | Under voltage 3.3 V V <sub>CC</sub> threshold                         | Ramp Down                                                                                                                                                                                    | 2.5  | 2.75 |     | V    |

# **6.6 Power Supply Characteristics (continued)**

parameters valid over –40°C ≤ T<sub>.I</sub> ≤ 150 °C range (unless otherwise noted)

|                     | PARAMETER                                   | TEST CONDITIONS                                                                                                                                          | MIN  | TYP  | MAX  | UNIT |

|---------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| OV <sub>CC5R</sub>  | Over voltage 5 V VCC threshold (1)          | Ramp Up                                                                                                                                                  |      | 5.6  | 6.0  | V    |

| OV <sub>CC5F</sub>  | Over voltage 5 V VCC threshold (1)          | Ramp Down                                                                                                                                                | 5.28 | 5.5  |      | V    |

| OV <sub>CC33R</sub> | Over voltage 3.3 V VCC threshold (1)        | Ramp Up                                                                                                                                                  |      | 3.79 | 3.98 | V    |

| OV <sub>CC33F</sub> | Over voltage 3.3 V VCC threshold (1)        | Ramp Down                                                                                                                                                | 3.58 | 3.73 |      | V    |

| Іссоит              | Output current                              | V <sub>CC</sub> in regulation with 14V V <sub>SUP</sub>                                                                                                  | 1    |      | 125  | mA   |

| Іссоить             | Output current limit                        | V <sub>CC</sub> short to ground                                                                                                                          |      |      | 275  | mA   |

| PSRR                | Power supply rejection ripple rejection (1) | $\rm V_{RIP}$ = 0.5 $\rm V_{PP}$ , Load = 10 mA, $f$ = 100 Hz, CO = 10 $\rm \mu F$ , $\rm V_{SUP}$ = 12 V and ambient temperature = 27 $^{\circ}{\rm C}$ |      | 60   |      | dB   |

| T <sub>SDR</sub>    | Thermal shutdown temperature (1)            | Internal junction temperature; rising                                                                                                                    | 160  |      | 185  | °C   |

| T <sub>SDF</sub>    | Thermal shutdown temperature (1)            | Internal junction temperature; falling                                                                                                                   | 150  |      | 170  | °C   |

| T <sub>SDHYS</sub>  | Thermal shutdown hysteresis (1)             | V <sub>SUP</sub> = 12 V                                                                                                                                  |      | 15   |      | °C   |

<sup>(1)</sup> Specified by design

### **6.7 Electrical Characteristics**

parameters valid over -40°C  $\leq$  T<sub>J</sub>  $\leq$  150 °C range (unless otherwise noted)

|                         | PARAMETER                                                                        | TEST CONDITIONS                                                                                                                | MIN   | TYP | MAX   | UNIT             |

|-------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------------------|

| RXD Output Te           | rminal                                                                           |                                                                                                                                |       |     |       |                  |

| V <sub>OH</sub>         | High level output voltage                                                        | I <sub>O</sub> = -2 mA, V <sub>CC</sub> = Active                                                                               | 0.8   |     |       | V <sub>CC</sub>  |

| V <sub>OL</sub>         | Low level output voltage                                                         | I <sub>O</sub> = 2 mA, V <sub>CC</sub> = Active                                                                                |       |     | 0.2   | V <sub>CC</sub>  |

| I <sub>LKG(OFF)</sub>   | Unpowered leakage current                                                        | Outputs = 5.25/3.465 V, V <sub>CC</sub> = V <sub>SUP</sub> = 0 V                                                               | -1    |     | 1     | μA               |

| TXD Input Tern          | ninal                                                                            |                                                                                                                                |       |     |       |                  |

| V <sub>IL</sub>         | Low level input voltage                                                          |                                                                                                                                | -0.3  |     | 8.0   | V                |

| V <sub>IH</sub>         | High level input voltage                                                         |                                                                                                                                | 2     |     | 5.5   | V                |

| I <sub>IH</sub>         | High level input leakage current                                                 | TXD = V <sub>IH</sub>                                                                                                          | -5    | 0   | 5     | μA               |

| R <sub>TXD</sub>        | Internal pull-up resistor value                                                  |                                                                                                                                | 125   | 350 | 800   | kΩ               |

| LIN Terminal (F         | Referenced to V <sub>SUP</sub> )                                                 |                                                                                                                                |       |     |       |                  |

| V <sub>OH</sub>         | HIGH level output voltage <sup>(5)</sup>                                         | LIN recessive, TXD = high, I <sub>O</sub> = 0 mA, V <sub>SUP</sub> = 5.5 V to 28 V                                             | 0.85  |     |       | V <sub>SUP</sub> |

| V <sub>OL</sub>         | LOW level output voltage <sup>(5)</sup>                                          | LIN dominant, TXD = low, V <sub>SUP</sub> = 5.5 V to 28 V                                                                      |       |     | 0.2   | $V_{SUP}$        |

| V <sub>SUP_NON_OP</sub> | V <sub>SUP</sub> where impact of recessive LIN bus < 5% (ISO/DIS 17987 Param 11) | TXD & RXD open V <sub>LIN</sub> = 5.5 V to 45 V                                                                                | -0.3  |     | 45    | ٧                |

| I <sub>BUS_LIM</sub>    | Limiting current (ISO/DIS 17987 Param 12)                                        | $TXD = 0 \text{ V, V}_{LIN} = 28 \text{ V, R}_{MEAS} = 440 \Omega,$ $V_{SUP} = 28 \text{ V,}$ $V_{BUSdom} \le 0.251 * V_{SUP}$ | 40    | 90  | 200   | mA               |

| I BUS_PAS_dom           | Receiver leakage current, dominant (ISO/DIS 17987 Param 13)                      | V <sub>LIN</sub> = 0 V, V <sub>SUP</sub> = 12 V Driver off/recessive                                                           | -1    |     |       | mA               |

| I BUS_PAS_rec1          | Receiver leakage current, recessive (ISO/DIS 17987 Param 14)                     | V <sub>LIN</sub> ≥ V <sub>SUP</sub> , 5.5 V ≤ V <sub>SUP</sub> ≤ 28 V Driver off                                               |       |     | 20    | μA               |

| I BUS_PAS_rec2          | Receiver leakage current, recessive (ISO/DIS 17987 Param 14)                     | V <sub>LIN</sub> = V <sub>SUP</sub> , Driver off                                                                               | -5    |     | 5     | μΑ               |

| I BUS_NO_GND            | Leakage current, loss of ground (ISO/DIS 17987 Param 15)                         | GND = V <sub>SUP</sub> , V <sub>SUP</sub> = 12 V, 0 V ≤ V <sub>LIN</sub> ≤ 28 V                                                | -1    |     | 1     | mA               |

| I <sub>BUS_NO_BAT</sub> | Leakage current, loss of supply (ISO/DIS 17987 Param 16)                         | 0 V ≤ V <sub>LIN</sub> ≤ 28 V, V <sub>SUP</sub> = GND                                                                          |       |     | 10    | μA               |

| V <sub>BUSdom</sub>     | Low level input voltage (ISO/DIS 17987 Param 17)                                 | LIN dominant (including LIN dominant for wake up); Figure 7-2                                                                  |       |     | 0.4   | V <sub>SUP</sub> |

| V <sub>BUSrec</sub>     | High level input voltage (ISO/DIS 17987 Param 18)                                | LIN recessive; Figure 7-2                                                                                                      | 0.6   |     |       | $V_{SUP}$        |

| V <sub>BUS_CNT</sub>    | Receiver center threshold (ISO/DIS 17987 Param 19)                               | V <sub>BUS_CNT</sub> = (V <sub>IL</sub> + V <sub>IH</sub> )/2; Figure 7-2                                                      | 0.475 | 0.5 | 0.525 | $V_{SUP}$        |

<sup>(2)</sup> Normal Mode: Ramp VSUP while LIN signal is a 10 kHz square wave with 50 % duty cycle and 18 V swing.

# **6.7 Electrical Characteristics (continued)**

parameters valid over –40°C ≤ T<sub>J</sub> ≤ 150 °C range (unless otherwise noted)

|                           | PARAMETER                                                                                                      | TEST CONDITIONS                                                                                                                                   | MIN  | TYP  | MAX   | UNIT             |

|---------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------|

| V <sub>HYS</sub>          | Hysteresis voltage (ISO/DIS 17987 Param 20) <sup>(6)</sup>                                                     | V <sub>HYS</sub> = (V <sub>IL</sub> - V <sub>IH</sub> ); Figure 7-2                                                                               |      |      | 0.175 | V <sub>SUP</sub> |

| • 113                     | (7)                                                                                                            | THIS (VIL VIII), 1 Iguil 1                                                                                                                        |      |      | 00    | * 30F            |

| V <sub>SERIAL_DIODE</sub> | Serial diode LIN term pull-up path (ISO/DIS 17987 Param 21)                                                    | By design and characterization                                                                                                                    | 0.4  | 0.7  | 1.0   | V                |

| R <sub>LIN</sub>          | Internal pull-up resistor to V <sub>SUP</sub> on LIN (ISO/DIS 17987 Param 26)                                  | Normal and Standby modes                                                                                                                          | 20   | 45   | 60    | kΩ               |

| I <sub>RSLEEP</sub>       | Pull-up current source to V <sub>SUP</sub>                                                                     | Sleep mode, V <sub>SUP</sub> = 12 V, LIN = GND                                                                                                    | -20  |      | -2    | μΑ               |

| C <sub>LIN,PIN</sub>      | Capacitance of the LIN pin                                                                                     | By design and characterization                                                                                                                    |      |      | 25    | pF               |

| EN Input Termin           | nal                                                                                                            |                                                                                                                                                   |      |      |       |                  |

| V <sub>IH</sub>           | High level input voltage                                                                                       |                                                                                                                                                   | 2    |      | 5.5   | V                |

| V <sub>IL</sub>           | Low level input voltage                                                                                        |                                                                                                                                                   |      |      | 0.8   | V                |

| V <sub>HYS</sub>          | Hysteresis voltage                                                                                             | By design and characterization                                                                                                                    | 30   |      | 500   | mV               |

| I <sub>IL</sub>           | Low level input current                                                                                        | EN = Low                                                                                                                                          | -8   |      | 8     | μA               |

| R <sub>EN</sub>           | Internal pull-down resistor                                                                                    |                                                                                                                                                   | 125  | 350  | 800   | kΩ               |

|                           | rminal (High Voltage Open-drain Output)                                                                        |                                                                                                                                                   |      |      |       |                  |

| ΔV <sub>H</sub>           | Hi-level voltage drop for LIMP with respect to V <sub>SUP</sub>                                                | I <sub>LIMP</sub> = -60 mA                                                                                                                        |      | 0.42 | 1.2   | V                |

| R <sub>dson</sub>         | LIMP output drain-to-source on resistance                                                                      | I <sub>O</sub> = -60 mA                                                                                                                           |      | 7    | 20    | Ω                |

| I <sub>LKG(LIMP)</sub>    | Leakage current                                                                                                | LIMP = 0 V, Sleep Mode                                                                                                                            |      |      | 1     | μA               |

|                           | /oltage open drain output pin                                                                                  |                                                                                                                                                   |      |      |       | •                |

| V <sub>DET INH</sub>      | Voltage on INH/WKRQ pin during t <sub>DET_INH</sub> time                                                       | VSUP = 14V                                                                                                                                        |      |      | 1.5   | V                |

| ΔV <sub>HINH</sub>        | Hi-level voltage drop for INH with respect to V <sub>SUP</sub>                                                 | I <sub>INH</sub> = -6 mA                                                                                                                          |      | 0.5  | 1     |                  |

| ΔV <sub>HHSS</sub>        | Hi-level voltage drop for HSS with respect to V <sub>SUP</sub>                                                 | I <sub>HSS</sub> = -60 mA                                                                                                                         |      | 0.42 | 1.2   |                  |

|                           | HSS output drain-to-source on resistance                                                                       | I <sub>O</sub> = -60 mA                                                                                                                           |      | 7    | 1.2   | Ω                |

| R <sub>dson</sub>         | <u>'</u>                                                                                                       | VSUP = 14 V,                                                                                                                                      |      | 60   | 100   | mA               |

| I <sub>O(HSS)</sub>       | Output current support                                                                                         | ,                                                                                                                                                 | 450  |      |       |                  |

| I <sub>OC(HSS)</sub>      | HSS overcurrent limit                                                                                          | VSUP = 14 V                                                                                                                                       | 150  |      | 300   | mA_              |

| I <sub>OL(HSS)</sub>      | HSS open load current                                                                                          | VSUP = 14 V                                                                                                                                       | -2.5 | 0.45 |       | mA               |

| IOLHYS(HSS)               | HSS open load current hysteresis                                                                               | VSUP = 14 V                                                                                                                                       | 0.05 | 0.45 | 1     | mA               |

| I <sub>lkg</sub>          | Leakage current                                                                                                | INH, HSS = 0 V, Sleep Mode                                                                                                                        | -1   |      | 1     | μA               |

| t <sub>R/F</sub>          | Output rise and fall times (HSS)                                                                               | $5.5 \text{ V} \le \text{V}_{\text{SUP}} \le 28 \text{ V}, \text{ I}_{\text{LOAD}} = 60 \text{ mA}, \text{ R}_{\text{L}} = 220 \Omega, 80\%/20\%$ | 0.6  |      | 2.5   | V/µs             |

| t <sub>HSS_on</sub>       | Switching on delay (HSS) from SPI command to on                                                                | $V_{SUP}$ = 14 V, $I_{LOAD}$ = 60 mA, $V_{OUT}$ = 80% of $V_{SUP}$                                                                                |      |      | 60    | μs               |

| t <sub>HSS_off</sub>      | Switching off delay (HSS) from SPI command to off                                                              | $V_{SUP}$ = 14 V, $I_{LOAD}$ = 60 mA, $V_{OUT}$ = 20% of $V_{SUP}$                                                                                |      |      | 140   | μs               |

| tocfltr                   | HSS overcurrent filter time <sup>(2)</sup>                                                                     | V <sub>SUP</sub> = 14 V                                                                                                                           |      | 16   |       | μs               |

| t <sub>OLFLTR</sub>       | HSS open load filter time <sup>(2)</sup>                                                                       | V <sub>SUP</sub> = 14 V                                                                                                                           |      | 64   |       | μs               |

| t <sub>OCOFF</sub>        | HSS overcurrent shut off time                                                                                  | I <sub>O(HSS)</sub> > I <sub>OC(HSS)</sub>                                                                                                        | 200  |      | 300   | μs               |

| WAKE Input Te             | rminal                                                                                                         |                                                                                                                                                   |      |      |       |                  |

| V <sub>IH</sub>           | High-level input voltage                                                                                       | Sleep or Standby Mode, WAKE pin enabled                                                                                                           | 4    |      |       | V                |

| V <sub>IL</sub>           | Low-level input voltage                                                                                        | Sleep or Standby Mode, WAKE pin enabled                                                                                                           |      |      | 2     | V                |

| I <sub>IL</sub>           | Low-level input leakage current                                                                                | WAKE = 1 V                                                                                                                                        |      | 15   | 25    | μA               |

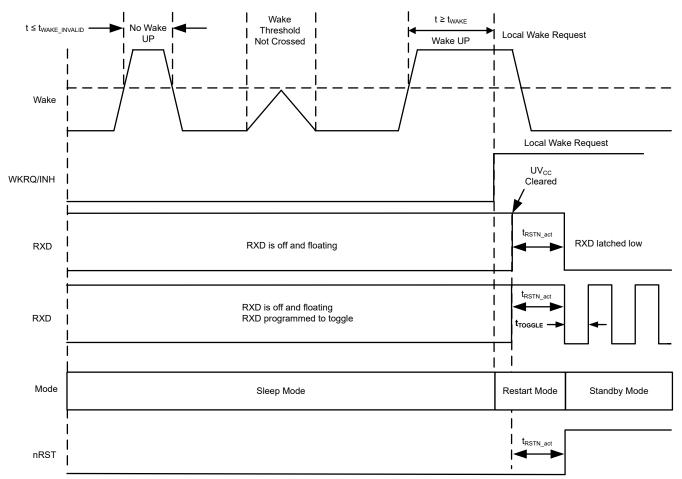

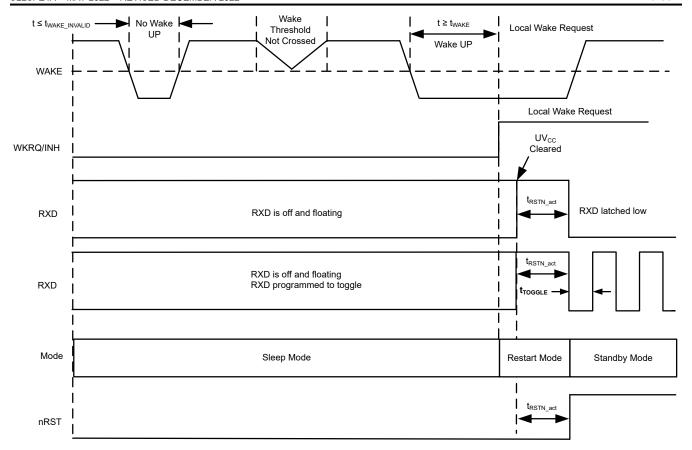

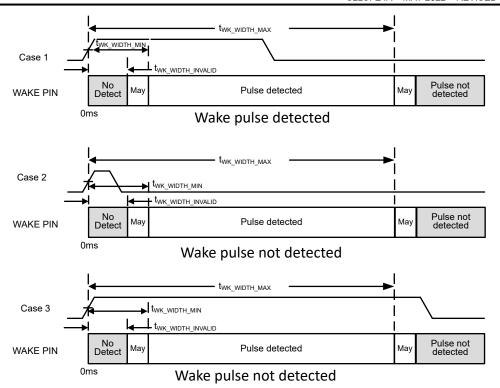

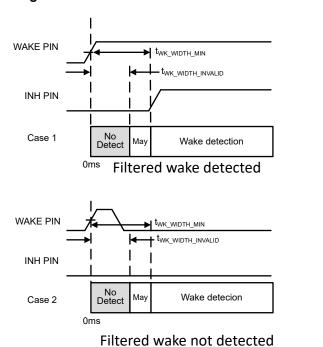

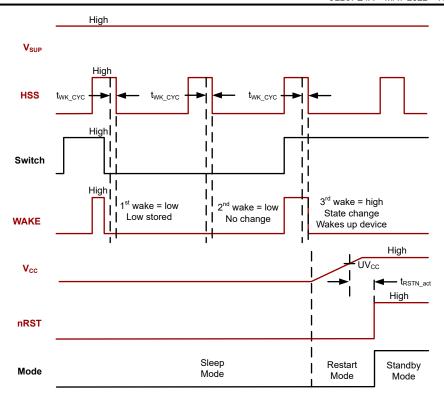

| t <sub>WAKE</sub>         | Wake up hold time from a wake edge on WAKE in standby or sleep mode for static sensing                         | See Figure 8-44 and Figure 8-45                                                                                                                   | 140  |      | -     | μs               |

| t <sub>WAKE_INVALID</sub> | WAKE pin pulses shorter than this will be filtered out in standby or sleep mode for static and cyclic sensing. | See Figure 8-44 and Figure 8-45                                                                                                                   |      |      | 10    | μs               |

| WDI, SDI, CLK,            | nCS Input Terminal                                                                                             | -                                                                                                                                                 |      |      |       |                  |

| V <sub>IH</sub>           | High-level input voltage                                                                                       |                                                                                                                                                   | 2.19 |      |       | V                |

| V <sub>IL</sub>           | Low-level input voltage                                                                                        |                                                                                                                                                   |      |      | 0.8   | V                |

|                           | High-level input leakage current                                                                               | Inputs = V <sub>CC</sub>                                                                                                                          |      |      | 1     | μA               |

| I <sub>IH</sub>           | Trigit-level input leakage current                                                                             |                                                                                                                                                   |      |      |       |                  |

# **6.7 Electrical Characteristics (continued)**

parameters valid over –40°C ≤ T<sub>.I</sub> ≤ 150 °C range (unless otherwise noted)

|                        | PARAMETER                                                            | TEST CONDITIONS                                                                                                                                                | MIN   | TYP | MAX  | UNIT            |

|------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|-----------------|

| C <sub>IN</sub>        | Input Capacitance                                                    | 4 MHz                                                                                                                                                          |       | 10  | 15   | pF              |

| I <sub>LKG(OFF)</sub>  | Unpowered leakage current                                            | Inputs = 5.25/3.465 V, V <sub>CC</sub> = V <sub>SUP</sub> = 0 V                                                                                                | -1    |     | 1    | μA              |

| R <sub>WDI_SDIpu</sub> | Internal pull-up resistor on WDI/SDI pin                             |                                                                                                                                                                | 100   | 240 | 400  | kΩ              |

| R <sub>CLKpu</sub>     | Internal pull-up resistor on WDT/CLK pin                             | SPI control only for CLK                                                                                                                                       | 100   | 240 | 400  | kΩ              |

| R <sub>nCSpu</sub>     | Internal pull-up resistor on PIN/nCS pin                             | SPI control only for nCS                                                                                                                                       | 100   | 240 | 400  | kΩ              |

| WDT Input Te           | rminal                                                               | 1                                                                                                                                                              |       |     |      |                 |

| V <sub>IH</sub>        | High-level input voltage                                             | Inputs = V <sub>CC</sub>                                                                                                                                       | 0.8   |     |      | V <sub>CC</sub> |

| V <sub>IL</sub>        | Low-level input voltage                                              | Inputs = V <sub>CC</sub>                                                                                                                                       |       |     | 0.2  | V <sub>CC</sub> |

| V <sub>IM(WDT)</sub>   | WDT Mid-level input voltage <sup>(1)</sup>                           | Inputs = V <sub>CC</sub>                                                                                                                                       | 0.4   | 0.5 | 0.6  | V <sub>CC</sub> |

| I <sub>IH</sub>        | High-level input leakage current                                     | Inputs = V <sub>CC</sub>                                                                                                                                       | 2.5   |     | 25   | μA              |

| I <sub>IL</sub>        | Low-level input leakage current                                      | Inputs = 0 V, V <sub>CC</sub> = Active                                                                                                                         | -25   |     | -2.5 | μA              |

| I <sub>LKG(OFF)</sub>  | Unpowered leakage current                                            | Inputs = 5.25/3.465 V, V <sub>CC</sub> = V <sub>SUP</sub> = 0 V                                                                                                | -3    |     | 3    | μA              |

| SDO Output 1           | [erminal                                                             |                                                                                                                                                                |       | -   |      |                 |

| V <sub>OH</sub>        | High level output voltage                                            | I <sub>O</sub> = -2 mA, V <sub>CC</sub> = Active                                                                                                               | 0.8   |     |      | V <sub>CC</sub> |

| V <sub>OL</sub>        | Low level output voltage                                             | I <sub>O</sub> = 2 mA, V <sub>CC</sub> = Active                                                                                                                |       |     | 0.2  | V <sub>CC</sub> |

| I <sub>LKG(OFF)</sub>  | Unpowered leakage current                                            | Outputs = 5.25/3.465 V, V <sub>CC</sub> = V <sub>SUP</sub> = 0 V                                                                                               | -1    |     | 1    | μA              |

|                        | al; input/output reset (Open-drain)                                  |                                                                                                                                                                | I     |     |      | -               |

| I <sub>LKG</sub>       | Leakage current, high-level                                          | LIN = V <sub>SUP</sub> , nRST = V <sub>CC</sub>                                                                                                                | -5    |     | 5    | μA              |

| V <sub>OL</sub>        | Low-level output voltage                                             | Based upon external pull up to V <sub>CC</sub>                                                                                                                 |       |     | 0.2  | V <sub>CC</sub> |

| I <sub>OL</sub>        | Low-level output current, open drain                                 | LIN = 0 V, nRST = 0.4 V                                                                                                                                        | 1.5   |     |      | mA              |

| V <sub>th(sw)</sub>    | Switching threshold voltage                                          |                                                                                                                                                                | 0.25  |     | 0.75 | V <sub>CC</sub> |

| R <sub>PU</sub>        | Pull-up resistance                                                   |                                                                                                                                                                | 30    | 45  | 65   | kΩ              |

|                        | WKRQ Terminal                                                        | 1                                                                                                                                                              |       |     |      |                 |

| V <sub>OH</sub>        | High level output voltage                                            | I <sub>O</sub> = -2 mA, V <sub>CC</sub> = Active                                                                                                               | 0.8   |     |      | V <sub>CC</sub> |

| V <sub>OL</sub>        | Low-level output voltage                                             | I <sub>O</sub> = 2 mA, V <sub>CC</sub> = Active                                                                                                                | 0.0   |     | 0.2  | V <sub>CC</sub> |

| V OL                   | Unpowered leakage current (nINT and nWDR                             |                                                                                                                                                                |       |     |      |                 |

| I <sub>LKG(OFF)</sub>  | pins)                                                                | Outputs = 5.25/3.465 V, V <sub>CC</sub> = V <sub>SUP</sub> = 0 V                                                                                               | -1    |     | 1    | μA              |

| HSSC                   |                                                                      |                                                                                                                                                                |       |     |      |                 |

| V <sub>IH</sub>        | High-level input voltage                                             |                                                                                                                                                                | 2     |     | 5.5  | V               |

| V <sub>IL</sub>        | Low-level input voltage                                              |                                                                                                                                                                |       |     | 0.8  | V               |

| I <sub>IL</sub>        | Low-level input current                                              | V <sub>IN</sub> = 0 V                                                                                                                                          | -1    |     | 1    | μA              |

| R <sub>HSSC</sub>      | Pull-down resistor                                                   |                                                                                                                                                                | 150   | 350 | 800  | kΩ              |

| f <sub>SW</sub>        | Switching frequency                                                  | V <sub>HSS</sub> = 14 V, I <sub>O(HSS)</sub> = 60 mA                                                                                                           |       |     | 400  | Hz              |

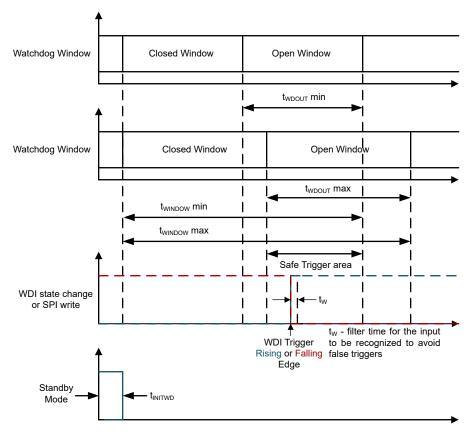

| WDI, WDT TIN           | MING and SWITCHING CHARACTERISTIC (RL = 1 M                          | $M\Omega$ , CL = 50 pF and T <sub>J</sub> = -40°C to 150°C)                                                                                                    |       |     | •    |                 |

| t <sub>W</sub>         | WDI pulse width; see Figure 7-8                                      | Filter time to avoid false input                                                                                                                               | 30    |     |      | μs              |

|                        |                                                                      | WDT = GND                                                                                                                                                      | 32    | 40  | 48   | ms              |

| t <sub>WINDOW</sub>    | Closed Window + Open Window; See Figure 7-8                          | WDT = V <sub>CC</sub>                                                                                                                                          | 480   | 600 | 720  | ms              |

|                        |                                                                      | WDT = Floating                                                                                                                                                 | 4.8   | 6   | 7.2  | s               |

| DIV_ON                 |                                                                      |                                                                                                                                                                | •     |     |      |                 |

| V <sub>IH</sub>        | High-level input voltage                                             |                                                                                                                                                                | 2     |     | 5.5  | V               |

| V <sub>IL</sub>        | Low-level input voltage                                              |                                                                                                                                                                |       |     | 0.8  | V               |

| I <sub>IL</sub>        | Low-level input current                                              | V <sub>DIV_ON</sub> = 0 V                                                                                                                                      | -1    |     | 1    | μA              |

| R <sub>DIV_ON</sub>    | Pull-down resistor                                                   |                                                                                                                                                                | 150   | 370 | 800  | kΩ              |

| PV                     |                                                                      |                                                                                                                                                                | 1     |     | l    |                 |

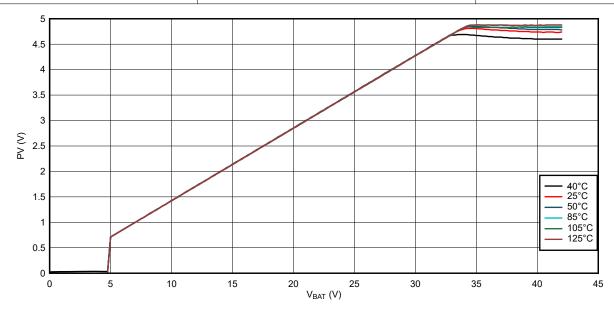

| Ratio                  | Divider ratio 5 V VCC                                                | V <sub>BAT</sub> = 5.5 V to 28 V                                                                                                                               |       | 1:7 |      |                 |

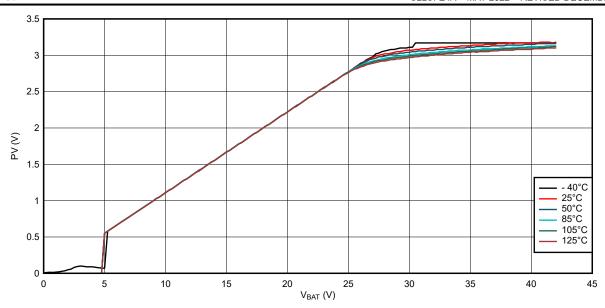

| Ratio                  | Divider ratio 3.3 V VCC                                              | V <sub>BAT</sub> = 5.5 V to 20 V                                                                                                                               |       | 1:9 |      |                 |

| ERR                    | Divider ratio error                                                  | V <sub>BAT</sub> = 5.5 V to 28 V                                                                                                                               | -2    |     | 2    | %               |

| V <sub>BATLIN5</sub>   | Linear voltage range for V <sub>BAT</sub> for 5 V LDO <sup>(3)</sup> | $R_{LOAD} = 470~\Omega \pm 5\%$ and $C_{LOAD} = 10~nF$<br>$\pm 10\%$ ; When capacitive load only 20 pF $\pm$<br>20%, 5.5 V $\leq$ V <sub>BAT</sub> $\leq$ 28 V | 0.735 |     | 4.05 | V               |

### 6.7 Electrical Characteristics (continued)

parameters valid over –40°C ≤ T<sub>.1</sub> ≤ 150 °C range (unless otherwise noted)

|                          | PARAMETER                                                                                                 | TEST CONDITIONS                                                                                                                                                                                                                                                                                               | MIN TYP MAX |    | MAX   | UNIT |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----|-------|------|--|

| V <sub>BATLIN3</sub>     | Linear voltage range for V <sub>BAT</sub> for 3.3 V LDO and when I/O is 3.3 V with 5 V LDO <sup>(4)</sup> | $R_{LOAD}$ = 470 $\Omega$ ± 5% and $C_{LOAD}$ = 10 nF<br>± 10%; When capacitive load only 20 pF ±<br>20%, 5.5 V ≤ $V_{BAT}$ ≤ 20 V                                                                                                                                                                            | 0.561       |    | 2.27  | V    |  |

| V <sub>MAX5V</sub>       | Maximum V <sub>PVOUT</sub>                                                                                | 28 V < V <sub>BAT</sub> ≤ 42 V, 470 Ω ± 5% and C <sub>LOAD</sub> = 10 nF ± 10%; When capacitive load only 20 pF ± 20%                                                                                                                                                                                         |             |    | 5.1   | V    |  |

| V <sub>MAX3.3V</sub>     | Maximum $\mbox{V}_{\mbox{\scriptsize PVOUT}}$ for $3.3$ V LDO and when I/O is $3.3$ V with $5$ V LDO      | 20 V < $V_{BAT}$ ≤ 42 V, 470 $\Omega$ ± 5% and $C_{LOAD}$ = 10 nF ± 10%; When capacitive load only 20 pF ± 20%                                                                                                                                                                                                |             |    | 3.36  | V    |  |

| V <sub>VCC5V_VIO3V</sub> | Voltage when VCC = 5 V and I/O is at 3.3 V                                                                | R <sub>LOAD</sub> = 470 Ω ± 5% and C <sub>LOAD</sub> = 10 nF<br>± 10%; When capacitive load only 20 pF ±<br>20% and I/O voltage is ≤ 3.6 V                                                                                                                                                                    |             |    | 3.36  | V    |  |

| C <sub>PIN</sub>         | Pin capacitance                                                                                           |                                                                                                                                                                                                                                                                                                               |             | 12 |       | pF   |  |

| t <sub>SET</sub>         | Settling time of the buffer                                                                               | $470~\Omega \pm 5\%$ and $C_{LOAD}$ = 10 nF ± 10%;<br>When capacitive load only 20 pF ± 20%                                                                                                                                                                                                                   |             |    | 50    | μs   |  |

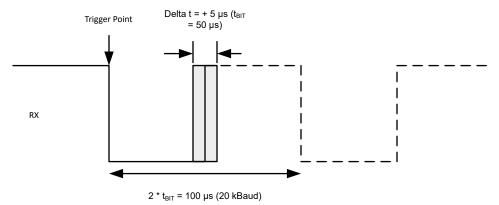

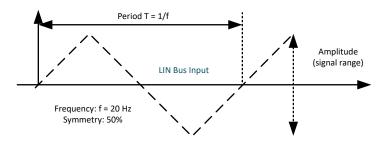

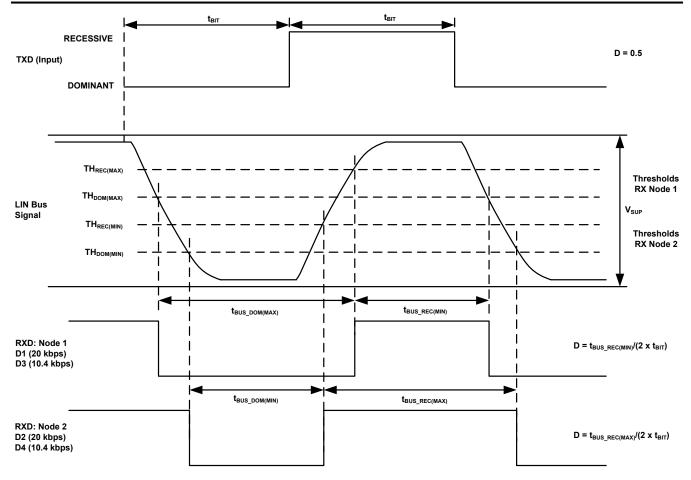

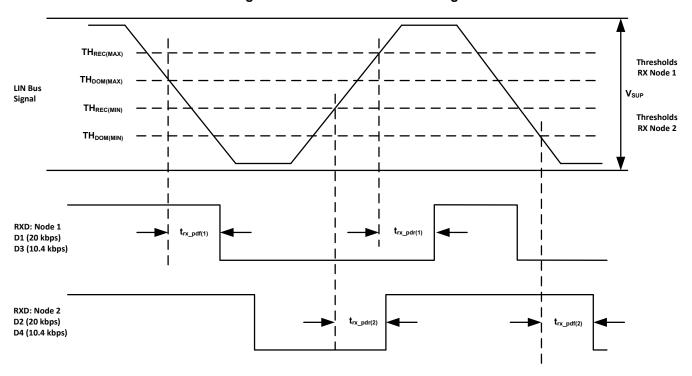

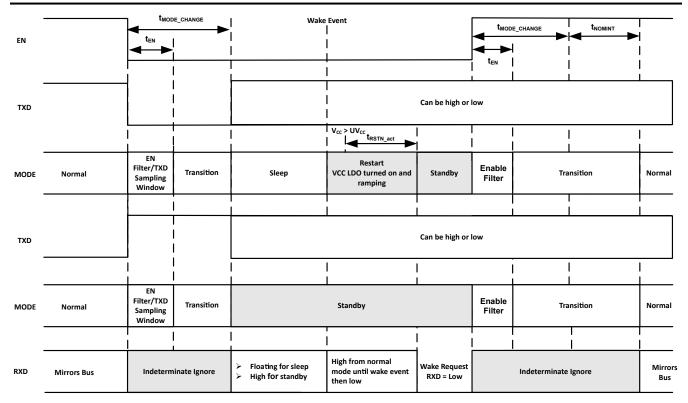

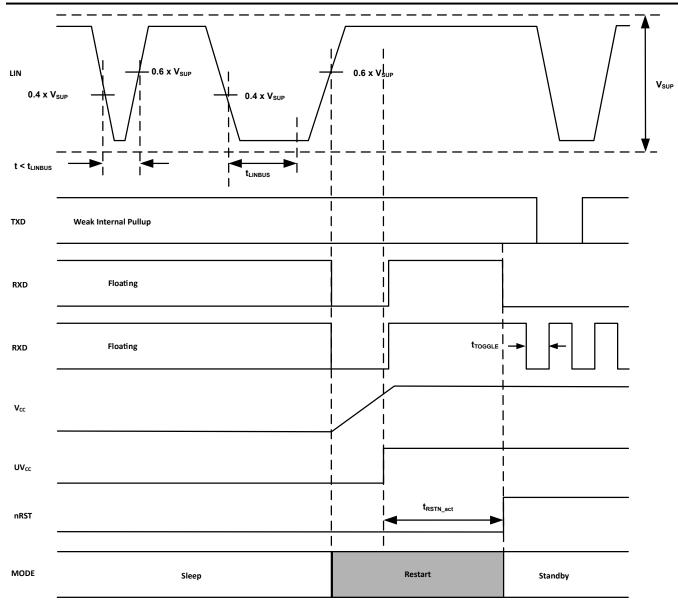

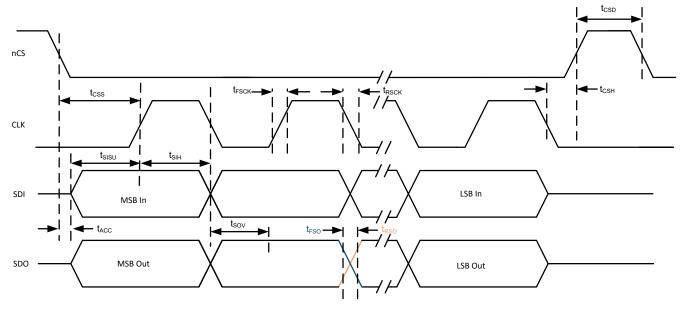

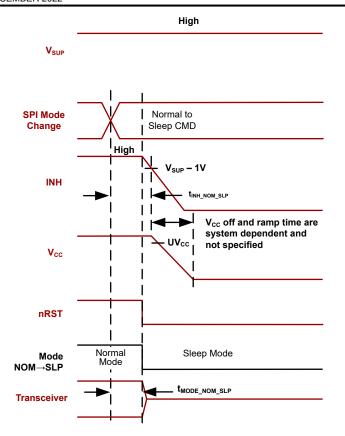

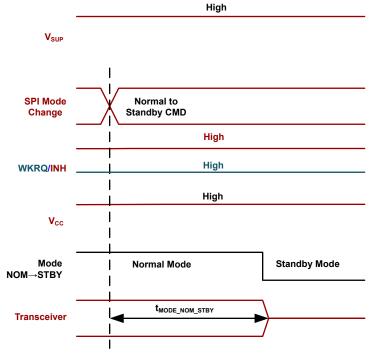

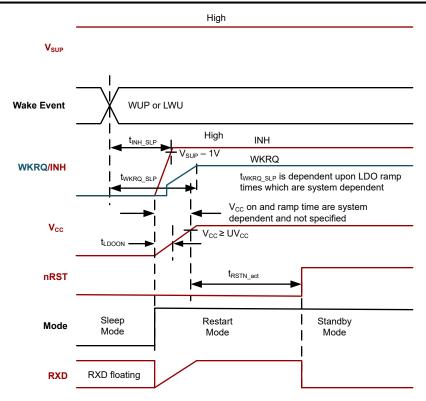

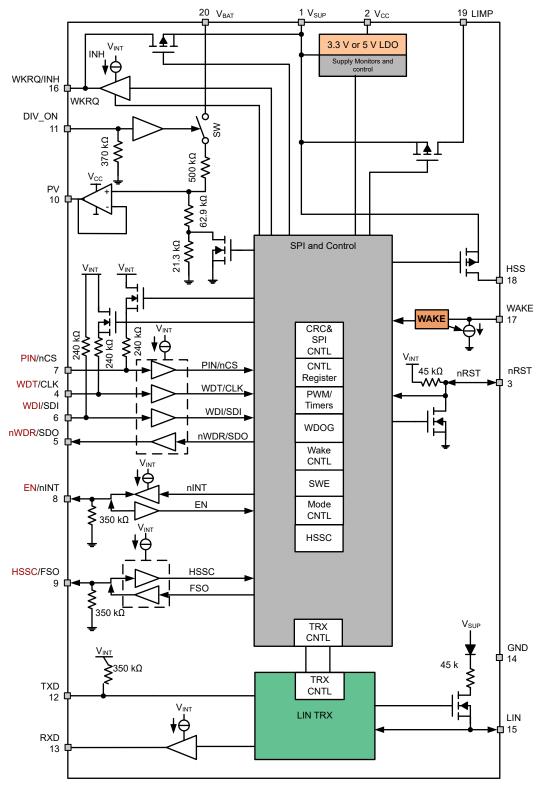

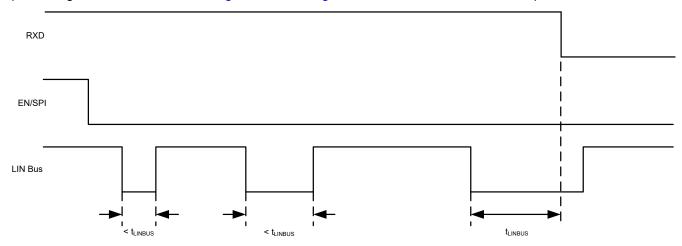

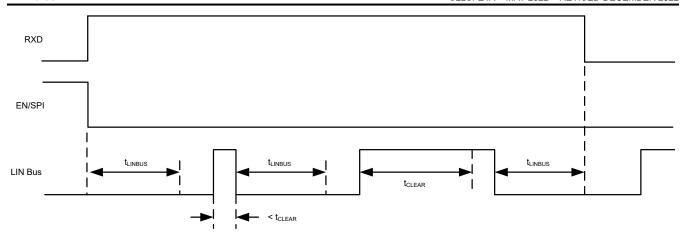

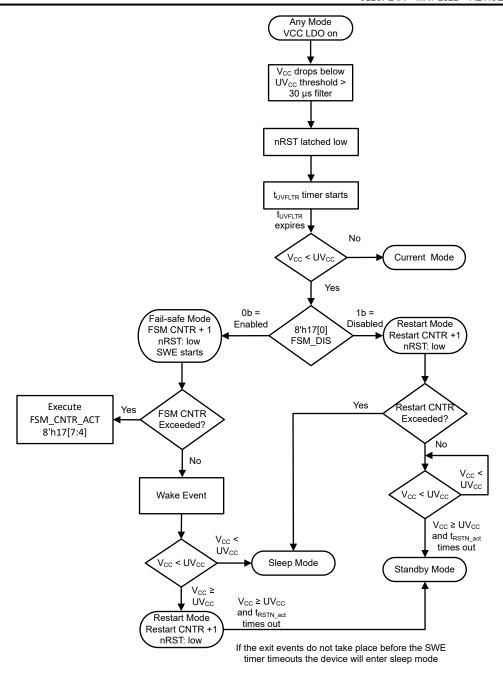

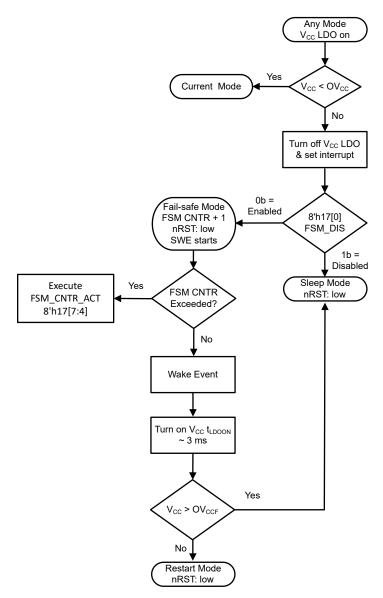

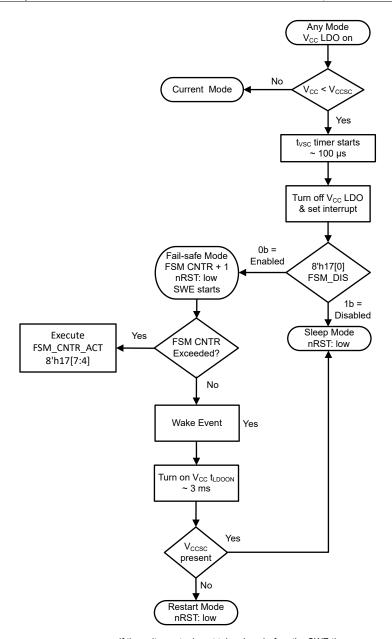

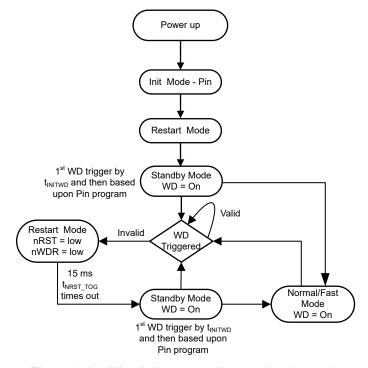

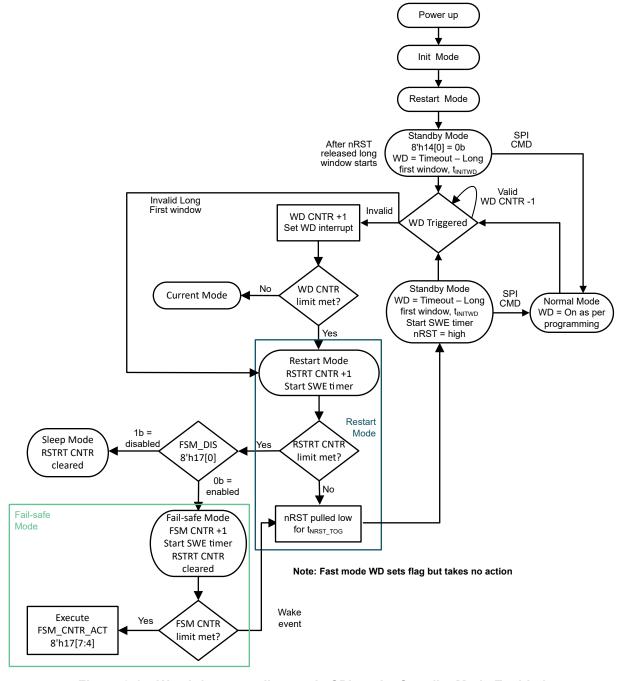

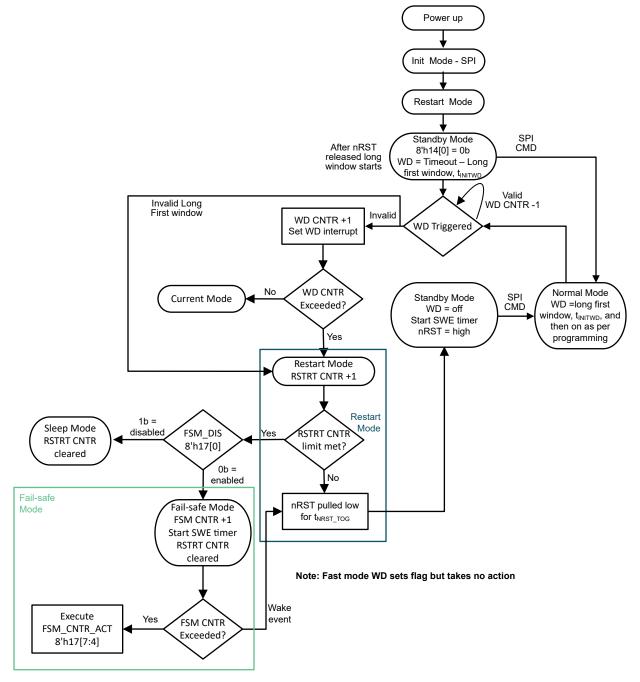

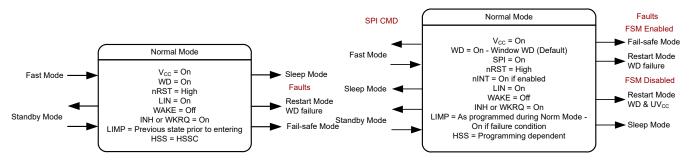

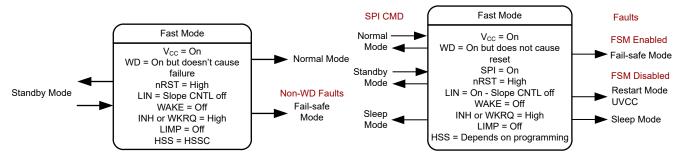

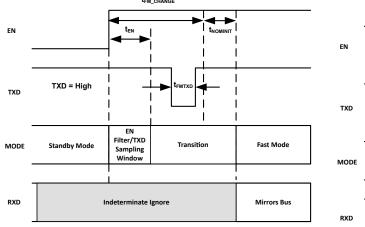

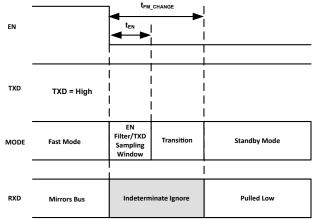

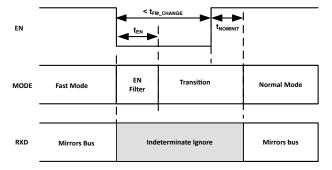

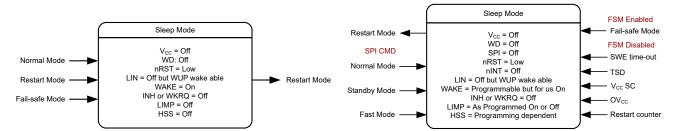

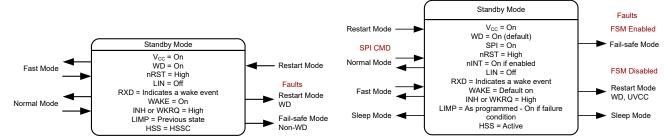

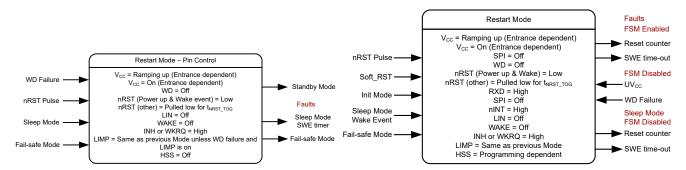

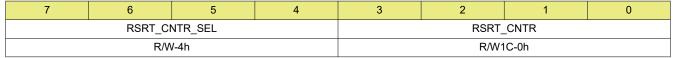

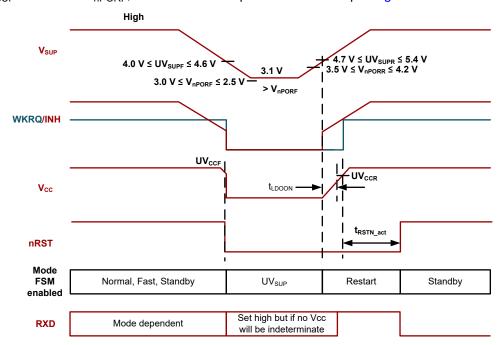

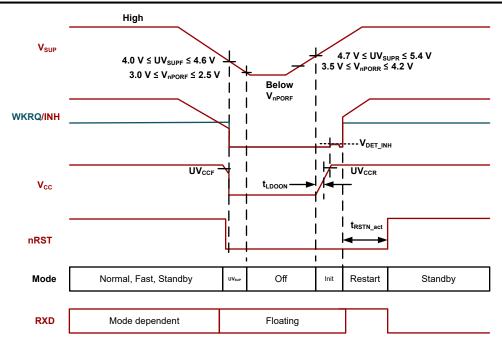

| <b>Duty Cycle Ch</b>     | aracteristics                                                                                             |                                                                                                                                                                                                                                                                                                               |             |    |       |      |  |