SNVSC61A - AUGUST 2022 - REVISED DECEMBER 2022

LP5891-Q1

# LP5891-Q1 Automotive 48 Current Sources, 64 Scans, Common Cathode LED Matrix Driver

#### 1 Features

- AEC-Q100-qualified for automotive applications:

- Temperature grade 1: –40°C to +125°C, T<sub>A</sub>

- Separated V<sub>CC</sub> and V<sub>R/G/B</sub> power supply

- V<sub>CC</sub> voltage range: 2.5 V 5.5 V

- V<sub>R/G/B</sub> voltage range: 2.5 V − 5.5 V

- 48 current source channels from 0.2 mA to 20 mA

- Channel-to-channel accuracy: ±0.5% (typ.), ±2% (max.); device-to-device accuracy: ±0.5% (typ.), ±2% (max.)

- Low knee voltage: 0.27 V (max.) when I<sub>OUT</sub> = 5

- 3-bits (8 steps) global brightness control

- 8-bits (256 steps) color brightness control

- Maximum 16-bits (65536 steps) PWM grayscale control

- 16 scan line switches with 190-mΩ R<sub>DS(ON)</sub>

- Ultra-low power consumption

- Independent V<sub>CC</sub> down to 2.5 V

- Lowest I<sub>CC</sub> down to 3.6 mA with 50-MHz GCLK

- Intelligent power saving mode with I<sub>CC</sub> down to

- Built-in SRAM to support 1–64 multiplexing

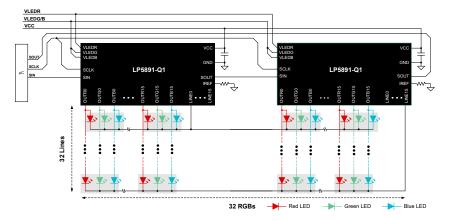

- Single device to support 48 × 16 LEDs or 16 × 16 RGB pixels

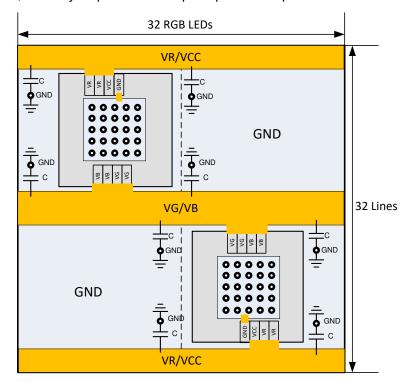

- Dual devices stackable to support 96 × 32 LEDs or 32 × 32 RGB pixels

- Three devices stackable to support 144 × 48 LEDs or 48 × 48 RGB pixels

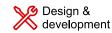

- Four devices stackable to support 192 × 64 LEDs or 64 × 64 RGB pixels

- High speed and low EMI Continuous Clock Series Interface (CCSI)

- Only three wires: SCLK / SIN / SOUT

- External 50-MHz (max.) SCLK with rising-edge transmission mechanism

- Internal frequency multiplier to support high frequency GCLK

- Optimized performances for LED matrix displays

- Upside and downside ghosting removal

- Low grayscale enhancement

- LED open, weak-short, short detection and removal

## 2 Applications

- Automotive interior light

- Automotive rear light

- Automotive local dimming backlight

## 3 Description

The LP5891-Q1 is a highly integrated, commoncathode LED matrix driver with 48 constant current sources and 16 scanning FETs. The LP5891-Q1 implements a high speed rising-edge transmission interface to support high device count daisy-chained while minimizing electrical-magnetic interference (EMI) and internal GCLK rate ranges from 40 MHz to 160 MHz. The device also implements LED open/ weak-short/short detections and removals during operations.

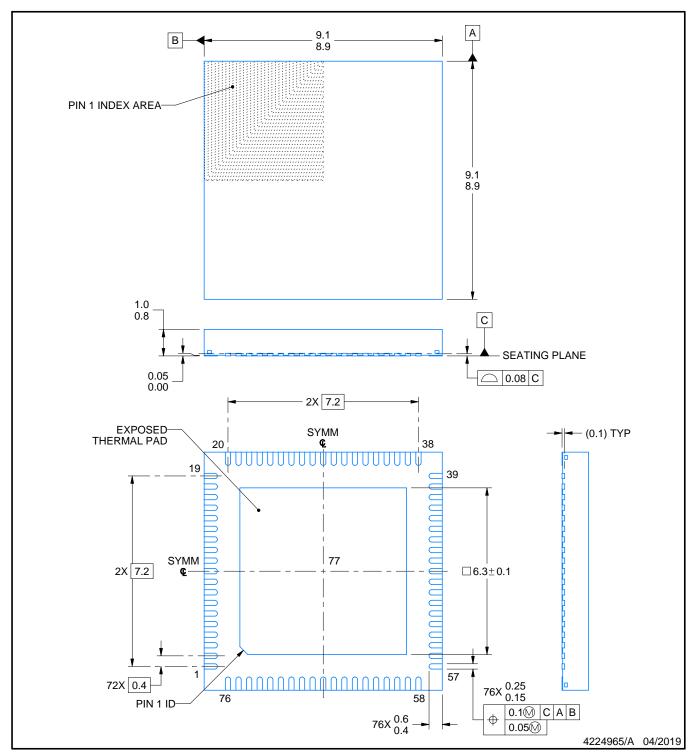

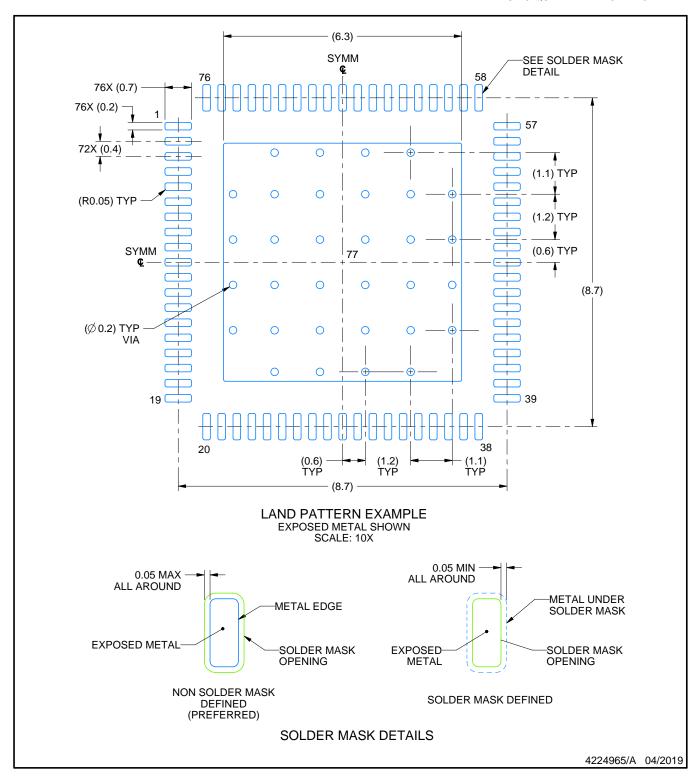

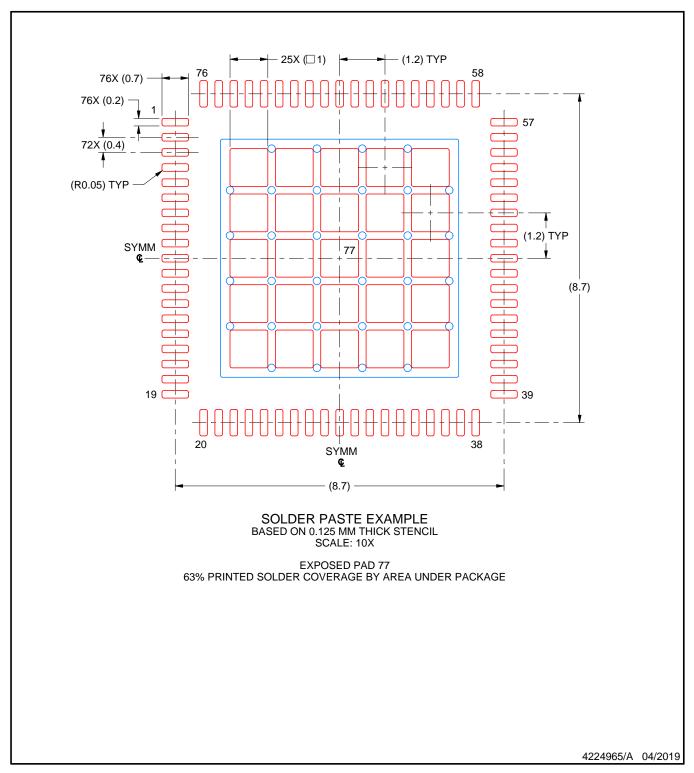

#### Package Information

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |

|-------------|------------------------|-------------------|

| LP5891-Q1   | VQFN (76)              | 9.00 mm × 9.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

LP5891-Q1 with Four Devices Stackable Connection

## **Table of Contents**

| 1 Features1                           | 8.4 Device Functional Modes25                          |

|---------------------------------------|--------------------------------------------------------|

| 2 Applications1                       | 8.5 Continuous Clock Series Interface25                |

| 3 Description                         | 8.6 PWM Grayscale Control31                            |

| 4 Revision History2                   | 8.7 Register Maps34                                    |

| 5 Description (continued)2            | 9 Application and Implementation49                     |

| 6 Pin Configuration and Functions3    | 9.1 Application Information49                          |

| 7 Specifications5                     | 9.2 Typical Application49                              |

| 7.1 Absolute Maximum Ratings5         | 9.3 Power Supply Recommendations55                     |

| 7.2 ESD Ratings5                      | 9.4 Layout55                                           |

| 7.3 Recommended Operating Conditions5 | 10 Device and Documentation Support60                  |

| 7.4 Thermal Information5              | 10.1 Documentation Support60                           |

| 7.5 Electrical Characteristics6       | 10.2 Receiving Notification of Documentation Updates60 |

| 7.6 Timing Requirements9              | 10.3 Support Resources60                               |

| 7.7 Switching Characteristics9        | 10.4 Trademarks60                                      |

| 7.8 Typical Characteristics10         | 10.5 Electrostatic Discharge Caution60                 |

| 8 Detailed Description12              | 10.6 Glossary60                                        |

| 8.1 Overview                          | 11 Mechanical, Packaging, and Orderable                |

| 8.2 Functional Block Diagram12        | Information61                                          |

| 8.3 Feature Description13             |                                                        |

## **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Revision * (August 2022) to Revision A (December 2022) | Page |

|----|--------------------------------------------------------------------|------|

| •  | Changed device status from Advance Information to Production Data  | 1    |

## 5 Description (continued)

The LP5891-Q1 is a highly integrated common cathode matrix LED display driver with 48 constant current sources and 16 scanning FETs. Besides driving 16 × 16 and 32 × 32 RGB LED pixels as LP5890, three LP5891-Q1 devices are capable of driving 48 × 48 RGB LED pixels and stacking four LP5891-Q1 devices can drive 64 × 64 RGB LED pixels. To achieve low power consumption, the device supports separated power supplies for the red, green, and blue LEDs by its common cathode structure. Furthermore, the operation power of the LP5891-Q1 is significantly reduced by ultra-low operation voltage range (Vcc down to 2.5 V) and ultra-low operation current (Icc down to 3.6 mA).

The LP5891-Q1 implements a high speed rising-edge transmission interface to support high device count daisy-chained and high refresh rate while minimizing electrical-magnetic interference (EMI). The device supports up to 50-MHz SCLK (external) and up to 160-MHz GCLK (internal). Meanwhile, the device integrates enhanced circuits and intelligent algorithms to solve the various display challenges in Narrow Pixel Pitch (NPP) LED display applications and mini and micro-LED products: dim at the first scan line, upper and downside ghosting, non-uniformity in low grayscale, coupling, caterpillar caused by open or short LEDs, which make the LP5891-Q1 a perfect choice in such applications.

The LP5891-Q1 also implements LED open/weak short/short detections and removals during operations and can also report those information out to the accompanying digital processor.

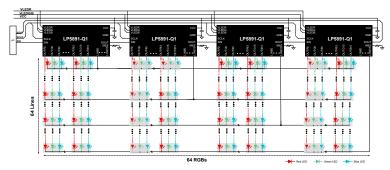

# **6 Pin Configuration and Functions**

Figure 6-1. LP5891-Q1 RRF Package, 76-Pin VQFN With Exposed Thermal Pad (Top View)

**Table 6-1. Pin Functions**

|                                    | PIN                                                                      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                   |  |  |

|------------------------------------|--------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME RRF NO.                       |                                                                          | 1/0 | DESCRIPTION .                                                                                                                                                                                                                                                                                                 |  |  |

| IREF                               | 20                                                                       | I   | Pin for setting the maximum constant-current value. Connecting an external resistor between IREF and GND sets the maximum current for each constant-current output channel. When this pin is connected directly to GND, all outputs are forced off. The external resistor must be placed close to the device. |  |  |

| VCC                                | 8                                                                        | ı   | Device power supply                                                                                                                                                                                                                                                                                           |  |  |

| VR                                 | VR 9, 10 I                                                               |     | Red LED power supply                                                                                                                                                                                                                                                                                          |  |  |

| VG 51, 50 I Green LED power supply |                                                                          |     |                                                                                                                                                                                                                                                                                                               |  |  |

| VB                                 | 49, 48                                                                   | ı   | Blue LED power supply                                                                                                                                                                                                                                                                                         |  |  |

| R0-R15                             | 1, 4, 11, 14,<br>17, 21, 24,<br>27, 32, 35,<br>38, 41, 44,<br>47, 54, 57 | 0   | Red LED constant-current output                                                                                                                                                                                                                                                                               |  |  |

| G0-G15                             | 2, 5, 12, 15,<br>18, 22, 25,<br>28, 31, 34,<br>37, 40, 43,<br>46, 53, 56 | 0   | Green LED constant-current output                                                                                                                                                                                                                                                                             |  |  |

| B0-B15                             | 3, 6, 13, 16,<br>19, 23, 26,<br>29, 30, 33,<br>36, 39, 42,<br>45, 52, 55 | 0   | Blue LED constant-current output                                                                                                                                                                                                                                                                              |  |  |

## **Table 6-1. Pin Functions (continued)**

| Р                | IN                                                                         | I/O | DESCRIPTION                                                              |  |

|------------------|----------------------------------------------------------------------------|-----|--------------------------------------------------------------------------|--|

| NAME             | RRF NO.                                                                    | 1/0 | DESCRIPTION                                                              |  |

| LINE0-<br>LINE15 | 76, 75, 74,<br>73, 72, 71,<br>70, 69, 68,<br>67, 66, 65,<br>64, 63, 62, 61 | 0   | Scan lines                                                               |  |

| SCLK             | 60                                                                         | 1   | Clock-signal input pin                                                   |  |

| SIN              | 59                                                                         | I   | Serial-data input pin                                                    |  |

| SOUT             | 58                                                                         | 0   | Serial data output pin                                                   |  |

| GND              | 7                                                                          | _   | Power-ground reference                                                   |  |

| Thermal pad      | _                                                                          | _   | The thermal pad and the GND pin must be connected together on the board. |  |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                | ,                     | N | IN  | MAX | UNIT |

|------------------------------------------------|-----------------------|---|-----|-----|------|

|                                                | V <sub>CC</sub>       | _ | ).3 | 6   | V    |

|                                                | $V_{R/G/B}$           | _ | ).3 | 6   | V    |

| Voltage                                        | IREF, SCLK, SIN, SOUT | _ | ).3 | 6   | V    |

|                                                | RX/GX/BX              | _ | ).3 | 6   | V    |

|                                                | LINE0 to LINE15       | _ | ).3 | 6   | V    |

| Operating junction temperature, T <sub>J</sub> |                       | _ | 40  | 150 | °C   |

| Storage temperature, T <sub>stg</sub>          |                       | _ | 55  | 150 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 7.2 ESD Ratings

|                    |                          |                                                                                            | VALUE | UNIT |

|--------------------|--------------------------|--------------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge  | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD classification level 3A | ±4000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discriarge | Charged-device model (CDM), per AEC Q100-011<br>CDM ESD classification level C6            | ±1000 | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                            | MIN       | NOM MAX   | UNIT |

|-------------------|--------------------------------------------|-----------|-----------|------|

| VCC               | Device supply voltage                      | 2.5       | 5.5       | V    |

| VLEDR/G/B         | LED supply voltage                         | 2.5       | 5.5       | V    |

| V <sub>IH</sub>   | High level logic input voltage (SCLK, SIN) | 0.7 × VCC |           | V    |

| V <sub>IL</sub>   | Low level logic input voltage (SCLK, SIN)  |           | 0.3 × VCC | V    |

| I <sub>OH</sub>   | High level logic output current (SOUT)     |           | -2        | mA   |

| I <sub>OL</sub>   | Low level logic output current (SOUT)      |           | 2         | mA   |

| I <sub>CH</sub>   | Constant output source current             | 0.2       | 20        | mA   |

| I <sub>LINE</sub> | Line scan switch load current              | 0         | 2         | Α    |

| T <sub>A</sub>    | Ambient operating temperature              | -40       | 125       | °C   |

#### 7.4 Thermal Information

|                        |                                              | LP5891-Q1  |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC(1)                            | RRF (VQFN) | UNIT |

|                        |                                              | 76 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 22.2       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 10.7       | °C/W |

| R <sub>θJB</sub>       | Junction-to-board thermal resistance         | 7.2        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.1        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 7.1        | °C/W |

## 7.4 Thermal Information (continued)

|                                   |                                    | LP5891-Q1  | UNIT |

|-----------------------------------|------------------------------------|------------|------|

|                                   | THERMAL METRIC <sup>(1)</sup>      | RRF (VQFN) | UNIT |

|                                   |                                    | 76 PINS    |      |

| R <sub>θJC(bot)</sub> Junction-to | o-case (bottom) thermal resistance | 1.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

At  $V_{CC} = V_R = 2.8 \text{ V}$ ,  $V_{G/B} = 3.8 \text{ V}$ ,  $T_A = -40 ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ ; Typical values are at  $T_A = 25 ^{\circ}\text{C}$  (unless otherwise specified)

|                      | PARAMETER                                            | TEST CONDITIONS                                                                                                                                                                                                     | MIN       | TYP MAX   | UNIT |

|----------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|------|

| V <sub>CC</sub>      | Device supply voltage                                |                                                                                                                                                                                                                     | 2.5       | 5.5       | V    |

| / <sub>UVR</sub>     | Undervoltage restart                                 | VCC rising                                                                                                                                                                                                          |           | 2.3       | V    |

| / <sub>UVF</sub>     | Undervoltage shutdown                                | VCC falling                                                                                                                                                                                                         | 2.0       |           | V    |

| / <sub>UV(HYS)</sub> | Undervoltage shutdown hysteresis                     |                                                                                                                                                                                                                     |           | 0.1       | V    |

|                      |                                                      | SCLK/SIN = 10 MHz,<br>MPSM_EN=1bit, Matrix PSM enable,<br>internal GCLK off, GSn = 0000h, BC<br>= 2h, CCR/G/B = 63h, PS_EN= 1h,<br>VOUTn = floating, R <sub>IREF</sub> = 7.8 kΩ (In<br>intelligent power save mode) |           | 0.9       | mA   |

|                      |                                                      | SCLK/SIN = 10 MHz, Standby enable, internal GCLK off, GSn = 0000h, BC = 2h, CCR/G/B = 63h, PS_EN= 1h, VOUTn = floating, $R_{IREF}$ = 7.8 k $\Omega$ (In intelligent power save mode)                                |           | 0.9       | mA   |

| lcc                  | Device supply current                                | SCLK/SIN = 10 MHz,<br>PSP_MOD=1bit, internal<br>GCLK=50MHz, GSn = 0000h, BC =<br>2h, CCR/G/B = 63h, PS_EN= 1h,<br>VOUTn = floating, R <sub>IREF</sub> = 7.8 kΩ (In<br>power save mode)                              |           | 3.6       | mA   |

|                      |                                                      | SCLK = 10 MHz, internal GCLK = 50 MHz, GSn = 1FFFh, BC = 2h, CCR/G/B = 63h,VOUTn = floating, R <sub>IREF</sub> = 7.8 kΩ, I <sub>CH</sub> = 2 mA                                                                     |           | 3.6       | mA   |

|                      |                                                      | SCLK = 10 MHz, internal GCLK = 100 MHz, GSn = 1FFFh, BC = 2h, CCR/G/B = 63h, VOUTn = floating, $R_{IREF}$ = 7.8 k $\Omega$ , $I_{CH}$ = 2 mA                                                                        |           | 4.9       | mA   |

| / <sub>R/G/B</sub>   | LED supply voltage                                   |                                                                                                                                                                                                                     | 2.5       | 5.5       | V    |

| / <sub>ІН</sub>      | High level input voltage (SCLK, SIN)                 |                                                                                                                                                                                                                     | 0.7 × VCC |           | V    |

| / <sub>IL</sub>      | Low level input voltage (SCLK, SIN)                  |                                                                                                                                                                                                                     |           | 0.3 × VCC | V    |

| /он                  | High level output voltage (SOUT)                     | IOH = -2 mA at SOUT                                                                                                                                                                                                 | VCC-0.4   | VCC       | V    |

| OL                   | Low level output voltage (SOUT)                      | IOL = 2 mA at SOUT                                                                                                                                                                                                  |           | 0.4       | V    |

| OGIC                 | Logic pin current (SCLK, SIN)                        | SCLK/SIN = VCC or GND                                                                                                                                                                                               | -1        | 1         | uA   |

| R <sub>DS(ON)</sub>  | Scan switches' on-state resistance (LINE0 to LINE15) | VCC = 2.8 V, T <sub>A</sub> = 25°C                                                                                                                                                                                  |           | 190       | mΩ   |

| $V_{IREF}$           | Reference voltage                                    | SCLK/SIN = GND, internal GCLK=<br>0MHz, GSn = 0000h, BC = 2h,<br>CCR/G/B = 63h, VOUTn = floating,<br>$R_{IREF}$ = 7.8 k $\Omega$                                                                                    |           | 0.8       | V    |

Submit Document Feedback

## 7.5 Electrical Characteristics (continued)

At  $V_{CC} = V_R = 2.8 \text{ V}$ ,  $V_{G/B} = 3.8 \text{ V}$ ,  $T_A = -40 ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ ; Typical values are at  $T_A = 25 ^{\circ}\text{C}$  (unless otherwise specified)

|                       | PARAMETER                                                                               | TEST CONDITIONS                                                                                                                                                                                                                                                                               | MIN | TYP  | MAX  | UNIT |

|-----------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

|                       |                                                                                         | VLEDR/G/B ≥ 2.8 V, all channel outputs on, output current at 1 mA                                                                                                                                                                                                                             |     |      | 0.25 | V    |

|                       |                                                                                         | VLEDR/G/B ≥ 2.8 V, all channel outputs on, output current at 5 mA                                                                                                                                                                                                                             |     |      | 0.27 | V    |

| $V_{KNEE}$            | Channel knee voltage (R0-R15 /                                                          | VLEDR/G/B ≥ 2.8 V, all channel outputs on, output current at 10 mA                                                                                                                                                                                                                            |     |      | 0.31 | V    |

| · KNLL                | G0-G15 / B0-B15)                                                                        | VLEDR/G/B ≥ 2.8 V, IMAX = 1b, all channel outputs on, output current at 15 mA                                                                                                                                                                                                                 |     |      | 0.37 | ٧    |

|                       |                                                                                         | VLEDR/G/B ≥ 2.8 V, IMAX=1b, all channel outputs on, output current at 20 mA                                                                                                                                                                                                                   |     |      | 0.41 | V    |

| CH(LKG)               | Channel leakage current (R0-<br>R15 / G0-G15 / B0-B15)                                  | Channel voltage at 0 V                                                                                                                                                                                                                                                                        |     |      | 1    | uA   |

|                       | Constant-current channel to channel deviation (R0-R15 / G0-G15 / B0-B15) <sup>(1)</sup> | All CHn = on, BC = 00h, CC = 31h, VOUTn = (VLED-1)V, $R_{IREF}$ = 19.05 k $\Omega$ ( $I_{CH}$ = 0.2-mA target), $T_A$ = 25°C, includes the $V_{IREF}$ tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15                                                                    |     | ±1   | ±2.5 | %    |

|                       |                                                                                         | All CHn = on, BC = 00h, CC = 7Dh, VOUTn = (VLED-1)V, $R_{IREF}$ = 19.05 k $\Omega$ ( $I_{CH}$ = 0.5-mA target), $T_A$ = 25°C, includes the $V_{IREF}$ tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15                                                                    |     | ±0.5 | ±1.5 | %    |

|                       |                                                                                         | All CHn = on, BC = 00h, CC = FBh, VOUTn = (VLED-1)V, R <sub>IREF</sub> = 19.05 k $\Omega$ (I <sub>CH</sub> = 1-mA target), T <sub>A</sub> = 25°C, includes the V <sub>IREF</sub> tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15                                         |     | ±0.5 | ±1.5 | %    |

| ∆I <sub>ERR(CC)</sub> |                                                                                         | All CHn = on, BC = 2h, CC = FBh, VOUTn = (VLED-1)V, $R_{IREF}$ = 7.8 k $\Omega$ ( $I_{CH}$ = 5-mA target), $T_A$ = 25°C, includes the $V_{IREF}$ tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15                                                                         |     | ±0.5 | ±2.5 | %    |

|                       |                                                                                         | All CHn = on, BC = 6h, CC = A7h, VOUTn = (VLED-1)V, $R_{IREF}$ = 7.8 k $\Omega$ ( $I_{CH}$ = 10-mA target), $T_{A}$ = 25°C, includes the $V_{IREF}$ tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15                                                                      |     | ±0.5 | ±2.5 | %    |

|                       |                                                                                         | All CHn = on, BC = 7h, CC = FBh, IMAX=1b, VOUTn = (VLED-1)V, R <sub>IREF</sub> = $6.8 \text{ k}\Omega$ (I <sub>CH</sub> = $20\text{-mA}$ target), T <sub>A</sub> = $25^{\circ}\text{C}$ , includes the V <sub>IREF</sub> tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15 |     | ±0.5 | ±2.7 | %    |

## 7.5 Electrical Characteristics (continued)

At  $V_{CC} = V_R = 2.8 \text{ V}$ ,  $V_{G/B} = 3.8 \text{ V}$ ,  $T_A = -40 ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ ; Typical values are at  $T_A = 25 ^{\circ}\text{C}$  (unless otherwise specified)

|                        | PARAMETER                                                  | TEST CONDITIONS                                                                                                                                                                                                                                                               | MIN TYF | MAX    | UNIT |

|------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|------|

|                        |                                                            | All CHn = on, BC = 00h, CC = 31h, VOUTn = (VLED-1)V, R <sub>IREF</sub> = 19.05 k $\Omega$ (I <sub>CH</sub> = 0.2-mA target), T <sub>A</sub> = 25°C, includes the V <sub>IREF</sub> tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15                       | ±       | l ±2.5 | %    |

|                        |                                                            | All CHn = on, BC = 00h, CC = 7Dh, VOUTn = (VLED-1)V, $R_{IREF}$ = 19.05 k $\Omega$ ( $I_{CH}$ = 0.5-mA target), $T_A$ = 25°C, includes the $V_{IREF}$ tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15                                                    | ±0.5    | 5 ±1.5 | %    |

|                        | Constant-current device to                                 | All CHn = on, BC = 00h, CC = FBh, VOUTn = (VLED-1)V, R <sub>IREF</sub> = 19.05 k $\Omega$ (I <sub>CH</sub> = 1-mA target), T <sub>A</sub> = 25°C, includes the V <sub>IREF</sub> tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15                         | ±0.5    | 5 ±1   | %    |

|                        | device deviation (R0-R15 / G0-G15 / B0-B15) <sup>(2)</sup> | All CHn = on, BC = 2h, CC = FBh, VOUTn = (VLED-1)V, $R_{IREF}$ = 7.8 k $\Omega$ ( $I_{CH}$ = 5-mA target), $T_A$ = 25°C, includes the $V_{IREF}$ tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15                                                         | ±0.5    | 5 ±1.5 | %    |

|                        |                                                            | All CHn = on, BC = 6h, CC = A7h, VOUTn = (VLED-1)V, $R_{IREF}$ = 7.8 k $\Omega$ ( $I_{CH}$ = 10-mA target), $T_A$ = 25°C, includes the $V_{IREF}$ tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15                                                        | ±0.5    | 5 ±2   | %    |

|                        |                                                            | All CHn = on, BC = 7h, CC = FBh, IMAX=1b, VOUTn = (VLED-1)V, R <sub>IREF</sub> = $6.8 \text{ k}\Omega$ (I <sub>CH</sub> = 20-mA target), T <sub>A</sub> = $25^{\circ}$ C, includes the V <sub>IREF</sub> tolerance, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15 | ±0.6    | 5 ±2   | %    |

| $\Delta I_{REG(LINE)}$ | Line regulation (R0-R15 / G0-G15 / B0-B15) <sup>(3)</sup>  | VLED = 2.5 to 5.5V, All CHn = on, VOUTn = (VLED-1)V, at same color grouped outputs of R0-R15 / G0-G15 / B0-B15                                                                                                                                                                |         | ±1     | %/V  |

| $\Delta I_{REG(LOAD)}$ | Load regulation (R0-R15 / G0-G15 / B0-B15) <sup>(4)</sup>  | VOUTn = (VLED-1)V to (VLED-3)V,<br>VR=VG/B=VLED=3.8V, All CHn =<br>on, at same color grouped outputs of<br>R0-R15 / G0-G15 / B0-B15                                                                                                                                           |         | ±1     | %/V  |

| T <sub>TSD</sub>       | Thermal shutdown threshold                                 |                                                                                                                                                                                                                                                                               | 170     | )      | °C   |

| T <sub>HYS</sub>       | Thermal shutdown hysteresis                                |                                                                                                                                                                                                                                                                               | 15      | 5      | °C   |

(1) The deviation of each output in same color group (OUTR0-15 or OUTG0-15 or OUTB0-15) from the average of same color group

$$\Delta(\%) = \left[\frac{I_{Xn}}{\frac{I_{X0} + I_{X1} + \dots + I_{X14} + I_{X15}}{16}} - 1\right] \times 100$$

constant current. The deviation is calculated by the formula. (X = R or G or B, n = 0-15)

(2) The deviation of the average of constant-current in each color group from the ideal constant-current value. (X = R or G or B):

$$\Delta(\%) = \begin{bmatrix} \frac{I_{X0} + I_{X1} + \dots + I_{X14} + I_{X15}}{16} - \text{Ideal Output Current} \\ \hline Ideal Output Current} \end{bmatrix} \times 100$$

$$I_{IDEAL\_R(or\ G\ or\ B)} = \frac{V_{IREF}}{R_{IREF}} \times GAIN_{(BC)} \times \frac{1 + CC\_R(or\ CC\_G\ or\ CC\_B)}{256}$$

Line regulation is calculated by the following equation. (X = R or G or B, n = 0-15):

$$\Delta\left(\%V\right) = \left[\frac{\left(I_{Xn} \ at \ V_{LED} = 5.5 \ V\right) - \left(I_{Xn} \ at \ V_{LED} = 2.5 \ V\right)}{\left(I_{Xn} \ at \ V_{LED} = 2.5 \ V\right)}\right] \times \frac{100}{5.5 \ V - 2.5 \ V}$$

Load regulation is calculated by the following equation. (X = R or G or B, n = 0-15):

$$\Delta\left(\%V\right) = \left[\frac{\left(I_{Xn} \ at \ V_{Xn} = 1 \ V\right) - \left(I_{Xn} \ at \ V_{Xn} = 3 \ V\right)}{\left(I_{Xn} \ at \ V_{Xn} = 3 \ V\right)}\right] \times \frac{100}{3 \ V - 1 \ V}$$

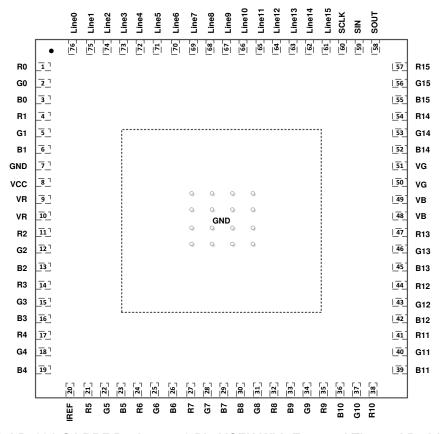

## 7.6 Timing Requirements

At  $V_{CC} = V_R = 2.8 \text{ V}$ ,  $V_{G/B} = 3.8 \text{ V}$ ,  $T_A = -40 ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ ; Typical values are at  $T_A = 25 ^{\circ}\text{C}$  (unless otherwise specified)

|                    | PARAMETER                        | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|----------------------------------|-----------------|-----|-----|-----|------|

| f <sub>SCLK</sub>  | Clock frequency (SCLK)           |                 |     |     | 50  | MHz  |

| t <sub>w(H0)</sub> | High level pulse duration (SCLK) |                 | 9   |     |     | ns   |

| t <sub>w(L0)</sub> | Low level pulse duration (SCLK)  |                 | 9   |     |     | ns   |

| t <sub>su(0)</sub> | Set-up time                      | SIN to SCLK↑    | 10  |     |     | ns   |

| t <sub>h(0)</sub>  | Hold time                        | SCLK↑ to SIN↑↓  | 2   |     |     | ns   |

## 7.7 Switching Characteristics

At  $V_{CC} = V_R = 2.8 \text{ V}$ ,  $V_{G/B} = 3.8 \text{ V}$ ,  $T_A = -40^{\circ}\underline{C}$  to +125°C; Typical values are at  $T_A = 25^{\circ}C$  (unless otherwise specified)

|                    | PARAMETER         | TEST CONDITIONS                                                                             | MIN | TYP | MAX  | UNIT |

|--------------------|-------------------|---------------------------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>r</sub>     | Rise time (SOUT)  | VCC = 3.3 V, C <sub>SOUT</sub> = 30 pF                                                      |     | 2   | 10   | ns   |

| t <sub>f</sub>     | Fall time (SOUT)  | VCC = 3.3 V, C <sub>SOUT</sub> = 30 pF                                                      |     | 2   | 10   | ns   |

| t <sub>pd(0)</sub> | Propagation delay | SCLK $\uparrow$ to SOUT $\uparrow\downarrow$ , full temperature, $C_{SOUT} = 30 \text{ pF}$ | 3.5 |     | 14.2 | ns   |

(1). Input pulse rise and fall time is 2 ns typically.

Figure 7-1. Timing and Switching Diagram

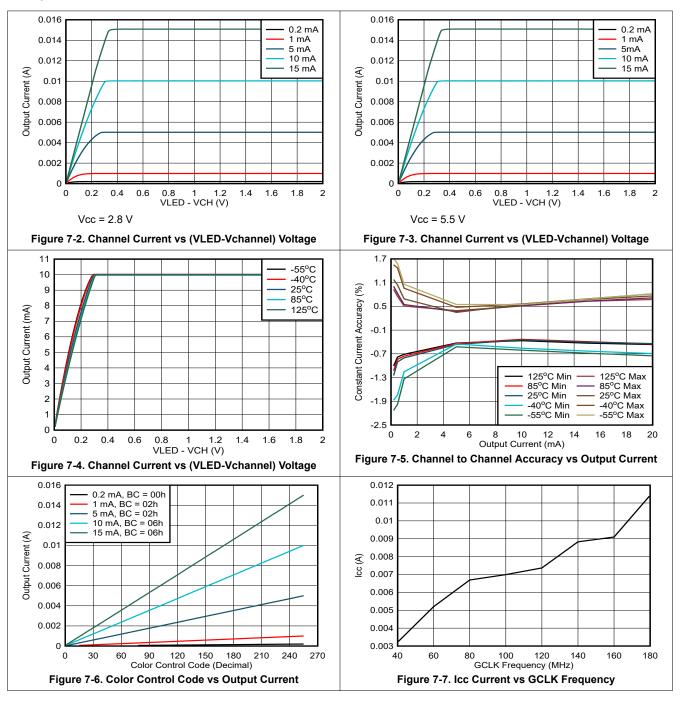

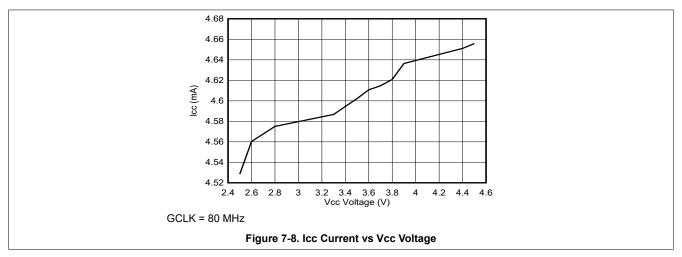

## 7.8 Typical Characteristics

# 7.8 Typical Characteristics (continued)

## **8 Detailed Description**

### 8.1 Overview

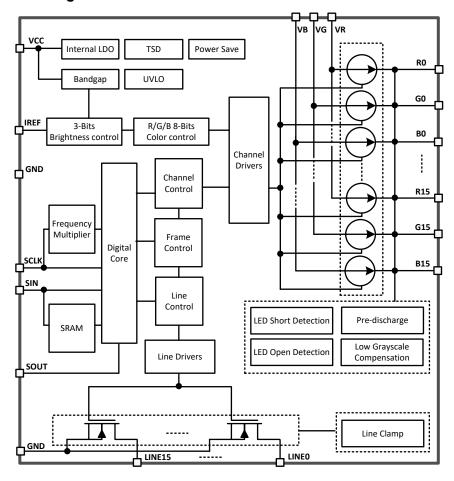

The LP5891-Q1 is a highly integrated RGB LED driver with 48 constant current sources and 16 scanning FETs. A single LP5891-Q1 is capable of driving  $16 \times 16$  RGB LED pixels while stacking four LP5891-Q1 devices can drive  $64 \times 64$  RGB LED pixels. To achieve low power consumption, the device supports separated power supplies for the red, green, and blue LEDs by its common cathode structure. Furthermore, the operation power of the LP5891-Q1 is significantly reduced by ultra-low operation voltage range ( $V_{CC}$  down to  $V_{CC}$

The LP5891-Q1 supports 0.2 mA to 20 mA per channel with typical 0.5% channel-to-channel current deviation and typical 0.5% device-to-device current deviation. The DC current value of all 48 channels is set by an external IREF resistor and can be adjusted by the 8-step global brightness control (BC) and the 256-step per-color group brightness control (CC R/CC G/CC B).

The LP5891-Q1 implements a high speed rising-edge transmission interface to support high device count daisy-chained and high refresh rate while minimizing electrical-magnetic interference (EMI). The LP5891-Q1 supports up to 50-MHz SCLK (external) and up to 160-MHz GCLK (internal).

The LP5891-Q1 also implements LED open, weak-short, and short detections and can also report this information out to the accompanying digital processor.

## 8.2 Functional Block Diagram

Submit Document Feedback

### 8.3 Feature Description

#### 8.3.1 Independent and Stackable Mode

The LP5891-Q1 can operate in two different modes: independent or stackable. In independent mode, a single LP5891-Q1 can drive a 16 × 16 RGB LED matrix, while in stackable mode, up to four LP5891-Q1 devices can be stacked together, which means the line switches of one device can be shared to the others. Stacking three LP5891-Q1 devices can drive a 48 × 48 RGB LED matrix while stacking four LP5891-Q1 devices can drive a 64 × 64 RGB matrix. The mode can be configured by the MOD SIZE (see FC2 for more details).

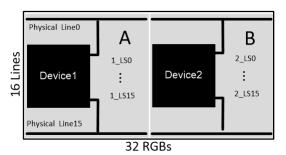

### 8.3.1.1 Independent Mode

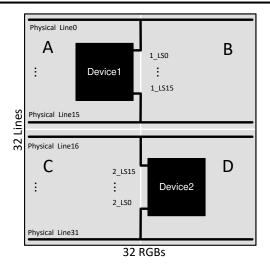

Figure 8-1 shows an implementation of a 16 × 32 RGB LED matrix using two LP5891-Q1 devices in independent mode. Each device is responsible for its own 16 ×16 RGB LED matrix, which means that all the data for section A is stored in device 1 and the data for section B is stored in device 2.

Figure 8-1. Two Devices in Independent Mode

The unused line must be assigned to the last several lines of the device. For example, if there are only 14 scanning lines, then the two unused lines must be assigned to 1 LS14 and 1 LS15.

#### 8.3.1.2 Stackable Mode

While operating the LP5891-Q1 in stackable mode, as shown in below table.

| Mode  | Matrix Size | Register Value | Scan Sequence      |

|-------|-------------|----------------|--------------------|

| Mode1 | 16x32       | 000b           | D1, D2 independent |

| Mode2 | 32x32       | 001b           | D1->D2             |

| Mode3 | 48x48       | 010b           | D1->D2->D3         |

| Mode4 | 48x48       | 011b           | D1->D3->D2         |

| Mode5 | 48x64       | 100b           | D1->D2->D3         |

| Mode6 | 48x64       | 101b           | D1->D3->D2         |

| Mode7 | 64x64       | 110b           | D1->D2->D3->D4     |

| Mode8 | 64x64       | 111b           | D1->D4->D3         |

Table 8-1. Stackable Mode

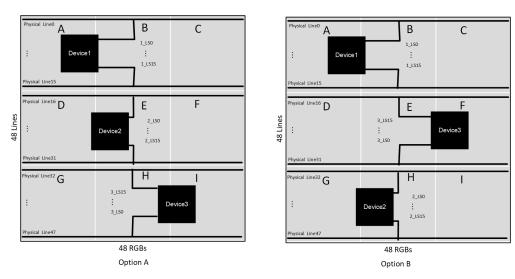

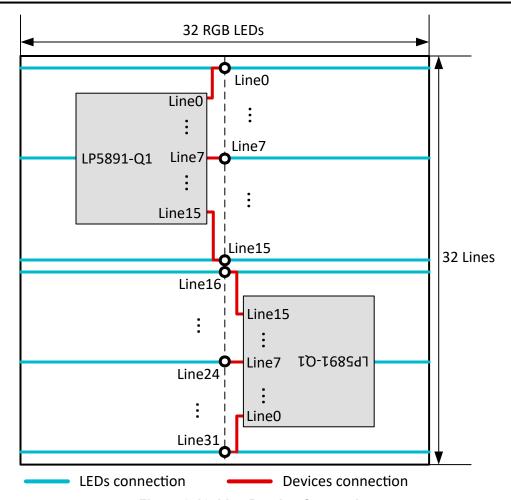

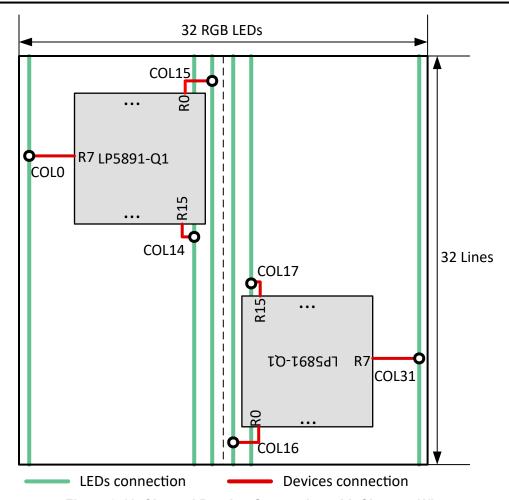

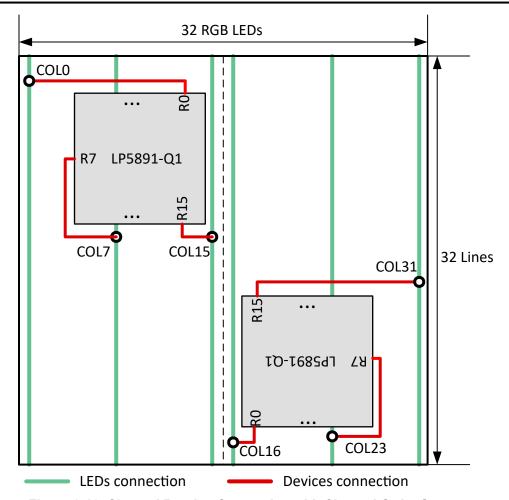

Figure 8-2 device 2 needs to be rotated 180° relative to device 1. This action allows the position of line switches to be near the center column of the LED matrix for better routing. For device 1, the lines connect sequentially (line switch 0 connected to scan line 1). However on device 2, it is connected in reverse order, with the 16<sup>th</sup> scan line is connected to line switch 15 and the 32<sup>nd</sup> scan line is connected to line switch 0.

Figure 8-2 shows the connection between two LP5891-Q1 devices in stackable mode driving 32 × 32 RGB LED pixels. The MOD\_SIZE must be configured to 001b. Device 1 supplies 16 line switches for the first 16 scan line, and device 2 supplies 16 line switches for scan line 17-32. The data for matrix sections A and C are stored in device 1, while matrix sections B and D data are stored in device 2.

To make sure the scanning sequence is still from 1<sup>st</sup> line to 32<sup>nd</sup> line, the scan line switching order of the second device must be reversed, which can be configured by the SCAN REV (see FC4 for more details).

Figure 8-2. Mode2 Diagram

Figure 8-3. Mode3 and Mode4 Diagram

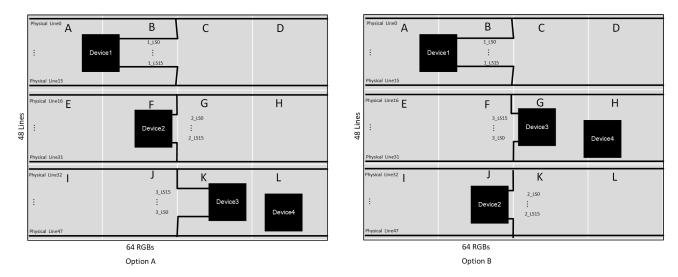

Figure 8-4. Mode5 and Mode6 Diagram

Submit Document Feedback

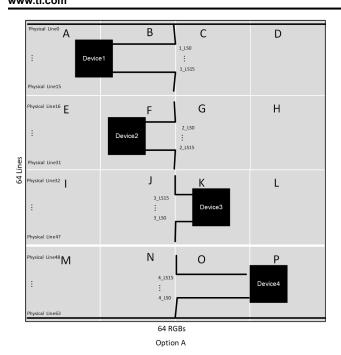

Figure 8-5. Mode7 and Mode8 Diagram

When two or more LP5891-Q1 devices are used in stackable mode, if there are unused line switches, these unused line switches must be the last line switches of the first or the second device. For example, if there are only 30 scanning lines, and if,

SCAN REV = '0'b, the unused line switches can be either of the below,

- 1 LS14, 1 LS15

- 2 LS14, 2 LS15

SCAN REV = '1'b, the unused line switches can be either of below,

- 1\_LS14, 1\_LS15

- 2 LS1, 2 LS0

The unused line switches must be 2 LS14, 2 LS15 if SCAN REV = '0'b, or 2 LS1, 2 LS0 if SCAN REV = '1'b.

#### 8.3.2 Current Setting

#### 8.3.2.1 Brightness Control (BC) Function

The LP5891-Q1 device is able to adjust the output current of all constant-current outputs simultaneously. This function is called global brightness control (BC). The global BC for all outputs is programmed with a 3-bit register, thus all output currents can be adjusted in eight steps for a given current-programming resistor,  $R_{IREF}$ . When the 3-bit BC register changes, the gain of output current,  $GAIN_{BC}$  changes as Table 8-2 below.

Table 8-2. Current Gain Versus BC Code

| BC Register (BC) | Current Gain (GAIN <sub>BC</sub> ) |

|------------------|------------------------------------|

| 000b             | 24.17                              |

| 001b             | 30.57                              |

| 010b             | 49.49                              |

| 011b (default)   | 86.61                              |

| 100b             | 103.94                             |

| 101b             | 129.92                             |

| 110b             | 148.48                             |

| 111b             | 173.23                             |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

The maximum output current per channel,  $I_{OUTSET}$ , is determined by resistor  $R_{IREF}$ , and the GAIN<sub>BC</sub>. The voltage on IREF is typically 0.8 V.  $R_{IREF}$  can be calculated by Equation 1 below. For noise immunity purpose, suggest  $R_{IREF}$  < 40 k $\Omega$ .

$$R_{IREF}(k\Omega) = \frac{V_{IREF}(V)}{I_{IREF}(mA)} = \frac{V_{IREF}(V)}{I_{OUTSET}(mA)} \times GAIN_{(BC)}$$

(1)

#### 8.3.2.2 Color Brightness Control (CC) Function

The LP5891-Q1 device is able to adjust the output current of each of the three color groups R0-R15, G0-G15, and B0-B15 separately. This function is called color brightness control (CC). For each color, it has 8-bit data register, CC\_R, CC\_G, or CC\_B. Thus, all color group output currents can be adjusted in 256 steps from 0% to 100% of the maximum output current, I<sub>OUTSET</sub>. The output current of each color, I<sub>OUT\_R (or G or B)</sub> can be calculated by Equation 2 below.

$$I_{OUT\_R(or\ G\ or\ B)} = I_{OUTSET} \times \frac{1 + CC\_R(or\ CC\_G\ or\ CC\_B)}{256}$$

(2)

Table Table 8-3 shows the CC data versus the constant-current against I<sub>OUTSET</sub>:

CC Register (CC R or CC G or Ratio of I<sub>OUTSET</sub> CC\_B) 0000 0000b 1/256 0.39% 0000 0001b 2/256 0.78% 0111 1111b (default) 50% 128/256 1111 1110b 255/256 99.61% 1111 1111b 256/256 100%

Table 8-3. CC Data vs Current Ratio

#### 8.3.2.3 Choosing BC/CC for a Different Application

BC is mainly used for global brightness adjustment to adapt to ambient brightness, such as between day and night, indoor and outdoor.

- Suggested BC is 3h or 4h, which is in the middle of the range, allowing flexible changes in brightness up and down.

- If the current of one color group (usually R LEDs) is close to the output maximum current (10 mA or 20 mA), to prevent the constant output current from exceeding the upper limit in case a larger BC code is input accidentally, choose the maximum BC value, 7h.

- If the current of one color group (usually B LEDs) is close to the output minimum current (0.2 mA), to prevent the constant output current from exceeding the lower limit in case a lower BC code is input accidentally, choose the minimum BC code, 0h.

CC can be used to fine tune the brightness in 256 steps. This is suitable for white balance adjustment between RGB color group. To get a pure white color, the general requirement for the luminous intensity ratio of R, G, B LED is 5:3:2. Depending on the characteristics of the LED (Electro-Optical conversion efficiency), the current ratio of R, G, B LED is much different from this ratio. Usually, the Red LED needs the largest current. Choose 255d (the maximum value) CC code for the color group that needs the largest initial current, then choose proper CC code for the other two color groups according to the current ratio requirement of the LED used.

### 8.3.3 Frequency Multiplier

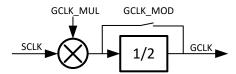

The LP5891-Q1 has an internal frequency multiplier to generate the GCLK by SCLK. The GCLK frequency can be configured by FREQ\_MOD (See FC0 for more details) and FREQ\_MUL (see FC0 for more details) from 40 MHz to 160 MHz. As Figure 8-6 shows, if the GCLK frequency is not higher than 80 MHz, the GCLK\_MOD is set

Submit Document Feedback

to 1 to disable the bypass switch (enable the  $\frac{1}{2}$  divider), while the GCLK frequency is higher than 80 MHz, the GCLK MOD is set to 0 to enable the bypass switch (disable the  $\frac{1}{2}$  divider).

Figure 8-6. Frequency Multiplier Block Diagram

#### 8.3.4 Line Transitioning Sequence

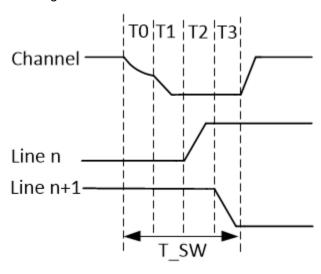

The LP5891-Q1 defines a timing sequence of scan line transition, shown as Figure 8-7. T\_SW is the total transitioning time. T\_SW is broken up into four intervals: T0 is the time interval between the end of PWM time in current segment and the beginning of channel pre-discharge, T1 is the time interval between the beginning of the channel pre-discharge and the beginning of current line OFF, T2 is the time interval that the beginning of current line OFF and the beginning of next line ON, T3 is the time interval of the beginning of next line ON and the beginning of PWM time in next segment.

Figure 8-7. Line Transitioning Sequence

The line switch time T\_SW equals to T0 + T1 + T2 + T3. T\_SW can be configured by the LINE\_SWT (see FC1 register bit 40-37 in Table 8-8).

Table 8-4 is the relation between LINE\_SWT bits and the line switch time (GCLK numbers) with different internal GCLK frequency.

LINE\_SW **GCLK** T\_SW (us, 40 T SW (us, 60 MHZ T\_SW (us, 100 MHZ T\_SW (us, 120 MHZ | T\_SW (us, 160 MHZ MHZ GCLK) Т Numbers GCLK) GCLK) GCLK) GCLK) 0000b 45 1.125 0.7515 0.45 0.3735 0.2835 0001b 60 1.5 1.002 0.6 0.498 0.378 0010b 2.25 90 1.503 0.9 0.747 0.567 0011b 120 3 2.004 1.2 0.996 0.756 0100b 3.75 2.505 1.5 1.245 0.945 150 0101b 4.5 1.8 1.494 1.134 180 3.006 0110b 210 5.25 3.507 2.1 1.743 1.323 0111b 240 6 4.008 2.4 1.992 1.512 1000b 270 6.75 4.509 2.7 2.241 1.701

Table 8-4. Line Switch Time

300

7.5

1001b

1.89

2.49

3

5.01

### Table 8-4. Line Switch Time (continued)

| LINE_SW<br>T | GCLK<br>Numbers | T_SW (us, 40<br>MHZ GCLK) | T_SW (us, 60 MHZ<br>GCLK) | T_SW (us, 100 MHZ<br>GCLK) | T_SW (us, 120 MHZ<br>GCLK) | T_SW (us, 160 MHZ<br>GCLK) |

|--------------|-----------------|---------------------------|---------------------------|----------------------------|----------------------------|----------------------------|

| 1010b        | 330             | 8.25                      | 5.511                     | 3.3                        | 2.739                      | 2.079                      |

| 1011b        | 360             | 9                         | 6.012                     | 3.6                        | 2.988                      | 2.268                      |

| 1100b        | 390             | 9.75                      | 6.513                     | 3.9                        | 3.237                      | 2.457                      |

| 1101b        | 420             | 10.5                      | 7.014                     | 4.2                        | 3.486                      | 2.646                      |

| 1110b        | 450             | 11.25                     | 7.515                     | 4.5                        | 3.735                      | 2.835                      |

| 1111b        | 480             | 12                        | 8.016                     | 4.8                        | 3.984                      | 3.024                      |

### 8.3.5 Protections and Diagnostics

#### 8.3.5.1 Thermal Shutdown Protection

The thermal shutdown (TSD) function turns off all IC constant-current outputs when the junction temperature (T<sub>J</sub>) exceeds 170°C (typical). The function resumes normal operation when T<sub>J</sub> falls below 155°C (typical).

#### 8.3.5.2 IREF Resistor Short Protection

The IREF resistor short protection (ISP) function prevents unwanted large currents from flowing through the constant-current output when the IREF resistor is shorted accidently. The LP5891-Q1 device turns off all output channels when the IREF pin voltage is lower than 0.19 V (typical). When the IREF pin voltage goes higher than 0.325 V (typical), the LP5891-Q1 device resumes normal operation.

#### 8.3.5.3 LED Open Load Detection and Removal

### 8.3.5.3.1 LED Open Detection

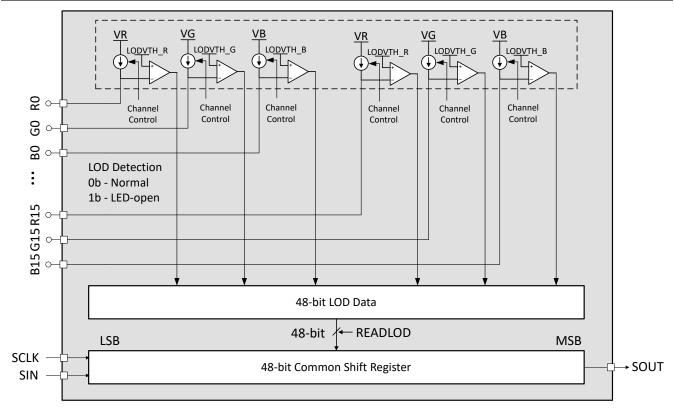

The LED Open Detection (LOD) function detects faults caused by an open circuit in any LED, or a short from OUTn to VLED with low impedance. This function was realized by comparing the OUTn voltage to the LOD detection threshold voltage level set by LODVTH\_R/LODVTH\_G/LODVTH\_B (See FC3 for more details). If the OUTn voltage is higher than the programmed voltage, the corresponding output LOD bit is set to 1 to indicate an open LED. Otherwise, the output of that LOD bit is 0. LOD data output by the detection circuit are valid only during the OUTn turning on period.

Figure 8-8 shows the equivalent circuit of LED open detection.

Figure 8-8. LED Open Detection Circuit

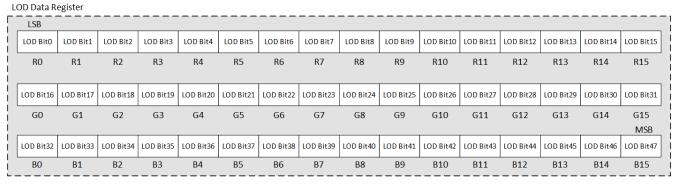

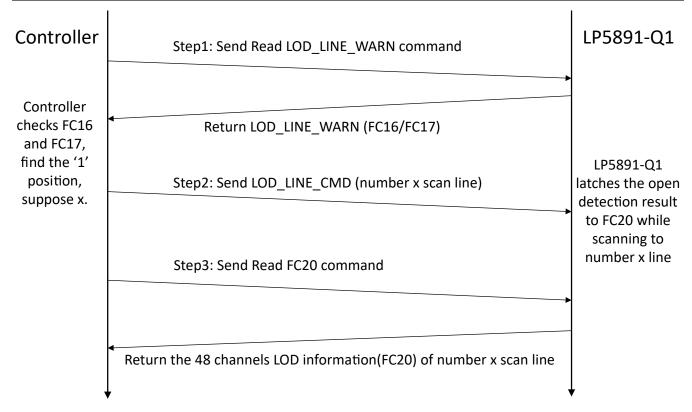

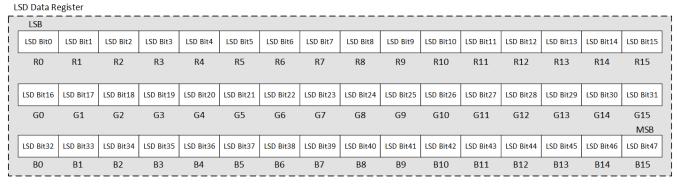

The LED open detection function records the position of the open LED, which contains the scan line number and relevant channel number. The scan line order is stored LOD\_LINE\_WARN register (see FC16, FC17 for more details), and the channel number is latched into the internal 48-bit LOD data register (see FC20 for more details) at the end of each segment. Figure 8-9 shows the bit arrangement of the LOD data register.

Figure 8-9. Bit Arrangement in LOD Data Register

#### 8.3.5.3.2 Read LED Open Information

The LOD readback function must be enabled before read LED open information. This function is enabled by LOD\_LSD\_RB (see FC3 for more details).

Figure 8-10 shows the steps to read LED open information. Wait at least one sub-period time between Step2 and Step3 command.

Figure 8-10. Steps to Read LED Open Information

### 8.3.5.3.3 LED Open Caterpillar Removal

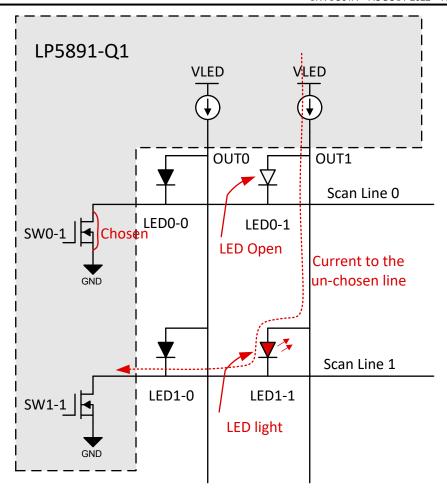

Figure 8-11 shows the caterpillar issue caused by open LED. Suppose the LED0-1 is an open LED. When line 0 is chosen and the OUT1 is turned on, the OUT1 voltage is forced to approach to VLED because of the broken path of the current source. However, the voltage of the un-chosen lines are below the Vclamp which is much lower than VLED, causing all LEDs which connect to the channel OUT1, light unwanted.

Figure 8-11. LED Open Caterpillar

The LP5891-Q1 implements circuits that can eliminate the caterpillar issue caused by open LEDs. The LED open caterpillar removal function is configured by LOD\_RM\_EN (see FC0 for more details). When LOD\_RM\_EN is set to 1b, the caterpillar removal function is enabled. The corresponding channel OUTn is turned off when scanning to line with open LED, The caterpillar issue is eliminated until device resets or LOD\_RM\_EN is set to 0b.

The internal caterpillar elimination circuit can handle a maximum of three lines that have open LEDs fault condition. If there are open LEDs located in three or fewer lines, the LP5891-Q1 is able to handle the open LEDs all in these lines. If there are open LEDs in more than three lines, the caterpillar issue is solved for the lines where the first three open LEDs were detected, but the open LEDs in the fourth and subsequent lines still cause the caterpillar issue.

## 8.3.5.4 LED Short and Weak Short Circuitry Detection and Removal

## 8.3.5.4.1 LED Short/Weak Short Detection

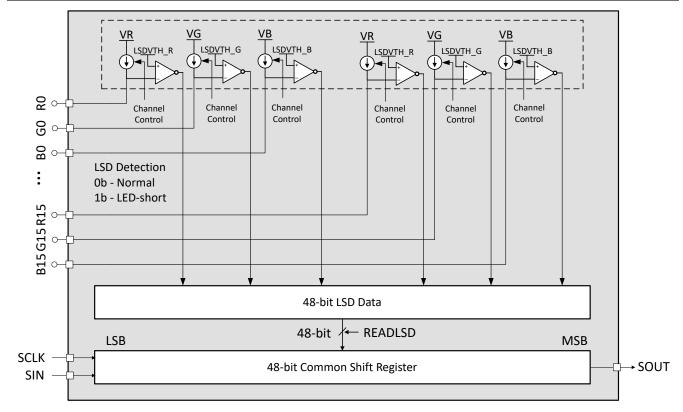

The LED short detection (LSD) function detects faults caused by a short circuit in any LED. This function was realized by comparing the OUTn voltage to the LSD threshold voltage. If the OUTn voltage is lower than the threshold voltage, the corresponding output LSD bit is set to 1 to indicate an short LED, otherwise, the output of that LSD bit is 0. LSD data output by the detection circuit are valid only during the OUTn turning on period.

LSD weak short can be detected by adjusting threshold voltage, which level is set by LSDVTH\_R/LSDVTH\_G/LSDVTH\_B (See FC3 for more details).

Figure 8-12 shows the equivalent circuit of LED short detection.

Figure 8-12. LED Short Detection Circuit

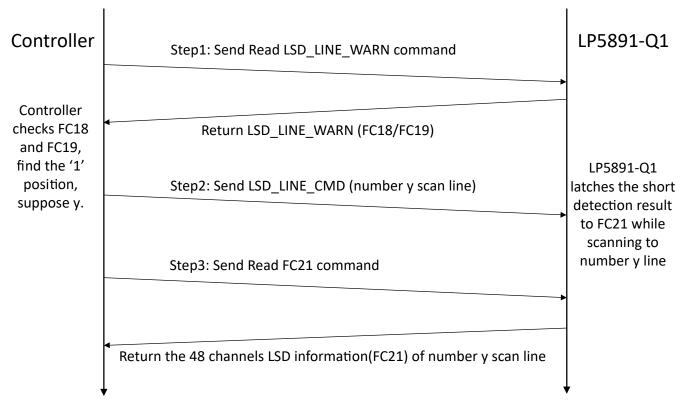

The LED short detection function records the position of the short LED, which contains the scan line order and relevant channel number. The scan line order is stored LSD\_LINE\_WARN register (see FC18, FC19 for more details), and the channel number is latched into the internal 48-bit LSD data register (see FC21 for more details) at the end of each segment. Figure 8-13 shows the bit arrangement of the LSD data register.

Figure 8-13. Bit Arrangement in the LSD Data Register

#### 8.3.5.4.2 Read LED Short Information

The LSD readback function must be enabled before reading LED Short information. This function is enabled by LOD\_LSD\_RB (see FC3 for more details).

Figure 8-14 shows the steps to read LED Short information. Wait at least one sub-period time between Step2 and Step3 command.

Submit Document Feedback

Figure 8-14. Steps to Read LED Short Information

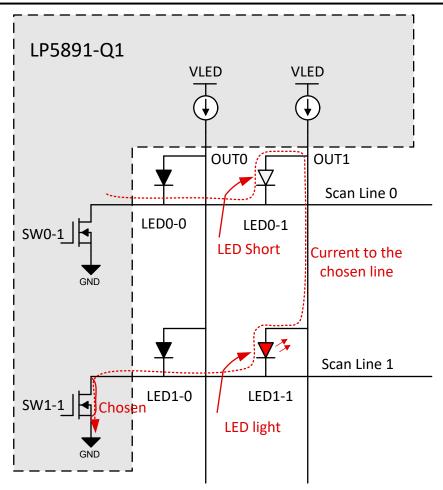

#### 8.3.5.4.3 LSD Caterpillar Removal

Figure 8-15 shows the LSD caterpillar issue caused by short LED. Suppose the LED0-1 is a short LED. When it scans to the line1 and the OUT1 is turned off, the OUT1 voltage is the same with scan line0 voltage because of the short path of the LED0-1. At this time, there is a current path from the line0 to the GND through the LED1-1 and SW1-1, which causes LED1-1 light unwanted.

Figure 8-15. LED Short Caterpillar

The LP5891-Q1 device implements internal circuits that can eliminate the caterpillar issue by short LEDs. As is shown in Figure 8-15, the LED short caterpillar is caused by the voltage of the Vclamp on the line. So it can be solved by adjusting the LSD\_RM\_EN (see FC3 for more details) to let the voltage drop of the LED1-1 be smaller than LED forward voltage.

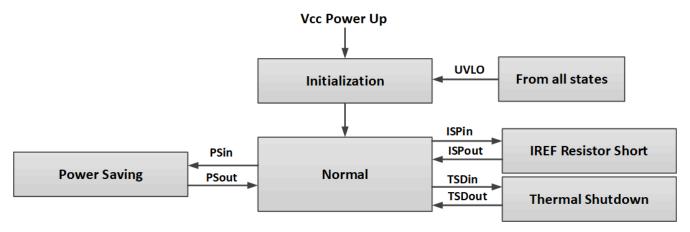

#### 8.4 Device Functional Modes

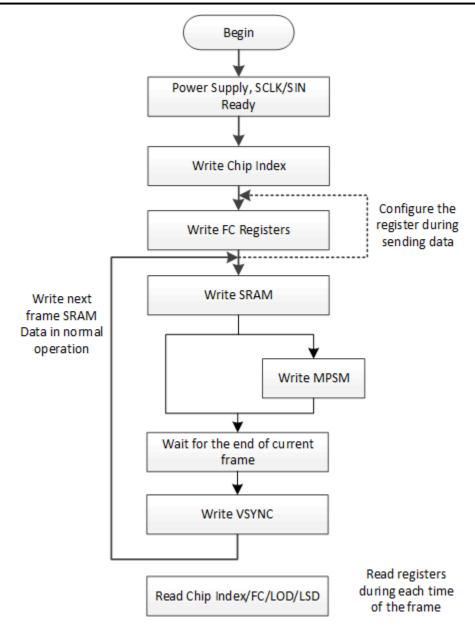

The device functional modes are shown in Figure 8-16.

Figure 8-16. Functional Modes

- **Initialization:** The device enters into Initialization when Vcc goes down to UVLO voltage. In this mode, all the registers are reset. Entry can also be from any state.

- **Normal:** The device enters the normal mode when Vcc is higher than UVLO threshold. The display process is shown as below in normal mode.

- Power saving: The device automatically enters and gets out from the power save mode when it detects the

condition PSin and PSout. In this mode, all channels turn off. PSin: after the device detects that the display

data of the next frame all equal to zero, it enters in to power save mode when the VSYNC comes. PSout:

after the device detects that there is non-zero display data of the next frame, it gets out from power save

mode immediately.

- **IREF resistor short protection:** The device automatically enters and gets out from the IREF resistor short protection mode when it detects the condition ISPin and ISPout. In this mode, all channels turn off. ISPin: the device detects that the reference voltage is smaller than 0.195 V ISPout: the device detects that the reference voltage is larger than 0.325 V.

- Thermal shutdown: The device automatically enters and gets out from the thermal shutdown mode when it

detects the condition TSDin and TSDout. In this mode, all channels turn off. TSDin: the device detects that

the junction temperature exceeds 170°C TSDout: the device detects that the junction temperature is below

155°C.

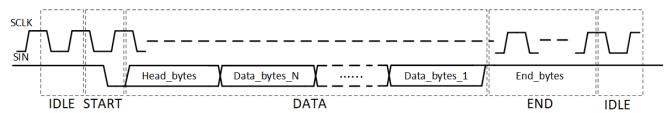

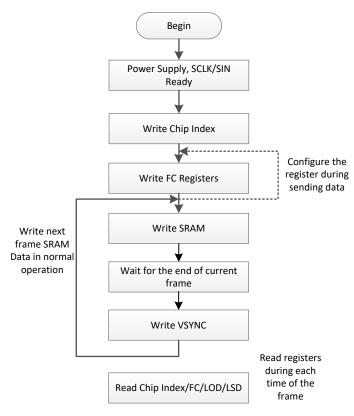

## 8.5 Continuous Clock Series Interface

The continuous clock series interface (CCSI) provides access to the programmable functions and registers, SRAM data of the device. The interface contains two input digital pins, they are the serial data input (SIN) and serial clock (SCLK). Moreover, there is an another wire called serial data output (SOUT) as the output digital signal of the device. The SIN is set to HIGH when device is in idle status and the SCLK must be existent and continuous all the time considering as the clock source of internal Frequency Multiplier, the SOUT is used to transmit the data or read the data of internal registers.

This protocol can support up to 32 devices cascaded in a data chain. The devices receive the chip index command after power up. The chip index command configured addresses of the devices from 0x00 up to 0x1F according to the sequence that receives the command. Then the controller can communicate with all the devices through the broadcast way or particular device through non-broadcast way.

The broadcast is mainly used to transmit function control commands. All the devices in a data chain receive the same data in this way. The non-broadcast is mainly used to transmit function control commands or display data, and each device receives its own data in this way. These two ways are distinguished by the command identification.

#### 8.5.1 Data Validity

The data on DIN wire must be stable at rising edges of the SCLK in transmission.

#### 8.5.2 CCSI Frame Format

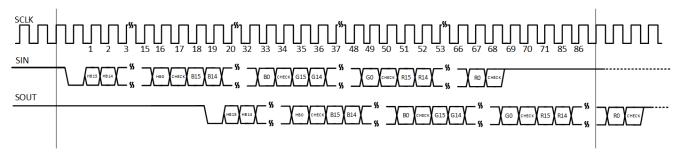

Figure 8-17 defines the format of the command and data transmission. There are four states in one frame.

- IDLE: SCLK is always existent and continuous, and DIN is always HIGH.

- START: DIN changes from HIGH to LOW after the IDLE states.

- DATA:

- Head\_bytes: It is the command identifier, contains one 16-bit data and one check bit. It can be WRITE COMMAND ID or READ COMMAND ID (see Register Maps for more details).

- Data\_bytes\_N: The N<sup>th</sup> data-bytes, contains 3 × 17-bit data, each 17-bit data contains one 16-bit data and one check bit. N is the number of devices cascaded in a data chain.

- END: The device recognizes continuous 18-bit HIGH on DIN, then returns to IDLE state.

- **CHECK BIT:** The check bit (17<sup>th</sup> bit) value is the *NOT* of 16<sup>th</sup> bit value to avoid continuous 18-bit HIGH (to distinguish with END).

Figure 8-17. CCSI Frame

The IDLE state is not necessary, which means the START state of the next frame can connect to the END state of the current frame.

#### 8.5.3 Write Command

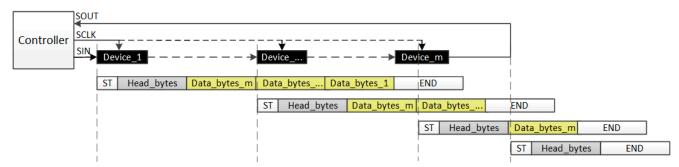

Take m devices cascaded in a data chain for example.

## 8.5.3.1 Chip Index Write Command

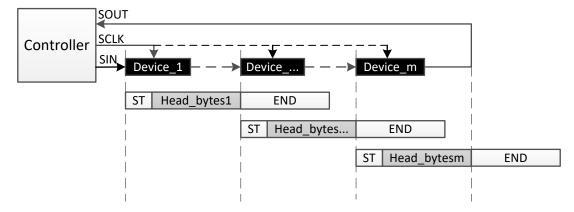

The chip index is used to set the identification of the device cascaded in a data chain. When the first device receives the chip index command Head\_bytes1, it sets the current address to 00h and meanwhile change the chip index command Head\_bytes2, then sends to the next device. When the device receives the Head\_bytes2, it sets the address to 01h and meanwhile changes the chip index command Head\_bytes3, then sends to the next device, likewise, all the cascaded devices get their unique identifications.

Figure 8-18. Chip Index Write Command

Submit Document Feedback

#### 8.5.3.2 VSYNC Write Command

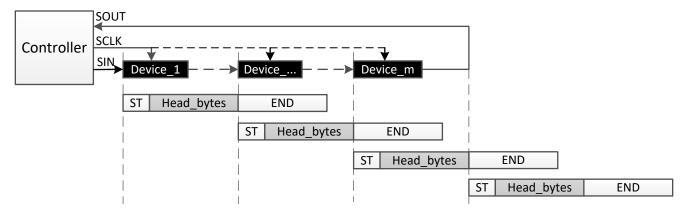

The VSYNC is used to sync the display of each frame for the devices in a cascaded chain. this command is a write-only command. The devices receive VSYNC command one time from the controller in each frame, and the VSYNC command needs to be active for all devices at the same time.

Because some devices receive the command earlier in the data chain, they need to wait until the last device receives the command, then all the devices are active at that time. To realize such function, each device needs to know its delay time from receiving VSYNC command to enabling VSYNC. The device uses some register bits to restore the device number in a data chain. This number minuses the device identification, and the result is the delay time of the device.

Because the sync function has been done by the device, the controller only must send the VSYNC command to the first device in a data chain.

Figure 8-19. VSYNC Write Command

#### 8.5.3.3 MPSM Write Command

The MPSM command is used to control the intelligent power save mode of devices in the same matrix. The device detects all zero data in a stackable module and receives MPSM command in current frame, then when VSYNC command comes, all devices in the same matrix turn off. After the device detects that there is non-zero display data of the next frame, it gets out from intelligent power save mode until MSPM command comes in current frame.

Figure 8-20. Design Procedure for MPSM Command

#### 8.5.3.4 Standby Clear and Enable Command

Standby clear command and standby enable command are used to control intelligent power save mode of devices in the same daisy chain. When the device receives standby enable command, it enters to intelligent power save mode right away and does not have to wait for other devices in a module or daisy chain. After the device receives standby enable command, it exits from intelligent power save mode immediately and does not wait for other devices in a module or daisy chain.

#### 8.5.3.5 Soft Reset Command

The Soft\_Reset Command is used to reset all the function registers to the default value, except for SRAM data. The format of this command is the same with VSYNC shown as *VSYNC Write Command*. The difference is the headbytes.

#### 8.5.3.6 Data Write Command

The device can receive the function control with broadcast and non-broadcast way, which depends on the configuration of the devices. If the cascaded devices have the same configuration, broadcast is used,. If the cascaded devices have the different configurations, non-broadcast is used. It is always the MSB transmitted first and the LSB transmitted last. For 48-bits RGB data, the Blue data must be transmitted first, then the Green, and last the Red data.

For broadcast, the devices receive the same data, when devices recognize the broadcast command, they copy the data to their internal registers. Generally, it is used for write FC0-FC13 command, LOD/LSD.

Figure 8-21. Data Write Command with Broadcast

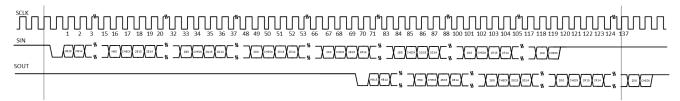

Figure 8-22 shows the time diagram of the Data Write Command with Broadcast.

Figure 8-22. Data Write Command with Broadcast (Timing Diagram)

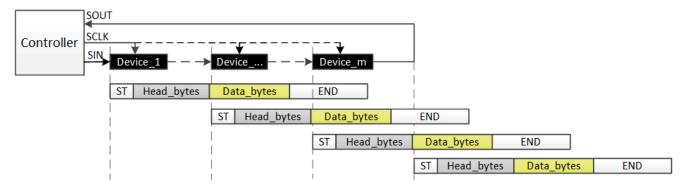

For non-broadcast, the devices receive the different data, the controller prepares the data as the figure shows. One pixel data is written to the corresponding device in each command. When the first device receives the END, it cuts off the last 51-bit (3 × 17-bit) data before the END, and the left are shifted out from SDO to the second device. Similarly, when the second device receives the END bytes from the former device, it cuts off the last 51-bit (3 × 17-bit) data before the END, and the left are shifted out to the next device. Generally, it is used for write SRAM command (WRTGS). Details for how to write a frame data into memory bank can be found in *Write a Frame Data into Memory Book*.

Figure 8-23. Data Write Command with Non-Broadcast

Figure 8-24 shows the time diagram of the Data Write Command with Non-Broadcast.

Figure 8-24. Data Write Command with Non-Broadcast (Timing Diagram)

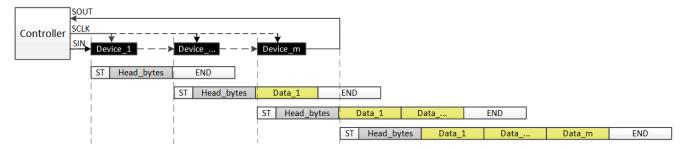

#### 8.5.4 Read Command

The controller sends the read command. When the first device receives this command, it inserts its 48-bit data before End\_bytes, and meanwhile shifts out to the second device. When the second device receives this command, it inserts its 48-bit data before End\_bytes and meanwhile shifts out to the third device. The data of all the device are shifted out from the last device SOUT with this flow. The MSB is always transmitted first and the LSB transmitted last.

Figure 8-25. Data Read Command

Submit Document Feedback

## 8.6 PWM Grayscale Control

#### 8.6.1 Grayscale Data Storage and Display

## 8.6.1.1 Memory Structure Overview

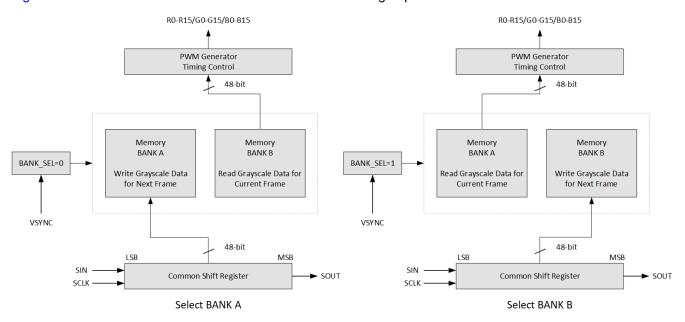

The LP5891-Q1 implements a display memory unit to achieve high refresh rate and high contrast ratio in an LED display products. The internal display memory unit is divided into two BANKs: BANK A and BANK B. During the normal operation, one BANK is selected to display the data of current frame, another is used to restore the data of next frame. The BANK switcher is controlled by the BANK SEL bit, which is an internal flag register bit.

After power on, BANK\_SEL is initialized to 0, and BANK A is selected to restore the data of next frame. Meanwhile, the data in BANK B is read out for display. When one frame has elapsed, the controller sends the vertical synchronization (VSYNC) command to start the next frame, the BANK\_SEL bit value is toggled and the selection of the two BANKs reverses. Repeat this operation until all the frame images are displayed.

With this method, the LP5891-Q1 device can display the current frame image at a very high refresh rate. See Figure 8-26 for more details about the BANK-selection exchange operation.

Figure 8-26. Bank Selection Exchange Operation

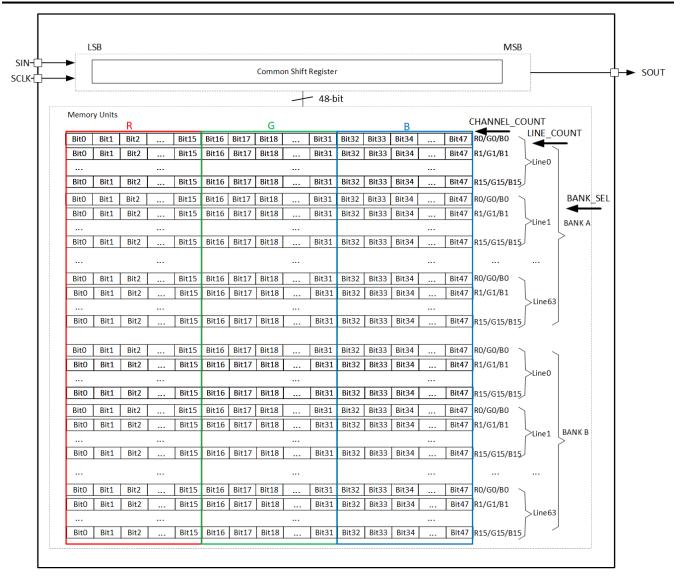

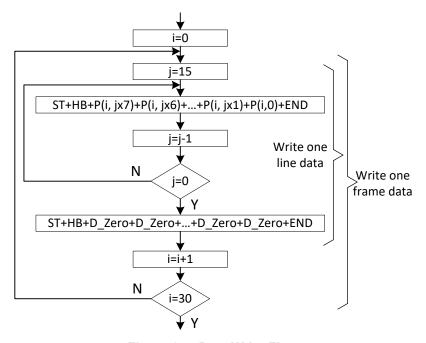

## 8.6.1.2 Details of Memory Bank

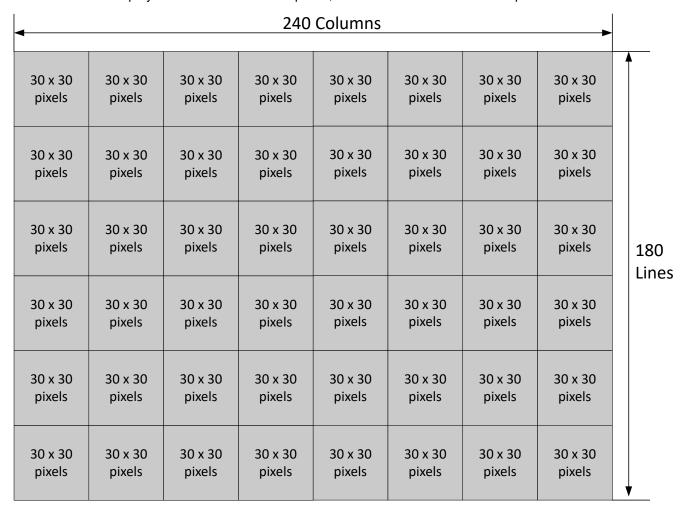

Each memory BANK contains the frame-image grayscale data of all the 64 lines. Each line comprises sixteen 48-bit-width memory units. Each memory unit contains the grayscale data of the corresponding R/G/B channels.

Depending on the number of scan lines set in SCAN\_NUM (FC0 bit 21 to bit 16), the total number of memory units that must be written in one BANK is:  $48 \times 10^{-5}$  the number of scan lines. For example, if the number of scan lines is set to 64, then 3072 ( $64 \times 48 = 3072$ ) memory units must be written during each frame period.

Figure 8-27 shows the detailed memory structure of the LP5891-Q1 device.

Figure 8-27. LP5891-Q1 Memory-unit Structure

#### 8.6.1.3 Write a Frame Data into Memory Bank

After power on, the LP5891-Q1 internal flag BANK\_SEL, and counters LINE\_COUNT, CHANNEL\_COUNT, are all initialized to 0. Thus, the memory unit of channel R0/G0/B0, locating in line 0 of BANK A, is selected to restore the data transimitted the first time after VSYNC command.

When the first WRTGS command is received, all the data in the common shift register is latched into the memory unit of channel R0/G0/B0, locating in line 0 of BANK A. Then CHANNEL\_COUNT increases by 1 and LINE\_COUNT stays the same. Thus, the memory unit of channel R1/G1/B1, locating in line 0 of BANK A, is selected to restore the data transimitted the second time after VSYNC command.

When the second WRTGS command is received, all the data in the common shift register is latched into the memory unit of channel R1/G1/B1, locating in line 0 of BANK A. Then CHANNEL\_COUNT increases by 1 and LINE\_COUNT stays the same. Thus, the memory unit of channel R2/G2/B2, locating in line 0 of BANK A, is selected to restore the data transimitted the third time after VSYNC command.

Repeat the grayscale-data-write operation until the 16<sup>th</sup> WRTGS command is received. Then CHANNEL\_COUNT is reset to 0 and LINE\_COUNT increases by 1. Thus, the memory unit of channel R0/G0/B0, locating in line 1 of BANK A, is selected to restore the data transimitted the 17<sup>th</sup> time after VSYNC command.

Repeat this operation for each line until the LINE\_COUNT exceeds the number of scan lines set in the SCAN\_NUM (See FC0 register bit21-16) and all scan lines have been updated with new GS data, which means one frame of GS data is restored into the memory BANK. Then the LINE COUNT is reset to 0.

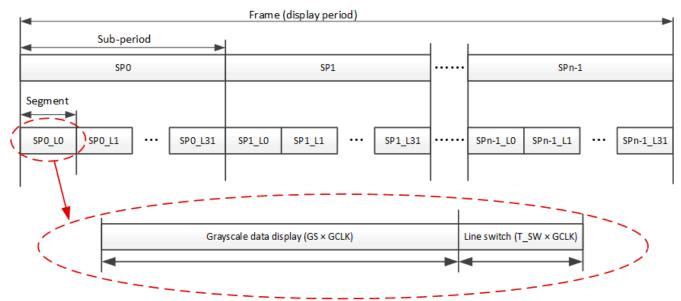

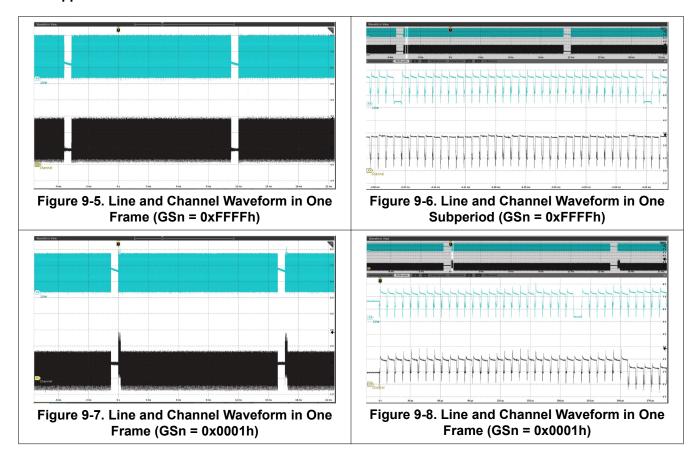

## 8.6.2 PWM Control for Display

To increase the refresh rate in time-multiplexing display system, a DS-PWM (Dynamic Spectrum-Pulse Width Modulation) algorithm is proposed in this device. One frame is divided into many segments shown below. Note that one frame is divided into n sub-periods, n is set by SUBP\_NUM (FC0 register bit24-22), and each sub-period is divided into 32 segments for 32 scan lines. Each segment contains GS GCLKs time for grayscale data display and T\_SW GCLKs time for switching lines. GS is configured by the SEG\_LENGTH (FC1 register bit9-0 in Table 8-8), and T\_SW is the line switch time, which is configured by the LINE\_SWT (see FC1 register bit 40-37 in Table 8-8).

Note that, SPO: Sub-period 0, LO: Scan line 0

Figure 8-28. DS-PWM Algorithm with 32 Scan Lines

The DS-PWM can not only increase the refresh rate meanwhile keep the same frame rate, but also decrease the brightness loss in low grayscale, which can smoothly increase the sub-period number when the grayscale data increases.

To achieve ultra-low luminance, the LED driver must have the ability to output a very short current pulse (1 GCLK time), however, because of the parasitic capacitor of the LEDs, such pulse can not turn on the LEDs. The larger GCLK frequency is, the harder to turn on LEDs.

DS-PWM algorithm have a parameter called subperiod threshold, which is used to calculate when to change subperiod number according to the giving grayscale data. Subperiod threshold defines the LED minimum turn-on time, so as to conquer the current loss caused by LED parasitic capacitor. Subperiod threshold is configured by the LG\_STEP\_R/G/B (FC1 register bit24-10 in Table 8-8).

With DS-PWM algorithm, the brightness has smoothly increased with the gradient grayscale data.

### 8.7 Register Maps

Table 8-5. Register Maps

| Table 6 61 1 togleter mape |      |                     |                    |                                                      |  |  |  |  |

|----------------------------|------|---------------------|--------------------|------------------------------------------------------|--|--|--|--|

| REGISTER NAME              | TYPE | WRITE COMMAND<br>ID | READ COMMAND<br>ID | DESCRIPTION                                          |  |  |  |  |

| FC0                        | R/ ₩ | AA00h               | AA60h              | Common configuration                                 |  |  |  |  |

| FC1                        | R/W  | AA01h               | AA61h              | Common configuration                                 |  |  |  |  |

| FC2                        | R/W  | AA02h               | AA62h              | Common configuration                                 |  |  |  |  |

| FC3                        | R/W  | AA03h               | AA63h              | Common configuration                                 |  |  |  |  |

| FC4                        | R/W  | AA04h               | AA64h              | Common configuration                                 |  |  |  |  |

| FC14                       | R/W  | AA0Eh               | AA6Eh              | Locate the line for LOD                              |  |  |  |  |

| FC15                       | R/ W | AA0Fh               | AA6Fh              | Locate the line for LSD                              |  |  |  |  |

| FC16                       | R    |                     | AAA0h              | Read the lines' warning of LOD from 64th ~ 49th line |  |  |  |  |

| FC17                       | R    |                     | AAA1h              | Read the lines' warning of LOD from 48th~1st line    |  |  |  |  |

| FC18                       | R    |                     | AAA2h              | Read the lines' warning of LSD from 64th ~ 49th line |  |  |  |  |

| FC19                       | R    |                     | AAA3h              | Read the lines' warning of LSD from 48th~1st line    |  |  |  |  |

Submit Document Feedback

## **Table 8-5. Register Maps (continued)**

| REGISTER NAME | TYPE | WRITE COMMAND ID | READ COMMAND<br>ID | DESCRIPTION                                 |

|---------------|------|------------------|--------------------|---------------------------------------------|

| FC20          | R    |                  | AAA4h              | Read the channel's warning of LOD           |

| FC21          | R    |                  | AAA5h              | Read the channel's warning of LSD           |

| Chip Index    | R/W  | AA10h            | AA70h              | Read/Write chip index                       |

| VSYNC         | W    | AAF0h            |                    | Write VSYNC command                         |

| MPSM          | W    | AA90h            |                    | Write matrix PSM command                    |

| SBY_CLR       | W    | AAB0h            |                    | Write standby clear command                 |

| SBY_EN        | W    | AAB1h            |                    | Write standby enable command                |

| Soft_Reset    | W    | AA80h            |                    | Reset the all the registers expect the SRAM |

| SRAM          | W    | AA30h            |                    | Write or read the SRAM data                 |

Table 8-6. Access Type Codes

| 14.5.0 0 017.00000 1 <b>3</b> po 00000 |           |                                        |  |  |  |  |  |  |

|----------------------------------------|-----------|----------------------------------------|--|--|--|--|--|--|

| Access Type                            | Code      | Description                            |  |  |  |  |  |  |

| Read Type                              | Read Type |                                        |  |  |  |  |  |  |

| R                                      | R         | Read                                   |  |  |  |  |  |  |