# **HFC0310**

# Programmable Fixed-Frequency Flyback Controller

#### DESCRIPTION

The HFC0310 is a flyback controller with programmable fixed-frequency operation.

The controller uses peak current mode to provide excellent transient response and ease loop compensation. When the output power falls below a given level, the controller enters burst mode to lower the stand-by power consumption.

An external capacitor connected between the FSET pin and GND programs the HFC0310 switching frequency. Otherwise, the HFC0310 uses a frequency shaping function that greatly reduces the noise level, and reduces the cost of the EMI filter.

The HFC0310 provides various protections, such as thermal shutdown,  $V_{\text{CC}}$  under-voltage lockout, over-load protection, over-voltage protection, and short-circuit protection.

The HFC0310 is available in a SOIC8 package.

#### **FEATURES**

- Programmable switching frequency up to 600kHz

- Frequency shaping

- Current-mode operation

- Very low start-up current

- Very low standby power consumption via active-burst mode

- Internal leading-edge blanking

- Built-in soft-start function

- Internal slope compensation

- External protection with recovery hysteresis on PRO pin

- Over-temperature protection

- V<sub>CC</sub> under-voltage lockout with hysteresis

- Over-voltage protection on VCC

- Time-based over-load protection

- Short-circuit protection

#### **APPLICATIONS**

- Power Meters

- Switching Mode Power Supplies

- AC/DC Adapters, Switching Chargers

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance.

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

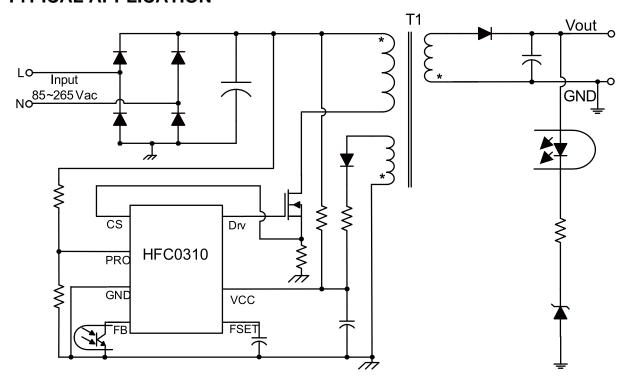

# **TYPICAL APPLICATION**

## **ORDERING INFORMATION**

| Part Number* | Package | Top Marking |

|--------------|---------|-------------|

| HFC0310GS    | SOIC8   | See below   |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. HFC0310GS–Z);

## **TOP MARKING**

HFC0310 LLLLLLLL MPSYWW

MPS: MPS prefix Y: year code WW: week code HFC0310: part number LLLLLLL: lot number

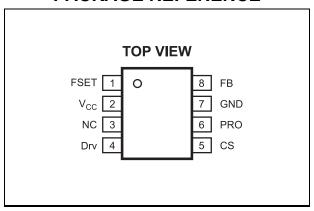

## **PACKAGE REFERENCE**

© 2018 MPS. All Rights Reserved.

| ABSOLUTE MAXIM           | UM RATINGS (1)                               |

|--------------------------|----------------------------------------------|

| Vcc, Drv to GND          |                                              |

| All Other Pins to GND    |                                              |

| Continuous Power Dissipa | tion (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

| SOIC8                    | 1.3W                                         |

| Junction Temperature     | 150°C                                        |

| Lead Temperature         | 260°C                                        |

| Storage Temperature      | 60°C to +150°C                               |

| ESD Capability Human Bo  | dy Model 2.0kV                               |

| ESD Capability Machine M | lodel 200V                                   |

| Recommended Operat       | ion Conditions <sup>(3)</sup>                |

| V <sub>CC</sub> to GND   |                                              |

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |   |

|------------------------|-------------------------|-------------------------|---|

| SOIC8                  | 96                      | 45 °C/W                 | • |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

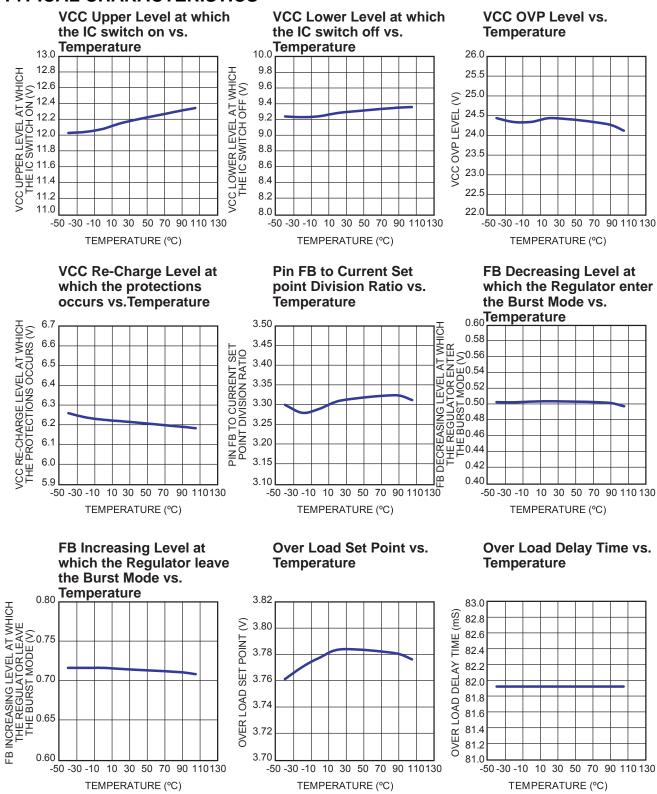

VCC = 12V,  $T_J = -40$ °C to 105°C, min and max values are guaranteed by characterization, typical values are tested under 25°C, unless otherwise noted.

| Parameter                                               | Symbol               | Conditions                                                      | Min  | Тур  | Max  | Unit  |

|---------------------------------------------------------|----------------------|-----------------------------------------------------------------|------|------|------|-------|

| Driving Signal (Pin Drv)                                |                      |                                                                 |      |      |      |       |

| Sourcing Resistor                                       | Rн                   |                                                                 | 17   | 25   | 34   | Ω     |

| Sinking Resistor                                        | R∟                   |                                                                 | 9    | 13   | 17   | Ω     |

| Supply Voltage Management (Pin Vcc)                     |                      |                                                                 |      |      |      |       |

| V <sub>CC</sub> Upper Turn-On/Off Level                 | V <sub>CCH</sub>     |                                                                 | 10.8 | 12   | 13.2 | V     |

| V <sub>CC</sub> , Lower Turn-On/Off Level               | V <sub>CCL</sub>     |                                                                 | 8.5  | 9.5  | 10.5 | V     |

| Start-Up Current                                        | I <sub>ST</sub>      | V <sub>CC</sub> =V <sub>CCH</sub> -<br>0.5V, Before<br>start up |      | 12   | 20   | μΑ    |

| V <sub>CC</sub> OVP Level                               | V <sub>OVP</sub>     |                                                                 | 21   | 23   | 25   | V     |

| Vcc Protection-Enabled Recharge Level                   | Vccr                 |                                                                 | 5.8  | 6.4  | 7.0  | V     |

| Internal IC Consumption, Protection Phase               | I <sub>Pro</sub>     | V <sub>CC</sub> =6.0V                                           |      | 8    | 12   | μA    |

| Feedback Management (Pin FB)                            |                      |                                                                 |      |      |      |       |

| Internal Pull-Up Resistor                               | R <sub>FB</sub>      |                                                                 | 12.5 | 14.5 | 17.0 | kΩ    |

| Internal Pull-Up Voltage                                | Vup                  |                                                                 | 4.25 | 4.55 | 4.85 | V     |

| FB to Current-Set–Point Division Ratio                  | I <sub>DIV</sub>     |                                                                 | 3    | 3.5  | 4    |       |

| Internal Soft-Start Time                                | tss                  |                                                                 |      | 3    |      | ms    |

| Falling FB Level Where the Regulator Enters Burst Mode  | V <sub>BURL</sub>    |                                                                 | 0.43 | 0.5  | 0.57 | V     |

| Rising FB Level where the Regulator Exits Burst Mode    | V <sub>BURH</sub>    |                                                                 | 0.66 | 0.73 | 0.80 | V     |

| Over-Load Set Point                                     | $V_{OLP}$            |                                                                 | 3.5  | 3.75 | 4    | V     |

| Over-Load Delay Time                                    | t <sub>Delay</sub>   | Fs=100kHz                                                       |      | 82   |      | ms    |

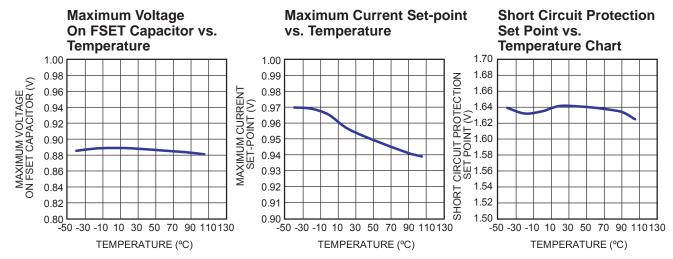

| Timing Capacitor(FSET)                                  |                      |                                                                 |      | •    | ·    | •     |

| Maximum Voltage on the FSET Capacitor                   | V <sub>FSETmax</sub> |                                                                 | 0.82 | 0.87 | 0.92 | V     |

| Source Current                                          | I <sub>FSET</sub>    |                                                                 | 40   | 50   | 60   | μA    |

| FSET Capacitor Discharge Time (Active at drive turn on) | t <sub>DISCH</sub>   |                                                                 | -    | 500  |      | ns    |

| Frequency Spectrum Shaping range, in percentage of Fs   | R <sub>Shaping</sub> |                                                                 |      | ±3.5 |      | %     |

| Current Sampling Management (CS)                        | I                    | l                                                               |      |      |      | ı     |

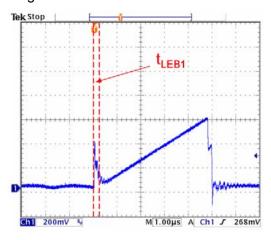

| Leading-Edge Blanking for Current<br>Sensor             | t <sub>LEB1</sub>    |                                                                 | 180  | 280  | 400  | ns    |

| Leading-Edge Blanking for SCP                           | t <sub>LEB2</sub>    |                                                                 | 150  | 250  | 370  | ns    |

| Maximum Current Set-Point                               | Vcs                  |                                                                 | 0.90 | 0.97 | 1.03 | V     |

| Short-Circuit–Protection Set Point                      | V <sub>SCP</sub>     |                                                                 | 1.60 | 1.72 | 1.84 | V     |

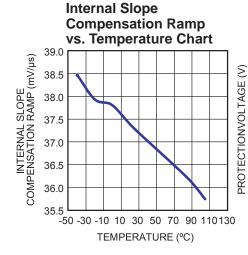

| Internal-Slope-Compensation Ramp                        | SRamp                | fs=100kHz                                                       | 27   | 42   | 57   | mV/μs |

| Protection Management (PRO)                             |                      |                                                                 | -    | . –  |      |       |

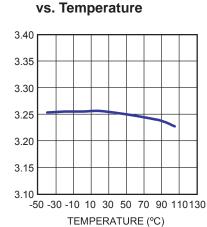

| Protection Voltage                                      | V <sub>PRO</sub>     |                                                                 | 3.1  | 3.3  | 3.5  | V     |

| Protection Hysteresis                                   | V <sub>HY</sub>      |                                                                 |      | 0.2  |      | V     |

| Thermal Shutdown                                        |                      | 1                                                               |      | 1    | ı    | 1     |

| Thermal shutdown threshold (5)                          |                      |                                                                 |      | 150  |      | °C    |

| HIGHHAL SHUUUWIH HIGSHUU 🐡                              |                      |                                                                 |      |      |      | . ~   |

#### Notes:

<sup>5)</sup> This parameter is guaranteed by design.

# **PIN FUNCTIONS**

| Package<br>Pin # | Name            | Description                                                                                                                                                                                                                                       |

|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | FSET            | Switching Frequency Set. Connect a capacitor to GND to set the switching frequency up to 600kHz.                                                                                                                                                  |

| 2                | V <sub>CC</sub> | IC Power Supply Connect to a $47\mu F$ bulky capacitor and a $0.1\mu F$ ceramic capacitor for most applications.                                                                                                                                  |

| 3                | NC              | Not Connected.                                                                                                                                                                                                                                    |

| 4                | Drv             | Drive Signal Output.                                                                                                                                                                                                                              |

| 5                | CS              | Primary Current Sense.                                                                                                                                                                                                                            |

| 6                | PRO             | Pull up PRO to shut down the IC with hysteresis.                                                                                                                                                                                                  |

| 7                | GND             | Ground.                                                                                                                                                                                                                                           |

| 8                | FB              | Feedback. The output voltage from the external compensation circuit is fed into this pin. This pin and the current sense signal from Source determines the PWM duty cycle. Burst mode operation and Over Load Protection are also detected on it. |

#### TYPICAL CHARACTERISTICS

## TYPICAL CHARACTERISTICS (continued)

**Protection Voltage**

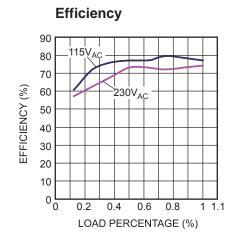

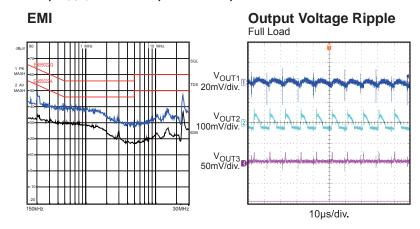

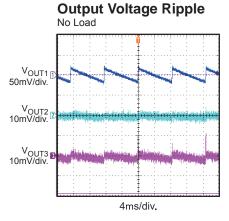

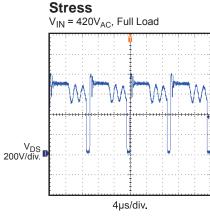

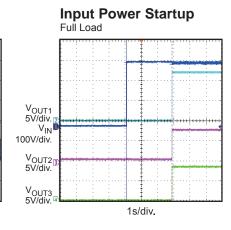

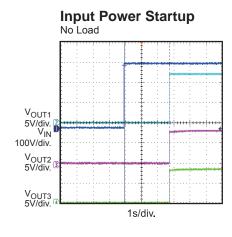

## TYPICAL PERFORMANCE CHARACTERISTICS

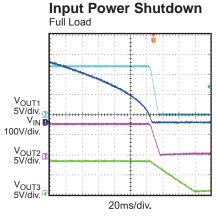

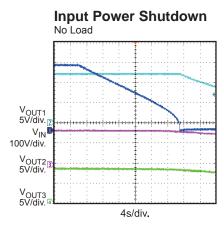

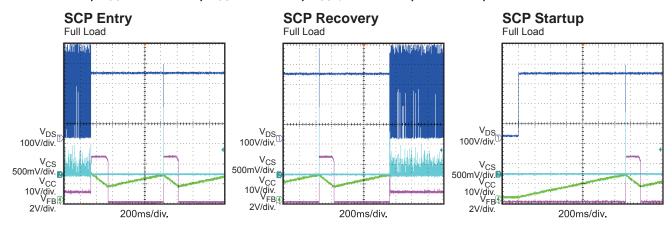

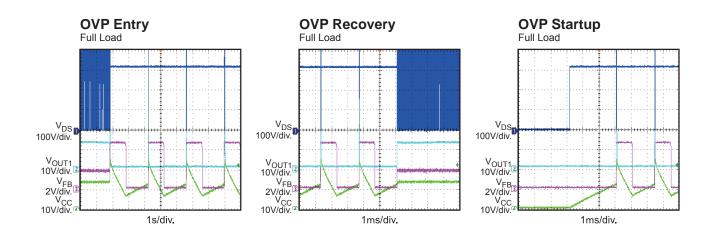

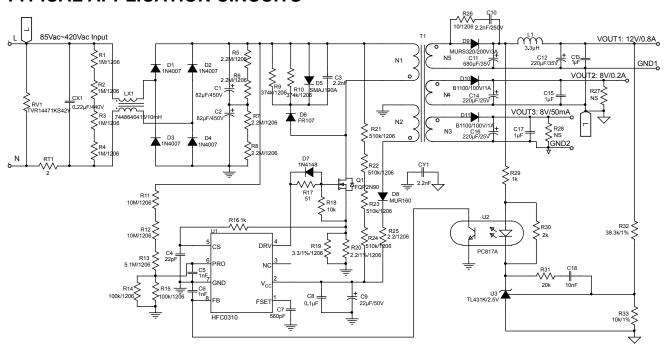

$V_{\text{IN}} = 230 \text{VAC}, \ V_{\text{OUT1}} = 12 \text{V}/0.8 \text{A}, \ V_{\text{OUT2}} = 8 \text{V}/0.2 \text{A}, \ V_{\text{OUT3}} = 8 \text{V}/0.05 \text{A}, \ T_{\text{A}} = +25 ^{\circ}\text{C}, \ unless \ otherwise \ noted.$

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{\text{IN}} = 230 \text{VAC}, \ V_{\text{OUT1}} = 12 \text{V}/0.8 \text{A}, \ V_{\text{OUT2}} = 8 \text{V}/0.2 \text{A}, \ V_{\text{OUT3}} = 8 \text{V}/0.05 \text{A}, \ T_{\text{A}} = +25 ^{\circ}\text{C}, \ unless \ otherwise \ noted.$

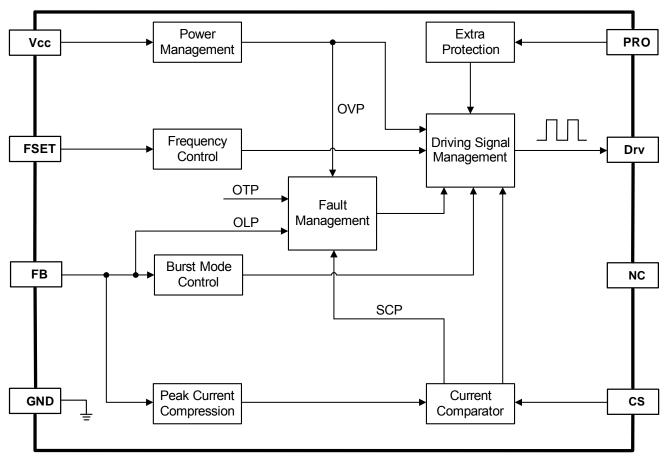

## **BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

#### **OPERATION**

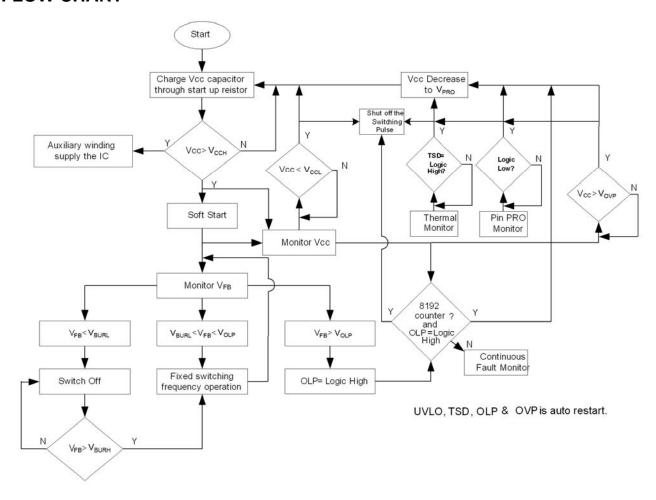

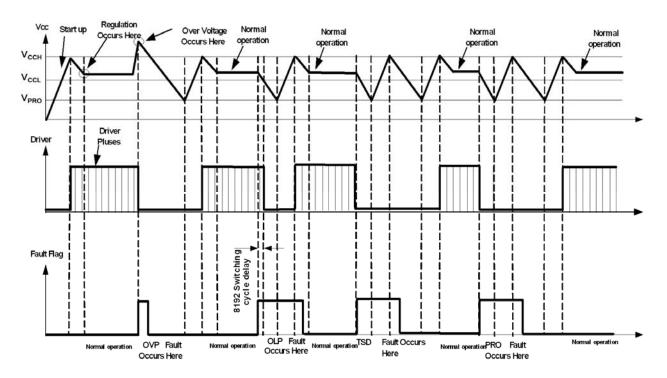

The HFC0310 incorporates all the necessary features to build a reliable switch-mode power supply. Its high level of integration requires very few external components. It has burst-mode operation to minimize the stand-by power consumption at light load. Protection features—such as auto-recovery for over-load protection (OLP), protection (SCP), over-voltage short-circuit protection (OVP), or thermal shutdown (TSD) for over-temperature protection (OTP)—contribute to a safer converter design without increasing circuit complexity.

#### **PWM Operation**

The HFC0310 is a fully integrated converter with adjustable-frequency peak-current-mode control PWM switching regulators. The output voltage is measured at FB through a resistive voltage divider, amplifier, and optocoupler. The voltage at the FB pin is compared to the internally measured switch current to control the output voltage. The integrated MOSFET turns on at the beginning of each clock cycle. The current in the inductor increases until it reaches the value set by the FB voltage, and then the integrated MOSFET turns off.

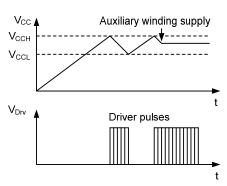

#### Start-Up and Vcc UVLO

During start-up, the IC consumption is  $I_{\text{ST}}$ , and the current supplied through the start-up resistor charges the  $V_{\text{CC}}$  capacitor.

The IC starts switching and the operation current increases when  $V_{\text{CC}}$  reaches  $V_{\text{CCH}}$ . At this point, the transformer's auxiliary winding powers the IC. When  $V_{\text{CC}}$  falls below  $V_{\text{CCL}}$ , the regulator stops switching and the current through the start up resistor charges the  $V_{\text{CC}}$  capacitor again.

Figure 2: Vcc UVLO

The lower threshold of VCC under-voltage lock-out (UVLO) decreases from  $V_{\text{CCL}}$  to  $V_{\text{CCR}}$  when fault conditions occur, such as OLP, OVP, and OTP.

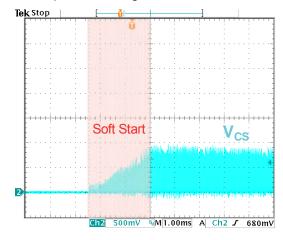

#### **Soft-Start**

To reduce stress on the primary MOSFET and the secondary diode during start-up and to smoothly establish the output voltage, the HFC0310 has an internal soft-start circuit that gradually increases the primary current sense threshold, which determines the MOSFET peak current during start-up. The pulse-width of the power switching device progressively increases to establish optimal operating conditions until the feedback control loop takes charge.

Figure 3: Soft Start

#### **Switching Frequency**

The capacitor between the FSET pin and GND sets the switching frequency of the HFC0310. Estimate the oscillator frequency as per the equation below:

$$f_{S} = \frac{1}{t_{DISCH} + C \times \frac{V_{FSETmax}}{I_{ESET}}} Hz$$

#### **Over Voltage Protection**

Monitoring the  $V_{\text{CC}}$  pin with about 20µs delay time allows the HFC0310 to enter OVP during an overvoltage condition; when  $V_{\text{CC}}$  goes above  $V_{\text{OVP}}$ . HFC0310 will resume operation after the fault disappears.

#### **Over-Current Protection**

The HFC0310 continuously monitors the FB pin. When FB pulls up to  $V_{\text{OLP}}$ , if after a 8192 switching cycle delay the fault signal is still present, the HFC0310 shuts down as soon as the power supply undergoes an overload. When the fault disappears, the power supply resumes operation.

#### **Short-Circuit Protection**

By monitoring the CS pin, the HFC0310 shuts down when the voltage rises higher than V<sub>SCP</sub>, to indicate a short circuit. The HFC0310 enters a safe low-power mode that prevents any lethal thermal or stress damage. As soon as the fault disappears, the power supply resumes operation.

#### **Thermal Shutdown**

When the temperature of the IC exceeds thermal shutdown threshold, the OTP is activated and it will resume operation when junction temperature drops to thermal shutdown recovery point.

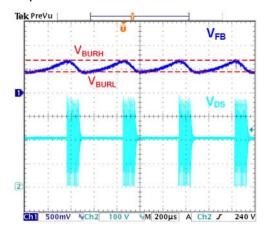

#### **Burst Operation**

To minimize stand-by power consumption, the HFC0310 implements burst mode at no load or light load. As the load decreases, the FB voltage decreases. The IC stops switching when the FB voltage drops below the lower threshold,  $V_{\text{BRUL}}$ . Then the output voltage drops at a rate dependent on the load. This causes the FB voltage to rise again due to the negative feedback control loop. Once the FB voltage exceeds the upper threshold,  $V_{\text{BRUH}}$ , the switching pulse resumes. The FB voltage then decreases and the whole process repeats. Burst-mode operation alternately enables

and disables the switching pulse of the MOSFET. Hence switching loss at no load or light load conditions is greatly reduced.

Figure 4 shows the signals generated by burst-mode operation.

Figure 4: Burst-Mode Operation

#### **PRO Pin**

The PRO pin provides extra protection against abnormal conditions. Use the PRO pin for input OVP and/or other protections. If the PRO pin voltage exceeds  $V_{PRO}$ , the IC shuts down. As soon as the fault disappears, the power supply resumes operation.

## Leading-Edge Blanking (LEB)

In normal operation, a resistor is placed between the MOSFET Source and Ground to senses the primary peak current. The FB voltage sets the turn-off threshold of the MOSFET,  $V_{\text{SENSE}} = V_{\text{FB}} / I_{\text{DIV}}$ . HFC0310 turns off the MOSFET when the sensing resistor voltage rises to  $V_{\text{SENSE}}$ .

During start-up and over-load condition, the maximum primary peak current threshold is internally limited to Vcs to avoid excessive output power and lower the switch voltage stress.

In order to avoid turning off the MOSFET by mistriggered spikes shortly after the switch turns on, the IC implements a leading-edge blanking period. During blanking time, any trigger signal on the source pin is blocked. Figure 5 shows the primary-current—sense waveform and the leading-edge blanking.

Figure 5: Leading-Edge Blanking

## Design Example

The following is a design example using the application guidelines for the given specifications:

| $V_{IN}$          | 85V to 420V |

|-------------------|-------------|

| V <sub>OUT1</sub> | 12V         |

| V <sub>OUT2</sub> | 8V          |

| V <sub>OUT3</sub> | 8V          |

| f <sub>SW</sub>   | 100kHz      |

The detailed application schematic is shown in Figure 6. The typical performance and circuit waveforms have been shown in the Typical Performance Characteristics section. For more possible applications of this device, please refer to the related Evaluation Board datasheets.

## **TYPICAL APPLICATION CIRCUITS**

Figure 6: Typical Application Schematic

## **FLOW CHART**

## SIGNAL EVOLUTION IN THE PRESENCE OF FAULTS

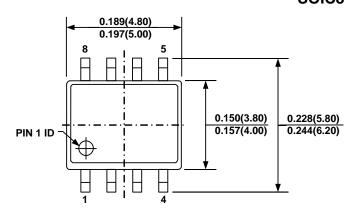

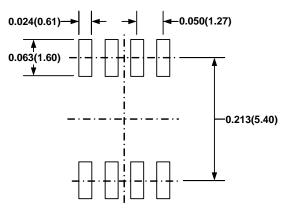

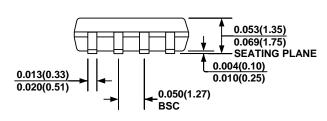

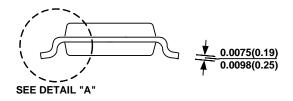

#### **PACKAGE INFORMATION**

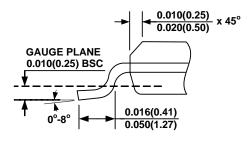

#### SOIC8

TOP VIEW RECOMMENDED LAND PATTERN

**FRONT VIEW**

**SIDE VIEW**

**DETAIL "A"**

#### **NOTE:**

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.