## Am29116

## A High-Performance 16-Bit Bipolar Microprocessor

### **PRELIMINARY**

## DISTINCTIVE CHARACTERISTICS

- Optimized for High-Performance Controllers Excellent solution for applications requiring speed and bit-manipulation power.

Fast

Supports 100ns microcycle time/10MHz data rate for all instructions.

16-Bit Barrel Shifter

Contains a 16-bit Barrel Shifter which can shift or rotate a word up to 15 positions in a single instruction cycle.

Immediate Instruction Capability May be used for storing constants in microcode or for configuring a second data port.

- Powerful Field Insertion/Extraction and Bit Manipulation Instructions

- Rotate and Merge, Rotate and Compare and bit manipulation instructions provided for complex bit control.

- 32-Working Registers

Single port RAM may be configured to accept different source and destination addresses within single cycle.

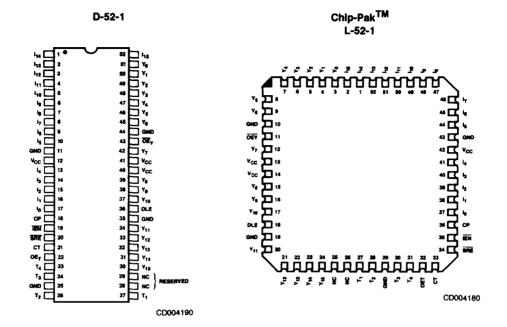

52-Pin Hermetic DIP

## **GENERAL DESCRIPTION**

The Am29116 is a microprogrammable 16-bit bipolar microprocessor whose architecture and instruction set is optimized for high performance peripheral controllers, like graphics controllers, disk controllers, communications controllers, front-end concentrators and modems. The device also performs well in microprogrammed processor applications, especially when combined with the Am29517 16 x 16 multiplier (65ns worst-case 16 x 16 multiply). In addition to its complete arithmetic and logic instruction set, the Am29116 instruction set contains functions particularly useful in controller applications; bit set, bit reset, bit test, rotate and merge, rotate and compare, and cyclic-redundancy-check (CRC) generation.

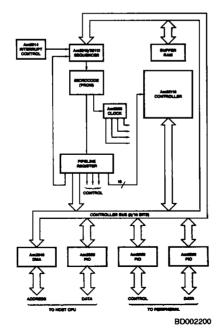

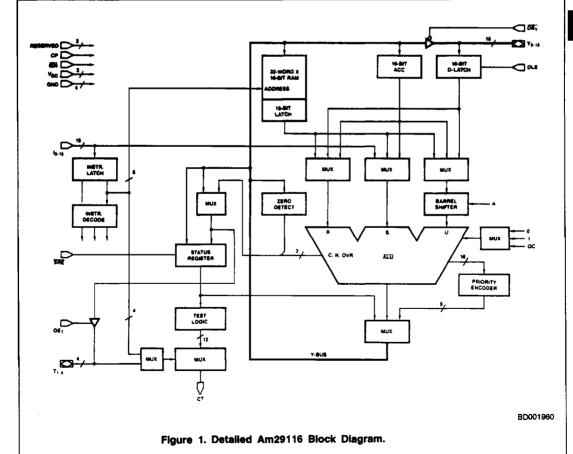

### **BLOCK DIAGRAM**

Am29116 BASED HIGH PERFORMANCE PERIPHERAL CONTROLLER

02112C

## **RELATED PRODUCTS**

## OTHER LITERATURE

- An Intelligent Fast Disk Controller using the

- Am29116 Application Note.

A Microprogrammed CPU Using the Am29116 Application Note.

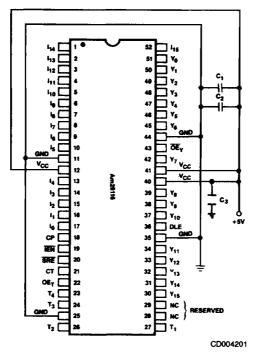

## CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation

## METALLIZATION AND PAD LAYOUT

## V<sub>CC</sub> AND GROUND PIN CONNECTIONS

Notes: 1. All V<sub>CC</sub> and all GND pins must be connected as shown. Offsets between any two V<sub>CC</sub> pins or between any two GND pins should be avoided.

2.  $C_1 = 1.0 \mu F$ ,  $C_2 = C_3 = 0.01 \mu F$ .

The  $C_1$ ,  $C_2$ , and  $C_3$  capacitors should be used to shunt low- and high-frequency noise from  $V_{CC}$ . Do not replace with one capacitor.

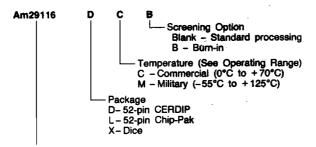

## ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

| Device type        |        |         |                |

|--------------------|--------|---------|----------------|

| A High-Performance | 16-Bit | Bipolar | Microprocessor |

| Valid Cor | nbinations                        |

|-----------|-----------------------------------|

| Am29116   | DC, DCB, DMB<br>LC, LMB<br>XC, XM |

## **Valid Combinations**

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

|                   |                                 |     | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|---------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.           | Name                            | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   | Y <sub>0</sub> -Y <sub>15</sub> | 1/0 | Data input/Output Lines. When OEy is HIGH, Y <sub>0</sub> -Y <sub>15</sub> are used as external data inputs which allow data to be directly loaded into the 16-bit data latch. Having OEy LOW allows the ALU data to be output on Y <sub>0</sub> -Y <sub>15</sub> .                                                                                                                                                                                                                                                                                                                   |

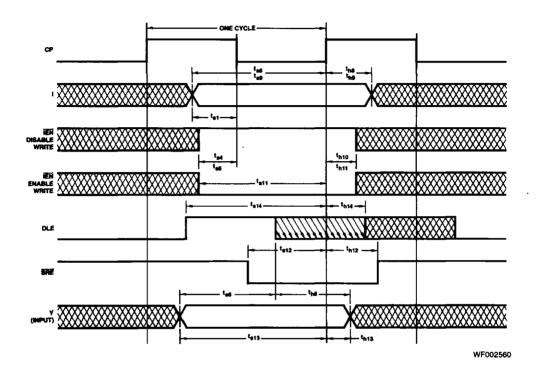

| 36                | DLE                             | - 1 | Data Latch Enable. When DLE is HIGH, the 16-bit data latch is transparent and is latched when DLE is LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 43                | ŌĒY                             | 1   | Output Enable. When OEy is HIGH, the 16-bit Y outputs are disabled (high-impedance); when OEy is LOW, the 16-bit Y outputs are enabled (HIGH or LOW).                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | lo-l <sub>15</sub>              | 1   | Sixteen Instruction Inputs. Used to select the operations to be performed in the Am29116. Also used as data inputs while performing immediate instructions.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 19                | IEN                             | I   | Instruction Enable. With TEN LOW, data can be written into the RAM when the clock is LOW. The Accumulator can accept data during the LOW-HIGH transition of the clock. Having TEN LOW, the Status Register can be updated when SRE is LOW. With TEN HIGH, the conditional test output, CT, is disabled as a function of the instruction inputs. TEN should be LOW for the first half of the first cycle of an immediate instruction.                                                                                                                                                  |

| 20                | SRE                             |     | Status Register Enable. When SRE and IEN are both LOW, the Status Register is updated at the end of all instructions with the exception of NO-OP, Save Status, and Test Status. Having either SRE or IEN HIGH will inhibit the Status Register from changing.                                                                                                                                                                                                                                                                                                                         |

| 18                | СР                              | ı   | Clock Pulse. The clock input to the Am29116. The RAM latch is transparent when the clock is HIGH. When the clock goes LOW, the RAM output is latched. Data is written into the RAM during the low period of the clock provided IEN is LOW and if the instruction being executed designates the RAM as the destination of operation. The Accumulator and Status Register will accept data on the LOW-HIGH transition of the clock if IEN is also LOW. The instruction latch becomes transparent when it exits an immediate instruction mode during a LOW-HIGH transition of the clock. |

| 27, 26,<br>24, 23 | T <sub>1</sub> -T <sub>4</sub>  | 1/0 | Input/Output Pin. Under the control of $OE_T$ , the four lower status bits Z, C, N, OVR become outputs on $T_1$ - $T_4$ , respectively when $OE_T$ goes HIGH. When $OE_T$ is LOW, $T_1$ - $T_4$ are used as inputs to generate the CT output.                                                                                                                                                                                                                                                                                                                                         |

| 22                | OET                             | ł   | Output Enable. When OE <sub>T</sub> is LOW, the 4-bit T outputs are disabled (high-impedance); when OE <sub>T</sub> is HiGH, the 4-bit T outputs are enabled (HiGH or LOW).                                                                                                                                                                                                                                                                                                                                                                                                           |

| 21                | СТ                              | 0   | Conditional Test. The condition code multiplexer selects one of the twelve condition code signals and places them on the CT output. A HIGH on the CT output indicates a passed condition and a LOW indicates a failed condition.                                                                                                                                                                                                                                                                                                                                                      |

02112C

### ARCHITECTURE OF THE Am29116

The Am29116 is a high-performance, microprogrammable 16-bit bipolar microprocessor.

As shown in the Block Diagram, Figure 1, the device consists of the following elements interconnected with 16-bit data paths.

- 32-Word by 16-Bit RAM

- Accumulator

- Data Latch

- Barrel Shifter

- ALU

- Priority Encoder

- Status Register

- Condition-Code Generator/Multiplexer

- Three-State Output Buffers

- Instruction Latch and Decoder

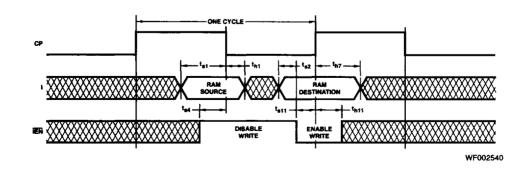

### 32-Word by 16-Bit RAM

The 32-Word by 16-Bit RAM is a single-port RAM with a 16-bit latch at its output. The latches are transparent when the clock input (CP) is HIGH and latched when the clock input is LOW. Data is written into the RAM while the clock is LOW if the IEN input is also LOW and if the instruction being executed defines the RAM as the destination of the operation. For byte instructions, only the lower eight RAM bits are written into; for word instructions, all 16 bits are written into. With the use of an external multiplexer on five of the instruction inputs, it is possible to select separate read and write addresses for the same instruction. This two-address operation is not allowed for immediate instructions.

#### Accumulator

The 16-bit Accumulator is an edge-triggered register. The Accumulator accepts data on the LOW-to-HIGH transition of the clock input if the IEN input is LOW and if the instruction being executed defines the Accumulator as the destination of the operation. For byte instructions, only the lower eight bits of the Accumulator are written into; for word instructions, all 16 bits are written into.

### **Data Latch**

The 16-bit Data Latch holds the data input to the Am29116 on the bi-directional Y bus. The latch is transparent when the DLE input is HIGH and latched when the DLE input is LOW.

## Barrel Shifter

A 16-bit Barrel Shifter is used as one of the ALU inputs. This permits rotating data from either the RAM, the Accumulator or the Data Latch up to 15 positions. In the word mode, the Barrel Shifter rotates a 16-bit word; in the byte mode, it rotates only the lower eight bits.

### **Arithmetic Logic Unit**

The Am29116 contains a 16-bit ALU with full carry lookahead across all 16 bits in the arithmetic mode. The ALU is capable of operating on either one, two or three operands, depending upon the instruction being executed. It has the ability to execute all conventional one and two operand operations, such as pass, complement, two's complement, add, subtract, AND, NAND, OR, NOR, EXOR, and EX-NOR. In addition, the ALU can also execute three-operand instructions such as rotate and merge and rotate and compare with mask. All ALU operations can be performed on either a word or byte basis, byte operations being performed on the lower eight bits only.

The ALU produces three status outputs, C (carry), N (negative) and OVR (overflow). The appropriate flags are generated at

the byte or word level, depending upon whether the device is executing in the byte or word mode. The Z (zero) flag, although not generated by the ALU, detects zero at both the byte and word level.

The carry input to the ALU is generated by the Carry Multiplexer which can select an input of zero, one, or the stored carry bit from the Status Register, QC. Using QC as the carry input allows execution of multiprecision addition and subtractions.

### **Priority Encoder**

The Priority Encoder produces a binary-weighted code to indicate the locations of the highest order ONE at its input. The input to the Priority Encoder is generated by the ALU which performs an AND operation on the operand to be prioritized and a mask. The mask determines which bit locations to eliminate from prioritization. In the word mode, if no bit is HIGH, the output is a binary zero. If bit 15 is HIGH, the output is a binary zero. If bit 15 is HIGH, the cutput is a binary two, etc. Finally, if only bit 0 is HIGH, a binary 16 is produced.

In the byte mode, bits 8 thru 15 do not participate. If none of bits 7 thru 0 are HIGH, the output is a binary zero. If bit 7 is HIGH a binary one is produced. Bit 6 produces a binary two, etc. Finally, if only bit 0 is HIGH, a binary 8 is produced.

### Status Register

The Status Register holds the 8-bit status word. With the Status-Register Enable, (SRE) input LOW and the IEN input LOW, the Status Register is updated at the end of all instructions except NO-OP, Save-Status and Test-Status instructions. SRE going HIGH or IEN going HIGH inhibits the Status Register from changing.

The lower four bits of the Status Register contain the ALU status bits of Zero (Z), Carry, (C) Negative (N), and Overflow (OVR). The upper four bits contain a Link bit and three user-definable status bits (Flag 1, Flag 2, Flag 3).

With SRE LOW and IEN LOW, the lower four status bits are updated after each instruction except those mentioned above, NO-OP, Save Status, Status Test and the Status Set/Reset instruction for the upper four bits. Under the same conditions, the upper four status bits are changed only during their respective Status Set/Reset instructions and during Status Load instructions in the word mode. The Link-Status bit is also updated after each shift instruction.

The Status Register can be loaded from the internal Y-bus, and can also be selected as a source for the internal Y-bus. When the Status Register is loaded in the word mode, all 8-bits are updated; in the byte mode, only the lower 4 bits (Z, C, N, OVR) are updated.

When the Status Register is selected as a source in the word mode, all eight bits are loaded into the lower byte of the destination; the upper byte of the destination is loaded with all zeros. In the byte mode, the Status Register again loads into the lower byte of the destination, but the upper byte remains unchanged. This Store and Load combination allows saving the restoring the Status Register for interrupt and subroutine processing. The four lower status bits (Z, C, N, OVR) can be read directly via the bidirectional T bus. These four bits are available as outputs on the  $T_{1-4}$  outputs whenever  $\mathsf{OE}_\mathsf{T}$  is HIGH.

### Condition-Code Generator/Multiplexer

The Condition-Code Generator/Multiplexer contains the logic necessary to develop the 12 condition-code test signals. The

multiplexer portion can select one of these test signals and place it on the CT output for use by the microprogram sequence. The multiplexer may be addressed in two different ways. One way is through the Test Instruction. This instruction specifies the test condition to be placed in the CT output, but does not allow an ALU operation at the same time. The second method uses the bidirectional T bus as an input. This requires extra bits in the microword, but provides the ability to simultaneously test and execute. The test instruction lines,  $\rm l_{0-4}$ , have priority over  $\rm T_{1-4}$ , for testing status.

### Three-State Output Buffers

There are two sets of Three-State Output Buffers in the Am29116. One set controls the bidirectional, 16-bit Y bus. These outputs are enabled by placing a LOW on the OE input. A HIGH puts the Y outputs in the high-impedance state, allowing data to be input to the Data latch from an external source.

The second set of Three-State Output Buffers controls the bidirectional 4-bit T bus and is enabled by placing a HIGH on the  $OE_T$  input. This allows storing the four internal ALU status

bits (Z, C, N, OVR) externally. A LOW OE<sub>T</sub> input forces the T outputs into the high-impedance state. External devices can then drive the T bus to select a test condition for the CT output.

#### Instruction Latch and Decoder

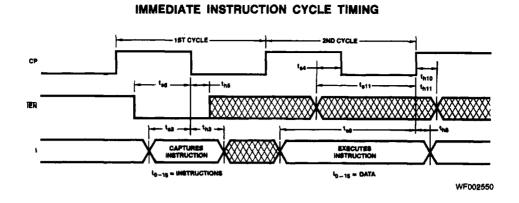

The 16-bit Instruction Latch is normally transparent to allow decoding of the Instruction Inputs by the Instruction Decoder into the internal control signals for the Am29116. All instructions except Immediate Instructions are executed in a single clock cycle.

Immediate instructions require two clock cycles for execution. During the first clock cycle, the Instruction Decoder recognizes that an Immediate Instruction is being specified and captures the data on the Instruction Inputs in the Instruction Latch. During the second clock cycle, the data on the Instruction Inputs is used as one of the operands for the function specified during the first clock cycle. At the end of the second clock cycle, the Instruction Latch is returned to its transparent state.

### INSTRUCTION SET

The instruction set of the Am29116 is very powerful. In addition to the single and two operand logical and arithmetic instructions, the Am29116 instruction set contains functions particularly useful in controller applications: bit set, bit reset, bit test, rotate and merge, rotate and compare, and cyclic-redundancy-check (CRC) generation. Complex instructions like rotate and merge, rotate and compare, and prioritize are executed in a single microcycle.

Three data types are supported by the Am29116.

- Bit

- Byte

- Word (16-bit)

In the byte mode data is written into the lower half of the word and the upper half is unchanged. The special case is when the status register is specified as the destination. In the byte mode the LSH (OVR, N, C, Z) of the status register is updated and in the word mode all eight bits of the status register are updated. The status register does not change for save status and test status instructions. In the test status instructions the CT output has the result and the Y-bus is undefined.

The Am29116 Instruction Set can be divided into eleven types of instructions. These are:

- Single Operand

- Two Operand

- Single Bit Shift

Rotate and Merge

- Bit Oriented

- Rotate by n Bits

- Rotate and Compare

- Prioritize

- Cyclic-Redundancy-Check

- Status

- No-Op

Each instruction type is arbitrarily divided into quadrants. Two of the sixteen instruction lines decode to four quadrants labelled from 0 to 3. The quadrants were defined mainly for convenience in classification of the instruction set and addressing modes and can be used together with the OP CODES to distinguish the instructions.

The following pages describe each of the instruction types in detail. Throughout the description  $\overline{OEy}$  is assumed to be LOW allowing ALU outputs on the Y-bus.

Table 1 illustrates operand source-destination combinations for each instruction type.

TABLE 1. OPERAND SOURCE DESTINATION COMBINATIONS

| Instruction Type      | Operand                          | Combination                 | ons (Note 1)                                       |

|-----------------------|----------------------------------|-----------------------------|----------------------------------------------------|

|                       | Source                           | (R/S)                       | Destination                                        |

| Single Operand        | RAM (I<br>AC<br>E<br>D(C<br>D(S  | CC<br>OE)<br>SE)            | RAM<br>ACC<br>Y Bus<br>Status<br>ACC and<br>Status |

|                       | Source (R)                       | Source (S)                  | Destination                                        |

| Two Operand           | RAM<br>RAM<br>D<br>D<br>ACC<br>D | ACC<br>I<br>RAM<br>ACC<br>I | RAM<br>ACC<br>Y Bus<br>Status<br>ACC and<br>Status |

|                       | Source                           | e (U)                       | Destination                                        |

| Single Bit Shift      | RA<br>AC<br>C                    | KM<br>CC                    | RAM<br>ACC<br>Y Bus<br>RAM<br>ACC<br>Y Bus         |

|                       | Source                           | e (U)                       | Destination                                        |

| Rotate n Bits         | AC                               | M<br>C<br>C                 | RAM<br>ACC<br>Y Bus                                |

|                       | Source                           | (R/S)                       | Destination                                        |

| Bit Oriented          | AC                               | AM<br>CC                    | RAM<br>ACC<br>Y Bus                                |

|                       | Rotated                          |                             | Non-Rotated<br>Source/                             |

|                       | Source (U)                       | Mask (S)                    | Destination (R)                                    |

| Rotate and Merge      | D<br>D<br>D<br>ACC<br>RAM        | RAM<br> <br>ACC<br>         | ACC<br>ACC<br>RAM<br>RAM<br>RAM<br>ACC             |

| Batta and             | Rotated<br>Source (U)            | Mask (S)                    | Non-Rotated<br>Source/<br>Destination (R)          |

| Rotate and<br>Compare | D<br>D<br>D<br>RAM               | I<br>ACC                    | RAM<br>RAM<br>ACC                                  |

| Instruction Type     | Operano    | 1 Combination                                | ons (Note 1)                |

|----------------------|------------|----------------------------------------------|-----------------------------|

|                      | Source (R) | Mask (S)                                     | Destination                 |

| Prioritize (Note 3)  | RAM        | RAM                                          | RAM                         |

| 1 11011020 (140to 0) | ACC        | ACC                                          | ACC                         |

|                      | D          | 0                                            | Y Bus                       |

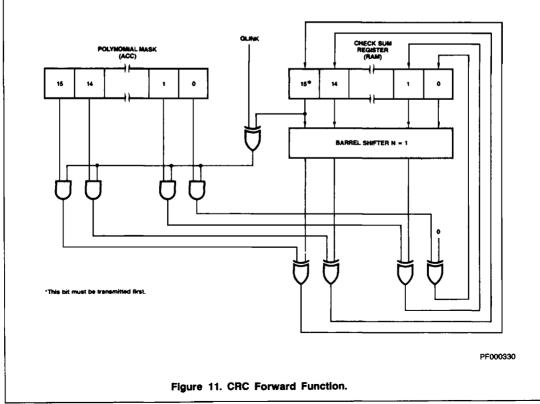

| Cyclic               | Data In    | Destination                                  | Polynomial                  |

| Redundancy<br>Check  | QLINK      | RAM                                          | ACC                         |

| No Operation         |            | _                                            |                             |

|                      |            | Bits Affect                                  | ted                         |

| Set Reset Status     |            | OVR, N, C<br>LINK<br>Flag1<br>Flag2<br>Flag3 | s, Z                        |

|                      | Sou        | irce                                         | Destination                 |

| Store Status         | Sta        | tus                                          | RAM<br>ACC<br>Y Bus         |

|                      | Source (R) | Source (S)                                   | Destination                 |

| Status Load          | D<br>ACC   | <b>ACC</b> —                                 | Status<br>Status and<br>ACC |

|                      | D          | 1                                            |                             |

|                      | To         | est Condition                                | n (CT)                      |

|                      |            | (N⊕OVR)<br>N⊕OVP                             |                             |

|                      |            | Z<br>OVR                                     |                             |

| Test Status          |            | Low                                          |                             |

| , set Gialge         |            | 2 + C                                        |                             |

|                      |            | 2 + C                                        |                             |

|                      |            | LINK                                         |                             |

|                      |            | Flag 1                                       |                             |

|                      |            | Flag 2<br>Flag 3                             |                             |

Notes: 1. When there is no dividing line between the R&S OPERAND or SOURCE and DESTINATION, the two must be used as a given pair. But where there exists such a separation, any combination of them is possible.

In the SINGLE OPERAND INSTRUCTION, RAM cannot be used when both ACC and STATUS are designated as a DESTINATION.

<sup>3.</sup> In the PRIORITIZE INSTRUCTION, OPERAND and MASK must be different sources.

## SINGLE OPERAND INSTRUCTIONS

The Single Operand Instructions contain four indicators: byte or word mode, opcode, source and destination. They are further subdivided into two types. The first type uses RAM as a source or destination or both, and the second type does not use RAM as a source or destination. Both types have different instruction formats as shown below. Under the control of instruction inputs, the desired function is performed on the source and the result is either stored in the specified destination or placed on the Y-bus or both. For a special case where 8-bit to 16-bit conversion is needed, the Am29116 is capable of extending sign bit (D(SE)) or binary zero (D(0E)) over 16-bits in the word mode. The least significant four bits of the Status Register (OVR, N, C, Z) are affected by the function performed in this category. The most significant bits of status register (FLAG1, FLAG2, FLAG3, LINK) are not affected. The only limitation in this type is that the RAM cannot be used as a source when both ACC and the Status Register are specified as a destination.

### SINGLE OPERAND FIELD DEFINITIONS

|       | 15  | 14 13 | 12 9   | 8 5      | 4 0         |

|-------|-----|-------|--------|----------|-------------|

| SOR   | B/W | Quad  | Opcode | SRC-Dest | RAM Address |

|       |     |       |        |          |             |

| SONFI | B/W | Quad  | Opcode | SRC      | Dest        |

### SINGLE OPERAND INSTRUCTION

|                          | 15               | 14 13             | 12 9                         |                            |                                                              | 8 5                                                                  |                                                                                |                                      |                                                                  | 4 0                              |                           |                                                                 |

|--------------------------|------------------|-------------------|------------------------------|----------------------------|--------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------|----------------------------------|---------------------------|-----------------------------------------------------------------|

| instruction <sup>1</sup> | B/W <sup>2</sup> | Quad <sup>3</sup> |                              | Орс                        | ode                                                          | 1                                                                    |                                                                                | R/S <sup>4</sup>                     | Dest <sup>4</sup>                                                |                                  | RAM                       | Address                                                         |

| SOFI                     | 0 = B<br>1 = W   | 10                | 1100<br>1101<br>1110<br>1111 | MOVE<br>COMP<br>INC<br>NEG | SRC Dest<br>SRC Dest<br>SRC + 1 Dest<br>SRC + 1 Dest         | 0000<br>0010<br>0011<br>0100<br>0110<br>0111<br>1000<br>1001<br>1010 | SORA<br>SORY<br>SORS<br>SOAR<br>SODR<br>SOIR<br>SOZR<br>SOZER<br>SOSER<br>SORR |                                      | ACC<br>Y Bus<br>Status<br>RAM<br>RAM<br>RAM<br>RAM<br>RAM<br>RAM | 11111                            | R00<br><br>R31            | RAM Reg 00<br><br>RAM Reg 31                                    |

| Instruction              | B/W              | Quad              |                              | Орс                        | ode                                                          |                                                                      |                                                                                | R/S <sup>4</sup>                     |                                                                  |                                  | Des                       | tination                                                        |

| SONR                     | 0 = B<br>1 = W   | 11                | 1100<br>1101<br>1110<br>1111 | MOVE<br>COMP<br>INC<br>NEG | SRC → Dest<br>SRC → Dest<br>SRC + 1 → Dest<br>SRC + 1 → Dest | 0100<br>0110<br>0111<br>1000<br>1001<br>1010                         | SOA<br>SOD<br>SOI<br>SOZ<br>SOZE<br>SOSE                                       | ACC<br>D<br>I<br>0<br>D(0E)<br>D(SE) |                                                                  | 00000<br>00001<br>00100<br>00101 | NRY<br>NRA<br>NRS<br>NRAS | Y Bus<br>ACC<br>Status <sup>5</sup><br>ACC, Status <sup>5</sup> |

- Notes: 1. The instruction mnemonic designates different instruction formats used in the Am29116. They are useful in assembly microcode with the System 29 AMDASM<sup>TM</sup> meta assembler.

2. B = Byte Mode, W = Word Mode.

- 3. See Instruction Set description.

- 4. R = Source; S = Source; Dest = Destination.

- 5. When status is destination

- Status i ← Yi i = 0 to 3 (Byte mode) i = 0 to 7 (Word mode)

### Y BUS AND STATUS - SINGLE OPERAND INSTRUCTIONS

| Instruction | Opcode | Description   | B/W          | Y — Bus    | Flag3 | Flag2 | Flag1 | LINK | OVR | N | С | Z |

|-------------|--------|---------------|--------------|------------|-------|-------|-------|------|-----|---|---|---|

| SOR         | MOVE   | SRC → Dest    | 0 <b>= B</b> | Y ⊷ SRC    | NC    | NC    | NC    | NC   | 0   | ٥ | 0 | U |

| SONR        | COMP   | SRC → Dest    | 1 = W        | Y ⊷ SAC    | NC    | NC    | NC    | NC   | 0   | U | 0 | U |

|             | INC    | SRC +1 → Dest | Ì            | Y - SRC +1 | NC    | NC    | NC    | NC   | U   | כ | ٥ | U |

|             | NEG    | SRC +1 → Dest |              | Y - SRC +1 | NC    | NC    | NC    | NC   | U   | U | υ | U |

SRC = Source U - Update NC - No Change 0 = Reset

1 = Set

### TWO OPERAND INSTRUCTIONS

The Two Operand Instructions contain five indicators: byte or word mode, opcode, R source, S source, and destination. They are further subdivided into two types. The first type uses RAM as the source and/or destination and the second type does not use RAM as source or destination. The first type has two formats; the only difference is in the quadrant. Under the control of instruction inputs, the desired function is performed on the specified sources and the result is stored in the

specified destination or placed on the Y-bus or both. The least significant four bits of the status register (OVR, N, C, Z) are affected by the arithmetic functions performed and only the N and Z bits are affected by the logical functions performed. The OVR and C bits of the status register are forced to ZERO for logical functions. Add with carry and Subtract with carry instructions are useful for Multiprecision Add or Subtract.

### TWO OPERAND FIELD DEFINITIONS

15 14 13 12 SRC-SRC TOR1 Quad Opcode RAM Address -Dest SRC-SRC TOR<sub>2</sub> **RAM Address** B/W Quad Opcode -Dest B/W Quad SRC-SRC TONR Opcode Dest

## TWO OPERAND INSTRUCTIONS

| Instruction | B/W            | Quad |                                                               |                                                                               | R <sup>1</sup>                                 | S <sup>1</sup>                                        | Dest <sup>1</sup>                                          |                                                                                      | Opcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | RAM Address    |  |

|-------------|----------------|------|---------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|--|

| TOR1        | 0 = B<br>1 = W | 00   | 0000<br>0010<br>0011<br>1000<br>1010<br>1011<br>1110<br>11110 | TORAA<br>TORIA<br>TODRA<br>TORAY<br>TORIY<br>TODRY<br>TORAR<br>TORIR<br>TODRR | RAM<br>RAM<br>D<br>RAM<br>RAM<br>D<br>RAM<br>D | ACC<br>I<br>RAM<br>ACC<br>I<br>RAM<br>ACC<br>I<br>RAM | ACC<br>ACC<br>ACC<br>Y Bus<br>Y Bus<br>Y Bus<br>HAM<br>RAM | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1011 | SUBR S minus R SUBRC <sup>2</sup> S minus R with carry R minus S SUBSC <sup>2</sup> R minus S ADDC R plus S ADDC R P P S EXOR R R S EXOR R R S EXOR R R S EXNOR R S S EXNOR R S S EXNOR R S S EXNOR R R S S S S S S S S S S S S S S S S S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00000 | R00 RAM Reg 00 |  |

| Instruction | B/W            | Quad |                                                               | _                                                                             | R <sup>1</sup>                                 | S <sup>1</sup>                                        | Dest <sup>1</sup>                                          |                                                                                      | Opcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | RAM Address    |  |

| TOR2        | 0 = B<br>1 = W | 10   | 0001<br>0010<br>0101                                          | TODAR<br>TOAIR<br>TODIR                                                       | D<br>ACC<br>D                                  | ACC<br>I                                              | RAM<br>RAM<br>RAM                                          | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1011 | SUBR S minus R SUBRC <sup>2</sup> S minus R with carry H minus S SUBSC <sup>2</sup> R minus S with carry ADD R los S ADDC R los S NAND R s S NAND R s S SUBSC <sup>3</sup> R los S NAND R s S SUBSC <sup>4</sup> R los S NAND R s S SUBSC <sup>4</sup> R los S NAND R s S SUBSC <sup>4</sup> R los S S SUBSC <sup>4</sup> R los S SUBSC <sup>4</sup> R los S S S S S S S S S S S S S S S S S S S | 11111 | R31 RAM Reg 31 |  |

Note 1: R = Source S = Source

Dest = Destination

Note 2: During subtraction the carry is interpreted as borrow.

## TWO OPERAND INSTRUCTIONS

| Instruction | B/W            | Quad |                      |                      | R <sup>1</sup> | S <sup>1</sup> |              | Op            | ocode                                |                         | Destination                                     |

|-------------|----------------|------|----------------------|----------------------|----------------|----------------|--------------|---------------|--------------------------------------|-------------------------|-------------------------------------------------|

|             | 0 = B<br>1 = W | 11   | 0001<br>0010<br>0101 | TODA<br>TOAI<br>TODI | D<br>ACC<br>D  | ACC<br>I       | 0000<br>0001 | SUBR<br>SUBRC | S minus R<br>S minus R with<br>carry | 00000<br>00001<br>00100 | NRY Y Bus<br>NRA ACC<br>NRS Status <sup>2</sup> |

|             | l              |      | [                    |                      | _              | -              | 0010         | SUBS          | R minus S                            | 00101                   | NRAS ACC, Status                                |

| TONR        |                |      |                      |                      |                |                | 0011         | SUBSC         | R minus S with carry                 |                         |                                                 |

|             |                |      |                      |                      |                |                | 0100         | ADD           | R plus S                             | l l                     |                                                 |

|             |                |      |                      |                      |                |                | 0101         | ADDC          | R plus S with carry                  |                         |                                                 |

|             | l              | l '  | ì                    |                      |                |                | 0110         | AND           |                                      | 1                       |                                                 |

|             |                |      |                      |                      |                |                | 0111         | NAND          | R•S<br>R•S                           |                         |                                                 |

|             |                |      |                      |                      |                |                | 1000         | EXOR          | <u>R⊕\$</u>                          | ı                       |                                                 |

|             |                |      |                      |                      |                |                | 1001         | NOR           | R+S                                  | 1                       |                                                 |

|             |                |      | <b>!</b>             |                      |                |                | 1010         | OR            | <u>R + S</u>                         | 1                       |                                                 |

|             |                | l .  | 1                    |                      |                |                | 1011         | EXNOR         | R⊕S                                  | - 1                     |                                                 |

Notes 1: R = Source S = Source

2: When status is destination,

Status i... Yi i = 0 to 3 (Byte mode)

i... 20 to 7 (Word mode)

3: During subtraction the carry is interpreted as borrow.

## Y BUS AND STATUS CONTENTS - TWO OPERAND INSTRUCTIONS

| instruction  | Opcode | Description          | B/W   | Y - Bus              | Flag3 | Flag2 | Flag<br>1 | LINK | OVR | N | С | z |

|--------------|--------|----------------------|-------|----------------------|-------|-------|-----------|------|-----|---|---|---|

|              | SUBR   | S minus R            | 0 = B | Y <sub>←</sub> S+R+1 | NC    | NC    | NC        | NC   | U   | U | U | υ |

|              | SUBRC  | S minus R with carry | 1 = w | Y - S + R + QC       | NC    | NC    | NC        | NC   | U   | υ | υ | υ |

|              | SUBS   | A minus S            |       | Y-R+S+1              | NC    | NC    | NC        | NC   | U   | υ | υ | U |

| TOR1<br>TOR2 | SUBSC  | R minus S with carry |       | Y - R + Š + QC       | NC    | NC    | NC        | NC   | U   | U | U | U |

| TONR         | ADD    | R plus S             |       | Y⊷R+S                | NC    | NC    | NC        | NC   | U   | U | v | υ |

|              | ADDC   | R plus S with carry  |       | Y_R+S+QC             | NC    | NC    | NC        | NC   | U   | U | U | U |

|              | AND    | R⋅S                  |       | Y-R; AND S;          | NC    | NC    | NC        | NC   | 0   | U | 0 | U |

|              | NAND   | R·S                  |       | Yi⊷Ri NAND Si        | NC    | NC    | NC        | NC   | 0   | U | 0 | U |

|              | EXOR   | R⊕S                  |       | Yi ← Ri EXOR Si      | NC    | NC    | NC        | NC   | 0   | υ | 0 | U |

|              | NOR    | R+S                  |       | Yi⊷Ri NOR Si         | NC    | NC    | NC        | NC   | 0   | υ | 0 | U |

|              | OR     | R+S                  |       | Yi⊷Ri OR Si          | NC    | NC    | NC        | NC   | 0   | U | 0 | U |

|              | EXNOR  | R⊕S                  |       | Yi ← Ri EXNOR Si     | NC    | NC    | NC        | NC   | 0   | 0 | 0 | U |

U = Update NC = No Change

0 = Reset

### SINGLE BIT SHIFT INSTRUCTIONS

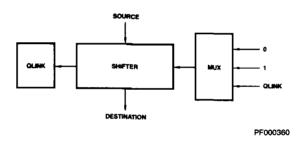

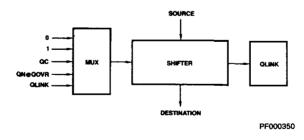

The Single Bit Shift Instructions contain four indicators: byte or word mode, direction and shift linkage, source and destination. They are further subdivided into two types. The first type uses RAM as the source and/or destination and the second type does not use RAM as source or destination. Under the control of the instruction inputs, the desired shift function is performed on the specified source and the result is stored in the specified destination or placed on the Y-bus or both. The direction and shift linkage indicator defines the direction of the shift (up or down) as well as what will be shifted into the vacant bit. On a shift-up instruction, the LSB may be loaded with ZERO. ONE.

or the Link-Status bit (QLINK). The MSB is loaded into the Link-Status bit as shown in Figure 2. On a shift-down instruction, the MSB may be loaded with ZERO, ONE, the contents of the Status Carry flip-flop, (QC), the Exclusive-OR of the Negative-Status bit and the Overflow-Status bit (QN  $\oplus$  QOVR) or the Link-Status bit. The LSB is loaded into the Link-Status bit as shown in Figure 3. The N and Z bits of the Status register are affected but the OVR and C bits are forced to ZERO. The Shift-Down with QN  $\oplus$  QOVR is useful for Two's Complement multiplication.

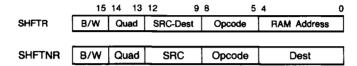

### SINGLE BIT SHIFT FIELD DEFINITIONS:

Figure 2. Shift Up Function.

Figure 3. Shift Down Function.

## SINGLE BIT SHIFT INSTRUCTIONS

### SINGLE BIT SHIFT

| instruction | B/W        | Quad |              |            | U <sup>1</sup> | Dest <sup>1</sup> |                                                              | Оре                                                                   | code                                                   |                                                     |                | RAM        | Addres       | 8 |

|-------------|------------|------|--------------|------------|----------------|-------------------|--------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------|----------------|------------|--------------|---|

| SHFTR       | 0-B<br>1-W | 10   | 0110<br>0111 | SHAR       | RAM<br>D       | RAM<br>RAM        | 0000<br>0001<br>0010<br>0100<br>0101<br>0110<br>0111<br>1000 | SHUPZ<br>SHUP1<br>SHUPL<br>SHONZ<br>SHON1<br>SHONL<br>SHONC<br>SHONOV | Up<br>Up<br>Up<br>Down<br>Down<br>Down<br>Down         | 0<br>1<br>QLINK<br>0<br>1<br>QLINK<br>QC<br>QN⊕QOVR | 11111          | R00<br>R31 | RAM Re       | • |

| Instruction | B/W        | Quad |              |            | U <sup>1</sup> |                   |                                                              | Оре                                                                   | code                                                   |                                                     |                | Des        | tination     |   |

| SHFTNR      | 0-B<br>1-W | 11   | 0110<br>0111 | SHA<br>SHD | ACC<br>D       |                   | 0000<br>0001<br>0010<br>0100<br>0101<br>0110<br>0111<br>1000 | SHUPZ<br>SHUP1<br>SHUPL<br>SHDNZ<br>SHDN1<br>SHDNL<br>SHDNC<br>SHDNOV | Up<br>Up<br>Up<br>Down<br>Down<br>Down<br>Down<br>Down | 0<br>1<br>QLINK<br>0<br>1<br>QLINK<br>QC<br>QN⊕QOVR | 00000<br>00001 | NRY<br>NRA | Y Bus<br>ACC |   |

U = Source Dest = Destination Note 1.

## Y BUS AND STATUS - SINGLE BIT SHIFT INSTRUCTIONS

| Instruction  | Opcode                   | Description                           | B/W          | Y - Bus                                                                                                                                                                  | Flag3 | Flag2 | Flag1    | LINK               | OVR    | N                 | С  | Z   |

|--------------|--------------------------|---------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|----------|--------------------|--------|-------------------|----|-----|

|              | SHUPZ<br>SHUP1           | Up 0<br>Up 1                          | 1 – W        | Y <sub>i</sub> -SRC <sub>i-1</sub> , i=1 to 15;<br>Y <sub>0</sub> -Shift Input                                                                                           | NC    | NC    | NC       | SRC <sub>15</sub>  | 0      | SRC <sub>14</sub> | 0  | U   |

| SHR<br>SHNR  | SHUPL                    | Up QLINK                              | 0 <b>-</b> B | Y <sub>i</sub> -SRC <sub>i-1</sub> , i=1 to 7;<br>Y <sub>0</sub> -Shift Input;<br>Y <sub>8</sub> -SRC <sub>7</sub> , Y <sub>1</sub> -SRC <sub>i-8</sub><br>for i=9 to 15 | NC    | NC    | NC       | SRC7*              | 0      | SAC <sub>6</sub>  | 0  | U   |

|              | SHDNZ<br>SHDN1           | Down 0<br>Down 1                      | 1 – W        | Y <sub>i</sub> -SRC <sub>i+1</sub> , i=0 to 14;<br>Y <sub>15</sub> -Shift Input                                                                                          | NC    | NC    | NC       | SRC <sub>0</sub> . | 0      | Shift<br>Input    | o  | U   |

|              | SHDNL<br>SHDNC<br>SHCNOV | Down QLINK<br>Down QC<br>Down QN@QOVR | 0-B          | Y <sub>i</sub> -SRC <sub>i+1</sub> , i=0 to 6;<br>Y <sub>i</sub> -SRC <sub>i-7</sub> , i=8 to 14;<br>Y <sub>7,15</sub> -Shift Input                                      | NC    | NC    | NC       | SRC <sub>0</sub> • | 0      | Shift<br>Input    | 0  | υ   |

| SRC - Source |                          |                                       |              |                                                                                                                                                                          |       |       | *Shifted | Output is          | loaded | into the          | QI | INK |

SRC = Source

U = Update

NC = No Change

0 = Reset

1 = Set

i = 0 to 15 when not specified

### **BIT ORIENTED INSTRUCTIONS**

The Bit Oriented Instructions contain four indicators: byte or word mode, operation, source/destination, and the bit position of the bit to be operated on (Bit 0 is the least significant bit). They are further subdivided into two types. The first type uses the RAM as both source and destination and has two kinds of formats which differ only by quadrant. The second type does not use the RAM as a source or a destination. Under the control of the instruction inputs, the desired function is performed on the specified source and the result is stored in the specified destination or placed on the Y-bus or both. The operations which can be performed are: Set Bit n which forces the nth bit to a ONE leaving other bits unchanged; Reset Bit n

which forces the n<sup>th</sup> bit to ZERO leaving the other bits unchanged; Test Bit n, which sets the ZERO Status Bit depending on the state of bit n leaving all the bits unchanged; Load 2<sup>n</sup>, which loads ONE in Bit position n and ZERO in all other bit positions; Load 2<sup>n</sup> which loads ZERO in bit position n and ONE in all other bit positions; increment by 2<sup>n</sup>, which adds 2<sup>n</sup> to the operand; and decrement by 2<sup>n</sup> which subtracts 2<sup>n</sup> from the operand. For all the Load, Set, Reset and Test instructions, the N and Z bits are affected and OVR and C bit of the Status register are forced to ZERO. For all arithmetic instructions the LSH (OVR, C, N, Z bits) of the Status register is affected.

## BIT ORIENTED FIELD DEFINITIONS

|      | 15  | 14 13 | 129 | 8 5    | 4 0         |

|------|-----|-------|-----|--------|-------------|

| BOR1 | B/W | Quad  | 2   | Opcode | RAM Address |

|      |     |       |     |        |             |

| BOR2 | B/W | Quad  | n   | Opcode | RAM Address |

|      |     |       |     |        |             |

| BONR | B/W | Quad  | n   | 1100   | Opcode      |

## **BIT ORIENTED INSTRUCTIONS**

| Instruction | B/W            | Quad | n       | Oi                       | pcode                                                                                                           | RAM Address                                                                                                       |                                                                                      |                                                                                                                                                                                                                                                                                                             |

|-------------|----------------|------|---------|--------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOR1        | 0 = B<br>1 = W | 11   | 0 to 15 | 1110 RSTNR               | Set RAM, bit n<br>Reset RAM, bit n<br>Test RAM, bit n                                                           | 00000<br>11111                                                                                                    | R00<br>R31                                                                           | RAM Reg 00<br>RAM Reg 31                                                                                                                                                                                                                                                                                    |

| instruction | B/W            | Quad | n       | O                        | pcode                                                                                                           |                                                                                                                   | RAM .                                                                                | Address                                                                                                                                                                                                                                                                                                     |

| BOR2        | 0 = B<br>1 = W | 10   | 0 to 15 | 1101 LDC2NR<br>1110 A2NR | 2 <sup>n</sup> → RAM<br>2 <sup>n</sup> → RAM<br>RAM plus 2 <sup>n</sup> → RAM<br>RAM minus 2 <sup>n</sup> → RAM | 00000<br><br>11111                                                                                                | R00<br><br>R31                                                                       | RAM Reg 00<br>RAM Reg 31                                                                                                                                                                                                                                                                                    |

| Instruction | B/W            | Quad | n       |                          |                                                                                                                 |                                                                                                                   | Ор                                                                                   | code                                                                                                                                                                                                                                                                                                        |

| BONFI       | 0=B<br>1=W     | 11   | 0 to 15 | 1100                     |                                                                                                                 | 00000<br>00001<br>00010<br>00100<br>00101<br>00111<br>00111<br>10000<br>10001<br>10100<br>10100<br>10110<br>10110 | TSTNA RSTNA RSTNA A2NA S2NA LDC2NA LDC2NA TSTND RSTND SETND A2NDY S2NDY LS2NY LDC2NY | Test ACC, bit n Reset ACC, bit n Set ACC, bit n ACC plus 2 <sup>n</sup> _ ACC ACC minus 2 <sup>n</sup> _ ACC 2 <sup>n</sup> _ ACC 2 <sup>n</sup> _ ACC Test D, bit n Reset D, bit n Set D, bit n D plus 2 <sup>n</sup> _ Y BUS D minus 2 <sup>n</sup> _ Y Bus 2 <sup>n</sup> _ Y Bus 2 <sup>n</sup> _ Y Bus |

## **BIT ORIENTED INSTRUCTIONS**

## Y BUS AND STATUS - BIT ORIENTED INSTRUCTIONS

| Instruction | Opcode         | Description                       | B/W            | Y - Bus                                                     | Flag3    | Flag2    | Flag1    | LINK     | OVR | N  | C | Z      |

|-------------|----------------|-----------------------------------|----------------|-------------------------------------------------------------|----------|----------|----------|----------|-----|----|---|--------|

| BOR1        | SETNA<br>RSTNR | Set RAM Bit n<br>Reset RAM, Bit n | 0 = B<br>1 = W | Yi←RAMi for i≠n; Yn←1<br>Yi←RAMi for i≠n; Yn←0              | NC<br>NC | NC<br>NC | NC<br>NC | NC<br>NC | 0   | 20 | 0 | 0<br>U |

|             | TSTNR          | Test Ram, Bit n                   |                | Yi-0 for i≠n; Yn-SRCn                                       | NC       | NC       | NC       | NC       | 0   | ٥  | 0 | U      |

|             | LD2NR          | 2 <sup>n</sup> →RAM               |                | $Y_i = 0$ for $i \neq n$ ; $Y_n = 1$                        | NC       | NC       | NC       | NC       | 0   | υ  | 0 | 0      |

| 2020        | LDC2NR         | 2 <sup>n</sup> → RAM              |                | Y <sub>i</sub> −1 for l≠n; Y <sub>n</sub> −0                | NC       | NC       | NC       | NC       | 0   | ٦  | 0 | 0      |

| BOR2        | A2NFI          | RAM + 2 <sup>n</sup> → RAM        |                | Yi-RAM + 2 <sup>n</sup>                                     | NC       | NC       | NC       | NC       | U   | Ü  | U | U      |

|             | S2NR           | RAM 2 <sup>n</sup> → RAM          |                | Yi-RAM - 2 <sup>n</sup>                                     | NC       | NC       | NC       | NC       | U   | υ  | U | U      |

|             | TSTNA          | Test ACC, Bit n                   |                | Y <sub>i</sub> ←0 for i≠n; Y <sub>n</sub> ←ACC <sub>n</sub> | NC       | NC       | NC       | NC       | 0   | υ  | 0 | U      |

| SE          | RSTNA          | Reset ACC, Bit n                  |                | Y <sub>i</sub> -ACC <sub>i</sub> for i≠n; Y <sub>n</sub> -0 | NC       | NC       | NC       | NC       | 0   | V  | 0 | U      |

|             | SETNA          | Set ACC, Bit n                    |                | Y <sub>i</sub> -ACC <sub>i</sub> for i≠n; Y <sub>n</sub> -1 | NC       | NC       | NC       | NC       | 0   | U  | 0 | 0      |

|             | A2NA           | ACC + 2 <sup>n</sup> → ACC        |                | Yi-ACC+2n                                                   | NC       | NC       | NC       | NC       | U   | U  | U | u      |

|             | S2NA           | ACC - 2 <sup>n</sup> → ACC        |                | Yi-ACC-2 <sup>n</sup>                                       | NC       | NC       | NC       | NC       | Ų   | υ  | U | U      |

|             | LD2NA          | 2 <sup>⊓</sup> →ACC               |                | Y <sub>i</sub> ← 0 for i ≠ n; Y <sub>n</sub> ← 1            | NC       | NC       | NC       | NC       | 0   | U  | 0 | 0      |

| 2010        | LDC2NA         | 2ri → ACC                         |                | Yı-1 for i≠n; Y <sub>n</sub> -0                             | NC       | NC       | NC       | NC       | 0   | U  | 0 | 0      |

| BONR        | TSTND          | Test D, Bit n                     |                | Y <sub>i</sub> ←0 for i≠n; Y <sub>n</sub> ←D <sub>n</sub>   | NC       | NC       | NC       | NC       | 0   | υ  | 0 | u      |

|             | RSTND          | Reset D, Bit n*                   |                | $Y_i \leftarrow D_i$ for $i \neq n$ ; $Y_n \leftarrow 0$    | NC       | NC       | NC       | NC       | 0   | ۳  | 0 | u      |

|             | SETND          | Set D, Bit n*                     |                | Y <sub>i</sub> ←D <sub>i</sub> for i≠n; Y <sub>n</sub> ←1   | NC       | NC       | NC       | NC       | 0   | Ü  | 0 | 0      |

| <u> </u>    | A2NDY          | D+2 <sup>n</sup> →Y Bus           |                | Y - D + 2 <sup>n</sup>                                      | NC       | NC       | NC       | NC       | υ   | J  | U | υ      |

|             | S2NDY          | D-2 <sup>n</sup> -Y Bus           |                | Y ← D − 2 <sup>n</sup>                                      | NC       | NC       | NC       | NC       | U   | U  | U | U      |

| <u> </u>    | LD2NY          | 2 <sup>n</sup> → Y Bus            |                | Y <sub>i</sub> ←0 for i≠n; Y <sub>n</sub> ←1                | NC       | NC       | NC       | NC       | 0   | υ  | 0 | 0      |

|             | LDC2NY         | 2 <sup>ल</sup> → Y Bus            |                | $Y_i \vdash 1$ for $i \neq n$ ; $Y_n \vdash 0$              | NC       | NC       | NC       | NC       | 0   | υ  | 0 | 0      |

SRC = Source U = Update NC = No Change 0 = Reset i = 0 to 15 when not specified

<sup>\*</sup>Destination is not D Latch but Y Bus.

## ROTATE BY n BITS INSTRUCTIONS

The Rotate by n Bits Instructions contain four indicators: byte or word mode, source, destination and the number of places the source is to be rotated. They are further subdivided into two types. The first type uses RAM as a source and/or a destination and the second type does not use RAM as a source or destination. The first type has two different formats and the only difference is in the quadrant. The second type has only one format as shown in the table. Under the control of instruction inputs, the n indicator specifies the number of bit positions the source is to be rotated up (0 to 15), and the result

is either stored in the specified destination or placed on the Y-bus or both. An example of this instruction is given in Figure 4. In the Word mode, all 16-bits are rotated up while in the Byte mode, only lower 8-bits (0-7) are rotated up. In the Word mode, a rotate up by n bits is equivalent to a rotate down by (16-n) bits. Similarly, in the Byte mode a rotate up by n bits is equivalent to a rotate down by (8-n) bits. The N and Z bits of the Status Register are affected and OVR and C bits are forced to ZERO.

| EXAMPLE:    | n = 4, Wor  | d Mode |      |      |

|-------------|-------------|--------|------|------|

| Source      | 0001        | 0011   | 0111 | 1111 |

| Destination | 0011        | 0111   | 1111 | 0001 |

| EXAMPLE: I  | n = 4, Byte | Mode   |      |      |

| Source      | 0001        | 0011   | 0111 | 1111 |

0001

15 14 13 12 9 8 5 4

ROTR1 B/W Quad n SRC-Dest RAM Address

ROTATE BY n BITS FIELD DEFINITIONS

ROTR2 B/W Quad n SRC-Dest RAM Address

Figure 4. Rotate by n Example

0011

ROTNR B/W Quad n 1100 SRC-Dest

### ROTATE BY n BITS INSTRUCTIONS

0111

1111

| Instruction | B/W            | Quad | n       |                      |                      | U <sup>1</sup>    | Dest <sup>1</sup>   |                                  | RAM                          | Address              | •                            |

|-------------|----------------|------|---------|----------------------|----------------------|-------------------|---------------------|----------------------------------|------------------------------|----------------------|------------------------------|

| ROTR1       | 0 = B<br>1 = W | 00   | 0 to 15 | 1100<br>1110<br>1111 | RTRA<br>RTRY<br>RTRR | RAM<br>RAM<br>RAM | ACC<br>Y Bus<br>RAM | 00000                            | R00<br>R31                   | RAM R                |                              |

| Instruction | B/W            | Quad | n       |                      |                      | U <sup>1</sup>    | Dest <sup>1</sup>   |                                  | RAM                          | Addres               | •                            |

| ROTR2       | 0 = B<br>1 = W | 01   | 0 to 15 | 0000<br>0001         | RTAR                 | ACC<br>D          | RAM<br>RAM          | 00000                            | R00<br>R31                   | RAM R                |                              |

| instruction | B/W            | Quad | n       |                      |                      |                   |                     |                                  |                              | U <sup>1</sup>       | Dest <sup>1</sup>            |

| ROTNR       | 0 = B<br>1 = W | 11   | 0 to 15 | 1100                 |                      |                   |                     | 11000<br>11001<br>11100<br>11101 | RTDY<br>RTDA<br>RTAY<br>RTAA | D<br>D<br>ACC<br>ACC | Y Bus<br>ACC<br>Y Bus<br>ACC |

Note 1: U = Source Dest = Destination

Destination

### Y BUS AND STATUS - ROTATE BY n BITS INSTRUCTIONS

| Instruction    | Op-<br>code | B/W          | Y - Bus                                                                         | Flag3 | Flag2 | Flag1 | LINK | OVR | N                  | С | z |

|----------------|-------------|--------------|---------------------------------------------------------------------------------|-------|-------|-------|------|-----|--------------------|---|---|

| ROTR1          |             | 1 – W        | Y <sub>i</sub> -SRC <sub>(i-n)mod16</sub>                                       | NC    | NC    | NC    | NC   | 0   | SRC 15-n           | 0 | U |

| ROTR2<br>ROTNR |             | 0 <b>-</b> B | Y <sub>i</sub> ←SRC <sub>i+8</sub> = SRC <sub>(i-n)mod8</sub><br>for i = 0 to 7 | NC    | NC    | NC    | NC   | 0   | SRC <sub>8-n</sub> | 0 | U |

SRC = Source U = No Change

0 = Reset

### ROTATE AND MERGE INSTRUCTION

The Rotate and Merge Instructions contain five indicators: byte or word mode, rotated source, non-rotated source/ destination, mask and the number of bit positions a source is to be rotated. The function performed by the Rotate and Merge instruction is illustrated in Figure 5. The rotated source, U, is rotated up by the Barrel Shifter n places. The mask input then selects, on a bit by bit basis, the rotated U input or R

input. A ZERO in bit i of the mask will select the i<sup>th</sup> bit of the R input as the i<sup>th</sup> output bit, while ONE in bit i will select the i<sup>th</sup> rotated U input as the output bit. The output word is stored in the non-rotated operand location. The N and Z bits are affected. The OVR and C bits of the Status register are forced to ZERO. An example of this instruction is given in Figure 6.

### **ROTATE AND MERGE FIELD DEFINITIONS:**

## EXAMPLE: n = 4, Word Mode

| U           | 0011 | 0001 | 0101 | 0110 |

|-------------|------|------|------|------|

| Rotated U   | 0001 | 0101 | 0110 | 0011 |

| R           | 1010 | 1010 | 1010 | 1010 |

| Mask (S)    | 0000 | 1111 | 0000 | 1111 |

| Destination | 1010 | 0101 | 1010 | 0011 |

Figure 6. Rotate and Merge Example.

Pro

Figure 5, Rotate and Merge Function.

### ROTATE AND MERGE INSTRUCTION

| Instruction | B/W            | Quad | n       | L                                            |                                              | U <sup>1</sup>            | R/Des                                  | t <sup>1</sup> S <sup>1</sup> |       | RAM A          | Address                      |

|-------------|----------------|------|---------|----------------------------------------------|----------------------------------------------|---------------------------|----------------------------------------|-------------------------------|-------|----------------|------------------------------|

| ROTM        | 0 = B<br>1 = W | 01   | 0 to 15 | 0111<br>1000<br>1001<br>1010<br>1100<br>1110 | MDAI<br>MDAR<br>MDRI<br>MDRA<br>MARI<br>MRAI | D<br>D<br>D<br>ACC<br>RAM | ACC<br>ACC<br>RAM<br>RAM<br>RAM<br>ACC | RAM<br>I<br>ACC               | 00000 | R00<br><br>R31 | RAM Reg 00<br><br>RAM Reg 31 |

Note 1. U = Rotated Source

R/Dest = Non-Rotated Source and Destination

S = Mask

### Y BUS AND STATUS - ROTATED MERGE

|             |        |       |                                                                                                                              |       |       |       |      |     | _ |   |   |

|-------------|--------|-------|------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|-----|---|---|---|

| Instruction | Opcode | B/W   | Y - Bus                                                                                                                      | Flag3 | Flag2 | Flag1 | LINK | OVR | N | C | Z |

| ROTM        |        | 1=W   | Y <sub>i</sub> (Non Rot Op) <sub>i</sub> - (mask) <sub>i</sub> +<br>(Rot Op) <sub>(i - n)mod 18</sub> - (mask) <sub>i</sub>  | NC    | NC    | NC    | NC   | 0   | U | 0 | U |

|             |        | 0 = B | Y <sub>i</sub> ← (Non Rot Op) <sub>i</sub> · (mask) <sub>i</sub> +<br>(Rot Op) <sub>ii = nimod</sub> s · (mask) <sub>i</sub> | NC    | NC    | NC    | NC   | 0   | υ | ٥ | U |

U = Update

NC = No Change

0 = Reset

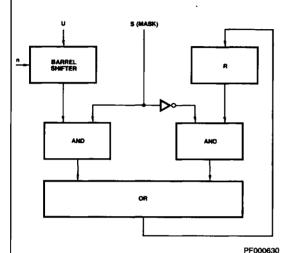

## ROTATE AND COMPARE INSTRUCTIONS

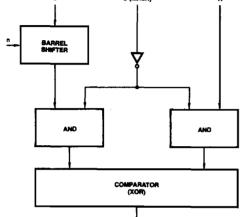

The Rotate and Compare Instructions contain five indicators: byte or word mode, rotated source, non-rotated source, mask, and the number of bit positions the rotated source is to be rotated up. Under the control of instruction inputs, the function performed by the Rotate and Compare instruction is illustrated in Figure 7. The rotated operand is rotated by the Barrel Shifter n places. The mask is inverted and ANDed on a bit-by-bit basis

with the output of the Barrel Shifter and R input. Thus, a ONE in the mask input eliminates that bit from the comparison. A ZERO allows the comparison. If the comparison passes, the Zero flag is set. If it fails, the Zero flag is reset. The N and Z bit are affected. The OVR and C bits of the Status register are forced to ZERO. An example of this instruction is given in Figure 8.

## ROTATE AND COMPARE FIELD DEFINITIONS 9 (MARK) R 15 14 13 12 9 8 5 4 (

|      | 15  | 14 13 | 129 | 8 5                              | 4         | 0   |

|------|-----|-------|-----|----------------------------------|-----------|-----|

| ROTC | B/W | Quad  | n   | Rot Src-<br>Non Rot Src-<br>Mask | RAM Addre | ess |

EXAMPLE: n = 4, Word Mode

| U              | 0011 | 0001 | 0101 | 0110 |

|----------------|------|------|------|------|

| U Rotated      | 0001 | 0101 | 0110 | 0011 |

| R              | 0001 | 0101 | 1111 | 0000 |

| Mask (S)       | 0000 | 0000 | 1111 | 1111 |

| Z (status) = 1 |      |      |      |      |

Figure 8. Rotate and Compare Examples.

PF000650

Figure 7. Rotate and Compare Function.

### ROTATE AND COMPARE INSTRUCTIONS

| Instruction | B/W          | Quad | n       |                              |                              | U <sup>1</sup>     | R <sup>1</sup>           | S <sup>1</sup> |       | RAM A          | ddress                   |

|-------------|--------------|------|---------|------------------------------|------------------------------|--------------------|--------------------------|----------------|-------|----------------|--------------------------|

| ROTC        | 0=B<br>1 = W | 01   | 0 to 15 | 0010<br>0011<br>0100<br>0101 | CDAI<br>CDRI<br>CDRA<br>CRAI | D<br>D<br>D<br>RAM | ACC<br>RAM<br>RAM<br>ACC | I<br>ACC       | 00000 | R00<br><br>R31 | RAM Reg 00<br>RAM Reg 31 |

Note 1. U = Rotated Source R = Non-Rotated Source S = Mask

### Y BUS AND STATUS - ROTATE AND COMPARE

| Instruction | Opcode | B/W   | Y - Bus                                                                                                                       | Flag3 | Fiag2 | Flag1 | LINK | OVR | N | С | Z |

|-------------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|-----|---|---|---|

| HOTC        |        | 1 = W | Y <sub>i</sub> ← (Non Rot Op) <sub>i</sub> · (mask) <sub>i</sub> ⊕<br>(Rot Op) <sub>(i – n)mod 16</sub> · (mask) <sub>i</sub> | NC    | NC    | NC    | NC   | 0   | υ | 0 | U |

| HOIC        |        | 0 = B | Y; ← (Non Rot Op); (mask); ⊕<br>(Rot Op)(i – n)mod 8 · (mask);                                                                | NC    | NC    | NC    | NC   | 0   | υ | 0 | υ |

U ~ Update

NC = No Change

0 = Reset

## PRIORITIZE INSTRUCTION

The Prioritize Instructions contain four indicators: byte or word mode, operand source (R), mask source (S) and destination. They are further subdivided into two types. The function performed by the Prioritize instruction is shown in Figure 9. The R operand is ANDed with the complement of the Mask operand. A ZERO in the Mask operand allows the corresponding bit in the R operand to participate in the priority encoding function. A ONE in the Mask operand forces the corresponding bit in the R operand to a ZERO, eliminating it from participation in the priority encoding function.

The priority encoder accepts a 16-bit input and produces a 5-bit binary-weighted code indicating the bit position of the highest priority active bit. If none of the inputs are active, the output is ZERO. In the Word mode, if input bit 15 is active, the output is 1, etc. Figure 10 lists the output as a function of the highest-priority active-bit position in both the Word and Byte mode. The N and Z bits are affected and the OVR and C bits of the status register are forced to ZERO. The only limitation in this instruction is that the operand and the mask must be different sources.

PRIORITIZE INSTRUCTION FIELD DEFINITIONS

Figure 9. Prioritize Function.