Document Number: SC900844

Rev. 2.0, 5/2011

# Integrated Power Management IC for Ultra-mobile and Embedded Applications

The 900844 is a high efficiency Power Management Integrated Circuit (PMIC) capable of providing operating voltages for Ultra-mobile platforms for Netbook, Tablets, and embedded devices through its 20 voltage rails. It has 5 switching power supplies running at frequencies from 1.0 to 4.0 MHz,14 highly efficient LDOs, and one 3.3 V power switch. It incorporates a 10-bit ADC, Real Time Clock, 8 GPIOs and 8 GPOs.

The 900844 is fully configurable and controllable through its SPI interface. It provides an optimized power management solution for ultramobile platforms used on netbooks, tablets, and slates.

Optimum partitioning, high feature integration, and state-of-the-art technology, allow Freescale to effectively serve this growing market segment.

#### **Features**

- · Main system power management integrated in a single chip

- Fully programmable DC/DC switching, low drop-out regulators, and load switches

- SPI interface (up to 25 MHz operation)

- 10-bit ADC for internal and external sensing with touch screen interface

- · Real time clock (RTC)

- · 8 Interrupt capable GPIOs and 8 GPOs

- · I/O interrupt and reset controller

# 900844

#### POWER MANAGEMENT

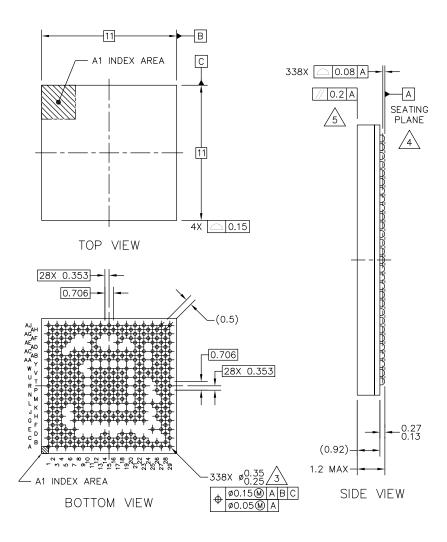

98ASA10841D 11 mm x 11 mm 338-MAPBGA

| ORDI        | ERING INFORMA                          | TION       |

|-------------|----------------------------------------|------------|

| Device      | Temperature<br>Range (T <sub>A</sub> ) | Package    |

| SC900844JVK | -40 °C to 85 °C                        | 338-MAPBGA |

#### **Applications**

- · Netbooks

- Tablet PC

- Slates

- · Embedded Devices

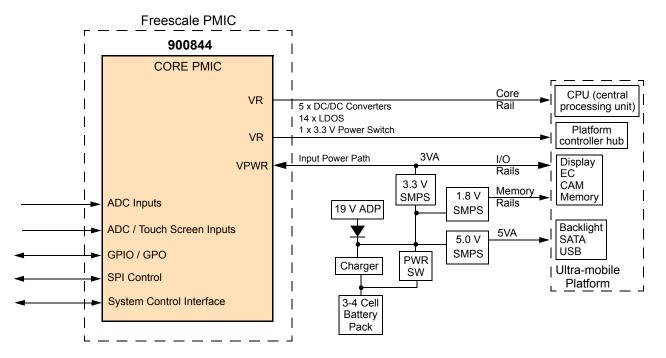

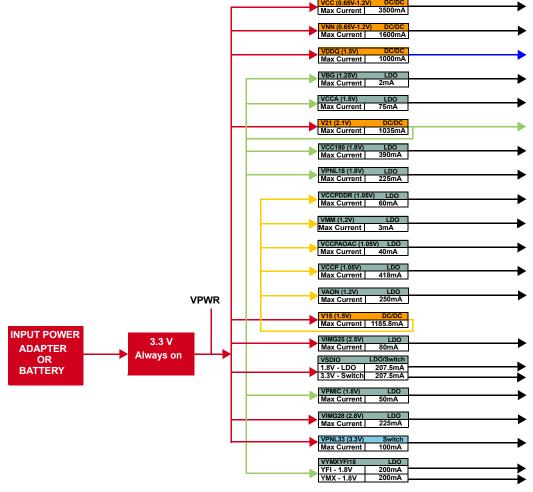

Figure 1. 900844 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product. Specifications and information herein are subject to change without notice. © Freescale Semiconductor, Inc., 2010-2011. All rights reserved.

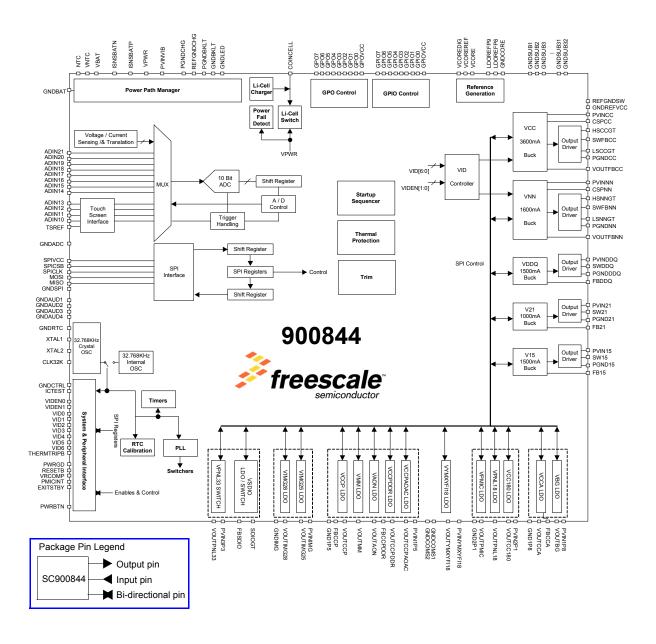

# INTERNAL BLOCK DIAGRAM

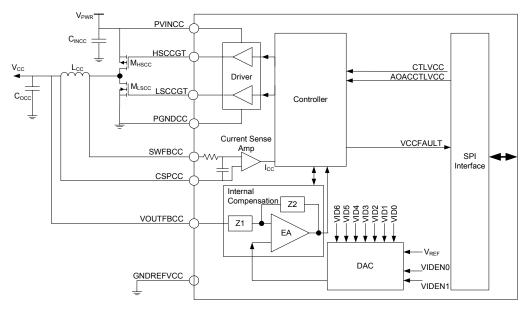

Figure 2. 900844 Internal Block Diagram

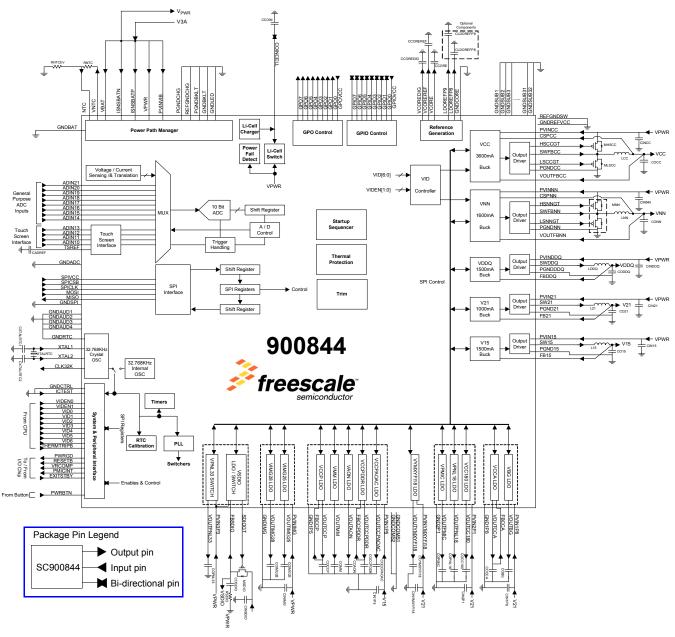

# PIN OUT DESCRIPTION AND BALL MAP

Refer to Pin Description for a detailed list of pins and ball assignments. The ball map of the package is given in Figure 3 as a top view. The BGA footprint on the application PCB will have the same mapping as given in Figure 3.

|    | 1                | 2                | 3             | 4               | 5           | 6            | 7            | 8            | 9              | 10           | 11            | 12            | 13            | 14            | 15            | 16      | 17             | 18      | 19           | 20     | 21            | 22     | 23          | 24 | 25           | 26           | 27    | 28           | 29             |

|----|------------------|------------------|---------------|-----------------|-------------|--------------|--------------|--------------|----------------|--------------|---------------|---------------|---------------|---------------|---------------|---------|----------------|---------|--------------|--------|---------------|--------|-------------|----|--------------|--------------|-------|--------------|----------------|

| Α  | NC1              |                  | NC1           |                 | PVIN1P5     |              | FBCCP        |              | NC             |              | PVIN2P1       |               | VOUTPNL<br>18 |               | SPICLK        |         | NC             |         | GNDLSP<br>R  |        | GNDLSPL       |        | NC          |    | NC           |              | NC2   |              | NC2            |

| В  |                  | NC1              |               | VOUTCC<br>PAOAC |             | LDOREFP<br>8 |              | CS           |                | VOUTPMI<br>C |               | VOUTCC<br>180 |               | VCORE         |               | PMICINT |                | VINLSPR |              | NC     |               | NC     |             | NC |              | NC           |       | NC2          |                |

| С  | NC1              |                  | VOUTCC<br>A   |                 | PVIN1P5     |              | VOUTAO<br>N  |              | VOUTCC<br>P    |              | PVIN2P1       |               | VCORER<br>EF  |               | RESETB        |         | NC             |         | VYMXPA<br>EN |        | VINLSPL       |        | NC          |    |              |              |       |              | NC2            |

| D  |                  | VOUTBG           |               | VIDEN0          |             | PVIN1P8      |              | •            |                |              |               |               |               | SPICSB        |               |         |                | NC      |              | NC     |               |        |             |    |              |              |       | NC           |                |

| E  | VID2             |                  | VID0          |                 | VIDEN1      |              | FBCCA        |              |                |              |               |               | •             |               |               |         |                |         | -            |        | •             |        |             |    | NC           |              | GNDCP |              | NC             |

| F  |                  | VID6             |               | VID4            |             |              |              |              |                |              |               |               |               |               |               |         |                |         |              |        |               |        |             |    |              |              |       | NC           |                |

| G  | CSPCC            |                  | SWFBCC        |                 |             |              | FBCCPD<br>DR |              | VOUTCC<br>PDDR |              | PWRBTN        |               | LDOREFP<br>9  |               | MOSI          |         | THERMT<br>RIPB |         | NC           |        | GNDAUD<br>4   |        | GNDAUD<br>1 |    |              |              | NC    |              | GNDAUD<br>XTAL |

| н  |                  | LSCCGT           |               | LSCCGT          |             |              |              | VID1         |                | GND1P5       |               | SCK           |               | GNDCOR<br>E   |               | VRCOMP  |                | GNDSUB  |              | NC     |               | GNDSUB |             |    |              | NC           |       | RX2          |                |

| J  | PGNDCC           |                  | PGNDCC        |                 | -           |              | VID5         |              | VID3           |              | VOUTMM        |               | VCOREDI<br>G  |               | MISO          |         | EXITSTB<br>Y   |         | GNDSUB       |        | GNDSUB        |        | GNDSUB      |    | •            |              | FS2   |              | BCL2           |

| к  |                  | HSCCGT           |               | HSCCGT          |             |              |              | VOUTFB<br>CC |                |              |               |               |               |               |               |         |                |         |              |        |               | NC     |             |    |              | NC           |       | BCL1         |                |

| L  | HSNNGT           |                  | PVINNN        |                 | PVINCC      |              | PVINCC       |              | PGNDNN         |              | GNDREF<br>VCC |               | GNDSPI        |               | SPIVCC        |         | GNDSUB         |         | GNDSUB       |        | GNDAUD<br>2   |        | RX1         |    | 12SVCC       |              | FS1   |              | NC             |

| М  |                  | LSNNGT           |               | VOUTFB<br>NN    |             | PGNDDD<br>Q  |              | PGNDDD<br>Q  |                |              |               | GND2P1        |               | GNDSUB        |               | PWRGD   |                | GNDSUB  |              |        |               | NC     |             |    |              |              |       | GNDSP        |                |

| N  | SWDDQ            |                  | SWDDQ         |                 | PGNDDD<br>Q |              | PGNDDD<br>Q  |              | SWFBNN         |              | CSPNN         |               | GND1P8        |               | GNDSUB        |         | GNDSUB         |         | GNDSUB       |        | NC            |        | NC          |    |              |              | NC    |              | NC             |

| Р  |                  | SWDDQ            |               | SWDDQ           |             | PVINDDQ      |              | PVINDDQ      |                |              |               | GNDSUB        |               | GNDSUB        |               | GNDSUB  |                | GNDSUB  |              |        |               | NC     |             |    |              | NC           |       | NC           |                |

| R  | PGNDYM<br>X3G    |                  | PGNDYM<br>X3G |                 | PVINDDQ     |              | PVINDDQ      |              | FBDDQ          |              | GNDSUB        |               | GNDSUB        |               | GNDSUB        |         | GNDSUB         |         | GNDAUD<br>3  |        | NC            |        | ICTEST      |    | •            |              | NC    |              | GNDLED         |

| Т  |                  | NC               |               | NC              |             | NC           |              | NC           |                |              |               | GNDSUB        |               | GNDSUB        |               | GNDSUB  |                | GNDSUB  |              |        |               | GNDSUB |             |    |              | NC           |       | NC           |                |

| U  | PGND21           |                  | PGND21        |                 | PGND21      |              | REFGND<br>SW |              | NC             |              | GNDSUB        |               | GNDSUB        |               | GNDSUB        |         | GNDSUB         |         | GNDSUB       |        | NC            |        | NC          |    | NC           |              | NC    |              | NC             |

| ٧  |                  | SW21             |               | SW21            |             | SW21         |              | FB21         |                |              |               | GNDSUB        |               | GNDIMG        |               | GNDADC  |                | GNDSUB  |              |        |               | NC     |             | NC |              | PGNDOT<br>G  |       | PGNDOT<br>G  |                |

| w  | PVIN21           |                  | PVIN21        |                 | PVIN21      |              | FB15         |              | -              |              | GNDCOM<br>S2  |               | NC            |               | ADIN20        |         | TSREF          |         | NC           |        | NC            |        | NC          |    | NC           |              | NC    |              | NC             |

| Υ  |                  | PGND15           |               | PGND15          |             | PGND15       |              | GPO4         |                |              |               |               |               |               |               |         |                | _       |              |        |               | NC     |             |    |              | PGNDBK<br>LT |       | PGNDBK<br>LT |                |

| AA | SW15             |                  | SW15          |                 | SW15        |              | GNDCOM<br>S1 |              | NC             |              | GPIO3         |               | NC            |               | NC            |         | ADIN13         |         | NC           |        | GNDBAT        |        | NC          |    | NC           |              | NC    |              | NC             |

| АВ |                  | PVIN15           |               | PVIN15          |             | PVIN15       |              | GPO7         |                | GPIO1        |               | SDIOGT        |               | GNDCTR<br>L   |               | ADIN11  |                | GPIO6   |              | NC     |               | NC     |             |    |              | VPWR         |       | GNDBKLT      |                |

| AC | NC               |                  | NC            |                 | _           |              | GPO1         |              | NC             |              | GPIOVCC       |               | FBSDIO        |               | ADIN21        |         | ADIN15         |         | GPIO4        |        | REFGND<br>CHG |        | NTC         |    | CHGBYP<br>GT |              | VBAT  |              | COINCEL<br>L   |

| AD |                  | PVINYMX<br>YFI18 |               | GPO2            |             |              |              |              |                |              |               | PGNDYM<br>XPA |               |               |               |         |                | _,      |              |        |               | NC     |             |    |              | ISNSBAT<br>P |       | NC           |                |

| AE | VOUTYM<br>XYFI18 |                  | NC            |                 | GPOVCC      |              |              |              |                |              | NC            |               |               |               |               |         | ADIN14         |         | _            |        | NC            |        | NC          |    | NC           |              | CHGGT |              | VNTC           |

| AF |                  | NC               |               | GP00            |             | NC           |              |              |                |              |               | PGNDYM<br>XPA |               |               |               |         |                | XTAL2   |              | GPIO5  |               | NC     |             | NC |              | PGNDCH<br>G  |       | ISNSBAT<br>N |                |

| AG | NC3              |                  | GPO3          |                 | GPO6        |              | GPI00        |              | VOUTPNL<br>33  |              | NC            |               | PVINVIB       |               | VOUTIMG<br>28 |         | ADIN16         |         | XTAL1        |        | GPIO7         |        | RAWCHG      |    | NC           |              | NC    |              | NC4            |

| АН |                  | NC3              |               | GPO5            |             | NC           |              | NC           |                | NC           |               | PGNDYM<br>XPA |               | VOUTIMG<br>25 |               | ADIN19  |                | ADIN17  |              | ADIN10 |               | CLK32K |             | NC |              | PGNDCH<br>G  |       | NC4          |                |

| AJ | NC3              |                  | NC3           |                 | NC          |              | GPIO2        |              | PVIN3P3        |              | NC            |               | NC            |               | PVINIMG       |         | ADIN18         |         | ADIN12       |        | GNDRTC        |        | NC          |    | NC           |              | NC4   |              | NC4            |

Figure 3. 900844 Package Ball Map

# **PIN DESCRIPTION**

The Type Column indicates the maximum average current through each ball assigned to the different nodes, 500 mA maximum for HIPWR, 300 mA maximum for MDPWR, and 100 mA maximum for LOPWR

Table 1. 900844 Pin Description

| Node Name | Туре     | I/O | Rating      | # of<br>Balls | BGA Location           | Pin Description                                                  |

|-----------|----------|-----|-------------|---------------|------------------------|------------------------------------------------------------------|

|           |          | VC  | C - (0.65 \ | /-1.2 V) / :  | 3.5 A VID CPU BUC      | K with External FETs                                             |

| PVINCC    | HIPWR    | -   | 4.8 V       | 2             | L5, L7                 | Gate drivers power supply input                                  |

| HSCCGT    | HIPWR    | -   | 4.8 V       | 2             | K2, K4                 | High side FET gate drive                                         |

| LSCCGT    | HIPWR    | -   | 4.8 V       | 2             | H2, H4                 | Low side FET gate drive                                          |

| PGNDCC    | HIPWRGND | -   | -           | 2             | J1, J3                 | Local ground for internal circuitry                              |

| VOUTFBCC  | SGNL     | I   | 4.8 V       | 1             | K8                     | Output voltage sensing input and negative current sense terminal |

| SWFBCC    | SGNL     | ı   | 3.6 V       | 1             | G3                     | Switch node feedback                                             |

| CSPCC     | SGNL     | ı   | 3.6 V       | 1             | G1                     | Positive current sense terminal                                  |

|           |          | VN  | N - (0.65 \ | /-1.2 V) /    | 1.6 A VID CPU BUC      | K with External FETs                                             |

| PVINNN    | HIPWR    | -   | 4.8 V       | 1             | L3                     | Gate drivers power supply input                                  |

| HSNNGT    | HIPWR    | -   | 4.8 V       | 1             | L1                     | High side FET gate drive                                         |

| LSNNGT    | HIPWR    | -   | 4.8 V       | 1             | M2                     | Low side FET gate drive                                          |

| PGNDNN    | HIPWRGND | -   | -           | 1             | L9                     | Local ground for internal circuitry                              |

| VOUTFBNN  | SGNL     | I   | 4.8 V       | 1             | M4                     | Output voltage sensing input and negative current sense terminal |

| SWFBNN    | SGNL     | I   | 3.6 V       | 1             | N9                     | Switch node feedback                                             |

| CSPNN     | SGNL     | I   | 3.6 V       | 1             | N11                    | Positive current sense terminal                                  |

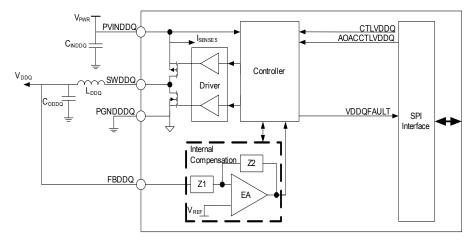

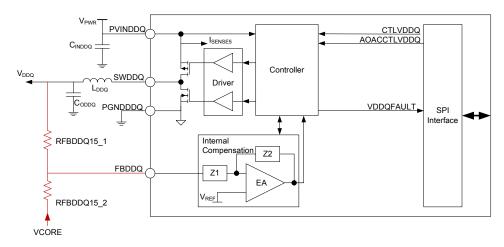

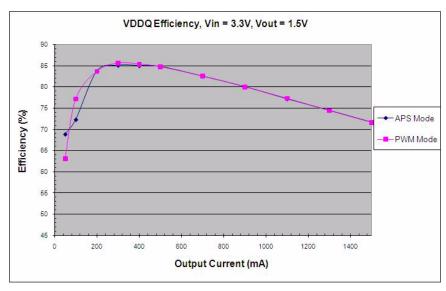

|           |          | •   |             | VDD           | Q - 1.8 V / 1.3 A BU   | ICK                                                              |

| PVINDDQ   | HIPWR    | -   | 4.8 V       | 4             | P6, P8, R5, R7         | Power supply input                                               |

| SWDDQ     | HIPWR    | -   | 4.8 V       | 4             | N1, N3, P2, P4         | Switch node                                                      |

| PGNDDDQ   | HIPWRGND | -   | -           | 4             | M6, M8, N5, N7         | Power ground                                                     |

| FBDDQ     | SGNL     | I   | 3.6 V       | 1             | R9                     | Output voltage feedback input                                    |

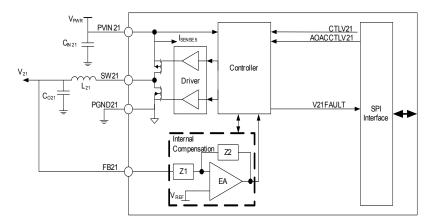

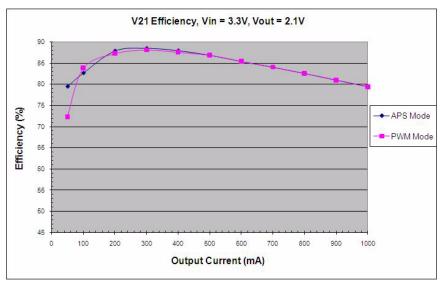

|           |          |     |             | V2            | 1 - 2.1 V / 1.0 A BUC  | ск                                                               |

| PVIN21    | HIPWR    | -   | 4.8 V       | 3             | W1, W3, W5             | Power supply input                                               |

| SW21      | HIPWR    | -   | 4.8 V       | 3             | V2, V4, V6             | Switch node                                                      |

| PGND21    | HIPWRGND | -   | -           | 3             | U1, U3, U5             | Power ground                                                     |

| FB21      | SGNL     | I   | 3.6 V       | 1             | V8                     | Output voltage feedback input                                    |

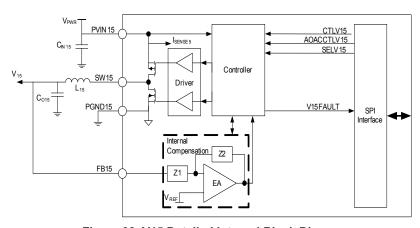

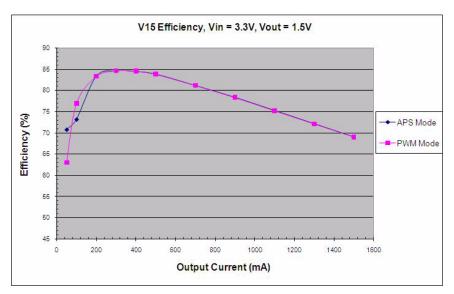

|           |          |     |             | V15 - 1.      | 5 V (or 1.6 V) / 1.5 A | BUCK                                                             |

| PVIN15    | HIPWR    | -   | 4.8 V       | 3             | AB2, AB4, AB6          | Power supply input                                               |

| SW15      | HIPWR    | -   | 4.8 V       | 3             | AA1, AA3, AA5          | Switch node                                                      |

| PGND15    | HIPWRGND | -   | -           | 3             | Y2, Y4, Y6             | Power ground                                                     |

| FB15      | SGNL     | ı   | 3.6 V       | 1             | W7                     | Output voltage feedback input                                    |

Table 1. 900844 Pin Description

| Node Name | Туре  | I/O | Rating | # of<br>Balls | BGA Location                              | Pin Description                            |

|-----------|-------|-----|--------|---------------|-------------------------------------------|--------------------------------------------|

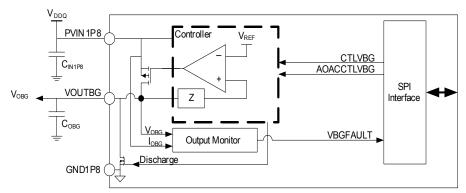

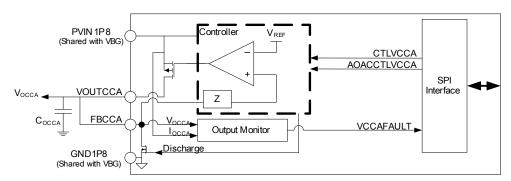

|           |       |     |        |               | G - 1.25 V/2 mA LD<br>CA - 1.5 V/150 mA L | -                                          |

| PVIN1P8   | LOPWR | -   | 3.6 V  | 1             | D6                                        | Power supply input, shared by VBG and VCCA |

| GND1P8    | GND   | -   | -      | 1             | N13                                       | Ground reference                           |

| VOUTBG    | LOPWR | -   | 2.5 V  | 1             | D2                                        | VBG output voltage node                    |

| VOUTCCA   | LOPWR | -   | 2.5 V  | 1             | C3                                        | VCCA output voltage node                   |

| FBCCA     | SGNL  | ı   | 2.5 V  | 1             | E7                                        | VCCA output voltage feedback input         |

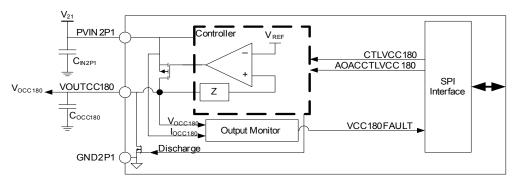

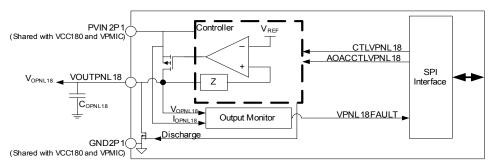

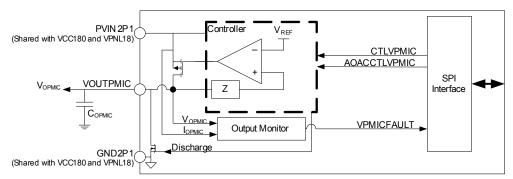

VCC180- 1.8 V/390 mA LDO VPNL18- 1.8 V/225 mA LDO VPMIC - 1.8 V/50 mA LDO

| PVIN2P1   | HIPWR | - | 3.6 V | 2 | A11, C11 | Power supply input, shared by VCC180, VPNL18, and VPMIC |

|-----------|-------|---|-------|---|----------|---------------------------------------------------------|

| GND2P1    | GND   | - | -     | 1 | M12      | Ground reference                                        |

| VOUTCC180 | HIPWR | - | 2.5 V | 1 | B12      | VCC180 output voltage node                              |

| VOUTPNL18 | MDPWR | - | 2.5 V | 1 | A13      | VPNL18 output voltage node                              |

| VOUTPMIC  | LOPWR | - | 2.5 V | 1 | B10      | VPMIC output voltage node                               |

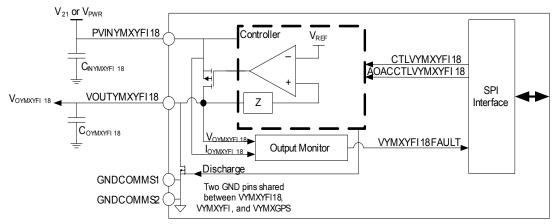

# VYMXYFI18 - (YMX:1.8 V/200 mA - YFI:1.8 V/200 mA) LDO

| PVINYMXYFI18 | MDPWR | - | 4.8 V | 1 | AD2 | Power supply input for VYMXYFI18 |

|--------------|-------|---|-------|---|-----|----------------------------------|

| VOUTYMXYFI18 | MDPWR | - | 3.6 V | 1 | AE1 | VYMXYFI18 output voltage node    |

| GNDCOMS1     | GND   | - | -     | 1 | AA7 | Ground reference                 |

| GNDCOMS2     | GND   | - | -     | 1 | W11 | Ground reference                 |

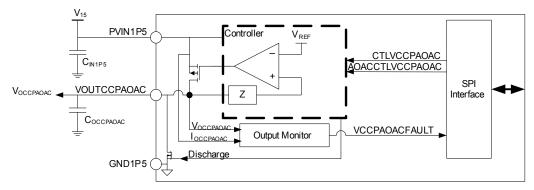

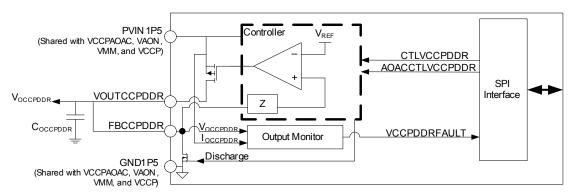

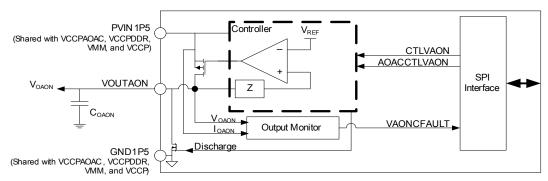

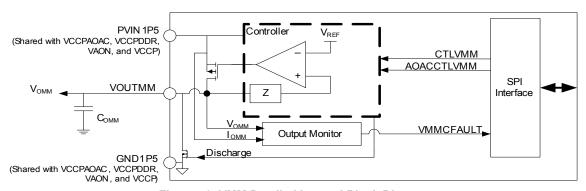

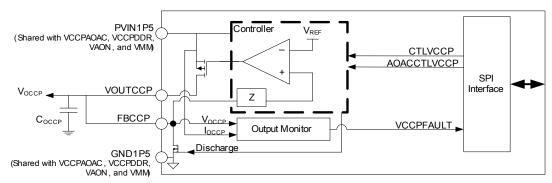

VCCPAOAC- 1.05 V/155 mA LDO VCCPDDR - 1.05 V/60 mA LDO VAON - 1.2 V/250 mA LDO VMM- 1.2 V/5 mA LDO VCCP - 1.05 V/445 mA LDO

| PVIN1P5     | HIPWR | - | 3.6 V | 2 | A5, C5 | Power supply input, shared by VCCPAOAC, VCCPDDR, VAON, VMM, and VCCP |

|-------------|-------|---|-------|---|--------|----------------------------------------------------------------------|

| GND1P5      | GND   | - | -     | 1 | H10    | Ground reference                                                     |

| VOUTCCPAOAC | LOPWR | - | 2.5 V | 1 | B4     | VCCPAOAC output voltage node                                         |

| VOUTCCPDDR  | LOPWR | - | 2.5 V | 1 | G9     | VCCPDDR output voltage node                                          |

| FBCCPDDR    | SGNL  | I | 2.5 V | 1 | G7     | VCCPDDR output voltage feedback input                                |

| VOUTAON     | MDPWR | - | 2.5 V | 1 | C7     | VAON output voltage node                                             |

| VOUTMM      | LOPWR | - | 2.5 V | 1 | J11    | VMM output voltage node                                              |

| VOUTCCP     | HIPWR | - | 2.5 V | 1 | C9     | VCCP output voltage node                                             |

| FBCCP       | SGNL  | I | 2.5 V | 1 | A7     | VCCP output voltage feedback input                                   |

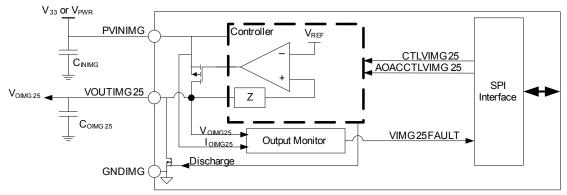

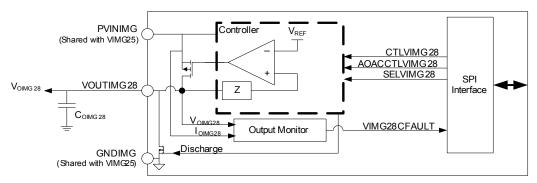

# VIMG25- 2.5 V/80 mA LDO VIMG28- 2.8 V/225 mA LDO

| PVINIMG   | MDPWR | - | 4.8 V | 1 | AJ15 | Power supply input, shared by VIMG25 and VIMG28 |

|-----------|-------|---|-------|---|------|-------------------------------------------------|

| GNDIMG    | GND   | - | -     | 1 | V14  | Ground reference                                |

| VOUTIMG25 | LOPWR | - | 3.6 V | 1 | AH14 | VIMG25 output voltage node                      |

Table 1. 900844 Pin Description

| Node Name | Туре     | I/O | Rating  | # of<br>Balls | BGA Location        | Pin Description                                                                            |

|-----------|----------|-----|---------|---------------|---------------------|--------------------------------------------------------------------------------------------|

| VOUTIMG28 | MDPWR    | -   | 3.6 V   | 1             | AG15                | VIMG28 output voltage node                                                                 |

|           |          |     |         | VPNL:         | 33 - 3.3 V/100 mA S | witch                                                                                      |

| PVIN3P3   | MDPWR    | -   | 3.6 V   | 1             | AJ9                 | Power supply input, shared by VPNL33 and VSDIO                                             |

| VOUTPNL33 | LOPWR    | -   | 3.6 V   | 1             | AG9                 | VPNL33 output voltage node                                                                 |

|           | 1        |     | VSDIO - | 3.3 V/21      | 5 mA Switch OR 1.   | 8 V/215 mA LDO                                                                             |

| SDIOGT    | LOPWR    | -   | 3.6 V   | 1             | AB12                | Gate driver output for VSDIO pass FET                                                      |

| FBSDIO    | SGNL     | -   | 3.6 V   | 1             | AC13                | Feedback node when VSDIO is in Switch mode; Output voltage node when VSDIO is in LDO mode. |

|           | 1        |     |         |               | Internal Supplies   | 1                                                                                          |

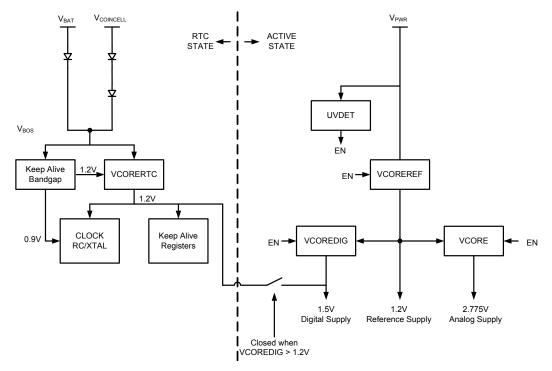

| VCORE     | LOPWR    | -   | 3.6 V   | 1             | B14                 | Internal supply output voltage node                                                        |

| VCOREDIG  | LOPWR    | -   | 1.5 V   | 1             | J13                 | Internal supply output voltage node                                                        |

| VCOREREF  | LOPWR    | -   | 3.6 V   | 1             | C13                 | Internal band gap supply output voltage node                                               |

| LDOREFP8  | LOPWR    | -   | 3.6 V   | 1             | В6                  | Internal divided down band gap supply output voltage noc dedicated for LDOs                |

| LDOREFP9  | LOPWR    | -   | 3.6 V   | 1             | G13                 | Internal divided down band gap supply output voltage noc dedicated for LDOs                |

| GNDCORE   | LOPWRGND | -   | -       | 1             | H14                 | Ground for internal supplies                                                               |

|           |          |     |         |               | Input Power Path    | 1                                                                                          |

| VPWR      | MDPWR    | -   | 4.8 V   | 1             | AB26                | Input power node for PMIC                                                                  |

| VBAT      | LOPWR    | -   | 4.8 V   | 1             | AC27                | Battery voltage sensing input                                                              |

| GNDBAT    | LOPWRGND | -   | -       | 1             | AA21                | Input supply ground                                                                        |

| VNTC      | LOPWR    | -   | 3.6 V   | 1             | AE29                | Bias voltage for NTC resistor stack                                                        |

| NTC       | SGNL     | I   | 3.6 V   | 1             | AC23                | NTC connection node                                                                        |

| ISNSBATP  | SGNL     | I   | 4.8 V   | 1             | AD26                | Connect to VBAT                                                                            |

| ISNSBATN  | SGNL     | I   | 4.8 V   | 1             | AF28                | Connect to VBAT                                                                            |

| PVINVIB   | MDPWR    | -   | 4.8 V   | 1             | AG13                | Always connect to VPWR                                                                     |

|           | •        |     |         |               | Coin Cell Charger   |                                                                                            |

| COINCELL  | LOPWR    | -   | 3.6 V   | 1             | AC29                | Coin cell supply input, coin cell charger output                                           |

|           |          |     |         |               | ADC + TS I/F        | 1                                                                                          |

| ADIN10    | SGNL     | I   | 4.8 V   | 1             | AH20                | ADC generic input 1, used as touchscreen input X1, TSX                                     |

| ADIN11    | SGNL     | I   | 4.8 V   | 1             | AB16                | ADC generic input 2, used as touchscreen input X2, TSX                                     |

| ADIN12    | SGNL     | I   | 4.8 V   | 1             | AJ19                | ADC generic input 3, used as touchscreen input Y1, TSY                                     |

| ADIN13    | SGNL     | I   | 4.8 V   | 1             | AA17                | ADC generic input 4, used as touchscreen input Y2, TSY                                     |

| ADIN14    | SGNL     | I   | 4.8 V   | 1             | AE17                | ADC generic input 5                                                                        |

| ADIN15    | SGNL     | I   | 4.8 V   | 1             | AC17                | ADC generic input 6                                                                        |

| ADIN16    | SGNL     | I   | 4.8 V   | 1             | AG17                | ADC generic input 7                                                                        |

| ADIN17    | SGNL     | ı   | 4.8 V   | 1             | AH18                | ADC generic input 8                                                                        |

Table 1. 900844 Pin Description

| Node Name | Туре     | I/O | Rating | # of<br>Balls | BGA Location | Pin Description                     |

|-----------|----------|-----|--------|---------------|--------------|-------------------------------------|

| ADIN18    | SGNL     | I   | 4.8 V  | 1             | AJ17         | ADC generic input 9                 |

| ADIN19    | SGNL     | I   | 4.8 V  | 1             | AH16         | ADC generic input 10                |

| ADIN20    | SGNL     | I   | 4.8 V  | 1             | W15          | ADC generic input 11                |

| ADIN21    | SGNL     | I   | 4.8 V  | 1             | AC15         | ADC generic input 12                |

| TSREF     | LOPWR    | -   | 3.6 V  | 1             | W17          | Reference for touchscreen interface |

| GNDADC    | LOPWRGND | -   | -      | 1             | V16          | Ground reference for ADC            |

## Oscillator and Real Time Clock - RTC

|            |      |   | (     | Oscillato | r and Real Time ( | Clock - RTC                                                                                                                                                                                                                                                                                |

|------------|------|---|-------|-----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL1      | SGNL | ı | 2.5 V | 1         | AG19              | 32.768 kHz oscillator crystal connection 1                                                                                                                                                                                                                                                 |

| XTAL2      | SGNL | 0 | 2.5 V | 1         | AF18              | 32.768 kHz oscillator crystal connection 2                                                                                                                                                                                                                                                 |

| CLK32K     | SGNL | 0 | 3.6 V | 1         | AH22              | 32 kHz clock output                                                                                                                                                                                                                                                                        |

| GNDRTC     | GND  | - | -     | 1         | AJ21              | Ground for the RTC block                                                                                                                                                                                                                                                                   |

|            |      |   | PI    | atform A  | rchitecture Sidel | band Signals                                                                                                                                                                                                                                                                               |

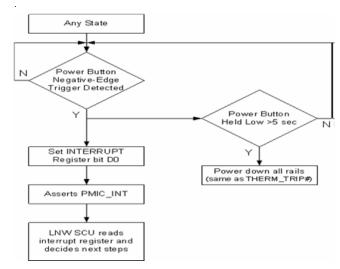

| PMICINT    | SGNL | 0 | 2.5 V | 1         | B16               | PMIC Interrupt. Asserted by PMIC to wake platform controller hub and begin communications. Level-sensitive, read to clear.                                                                                                                                                                 |

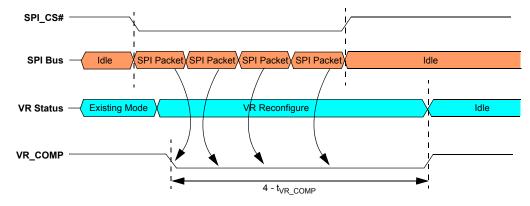

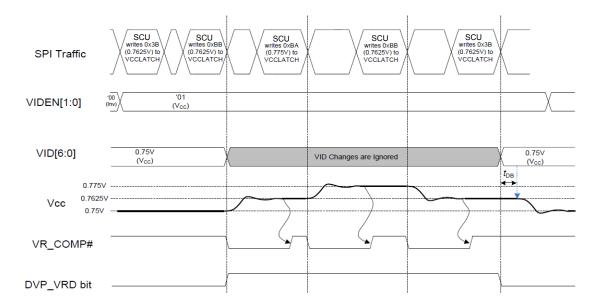

| VRCOMP     | SGNL | 0 | 2.5 V | 1         | H16               | Voltage regulator complete. Asserted high by the PMIC when a SPI voltage regulation request has been decoded. The signal is de-asserted on completion of the request (i.e. the rail is in regulation).                                                                                     |

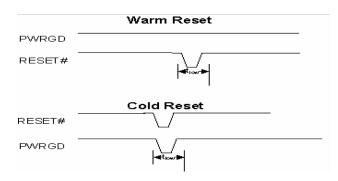

| RESETB     | SGNL | 0 | 2.5 V | 1         | C15               | Active low hard reset for platform controller hub. When asserted, the platform controller hub should return to its initial default state.                                                                                                                                                  |

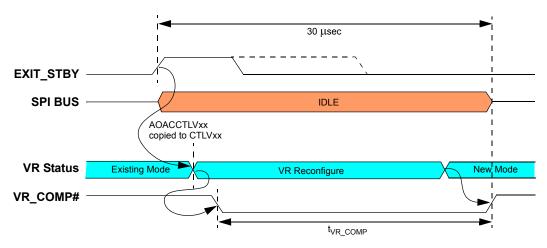

| PWRGD      | SGNL | 0 | 2.5 V | 1         | M16               | POWER GOOD: The 900844 asserts this signal to indicate that all power rails to the platform controller hub are good. Assertion of PWRGD also means that VCCA_OSC has been valid for at least 30 microseconds. The Platform Controller Hub will remain "off" until this signal is asserted. |

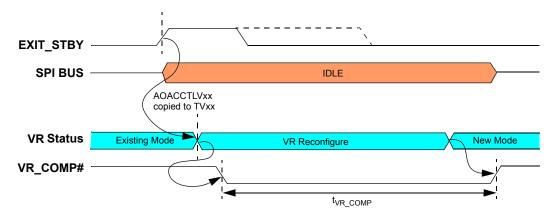

| EXITSTBY   | SGNL | I | 2.5 V | 1         | J17               | EXIT Standby. When asserted, the 900844 exits the AOAC standby settings for regulating the platform supplies. When asserted, the 900844 switches VRs on which are defined in registers 0x09 through 0x0D. This is a low latency VR context switch.                                         |

| THERMTRIPB | SGNL | I | 1.5 V | 1         | G17               | Thermal trip. Asserted by the CPU to indicate a catastrophic thermal event.                                                                                                                                                                                                                |

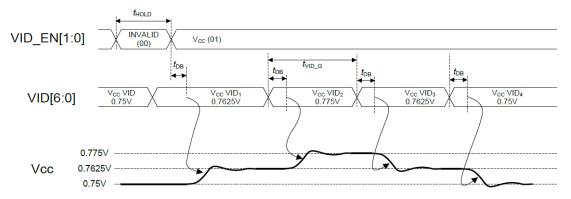

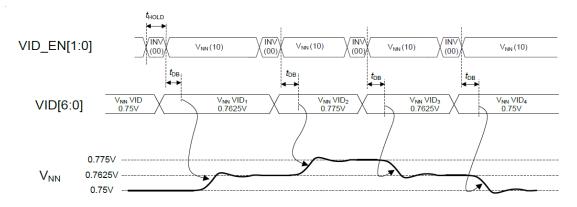

| VIDEN0     | SGNL | ı | 1.5 V | 1         | D4                | Driven by the CPU to indicate which VR the VID bus is                                                                                                                                                                                                                                      |

| VIDEN1     | SGNL | 1 | 1.5 V | 1         | E5                | addressed to (VCC or VNN). Debounced inside the 900844 for 150 ns. The CPU will hold the value for at least 300 ns.                                                                                                                                                                        |

| VID0       | SGNL | 1 | 1.5 V | 1         | E3                |                                                                                                                                                                                                                                                                                            |

| VID1       | SGNL | 1 | 1.5 V | 1         | H8                |                                                                                                                                                                                                                                                                                            |

| VID2       | SGNL | ı | 1.5 V | 1         | E1                | Driven by the CPU to indicate the output voltage setting for                                                                                                                                                                                                                               |

| VID3       | SGNL | I | 1.5 V | 1         | J9                | the VCC and VNN rails. Debounced inside the 900844 for                                                                                                                                                                                                                                     |

| VID4       | SGNL | ı | 1.5 V | 1         | F4                | 150 ns. The CPU will hold the value for at least 300 ns.                                                                                                                                                                                                                                   |

| VID5       | SGNL | I | 1.5 V | 1         | J7                |                                                                                                                                                                                                                                                                                            |

| VID6       | SGNL | I | 1.5 V | 1         | F2                |                                                                                                                                                                                                                                                                                            |

| GNDCTRL    | GND  | - | -     | 1         | AB14              | Logic Control Ground                                                                                                                                                                                                                                                                       |

Table 1. 900844 Pin Description

| Node Name | Туре  | I/O | Rating | # of<br>Balls | BGA Location       | Pin Description                                           |

|-----------|-------|-----|--------|---------------|--------------------|-----------------------------------------------------------|

|           |       |     |        |               | SPI Interface      | 1                                                         |

| SPIVCC    | LOPWR | -   | 3.6 V  | 1             | L15                | Supply for SPI Bus                                        |

| SPICLK    | SGNL  | ı   | 3.6 V  | 1             | A15                | SPI Clock Input                                           |

| MOSI      | SGNL  | ı   | 3.6 V  | 1             | G15                | SPI write input                                           |

| MISO      | SGNL  | 0   | 3.6 V  | 1             | J15                | SPI read output                                           |

| SPICSB    | SGNL  | ı   | 3.6 V  | 1             | D14                | SPI chip select input                                     |

| GNDSPI    | GND   | -   | -      | 1             | L13                | Ground for SPI interface                                  |

|           |       |     |        | GPIOs         | & GPOs & Power     | Button                                                    |

| GPIOVCC   | LOPWR | -   | 3.6 V  | 1             | AC11               | GPIO power                                                |

| GPIO0     | SGNL  | I/O | 3.6 V  | 1             | AG7                |                                                           |

| GPIO1     | SGNL  | I/O | 3.6 V  | 1             | AB10               |                                                           |

| GPIO2     | SGNL  | I/O | 3.6 V  | 1             | AJ7                |                                                           |

| GPIO3     | SGNL  | I/O | 3.6 V  | 1             | AA11               | Fully configurable GPIO inputs/outputs for general purpos |

| GPIO4     | SGNL  | I/O | 3.6 V  | 1             | AC19               | sensing and platform control                              |

| GPIO5     | SGNL  | I/O | 3.6 V  | 1             | AF20               |                                                           |

| GPIO6     | SGNL  | I/O | 3.6 V  | 1             | AB18               |                                                           |

| GPIO7     | SGNL  | I/O | 3.6 V  | 1             | AG21               |                                                           |

| GPOVCC    | LOPWR | -   | 3.6 V  | 1             | AE5                | GPO power                                                 |

| GPO0      | SGNL  | 0   | 3.6 V  | 1             | AF4                |                                                           |

| GPO1      | SGNL  | 0   | 3.6 V  | 1             | AC7                |                                                           |

| GPO2      | SGNL  | 0   | 3.6 V  | 1             | AD4                |                                                           |

| GPO3      | SGNL  | 0   | 3.6 V  | 1             | AG3                | Consent numbers subsubs                                   |

| GPO4      | SGNL  | 0   | 3.6 V  | 1             | Y8                 | General purpose outputs                                   |

| GPO5      | SGNL  | 0   | 3.6 V  | 1             | AH4                |                                                           |

| GPO6      | SGNL  | 0   | 3.6 V  | 1             | AG5                |                                                           |

| GPO7      | SGNL  | 0   | 3.6 V  | 1             | AB8                |                                                           |

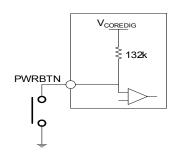

| PWRBTN    | SGNL  | ı   | 1.5 V  | 1             | G11                | PMIC hardware on/off button                               |

|           | -     |     |        |               | Test Pins          | -1                                                        |

| ICTEST    | SGNL  | I   | 7.5 V  | 1             | R23                | Always connect to GND                                     |

|           | ı     |     |        | F             | Reference Supplies | 5                                                         |

|           | MDPWR | -   | 5.5V   | 1             | B18                | Always connect to VPWR                                    |

| VINLSPR   |       |     |        |               |                    |                                                           |

| VINLSPR   | MDPWR | -   | 5.5V   | 1             | C21                | Always connect to VPWR                                    |

Table 1. 900844 Pin Description

| Node Name  | Type     | I/O | Rating | # of<br>Balls | BGA Location                                                                                                                                                        | Pin Description                                         |

|------------|----------|-----|--------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| ,          |          |     | 1      | (             | Ground References                                                                                                                                                   |                                                         |

| PGNDCHG    | HIPWRGND | -   | -      | 2             | AF26, AH26                                                                                                                                                          | Power GND                                               |

| BCL1       | SGNL     | I/O | 3.6 V  | 1             | K28                                                                                                                                                                 | Always connect to GND                                   |

| FS1        | SGNL     | I/O | 3.6 V  | 1             | L27                                                                                                                                                                 | Always connect to GND                                   |

| RX1        | SGNL     | I   | 3.6 V  | 1             | L23                                                                                                                                                                 | Always connect to GND                                   |

| BCL2       | SGNL     | I/O | 3.6 V  | 1             | J29                                                                                                                                                                 | Always connect to GND                                   |

| FS2        | SGNL     | I/O | 3.6 V  | 1             | J27                                                                                                                                                                 | Always connect to GND                                   |

| RX2        | SGNL     | I   | 3.6 V  | 1             | H28                                                                                                                                                                 | Always connect to GND                                   |

| SCK        | SGNL     | I   | 3.6 V  | 1             | H12                                                                                                                                                                 | Always connect to GND                                   |

| GNDSP      | LOPWRGND | -   | -      | 1             | M28                                                                                                                                                                 | Analog GND                                              |

| GNDLSPR    | MDPWRGND | -   | -      | 1             | A19                                                                                                                                                                 | Analog GND                                              |

| GNDLSPL    | MDPWRGND | -   | -      | 1             | A21                                                                                                                                                                 | Analog GND                                              |

| GNDCP      | LOPWRGND | -   | -      | 1             | E27                                                                                                                                                                 | Analog GND                                              |

| PGNDYMXPA  | HIPWRGND | -   | -      | 3             | AD12, AF12, AH12                                                                                                                                                    | Power GND                                               |

| PGNDYMX3G  | HIPWRGND | -   | -      | 2             | R1, R3                                                                                                                                                              | Power GND                                               |

| PGNDOTG    | HIPWRGND | -   | -      | 2             | V26, V28                                                                                                                                                            | Power GND                                               |

| PGNDBKLT   | HIPWRGND | -   | -      | 2             | Y26, Y28                                                                                                                                                            | Power GND                                               |

| GNDAUDXTAL | GND      | -   | -      | 1             | G29                                                                                                                                                                 | Analog GND                                              |

| GNDAUD1    | GND      | -   | -      | 1             | G23                                                                                                                                                                 | Analog GND                                              |

| GNDAUD2    | GND      | -   | -      | 1             | L21                                                                                                                                                                 | Analog GND                                              |

| GNDAUD3    | GND      | -   | -      | 1             | R19                                                                                                                                                                 | Analog GND                                              |

| GNDAUD4    | GND      | -   | -      | 1             | G21                                                                                                                                                                 | Analog GND                                              |

| GNDBKLT    | GND      | -   | -      | 1             | AB28                                                                                                                                                                | Analog GND                                              |

| GNDLED     | GND      | -   | -      | 1             | R29                                                                                                                                                                 | Analog GND                                              |

| REFGNDCHG  | GND      | -   | -      | 1             | AC21                                                                                                                                                                | Dedicated reference ground for the input power path     |

| REFGNDSW   | GND      | -   | -      | 1             | U7                                                                                                                                                                  | Dedicated reference ground for the switching regulators |

| GNDREFVCC  | GND      | -   | -      | 1             | L11                                                                                                                                                                 | Dedicated reference ground for VCC regulator            |

| GNDSUB     | GND      | -   | -      | 32            | H18, H22, J19,<br>J21, J23, L17, L19,<br>M14, M18, N15,<br>N17, N19, P12,<br>P14, P16, P18,<br>R11, R13, R15,<br>R17, T12, T14,<br>T16, T18, T22,<br>U11, U13, U15, | Substrate GND                                           |

|            |          |     |        |               | U17, U19, V12,<br>V18                                                                                                                                               |                                                         |

Table 1. 900844 Pin Description

| Node Name | Туре  | I/O | Rating | # of<br>Balls | BGA Location | Pin Description           |

|-----------|-------|-----|--------|---------------|--------------|---------------------------|

|           |       |     |        |               | Reserved     |                           |

| RAWCHG    | MDPWR | -   | 20 V   | 1             | AG23         | Reserved - Do not connect |

| CHGBYPGT  | MDPWR | -   | 4.8 V  | 1             | AC25         | Reserved - Do not connect |

| CHGGT     | MDPWR | -   | 4.8 V  | 1             | AE27         | Reserved - Do not connect |

| VYMXPAEN  | SGNL  | I   | 2.5 V  | 1             | C19          | Reserved - Do not connect |

| CS        | SGNL  | I   | 3.6 V  | 1             | B8           | Reserved - Do not connect |

#### Notes

The Type Column indicates the maximum average current through each ball assigned to the different nodes. 500 mA maximum for HIPWR, 300 mA maximum for MDPWR, and 100 mA maximum for LOPWR

# **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

#### Table 2. Maximum Ratings

All voltages are with respect to ground, unless otherwise noted. Exceeding these ratings may cause malfunction or permanent damage to the device. The detailed maximum voltage rating per pin can be found in the pin list section.

| Ratings                                                                                                                                                         | Symbol              | Value        | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|------|

| ELECTRICAL RATINGS                                                                                                                                              |                     | 1            | I.   |

| Input Voltage                                                                                                                                                   | -                   | -0.3 to +4.4 | V    |

| Coin Cell Voltage                                                                                                                                               | -                   | -0.3 to +3.6 | V    |

| ESD Rating, All Pins, Human Body Model (HBM) <sup>(4)</sup>                                                                                                     | V <sub>ESDHBM</sub> | ±2000        | V    |

| ESD Rating, All Pins, Charge Device Model (CDM) (4), (5)                                                                                                        | V <sub>ESDCDM</sub> | ±450         | V    |

| THERMAL RATINGS                                                                                                                                                 |                     |              |      |

| Ambient Operating Temperature Range                                                                                                                             | T <sub>A</sub>      | -40 to +85   | °C   |

| Operating Junction Temperature Range                                                                                                                            | TJ                  | -30 to +125  | °C   |

| Storage Temperature Range                                                                                                                                       | T <sub>ST</sub>     | -65 to +150  | °C   |

| Peak Package Reflow Temperature (2), (3)                                                                                                                        | T <sub>PPRT</sub>   | 260          | °C   |

| POWER RATINGS                                                                                                                                                   |                     |              |      |

| Hard Mechanical Off                                                                                                                                             |                     |              | mW   |

| There is no Valid VBAT voltage connected to the 900844, BATDET = 0                                                                                              |                     | 0            |      |

| Soft Mechanical Off                                                                                                                                             |                     |              | mW   |

| The 900844 has input power from 3.3 V Supply into VBAT. All VRs are programmed "OFF", BATDET = 1                                                                |                     | 5.0          |      |

| Power On                                                                                                                                                        |                     |              | mW   |

| The 900844 has input power from 3.3 V supply into VBAT. The cold-boot rails are "ON".                                                                           |                     |              |      |

| V21 = 2.1 V, V15 = 1.5 V, VAON = 1.2 V, VCCPAOAC = 1.05 V, VPMIC = 1.8 V, All VR outputs are set in PFM or APS mode driving purely capacitive loads. BATDET = 1 |                     | 100          |      |

#### Notes

- 2. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause a malfunction or permanent damage to the device.

- 3. Freescale's Package Reflow capability meets the Pb-free requirements for JEDEC standard J-STD-020C, for Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL)

- 4. ESD testing is performed in accordance with the Human Body Model (HBM) (CZAP = 100 pF, RZAP = 1500  $\Omega$ ), and the Charge Device Model (CDM), Robotic (CZAP = 4.0 pF).

- 5. All pins meet 500 V CDM except VCOREREF.

# ELECTRICAL CHARACTERISTICS MAXIMUM RATINGS

#### POWER DISSIPATION

During operation, the temperature of the die must not exceed the maximum junction temperature. Depending on the operating ambient temperature and the total internal dissipation this limit can be exceeded.

To optimize the thermal management scheme and avoid overheating, the 900844 provides a thermal management system that protects against overheating. This protection should be considered as a fail-safe mechanism, and the application design should initiate thermal shutdown under normal conditions. Reference Thermal Management for more details.

#### POWER CONSUMPTION

<u>Table 2</u> defines the maximum power consumption specifications in the various system and device states. For each entry in the table, the component is assumed to be configured for driving purely capacitive loads, and the voltages listed in each entry are nominal output voltages.

Note that the "Soft Mechanical Off" state is a transitional state. The device will spend less than 150  $\mu$ s in this state before V15 starts to turn on, upon detection of a valid input voltage.

# STATIC ELECTRICAL CHARACTERISTICS

# **Table 3. Static Electrical Characteristics**

$T_A$  = -40 to 85 °C,  $V_{PWR}$  = 3.0 to 4.4 V, in gathering these parametrics, Freescale used the external components described in the Hardware Design Considerations section of this document, over the full load current range, unless otherwise noted. Typical values are characterized at  $V_{PWR}$  = 3.6 V and 25 °C.

| Characteristic                                                                                                           | Symbol          | Min                                            | Тур | Max                                            | Unit |

|--------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------|-----|------------------------------------------------|------|

| SYSTEM CONTROL INTERFACE                                                                                                 |                 | L                                              |     | <u> </u>                                       |      |

| Input Low Voltage  EXITSTBY, VID[6:0]  THRMTRIPB, VIDEN[1:0]                                                             | V <sub>IL</sub> | 0                                              | -   | 0.3*V <sub>CCP</sub> 0.3*V <sub>CCPA</sub> OAC | V    |

| Input High Voltage EXITSTBY, VID[6:0] THRMTRIPB, VIDEN[1:0]                                                              | V <sub>IH</sub> | 0.7*V <sub>CCP</sub> 0.7*V <sub>CCPA</sub> OAC | -   | V <sub>CCP</sub><br>V <sub>CCPAOAC</sub>       | V    |

| Output Low Voltage PMICINT, VRCOMP, RESETB, PWRGD.                                                                       | V <sub>OL</sub> | 0                                              | -   | 0.1                                            | V    |

| Output High Voltage PMICINT, VRCOMP, RESETB, PWRGD.                                                                      | V <sub>OH</sub> | V <sub>PMIC</sub> - 0.1                        | -   | V <sub>PMIC</sub>                              | V    |

| SPI INTERFACE LOGIC IO                                                                                                   |                 |                                                |     |                                                |      |

| Operating Voltage Range (SPIVCC Pin)                                                                                     | $V_{SPIVCC}$    | 1.74                                           | 1.8 | 3.1                                            | V    |

| Input High SPICSB, MOSI, SPICLK                                                                                          | -               | 0.7*<br>V <sub>SPIVCC</sub>                    | -   | V <sub>SPIVCC</sub><br>+0.3                    | V    |

| Input Low SPICSB, MOSI, SPICLK                                                                                           | -               | 0                                              | -   | 0.3*<br>V <sub>SPIVCC</sub>                    | V    |

| Output Low MISO (Output sink 100 μA)                                                                                     | -               | 0                                              | -   | 0.1                                            | V    |

| Output High MISO (Output source 100 μA)                                                                                  | -               | V <sub>SPIVCC</sub><br>-0.1                    | -   | V <sub>SPIVCC</sub>                            | V    |

| DSCILLATOR AND CLOCK OUTPUTS MAIN CHARACTERISTICS                                                                        |                 | - 1                                            |     |                                                |      |

| Operating Voltage                                                                                                        | -               | 1.2                                            | -   | 1.5                                            | V    |

| RTC OSC Consumption Current (RTC Mode: All blocks disabled, no main battery attached, coin cell is attached to COINCELL) | -               | -                                              | 1.0 | 2.0                                            | μΑ   |

| Output Low CLK32K (Output sink 100 μA)                                                                                   | -               | 0                                              | -   | 0.1                                            | V    |

| Output High CLK32K (Output source 100 μA)                                                                                | -               | V <sub>SPIVCC</sub> - 0.1                      | -   | V <sub>SPIVCC</sub>                            | V    |

| CLK32K Output Duty Cycle                                                                                                 | -               | 40                                             | 50  | 60                                             | %    |

| RTC                                                                                                                      |                 | •                                              |     |                                                |      |

| Input Voltage Range                                                                                                      | -               | 1.2                                            | -   | 1.5                                            | V    |

| Consumption Current                                                                                                      | -               | -                                              | 15  | 25                                             | μA   |

| Crystal OSC Frequency Tolerance                                                                                          | -               | -30                                            | -   | +30                                            | ppm  |

| Crystal OSC Peak Temperature Frequency (Turn Over Temperature)                                                           | -               | 20                                             | 25  | 30                                             | °C   |

| Crystal OSC Maximum Series Resistance                                                                                    | -               | -                                              | 80  | -                                              | ΚΩ   |

| Crystal OSC Maximum Drive Level                                                                                          | -               | -                                              | 0.5 | -                                              | μW   |

| Characteristic                                                                                                          | Symbol                | Min  | Тур  | Max | Unit     |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|-----|----------|

| Crystal OSC Operating Drive Level                                                                                       | -                     | 0.25 | -    | 0.5 | μW       |

| Crystal OSC Nominal Lead Capacitance                                                                                    | -                     | -    | 9.0  | -   | pF       |

| Crystal OSC Aging                                                                                                       | -                     | -    | -    | 3.0 | ppm/year |

| COIN CELL CHARGER                                                                                                       | •                     |      | •    |     | 1        |

| Coin cell Charge Voltage (Selectable through VCOIN[2:0] bits)                                                           | V <sub>COINCELL</sub> | 2.5  | -    | 3.3 | V        |

| Coin cell Charge Voltage Accuracy                                                                                       | -                     | -100 | -    | 100 | mV       |

| Coin cell Charge Current                                                                                                | I <sub>COIN</sub>     | -    | 60   | -   | μΑ       |

| Coin cell Charge Current Accuracy                                                                                       | -                     | -15  | -    | 15  | %        |

| POWER STATES DETECTION THRESHOLDS                                                                                       | 1                     |      | I.   |     | 1        |

| Battery Cutoff Threshold (Depending on Battery Model)                                                                   | V <sub>BATOFF</sub>   | 2.2  | -    | 2.4 | V        |

| Coin Cell Disconnect Threshold                                                                                          | V <sub>COINOFF</sub>  | 1.8  | -    | 2.0 | V        |

| Low Battery Threshold                                                                                                   | V <sub>LOWBAT</sub>   | 3.2  | -    | -   | V        |

| Valid Battery Threshold                                                                                                 | $V_{TRKL}$            | -    | 3.0  | -   | V        |

| VPWR Rising Under-voltage Threshold                                                                                     | V <sub>PWRUVR</sub>   | -    | 3.1  | -   | V        |

| VPWR Falling Under-voltage Threshold                                                                                    | V <sub>PWRUVF</sub>   | -    | 2.55 | -   | V        |

| VCC ELECTRICAL CHARACTERISTICS                                                                                          |                       | 1    | I.   |     | l        |

| Input Voltage Range                                                                                                     | V <sub>PWR</sub>      | 3.0  | 3.6  | 4.4 | V        |

| Extended Input Voltage Range                                                                                            | V <sub>PWR</sub>      | 2.8  | 3.6  | 4.7 | V        |

| Output Voltage Programmability Range                                                                                    | V <sub>CC</sub>       |      |      |     | V        |

| Low Power Mode                                                                                                          |                       | 0.3  | -    | 0.7 |          |

| Active Mode                                                                                                             |                       | 0.65 | -    | 1.2 |          |

| Output Voltage Programmability Step Size                                                                                | -                     | -    | 12.5 | -   | mV       |

| Output Voltage Accuracy                                                                                                 | -                     |      |      |     | %        |

| $0.6 \text{ V} < \text{V}_{\text{CC}} < 12 \text{ V}, 1.5 \text{ A} < \text{I}_{\text{CC}} < 3.5 \text{ A}$             |                       | -5.0 | -    | 5.0 |          |

| $0.6 \text{ V} < \text{V}_{\text{CC}} < 12 \text{ V}, \text{I}_{\text{CC}} < 1.5 \text{ A}$                             |                       | -4.0 | -    | 4.0 |          |

| $0.3 \text{ V} < \text{V}_{CC} < 0.6 \text{ V}$                                                                         |                       | -7.0 | -    | 7.0 |          |

| Output Voltage Overshoot                                                                                                | V <sub>OS</sub>       |      |      |     | mV       |

| Maximum overshoot voltage above VID setting voltage. Maximum overshoot time is 10-30 s, output voltage = 0.9 V at 50 mA |                       | -    | -    | 50  |          |

| Continuous Output Load Current                                                                                          |                       |      |      |     | Α        |

| Low Power mode                                                                                                          | I <sub>CC</sub>       | -    | -    | 0.2 |          |

| Active Mode                                                                                                             |                       | 0.2  | -    | 3.5 |          |

| Peak Current Limit                                                                                                      | I <sub>LIMCC</sub>    | -    | 5.0  | -   | Α        |

| Output Current Limit Accuracy                                                                                           | -                     |      | ±15  | -   | %        |

| Transient Load Change                                                                                                   | Δl <sub>CC</sub>      |      |      |     | Α        |

| Low Power Mode                                                                                                          |                       | -    | -    | 0.2 |          |

| Active Mode                                                                                                             |                       | _    | -    | 1.2 |          |

$T_A$  = -40 to 85 °C,  $V_{PWR}$  = 3.0 to 4.4 V, in gathering these parametrics, Freescale used the external components described in the Hardware Design Considerations section of this document, over the full load current range, unless otherwise noted. Typical values are characterized at  $V_{PWR}$  = 3.6 V and 25 °C.

| Characteristic                                                                                                                                 | Symbol              | Min        | Тур  | Max        | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|------|------------|------|

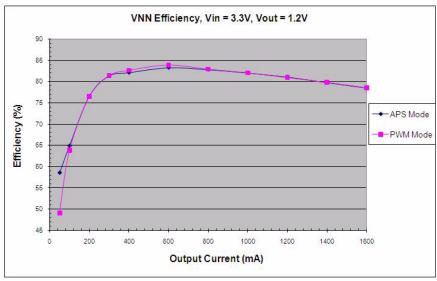

| VNN ELECTRICAL CHARACTERISTICS                                                                                                                 |                     | •          |      | •          | •    |

| Input Voltage Range                                                                                                                            | $V_{PWR}$           | 3.0        | 3.6  | 4.4        | V    |

| Extended Input Voltage Range                                                                                                                   | $V_{PWR}$           | 2.8        | 3.6  | 4.7        | ٧    |

| Output Voltage Programmability Range (Set by VID Control Signals)                                                                              | V <sub>NN</sub>     | 0.65       | -    | 1.2        | V    |

| Output Voltage Programmability Step Size                                                                                                       | -                   | -          | 12.5 | -          | mV   |

| Output Voltage Accuracy                                                                                                                        | -                   | -5.0       | -    | 5.0        | %    |

| Output Voltage Overshoot  Maximum overshoot voltage above VID setting voltage. Maximum overshoot time is 10 s, output voltage = 0.9 V at 50 mA | V <sub>OS</sub>     | -          | -    | 50         | mV   |

| Continuous Output Load Current Low Power Mode Active Mode                                                                                      | I <sub>NN</sub>     | - 0.2      |      | 0.2<br>1.6 | А    |

| Peak Current Limit                                                                                                                             | I <sub>LIMNN</sub>  | -          | 2.5  | -          | Α    |

| Output Current Limit Accuracy                                                                                                                  | -                   | -          | ±20  | -          | %    |

| Transient Load Change                                                                                                                          | Δl <sub>NN</sub>    | -          | -    | 0.5        | Α    |