# Cascadable 4K x 9 FIFO

### **Features**

- 4096 x 9 FIFO buffer memory

- Dual-port RAM cell

- Asynchronous read/write

- High-speed 28.5-MHz read/write independent of depth/width

- 25-ns access time

- Low operating power

- $-I_{CC}$  (max.) = 142 mA commercial

- $-I_{CC}$  (max.) = 155 mA military

- · Half Full flag in standalone

- **Empty and Full flags**

- Expandable in width and depth

- Retransmit in standalone

- Parallel cascade minimizes bubble-through

- $5V \pm 10\%$  supply

- 300-mil DIP packaging

- 300-mil SOJ packaging

- TTL compatible

- Three-state outputs

- Pin compatible and functionally equivalent to IDT7204

## **Functional Description**

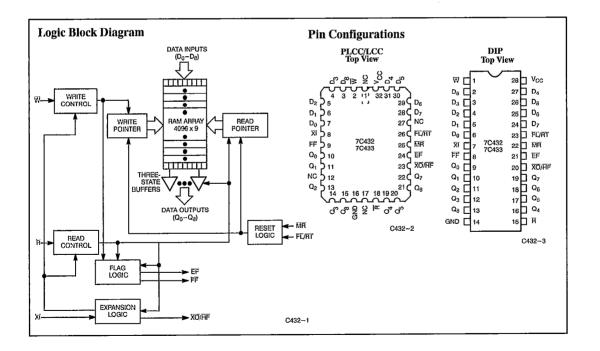

The CY7C432 and CY7C433 are first-in first-out (FIFO) memories offered in 600-mil-wide and 300-mil-wide packages. respectively. They are 4096 words by 9 bits wide. Each FIFO memory is organized so that the data is read in the same sequential order that it was written. Full and Empty flags are provided to prevent overrun and underrun. Three additional pins are also provided to facilitate unlimited expansion in width, depth, or both. The depth expansion technique steers the control signals from one device to another in parallel, thus eliminating the serial addition of propagation delays so that throughput is not reduced. Data is steered in a similar manner. The read and write operations may be asynchronous; each can occur at a rate of 28.5 MHz. The write operation occurs

when the write  $(\overline{W})$  signal is LOW. Read occurs when read (R) goes LOW. The 9 data outputs go to the high-impedance state when R is HIGH.

A Half Full (HF) output flag is provided that is valid in the standalone and width expansion configurations. In the depth expansion configuration, this pin provides the expansion out  $(\overline{XO})$  information that is used to tell the next FIFO that it will be activated.

In the standalone and width expansion configurations, a LOW on the retransmit (RT) input causes the FIFOs to retransmit the data. Read enable (R) and write enable (W) must both be HIGH during a retransmit cycle, and then  $\overline{R}$  is used to access the

The CY7C432 and CY7C433 are fabricated using advanced 0.8-micron N-well CMOS technology. Input ESD protection is greater than 2000V and latch-up is prevented by careful layout, guard rings, and a substrate bias generator.

## **Selection Guide**

**Maximum Ratings**

|                   |                     | 7C432-25<br>7C433-25 | 7C432-30<br>7C433-30 | 7C432-40<br>7C433-40 | 7C432-65<br>7C433-65 |

|-------------------|---------------------|----------------------|----------------------|----------------------|----------------------|

| Frequency (MHz)   | 28.5                | 25                   | 20                   | 12.5                 |                      |

| Access Time (ns)  | 25                  | 30                   | 40                   | 65                   |                      |

| Maximum Operating | Commercial          | 142                  | 135                  | 125                  | 110                  |

| Current (mA)      | Military/Industrial |                      | 155                  | 145                  | 130                  |

| (Above which the useful life may be impaire not tested.) | d. For user guidelines |

|----------------------------------------------------------|------------------------|

| Storage Temperature                                      | 65°C to +150°C         |

| Ambient Temperature with Power Applied                   | . – 55°C to +125°C     |

| Supply Voltage to Ground Potential                       | 0.5V to +7.0V          |

| DC Voltage Applied to Outputs                            | 0.871                  |

in High Z State ..... - 0.5V to +7.0V DC Input Voltage ...... - 3.0V to +7.0V Power Dissipation . . . . . . . . . . . . . . . . . 0.88W Static Discharge Voltage ...... (per MIL-STD-883, Method 3015)

# **Operating Range**

| Range                   | Ambient<br>Temperature | $\mathbf{v}_{\mathbf{cc}}$ |

|-------------------------|------------------------|----------------------------|

| Commercial              | 0°C to +70°C           | 5V ± 10%                   |

| Industrial              | - 40°C to +85°C        | 5V ± 10%                   |

| Military <sup>[1]</sup> | - 55°C to +125°C       | 5V ± 10%                   |

# Electrical Characteristics Over the Operating Range<sup>[2]</sup>

|                  |                                                    | Test Conditions                                   |                        |      | 2-25<br>3-25 |      | 2-30<br>3-30    |      |

|------------------|----------------------------------------------------|---------------------------------------------------|------------------------|------|--------------|------|-----------------|------|

| Parameter        | Description                                        |                                                   |                        | Min. | Max.         | Min. | Max.            | Unit |

| V <sub>OH</sub>  | Output HIGH Voltage                                | $V_{CC} = Min., I_{OH} = -2.0$                    | mA                     | 2.4  |              | 24   |                 | v    |

| V <sub>OL</sub>  | Output LOW Voltage                                 | $V_{CC}$ = Min., $I_{OL}$ = 8.0 m                 | A                      |      | 0.4          |      | 0.4             | v    |

| $V_{lH}$         | Input HIGH Voltage                                 |                                                   | Com'l                  | 2.0  | $v_{cc}$     | 2.0  | V <sub>CC</sub> | v    |

|                  |                                                    |                                                   | Mil/Ind                |      |              | 2.2  | V <sub>CC</sub> | 1    |

| V <sub>IL</sub>  | Input LOW Voltage                                  |                                                   | •                      | -3.0 | 0.8          | -3.0 | 0.8             | v    |

| $I_{IX}$         | Input Leakage Current                              | $GND \le V_I \le V_{CC}$                          |                        | -10  | +10          | -10  | +10             | μA   |

| I <sub>OZ</sub>  | Output Leakage Current                             | $\overline{R} \ge V_{IH}, GND \le V_O \le V_{CC}$ |                        | - 10 | +10          | -10  | +10             | μА   |

| $I_{CC}$         | Operating Current                                  | V <sub>CC</sub> = Max.                            | Com'l[3]               |      | 140          |      | 135             | mA   |

|                  |                                                    | $I_{OUT} = 0 \text{ mA}$                          | Mil/Ind <sup>[4]</sup> |      |              |      | 155             | 1    |

| I <sub>SB1</sub> | Standby Current                                    | All Inputs = V <sub>IH</sub> Min,                 | Com'l                  | _    | 25           |      | 25              | mA   |

|                  |                                                    |                                                   | Mil/Ind                |      |              |      | 30              | 1    |

| I <sub>SB2</sub> | Power-Down Current All Inputs $\geq V_{CC} - 0.2V$ |                                                   | Com'l                  |      | 20           |      | 20              | mA   |

|                  |                                                    |                                                   | Mil/Ind                |      | -            |      | 25              | 1    |

| I <sub>OS</sub>  | Output Short<br>Circuit Current <sup>[5]</sup>     | $V_{CC} = Max., V_{OUT} = GN$                     | D O                    |      | -90          |      | -90             | mA   |

#### Notes:

- 1. TA is the "instant on" case temperature.

- See the last page of this specification for Group A subgroup testing information.

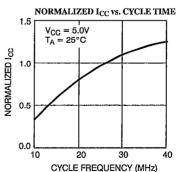

- $I_{CC}$  (commercial) = 110 mA + [( $\overline{f}$  12.5) 2 mA/MHz] for  $\overline{f} \ge$  12.5 MHz

- where  $\bar{f}$  = the larger of the write or read operating frequency.

- $I_{CC}$  (military) = 130 mA + [( $\bar{f}$  12.5) 2 mA/MHz] for  $\bar{f} \geq$  12.5 MHz

- where  $\tilde{f}$  = the larger of the write or read operating frequency.

- For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.

# Electrical Characteristics Over the Operating Range<sup>[2]</sup> (continued)

|                   |                                                |                                                  |                                                   |       | 32-40<br>33-40 | 77C4<br>77C4 | 32-65<br>33-65  |      |

|-------------------|------------------------------------------------|--------------------------------------------------|---------------------------------------------------|-------|----------------|--------------|-----------------|------|

| Parameter         | Description                                    | Test Conditions                                  | Test Conditions                                   |       | Max.           | Min.         | Max.            | Unit |

| $V_{\mathrm{OH}}$ | Output HIGH Voltage                            | $V_{CC} = Min., I_{OH} = -2m$                    | A                                                 | 2.4   |                | 24           |                 | V    |

| V <sub>OI</sub> , | Output LOW Voltage                             | $V_{CC} = Min., I_{OL} = 8.0 m$                  | A                                                 |       | 0.4            |              | 0.4             | V    |

| VIII              | Input HIGH Voltage                             |                                                  | Com'l                                             | 2.0   | $V_{CC}$       | 2.0          | $v_{cc}$        | V    |

|                   |                                                |                                                  | Mil/Ind                                           | 2.2   | $V_{CC}$       | 2.2          | V <sub>CC</sub> | V    |

| V <sub>II</sub> , | Input LOW Voltage                              |                                                  |                                                   | - 3.0 | 0.8            | -3.0         | 0.8             | V    |

| I <sub>IX</sub>   | Input Leakage Current                          | $GND \le V_I \le V_{CC}$                         |                                                   | -10   | +10            | ~10          | +10             | μА   |

| $I_{OZ}$          | Output Leakage Current                         | $\overline{R} \ge V_{IH}, GND \le V_O \le Y_{O}$ | $\overline{R} \ge V_{IH}, GND \le V_O \le V_{CC}$ |       | +10            | - 10         | +10             | μΑ   |

| $I_{CC}$          | Operating Current                              | $V_{CC} = Max.,$                                 | Com'l[3]                                          |       | 125            |              | 110             | mA   |

|                   |                                                | $I_{OUT} = 0 \text{ mA}$                         | Mil/Ind <sup>[4]</sup>                            | ····  | 145            |              | 130             |      |

| I <sub>SB1</sub>  | Standby Current                                | All Inputs = $V_{IH}$ Min.                       | Com'l                                             |       | 25             |              | 25              | mA   |

|                   |                                                |                                                  | Mil/Ind                                           |       | 30             |              | 30              | 1    |

| I <sub>SB2</sub>  | Power-Down Current                             | All Inputs $\geq$ V <sub>CC</sub> $-$ 0.2V       | Com'l                                             |       | 20             |              | 20              | mA   |

|                   |                                                |                                                  | Mil/Ind                                           |       | 25             |              | 25              |      |

| I <sub>OS</sub>   | Output Short Circuit<br>Current <sup>[5]</sup> | $V_{CC} = Max., V_{OUT} = GN$                    | $V_{CC} = Max., V_{OUT} = GND$                    |       | - 90           |              | <b>–</b> 90     | mA   |

# Capacitance<sup>[6]</sup>

| Parameter        | Description        | Test Conditions                         | Max. | Unit |

|------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 8    | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 4.5V$                         | 10   | pF   |

## Note:

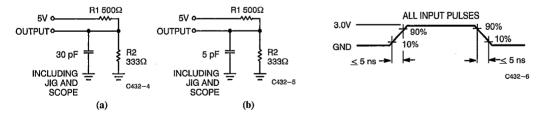

## **AC Test Loads and Waveforms**

Equivalent to:

THÉVENIN EQUIVALENT

0UTPUT • 200Ω 2V

<sup>6.</sup> Tested initially and after any design or process changes that may affect these parameters.

Switching Characteristics Over the Operating Range<sup>[7,8]</sup>

| -                              |                                           |      | 2-25<br>3-25 |              | 2-30<br>3-30 |             | 2-40<br>3-40 |             | 2-65<br>3-65 |      |

|--------------------------------|-------------------------------------------|------|--------------|--------------|--------------|-------------|--------------|-------------|--------------|------|

| Parameter                      | Description                               | Min. | Max.         | Min.         | Max.         | Min.        | Max.         | Min.        | Max.         | Unit |

| t <sub>RC</sub>                | Read Cycle Time                           | 35   |              | 40           |              | 50          |              | 80          |              | ns   |

| t <sub>A</sub>                 | Access Time                               |      | 25           |              | 30           |             | 40           |             | 65           | ns   |

| t <sub>RR</sub>                | Read Recovery Time                        | 10   |              | 10           |              | 10          |              | 15          |              | ns   |

| t <sub>PR</sub>                | Read Pulse Width                          | 25   |              | 30           |              | 40          |              | 65          |              | ns   |

| t <sub>LZR<sup>[9]</sup></sub> | Read LOW to Low Z                         | 3    |              | 3            |              | 3           |              | 3           |              | ns   |

| t <sub>DVR</sub> [9,10]        | Read HIGH to Data Valid                   | 3    |              | 3            |              | 3           |              | 3           |              | ns   |

| t <sub>HZR</sub> [9,10]        | Read HIGH to High Z                       |      | 18           |              | 20           |             | 25           |             | 30           | ns   |

| twc                            | Write Cycle Time                          | 35   |              | 40           |              | 50          |              | 80          |              | ns   |

| t <sub>PW</sub>                | Write Pulse Width                         | 25   |              | 30           | <u> </u>     | 40          |              | 65          |              | ns   |

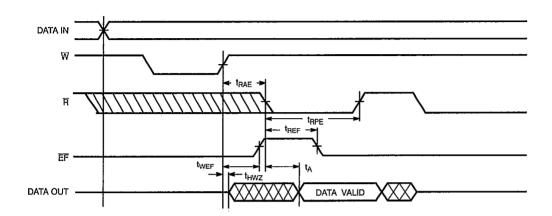

| t <sub>HWZ</sub> [9]           | Write HIGH to Low Z                       | 10   |              | 10           |              | 10          |              | 10          |              | ns   |

| twR                            | Write Recovery Time                       | 10   |              | 10           |              | 10          |              | 15          |              | ns   |

| t <sub>SD</sub>                | Data Set-Up Time                          | 15   |              | 18           |              | 20          |              | 30          |              | ns   |

| t <sub>HD</sub>                | Data Hold Time                            | 0    |              | 0            |              | 0           | -            | 10          |              | ns   |

| t <sub>MRSC</sub>              | MR Cycle Time                             | 35   |              | 40           |              | 50          |              | 80          | -            | ns   |

| t <sub>PMR</sub>               | MR Pulse Width                            | 25   |              | 30           |              | 40          |              | 65          |              | ns   |

| t <sub>RMR</sub>               | MR Recovery Time                          | 10   |              | 10           |              | 10          | <u> </u>     | 15          |              | ns   |

| t <sub>RPW</sub>               | Read HIGH to MR HIGH                      | 25   |              | 30           |              | 40          |              | 65          |              | ns   |

| twpw                           | Write HIGH to MR HIGH                     | 25   |              | 30           |              | 40          | <u> </u>     | 65          |              | ns   |

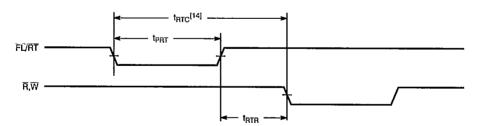

| t <sub>RTC</sub>               | Retransmit Cycle Time                     | 35   |              | 40           |              | 50          |              | 80          |              | ns   |

| tPRT                           | Retransmit Pulse Width                    | 25   |              | 30           |              | 40          |              | 65          | _            | ns   |

| t <sub>RTR</sub>               | Retransmit Recovery Time                  | 10   |              | 10           |              | 10          |              | 15          |              | ns   |

| t <sub>EFL</sub>               | MR to EF LOW                              |      | 35           |              | 40           | -           | 50           |             | 80           | ns   |

| t <sub>HFH</sub>               | MR to HF HIGH                             |      | 35           |              | 40           |             | 50           | <del></del> | 80           | ns   |

| t <sub>FFH</sub>               | MR to FF HIGH                             |      | 35           |              | 40           |             | 50           | <u> </u>    | 80           | ns   |

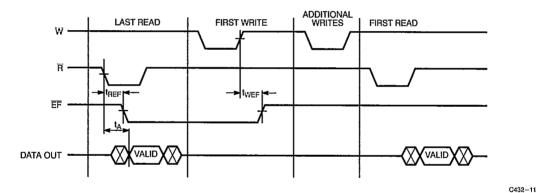

| t <sub>REF</sub>               | Read LOW to EF LOW                        |      | 25           |              | 30           |             | 35           |             | 60           | ns   |

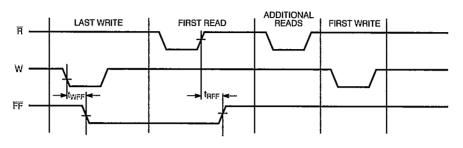

| t <sub>RFF</sub>               | Read HIGH to FF HIGH                      |      | 25           | <u> </u>     | 30           |             | 35           |             | 60           | ns   |

| tweF                           | Write HIGH to EF HIGH                     |      | 25           |              | 30           |             | 35           |             | 60           | ns   |

| twff                           | Write LOW to FF LOW                       |      | 25           |              | 30           |             | 35           |             | 60           | ns   |

| t <sub>WHF</sub>               | Write LOW to HF LOW                       |      | 35           |              | 40           |             | 50           |             | 80           | ns   |

| t <sub>RHF</sub>               | Read HIGH to HF HIGH                      |      | 35           |              | 40           |             | 50           |             | 80           | ns   |

| t <sub>RAE</sub>               | Effective Read from Write HIGH            |      | 25           |              | 30           |             | 35           |             | 60           | ns   |

| t <sub>RPE</sub>               | Effective Read Pulse Width after EF HIGH  | 25   |              | 30           |              | 40          |              | 65          |              | ns   |

| twaF                           | Effective Write from Read HIGH            |      | 25           |              | 30           | <b></b> -   | 35           |             | 60           | ns   |

| t <sub>WPF</sub>               | Effective Write Pulse Width after FF HIGH | 25   |              | 30           |              | 40          |              | 65          |              | ns   |

| t <sub>XOL</sub>               | Expansion Out LOW Delay from Clock        |      | 25           |              | 30           | l —         | 40           |             | 65           | ns   |

| t <sub>XOH</sub>               | Expansion Out HIGH Delay from Clock       |      | 25           | <del> </del> | 30           | <b>├</b> ─~ | 40           |             | 65           | ns   |

#### Notes

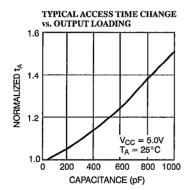

Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V and output loading of the specified I<sub>OL</sub>/I<sub>OH</sub> and 30-pF load capacitance, as in part (a) of AC Test Loads, unless otherwise specified.

See the last page of this specification for Group A subgroup testing information.

t<sub>HZR</sub> transition is measured at +500 mV from V<sub>OL</sub> and -500 mV from V<sub>OH</sub>. t<sub>DVR</sub> transition is measured at the 1.5V level. t<sub>HWZ</sub> and t<sub>LZR</sub> transition is measured at ±100 mV from the steady state.

<sup>10.</sup>  $t_{HZR}$  and  $t_{DVR}$  use capacitance loading as in part (a) of ACTest Loads.

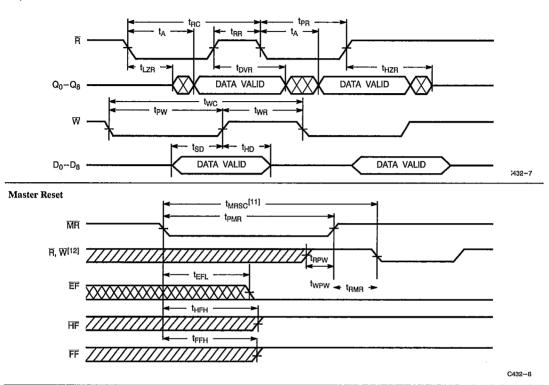

# **Switching Waveforms**

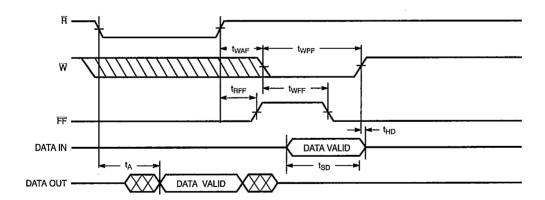

## Asynchronous Read and Write

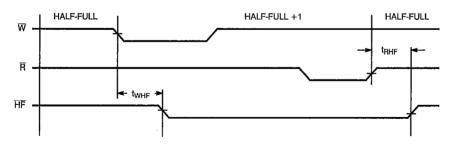

## Half-Full Flag

C432-9

Notes:

11. t<sub>MRSC</sub> = t<sub>PMR</sub> + t<sub>RMR</sub>.

12. Wand R ≥ V<sub>IH</sub> for at least t<sub>WPW</sub> or t<sub>RPR</sub> before the rising edge of MR.

C432-10

# Switching Waveforms (continued) Last Write to First Read Full Flag

Last Read to First Write Empty Flag

Retransmit<sup>[13]</sup>

C432-12

Notes:

13. EF, HF and FF may change state during retransmit as a result of the offset of the read and write pointers, but flags will be valid at t<sub>RTC</sub>.

14.  $t_{RTC} = t_{PRT} + t_{RTR}$ .

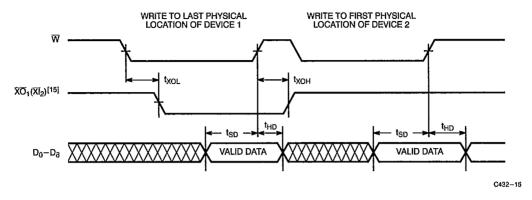

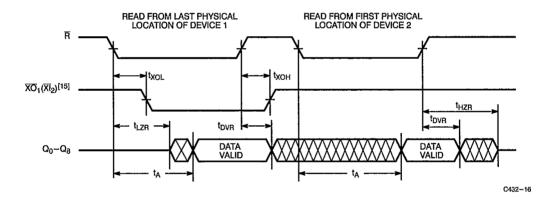

Switching Waveforms (continued)

**Empty Flag and Read Data Flow-Through Mode**

C432-13

## Full Flag and Write Data Flow-Through Mode

C432-14

# Switching Waveforms (continued)

### Expansion

<sup>15.</sup> Expansion Out of device 1  $(\overline{XO}_1)$  is connected to Expansion In of device 2  $(\overline{XI}_2)$ .

#### Architecture

The CY77C432/33 FIFOs consist of an array of 4096 words of 9 bits each (implemented by an array of dual-port RAMcells), a read pointer, a write pointer, control signals (W, R, XI, XO, FL, RT, MR), and Full, Half Full, and Empty flags.

#### **Dual-Port RAM**

The dual-port RAM architecture refers to the basic memory cell used in the RAM. The cell itself enables the read and write operations to be independent of each other, which is necessary to achieve truly asynchronous operations of the inputs and outputs. A second benefit is that the time required to increment the read and write pointers is much less than the time that would be required for data to propagate through the memory, which would be the case if the memory were implemented using the conventional register array architecture.

### Resetting the FIFO

Upon power-up, the FIFO must be reset with a master reset ( $\overline{MR}$ ) cycle. This causes the FIFO to enter the empty condition signified by the empty flag ( $\overline{EF}$ ) being LOW, and both the Half Full ( $\overline{HF}$ ) and Full flag ( $\overline{FF}$ ) resetting to HIGH. Read ( $\overline{R}$ ) and write ( $\overline{W}$ ) must be IIIGH  $t_{RPW}/t_{WPW}$  nanoseconds before and  $t_{RMR}$  nanoseconds after the rising edge of  $\overline{MR}$  for a valid reset cycle.

## Writing Data to the FIFO

The availability of an empty location is indicated by the HIGH state of the Full flag (FF). A falling edge of write (W) initiates a write cycle. Data appearing at the inputs  $(D_0-D_8)$  tgp before and tHD after the rising edge of W will be stored sequentially in the FIFO.

The Empty flag (EF) LOW-to-HIGH transition occurs  $t_{WEF}$  nanoseconds after the first LOW-to-HIGH transition on the write clock of an empty FIFO. The Half Full flag (HF) will go LOW on the falling edge of the write clock following the occurrence of half full. HF will remain LOW while less than one half of the total memory of this device is available for writing. The LOW-to-HIGH transition of the HF flag occurs on the rising edge of read (R). HF is available in single device mode only. The Full flag (FF) goes LOW on the falling edge of  $\overline{W}$  during the cycle in which the last available location in the FIFO is written, prohibiting overflow,  $\overline{FF}$  goes HIGH  $t_{RFF}$  after the completion of a valid read of a full FIFO.

### Reading Data from the FIFO

The falling edge of read  $(\overline{R})$  initiates a read cycle if the Empty flag  $(\overline{EF})$  is not LOW. Data outputs  $(Q_0-Q_8)$  are in a high-impedance condition between read operations  $(\overline{R}$  HIGH), when the FIFO is empty, or when the FIFO is in the depth expansion mode but is not the active device.

The falling edge of  $\overline{R}$  during the last read cycle before the empty condition triggers a HIGH-to-LOW transition of  $\overline{EE}$ , prohibiting any further read operations until twee after a valid write.

#### Retransmit

The retransmit feature is beneficial when transferring packets of data. It enables the receipt of data to be interrogated by the receiver and retransmitted if necessary.

The retransmit  $(\overline{RT})$  input is active in the single device mode only. The retransmit feature is intended for use when 4096 or less writes have occurred since the previous  $\overline{MR}$  cycle. A LOW pulse on  $\overline{RT}$  resets the internal read pointer to the first physical location of the FIFO. The write pointer is unaffected.  $\overline{R}$  and  $\overline{W}$  must both be HIGH during a retransmit cycle. Full, Half Full, and Empty flags are governed by the relative locations of the read and write pointers and will be updated by a retransmit operation.

After a retransmit cycle, previously read data may be reaccessed using  $\overline{R}$  to initiate standard read cycles beginning with the first physical location.

## Single Device/Width Expansion Modes

Single device and width expansion modes are entered by connecting  $\overline{\mathbf{X}}$ 1 to ground prior to an  $\overline{\mathbf{M}}\overline{\mathbf{K}}$  cycle. During these modes the  $\overline{\mathbf{H}}\overline{\mathbf{F}}$  and  $\overline{\mathbf{K}}\overline{\mathbf{T}}$  features are available. FIFOs can be expanded in width to provide word widths greater than 9 in increments of 9. During width expansion mode all control line inputs are common to all devices and flag outputs from any device can be monitored.

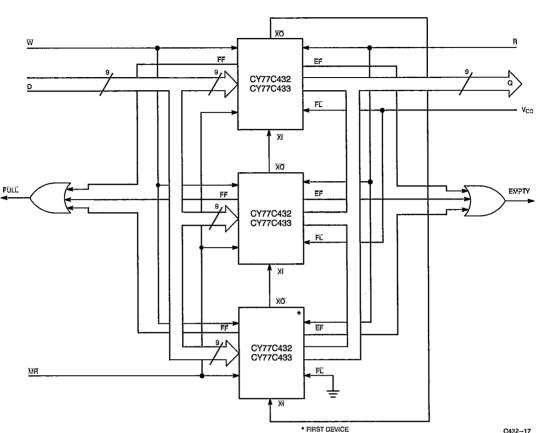

### Depth Expansion Mode (see Figure 1)

Depth expansion mode is entered when, during a  $\overline{MR}$  cycle, expansion Out ( $\overline{XO}$ ) of one device is connected to expansion in ( $\overline{XI}$ ) of the next device, with  $\overline{XO}$  of the last device connected to  $\overline{XI}$  of the first device. In the depth expansion mode the first load ( $\overline{FL}$ ) input, when grounded, indicates that this part is the first part to be loaded. All other devices must have this pin HIGH. To enable the correct FIFO,  $\overline{XO}$  is pulsed LOW when the last physical location of the previous FIFO is written to and is pulsed LOW again when the last physical location is read. Only one FIFO is enabled for read and one is enabled for write at any given time. All other devices are in standby.

FIFOs can also be expanded simultaneously in depth and width. Consequently, any depth or width FIFO can be created of word widths in increments of 9. When expanding in depth, a composite FF must be created by ORing the FFs together. Likewise, a composite EF is created by ORing the EFs together. HF and RT functions are not available in depth expansion mode.

C432-17

Figure 1. Depth Expansion

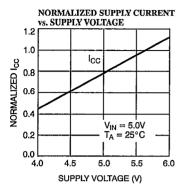

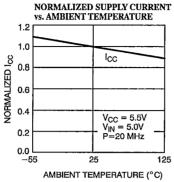

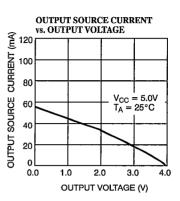

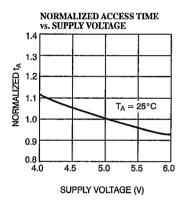

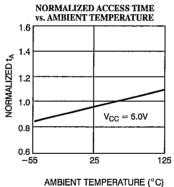

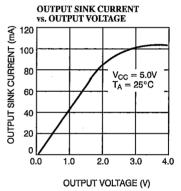

# **Typical DC and AC Characteristics**

C432-18

# **Ordering Information**

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                 | Operating<br>Range |

|---------------|---------------|-----------------|------------------------------|--------------------|

| 25            | CY7C432-25DC  | D16             | 28-Lead (600-Mil) CerDIP     | Commercial         |

|               | CY7C432-25PC  | P15             | 28-Lead (600-Mil) Molded DIP | ]                  |

| 30            | CY7C432-30DC  | D16             | 28-Lead (600-Mil) CerDIP     | Commercial         |

|               | CY7C432-30PC  | P15             | 28-Lead (600-Mil) Molded DIP | ]                  |

|               | CY7C432-30PI  | P15             | 28-Lead (600-Mil) Molded DIP | Industrial         |

|               | CY7C432-30DMB | D16             | 28-Lead (600-Mil) CerDIP     | Military           |

| 40            | CY7C432-40DC  | D16             | 28-Lead (600-Mil) CerDIP     | Commercial         |

|               | CY7C432-40PC  | P15             | 28-Lead (600-Mil) Molded DIP |                    |

|               | CY7C432-40PI  | P15             | 28-Lead (600-Mil) Molded DIP | Industrial         |

|               | CY7C432-40DMB | D16             | 28-Lead (600-Mil) CerDIP     | Military           |

| 65            | CY7C432-65DC  | D16             | 28-Lead (600-Mil) CerDIP     | Commercial         |

|               | CY7C432-65PC  | P15             | 28-Lead (600-Mil) Molded DIP |                    |

|               | CY7C432-65PI  | P15             | 28-Lead (600-Mil) Molded DIP | Industrial         |

|               | CY7C432-65DMB | D16             | 28-Lead (600-Mil) CerDIP     | Military           |

# Ordering Information (continued)

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                             | Operating<br>Range |

|---------------|---------------|-----------------|------------------------------------------|--------------------|

| 25            | CY7C433-25DC  | D22             | 28-Lead (300-Mil) CerDIP                 | Commercial         |

|               | CY7C433-25JC  | J65             | 32-Lead Plastic Leaded Chip Carrier      | 1                  |

|               | CY7C433-25PC  | P21             | 28-Lead (300-Mil) Molded DIP             |                    |

|               | CY7C433-25VC  | V21             | 28-Lead (300-Mil) Molded SOJ             |                    |

| 30            | CY7C433-30DC  | D22             | 28-Lead (300-Mil) CerDIP                 | Commercial         |

|               | CY7C433-30JC  | J65             | 32-Lead Plastic Leaded Chip Carrier      |                    |

|               | CY7C433-30PC  | P21             | 28-Lead (300-Mil) Molded DIP             | 1                  |

|               | CY7C433-30VC  | V21             | 28-Lead (300-Mil) Molded SOJ             |                    |

| ļ             | CY7C433-30JI  | J65             | 32-Lead Plastic Leaded Chip Carrier      | Industrial         |

| 1             | CY7C433-30PI  | P21             | 28-Lead (300-Mil) Molded DIP             |                    |

|               | CY7C433-30DMB | D22             | 28-Lead (300-Mil) CerDIP                 | Military           |

|               | CY7C433-30KMB | K74             | 28-Lead Rectangular Cerpack              |                    |

| İ             | CY7C433-30LMB | L55             | 32-Pin Rectangular Leadless Chip Carrier |                    |

| 40            | CY7C433-40DC  | D22             | 28-Lead (300-Mil) CerDIP                 | Commercial         |

|               | CY7C433-40JC  | J65             | 32-Lead Plastic Leaded Chip Carrier      |                    |

| ļ             | CY7C433-40PC  | P21             | 28-Lead (300-Mil) Molded DIP             |                    |

| ĺ             | CY7C433-40VC  | V21             | 28-Lead (300-Mil) Molded SOJ             |                    |

|               | CY7C433-40JI  | J65             | 32-Lead Plastic Leaded Chip Carrier      | Industrial         |

|               | CY7C433-40PI  | P21             | 28-Lead (300-Mil) Molded DIP             |                    |

|               | CY7C433-40DMB | D22             | 28-Lead (300-Mil) CerDIP                 | Military           |

|               | CY7C433-40KMB | K74             | 28-Lead Rectangular Cerpack              |                    |

|               | CY7C433~40LMB | L55             | 32-Pin Rectangular Leadless Chip Carrier |                    |

| 65            | CY7C433-65DC  | D22             | 28-Lead (300-Mil) CerDIP                 | Commercial         |

|               | CY7C433-65JC  | J65             | 32-Lead Plastic Leaded Chip Carrier      |                    |

|               | CY7C433-65PC  | P21             | 28-Lead (300-Mil) Molded DIP             |                    |

|               | CY7C433-65VC  | V21             | 28-Lead (300-Mil) Molded SOJ             |                    |

|               | CY7C433-65JI  | J65             | 32-Lead Plastic Leaded Chip Carrier      | Industrial         |

|               | CY7C433-65PI  | P21             | 28-Lead (300-Mil) Molded DIP             |                    |

|               | CY7C433-65DMB | D22             | 28-Lead (300-Mil) CerDIP                 | Military           |

|               | CY7C433-65KMB | K74             | 28-Lead Rectangular Cerpack              |                    |

|               | CY7C433-65LMB | L55             | 32-Pin Rectangular Leadless Chip Carrier |                    |

# MILITARY SPECIFICATIONS Group A Subgroup Testing DC Characteristics

| Parameters           | Subgroups |

|----------------------|-----------|

| $V_{\mathrm{OH}}$    | 1, 2, 3   |

| $V_{OL}$             | 1, 2, 3   |

| $V_{\rm III}$        | 1, 2, 3   |

| V <sub>IL</sub> Max. | 1, 2, 3   |

| $I_{IX}$             | 1, 2, 3   |

| $I_{CC}$             | 1, 2, 3   |

| $I_{\mathrm{SB1}}$   | 1, 2, 3   |

| $I_{\mathrm{SB2}}$   | 1, 2, 3   |

| $I_{OS}$             | 1, 2, 3   |

# **Switching Characteristics**

| Parameters        | Subgroups |

|-------------------|-----------|

| t <sub>RC</sub>   | 9, 10, 11 |

| t <sub>A</sub>    | 9, 10, 11 |

| t <sub>RR</sub>   | 9, 10, 11 |

| $t_{\mathrm{PR}}$ | 9, 10, 11 |

| t <sub>LZR</sub>  | 9, 10, 11 |

| t <sub>DVR</sub>  | 9, 10, 11 |

| t <sub>HZR</sub>  | 9, 10, 11 |

| t <sub>WC</sub>   | 9, 10, 11 |

| tpw               | 9, 10, 11 |

| t <sub>HWZ</sub>  | 9, 10, 11 |

| t <sub>WR</sub>   | 9, 10, 11 |

| t <sub>SD</sub>   | 9, 10, 11 |

| $t_{ m HD}$       | 9, 10, 11 |

| t <sub>MRSC</sub> | 9, 10, 11 |

| t <sub>PMR</sub>  | 9, 10, 11 |

| t <sub>RMR</sub>  | 9, 10, 11 |

| t <sub>RPW</sub>  | 9, 10, 11 |

| t <sub>WPW</sub>  | 9, 10, 11 |

| t <sub>RTC</sub>  | 9, 10, 11 |

| t <sub>PRT</sub>  | 9, 10, 11 |

| t <sub>RTR</sub>  | 9, 10, 11 |

| t <sub>EFL</sub>  | 9, 10, 11 |

| t <sub>HFH</sub>  | 9, 10, 11 |

| t <sub>FFH</sub>  | 9, 10, 11 |

| t <sub>REF</sub>  | 9, 10, 11 |

| t <sub>RFF</sub>  | 9, 10, 11 |

| t <sub>WEF</sub>  | 9, 10, 11 |

| t <sub>WFF</sub>  | 9, 10, 11 |

| t <sub>WHF</sub>  | 9, 10, 11 |

| t <sub>RHF</sub>  | 9, 10, 11 |

| t <sub>RAE</sub>  | 9, 10, 11 |

| t <sub>RPE</sub>  | 9, 10, 11 |

| t <sub>WAF</sub>  | 9, 10, 11 |

| t <sub>WPF</sub>  | 9, 10, 11 |

| t <sub>XOL</sub>  | 9, 10, 11 |

| t <sub>XOH</sub>  | 9, 10, 11 |

Document #: 38-00109-C