# LC<sup>2</sup>MOS 14-Bit μP Compatible DAC

AD7536

#### **FEATURES**

Full 4-Quadrant Multiplication without External Resistors

All Grades 14-Bit Monotonic over the Full Temperature Range

Low Output Leakage (<20nA) over the Full

Temperature Range

Low Gain Temperature Coefficient, 2ppm/°C

APPLICATIONS

Control and Measurement in High Temperature

Environments Digital Audio

Precision Servo Control

All Microprocessor Based Control Systems

#### **GENERAL DESCRIPTION**

The AD7536 is a 14-bit monolithic CMOS D/A converter. The part is laser trimmed and specified as a dedicated bipolar DAC. The resistors needed for 4-quadrant multiplication are contained on the chip. Thus, the user requires only the AD7536, a voltage reference and two op-amps for bipolar operation. The AD7536 has the same low leakage configuration (patent pending) as the other members of the 14-bit CMOS DAC family. The excellent output leakage current characteristics also ensure exceptional stability of linearity and gain error over the full temperature range.

The device is speed compatible with most microprocessors and accepts TTL or 5V CMOS logic level inputs. There is standard Chip Select and Memory Write logic for easy interfacing. The AD7536 has full protection against CMOS "latch-up" phenomena and does not require the use of external Schottky diodes or the use of a FET Input op-amp.

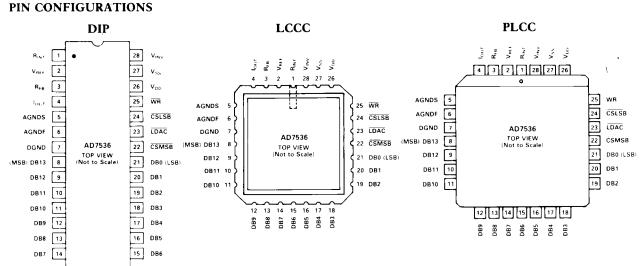

#### DIN CONFICUR ATTONIO

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

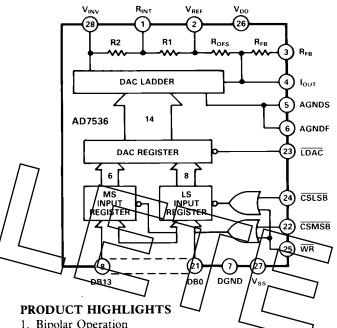

#### FUNCTIONAL BLOCK DIAGRAM

- 1. Bipolar Operation

The AD7536 gives the user 4-Quadrant Multiplication without any external resistors.

- 2. Guaranteed Monotonicity

14-bit monotonicity is guaranteed over the full temperature range for all grades.

- Low Output Leakage

The device has excellent output leakage current characteristics at all temperatures.

One Technology Way; Norwood, Massachusetts 02062-9106 Tel: 617/329-4700 TWX: 710/394-6577 West Coast Mid-West Texas

312/350-93<del>9</del>9

714/641-9391

214/231-5094

| Parameter                                                                                                                                                                | AD7536JN<br>AD7536AQ                    | AD7536KN<br>AD7536BQ    | AD7536SQ                   | AD7536TQ                       | Units                                | Test Conditions/Comments                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------|----------------------------|--------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACCURACY                                                                                                                                                                 |                                         |                         |                            |                                |                                      |                                                                                                                                                            |

| Resolution                                                                                                                                                               | 14                                      | 14                      | 14                         | 14                             | Bits                                 | $1LSB = 2V_{REF}/2^{14}$                                                                                                                                   |

| Relative Accuracy                                                                                                                                                        | ± 2                                     | ± 1                     | ± 2                        | ± 1                            | LSB max                              | All grades guaranteed monotonic                                                                                                                            |

| Differential Nonlinearity                                                                                                                                                | ± 1                                     | ± 1                     | ± 1                        | ± 1                            | LSB max                              | over temperature.                                                                                                                                          |

| Gain Error                                                                                                                                                               | ± 16                                    | ± 8                     | ± 16                       | ± 8                            | LSB max                              | Measured using internal R <sub>FB</sub> and includes effects of leakage current and gain T.C.                                                              |

| Offset Error                                                                                                                                                             | ± <b>4</b>                              | ± <b>4</b>              | <u>±</u> 4                 | ± <b>4</b>                     | LSB max                              | Error due to mismatch between $R_{FB}$ and offset resistor. It also includes leakage current to $I_{OUT}$ and is measured when DAC is loaded with all 0's. |

| Gain Temperature Coefficient <sup>4</sup> ,                                                                                                                              | ± 5                                     | ± 5                     | ± 5                        | ± 5                            | /°C                                  | Typical Value is 2ppm/°C                                                                                                                                   |

| ΔGain/ΔTemperature Offset Temperature Coefficient <sup>4</sup>                                                                                                           | ± 5                                     | ± 3                     | ± 3                        | ± 3                            | ppm/°C max                           | Typical value is 2ppm/ C                                                                                                                                   |

| ΔOffset/Δ Temperature                                                                                                                                                    | ± 5                                     | ± 2.5                   | ± 5                        | ± 2.5                          | ppm/°C max                           | Typical Value is 1ppm/°C                                                                                                                                   |

| INPUT RESISTANCES  V <sub>REF</sub> Input Resistance, Pin 2  V <sub>INV</sub> Input Resistance Pin 18                                                                    | 3 13 2 8                                | 3<br>13<br>2<br>8       | 3<br>13<br>2<br>8          | 3<br>13<br>2<br>8              | kΩ min<br>kΩ max<br>kΩ min<br>kΩ max | Typical Input Resistance = $6k\Omega$<br>Typical Input Resistance – $4k\Omega$                                                                             |

| DIGITAL INPUTS  V <sub>III</sub> (Input High Voltage)  V <sub>II</sub> (Input Low Voltage)  I <sub>IN</sub> (Input Current)  + 25°C  T <sub>mo</sub> to T <sub>max</sub> | 2.4                                     | 2.4<br>0.8<br>±1<br>±10 | 2.4<br>0.8<br>± 1<br>± 1/0 | 2.4<br>0.8<br>±1<br>±10        | V min<br>V max<br>µA max             | V <sub>IN</sub> 0V or V <sub>DD</sub>                                                                                                                      |

| C <sub>IN</sub> (Input Capacitance) <sup>4</sup>                                                                                                                         | 7                                       | 7                       | ' 7                        | 7 /                            | pF max                               |                                                                                                                                                            |

| POWER SUPPLY                                                                                                                                                             | <u> </u>                                |                         | 7 1 1                      | - 1                            |                                      |                                                                                                                                                            |

| V <sub>DD</sub> Range                                                                                                                                                    | 11.4/15.75                              | 11.4/15.75              | 11.4/15.75                 | 11.4/15.75                     | V <sub>min</sub> V <sub>max</sub>    | Specification guaranteed over                                                                                                                              |

| V <sub>SS</sub> Range                                                                                                                                                    | 200/ 500                                | 200/ - 500              | 200/500                    | <del>200</del> / - <b>1</b> 00 | mV min/mV max                        | this range.                                                                                                                                                |

| $I_{ m DD}$                                                                                                                                                              | 4<br>500                                | 4<br>500                | 4 500                      | 500                            | mA max<br>μA max                     | All digital inputs $V_{IL}$ or $V_{IH}$ All digital inputs $\emptyset V$ or $V_{DD}$                                                                       |

| Power Supply Rejection                                                                                                                                                   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                         |                            |                                |                                      |                                                                                                                                                            |

| $\Delta Gain/\Delta V_{DD}$                                                                                                                                              | $\pm 0.02$                              | $\pm 0.02$              | $\pm 0.02$                 | ± 0.02                         | % per % max                          | $\Delta V_{DD} = V_{DD} m_{ax} = V_{DD} min$                                                                                                               |

# **AC PERFORMANCE CHARACTERISTICS**

These characteristics are included for Design Guidance only and are not subject to test.  $(V_{DD}=+11.4V \text{ to }+15.75V, V_{REF}=+10V, V_{PIN4}=V_{PIN5}=0V, V_{SS}=0V \text{ OR }-300\text{mV},$  See Figure 6 for Suggested Specification Circuit<sup>3</sup>).

| Parameter                                  | $T_A = 25^{\circ}C$ | $T_A = T_{min}, T_{max}$ | Units              | Test Conditions/Comments                              |

|--------------------------------------------|---------------------|--------------------------|--------------------|-------------------------------------------------------|

| Current Settling Time                      | 1.5                 | _                        | μs max             | To 0.003% of full scale range.                        |

| <u>-</u>                                   |                     |                          |                    | $I_{OUT}$ load = $100\Omega$ ,                        |

|                                            |                     |                          |                    | C <sub>EXT</sub> = 13pF. DAC register alternately     |

|                                            |                     |                          |                    | loaded with all 1's and all 0's.                      |

|                                            |                     |                          |                    | Typical value of Settling Time                        |

|                                            |                     |                          |                    | is 0.8μs.                                             |

| Digital-to-Analog Glitch Impulse           | 50                  | _                        | nV-sec typ         | Measured with $V_{REF} = 0V$ . $I_{OUT}$ load         |

|                                            |                     |                          |                    | = $100\Omega$ , $C_{EXT} = 13pF$ . DAC                |

|                                            |                     |                          |                    | register alternately loaded with all                  |

|                                            |                     |                          |                    | 1's and all 0's.                                      |

| Multiplying Feedthrough Error <sup>5</sup> | 4                   | _                        | mV p-p typ         | $V_{REF} = \pm 10V$ , 1kHz sine wave                  |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,    |                     |                          |                    | DAC register loaded with 10 0000 0000 0000            |

| Output Capacitance                         |                     |                          |                    |                                                       |

| Cottr (Pin 4)                              | 260                 | 260                      | pF max             | DAC register loaded with all 1's                      |

| COUT (Pin 4)                               | 130                 | 130                      | pF max             | DAC register loaded with all 0's                      |

| Output Noise Voltage Density               |                     |                          | . —                |                                                       |

| (10Hz - 100kHz)                            | 50                  |                          | $nV/\sqrt{Hz}$ typ | Measured between R <sub>FB</sub> and I <sub>OUT</sub> |

NOTES

<sup>1</sup>Temperature range as follows:

JN, KN Versions:

AQ, BQ Versions: - 25°C to + 85°C SQ, TQ Versions: - 55°C to + 125°C

<sup>4</sup>Guaranteed by Product Assurance testing.

$<sup>^{2}</sup>$ Specifications are guaranteed for a  $V_{\mathrm{DD}}$  of + 11.4V to + 15.75V. At  $V_{\mathrm{DD}}$  = 5V, the device is fully functional with degraded specifications.

<sup>&</sup>lt;sup>3</sup>Only the D.U.T. (i.e., AD7536) is subjected to full temperature conditions.

Feedthrough can be further reduced by connecting the metal lid on the ceramic package to DGND.

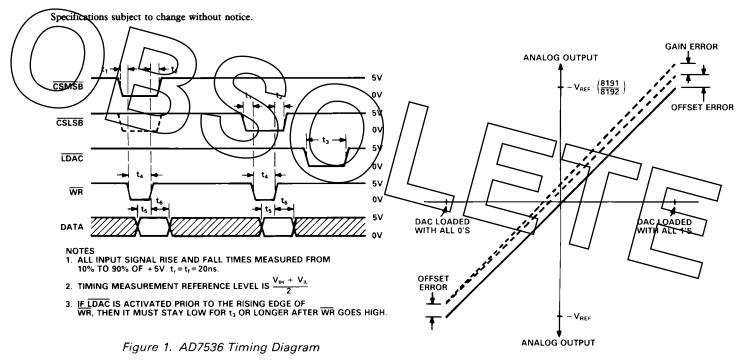

Specifications subject to change without notice.

### **TIMING CHARACTERISTICS**

( $V_{DD}=+11.4V$  to +15.75V,  $V_{REF}=+10V$ ,  $V_{PBN4}=V_{PBN5}=0V$ ,  $V_{SS}=0V$  or -300mV All specifications  $T_{min}$  to  $T_{max}$  unless otherwise stated. See Figure 1 for Timing Diagram.)

| Parameter      | Limit at<br>T <sub>A</sub> = 25°C | Limit at<br>$T_A = 0 \text{ to } + 70^{\circ}\text{C}$<br>$T_A = -25^{\circ}\text{C to } + 85^{\circ}\text{C}$ | Limit at<br>T <sub>A</sub> = -55°C to | + 125°C Units | Test Conditions/Comments        |

|----------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------|---------------------------------|

| t <sub>1</sub> | 0                                 | 0                                                                                                              | 0                                     | ns min        | CSMSB or CSLSB to WR Setup Time |

| t <sub>2</sub> | 0                                 | 0                                                                                                              | 0                                     | ns min        | CSMSB or CSLSB to WR Hold Time  |

| t <sub>3</sub> | 170                               | 200                                                                                                            | 240                                   | ns min        | LDAC Pulse Width                |

| t <sub>4</sub> | 170                               | 200                                                                                                            | 240                                   | ns min        | Write Pulse Width               |

| t <sub>5</sub> | 140                               | 160                                                                                                            | 180                                   | ns min        | Data Setup Time                 |

| t <sub>6</sub> | 20                                | 20                                                                                                             | 30                                    | ns min        | Data Hold Time                  |

Figure 2. AD7536 Transfer Function

#### **ORDERING INFORMATION**

|          | Temperature                                   | Relative | Full Scale | Package  |

|----------|-----------------------------------------------|----------|------------|----------|

| Model    | Range                                         | Accuracy | Error      | Options* |

| AD7536JN | $0^{\circ}$ C to $+70^{\circ}$ C              | ± 2LSB   | ± 16LSB    | N-28     |

| AD7536KN | $0^{\circ}$ C to $+70^{\circ}$ C              | ±1LSB    | ±8LSB      | N-28     |

| AD7536JP | $0^{\circ}$ C to $+70^{\circ}$ C              | ±2LSB    | ± 16LSB    | P-28A    |

| AD7536KP | $0^{\circ}$ C to + $70^{\circ}$ C             | ±1LSB    | ±8LSB      | P-28A    |

| AD7536AQ | − 25°C to + 85°C                              | ± 2LSB   | ± 16LSB    | Q-28     |

| AD7536BQ | $-25^{\circ}\text{C to} + 85^{\circ}\text{C}$ | ±1LSB    | ±8LSB      | Q-28     |

| AD7536SQ | $-55^{\circ}$ C to $+125^{\circ}$ C           | ± 2LSB   | ± 16LSB    | Q-28     |

| AD7536TQ | - 55°C to + 125°C                             | ± 1LSB   | ±8LSB      | Q-28     |

| AD7536SE | −55°C to +125°C                               | ± 2LSB   | ± 16LSB    | E-28A    |

| AD7536TE | −55°C to +125°C                               | ±1LSB    | ±8LSB      | E-28A    |

#### NOTE

#### **PRICING** (100+)\$

| AD7536JN | \$18.95  |

|----------|----------|

| AD7536KN | \$28.45  |

| AD7536AD | \$28.95  |

| AD7536BD | \$38.45  |

| AD7536SD | \$80.70  |

| AD7536TD | \$113.05 |

<sup>\*</sup>E = Leadless Ceramic Chip Carrier; N = Plastic DIP; P = Plastic Leaded Chip Carrier;

Q = Cerdip; R - SOIC.

### AD7536

| ABSOLUTE MAXIMUM RATINGS                                         |

|------------------------------------------------------------------|

| $(T_A = 25^{\circ}C \text{ unless otherwise stated})$            |

| $V_{DD}$ (pin 26) to DGND0.3V, +17V                              |

| $V_{SS}$ (pin 27) to AGND                                        |

| $V_{REF}$ (pin 2) to AGND                                        |

| $V_{INV}$ (pin 28) to AGND ±25V                                  |

| $R_{INT}$ (pin 1) to AGND                                        |

| $R_{FB}$ (pin 3) to AGND                                         |

| Digital Input Voltage (pins 8–25) to DGND $-0.3V$ , $V_{\rm DD}$ |

| $V_{PIN4}$ to DGND0.3V, $V_{DD}$                                 |

| AGND to DGND $-0.3V$ , $V_{DD}$                                  |

| Power Dissipation (Any package)                                  |

| Derates above +75°C 10mW/°C                             |

|---------------------------------------------------------|

| Operating Temperature Range                             |

| Commercial Plastic (JN, KN versions) 0 to +70°C         |

| Industrial Ceramic (AQ, BQ versions)25°C to +85°C       |

| Extended Ceramic (SQ, TQ versions)55°C to +125°C        |

| Storage Temperature $-65^{\circ}$ C to $+150^{\circ}$ C |

| Lead Temperature (Soldering, 10 secs) + 300°C           |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### CAUTION

ESD (Electro-Static-Discharge) sensitive device. The digital control inputs are diode protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are removed.

#### **TERMINOLOGY**

#### **LEAST SIGNIFICANT BIT (LSB)**

ARSOLLITE MAYIMLIM DATINGS

This is the analog weighting of 1 bit of the digital word in a

DAC. For the AD7536 1LSB =  $\frac{2V_{REF}}{2^{14}}$

#### **RELATIVE ACCURACY**

Relative accuracy or end point nonlinearity is a measure of the maximum deviation from a straight line passing through the end-points of the DAC transfer function. It is measured after adjusting for both endpoints (i.e., Offset and Gain Error are adjusted out) and is normally expressed in Least Significant Bits or as a percentage of full scale range.

#### **DIFFERENTIAL NONLINEARITY**

Differential nonlinearity is the difference between the measured change and the ideal 1LSB change between any two adjacent codes. A specified differential nonlinearity of +1LSB max over the operating temperature range ensures monotonicity.

#### **GAIN ERROR**

Gain error is a measure of the output error between an ideal DAC and the actual device output with all one's loaded after offset error has been adjusted out. Gain error is adjustable to zero with an external potentiometer.

#### OFFSET ERROR

Offset error is a measure of the mismatch between R<sub>FB</sub> and the internal offset resistor, R<sub>OFS</sub>. It also includes the leakage component from the DAC (see Figure 8). It is present for all codes and is expressed in Least Significant Bits.

#### DIGITAL-TO-ANALOG GLITCH IMPULSE

The amount of charge injected from the digital inputs to the analog output when the inputs change state is called Digital-to-Analog Glitch Impulse. This is normally specified as the area of the glitch in either pA-secs or nV-secs depending upon whether the glitch is measured as a current or voltage. It is measured with  $V_{\rm REF} = AGND$ .

### **OUTPUT CAPACITANCE**

This is the capacitance from I<sub>OUT</sub> to AGND.

#### LEAKAGE CURRENT

Leakage current flows into I<sub>OUT</sub> from the 14-bit DAC when all the DAC switches are off. It contributes to the Linearity, Gain and Offset error (see Figure 8).

#### MULTIPLYING FEEDTHROUGH ERROR

This is the ac error due to capacitive feedthrough from  $V_{REF}$  terminal to  $I_{OUT}$  with DAC register loaded with 10 0000 0000 0000.

| Pin      | Function                                      | Descript                                                                                                                                    | tion                                                                                                                                                     |                         |         |                                                                                                                                |  |  |  |  |  |

|----------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1        | $R_{INT}$                                     | Contact point for internal resistors R1 and R2 which perform the inverting function on V <sub>REF</sub> with external op-amp. See Figure 3. |                                                                                                                                                          |                         |         |                                                                                                                                |  |  |  |  |  |

| 2        | $V_{REF}$                                     | Reference input to the DAC. It is internally connected to R <sub>OFS</sub> and R1. See Figure 3.                                            |                                                                                                                                                          |                         |         |                                                                                                                                |  |  |  |  |  |

| 3        | $R_{FB}$                                      | Feedback resistor. Used to close the loop around an external op-amp.                                                                        |                                                                                                                                                          |                         |         |                                                                                                                                |  |  |  |  |  |

| 4        | $I_{OUT}$                                     |                                                                                                                                             | Current Output Terminal.                                                                                                                                 |                         |         |                                                                                                                                |  |  |  |  |  |

| 5        | $A_{GNDS}$                                    | Analog g                                                                                                                                    | Analog ground sense line. Reference point for external circuitry. This pin should carry minimal current.                                                 |                         |         |                                                                                                                                |  |  |  |  |  |

| 6        | $A_{GNDF}$                                    |                                                                                                                                             | Analog ground force line; carries current from internal analog ground connections. A <sub>GNDF</sub> and A <sub>GNDS</sub> are tied together internally. |                         |         |                                                                                                                                |  |  |  |  |  |

| 7        | DGND                                          | Digital G                                                                                                                                   | round                                                                                                                                                    |                         |         |                                                                                                                                |  |  |  |  |  |

| 8        | DB13                                          | Data Bit                                                                                                                                    | 13. DAC                                                                                                                                                  | MSB                     |         |                                                                                                                                |  |  |  |  |  |

| 9        | QB12                                          | Data Bit                                                                                                                                    |                                                                                                                                                          |                         |         |                                                                                                                                |  |  |  |  |  |

| / 10     | √D <b>ğ</b> (1 /                              | Data Bit                                                                                                                                    |                                                                                                                                                          |                         |         |                                                                                                                                |  |  |  |  |  |

| / / 11   | Ъви̂о /                                       | Data Bit                                                                                                                                    |                                                                                                                                                          |                         |         |                                                                                                                                |  |  |  |  |  |

| 12       | фв9  /                                        | Data Bit                                                                                                                                    |                                                                                                                                                          |                         |         |                                                                                                                                |  |  |  |  |  |

| \ \ 13   | /DB\$ /                                       | Data Bit                                                                                                                                    | , , ,                                                                                                                                                    | $\frown$ $'$            | \       |                                                                                                                                |  |  |  |  |  |

| 14       | / DB7 / /                                     | Data Bit                                                                                                                                    |                                                                                                                                                          | $\setminus$ $\setminus$ | ) /     |                                                                                                                                |  |  |  |  |  |

| 15       | DB6/L                                         | Data Bit                                                                                                                                    |                                                                                                                                                          | , \                     | //      | $\frown$                                                                                                                       |  |  |  |  |  |

| 16       | DB5                                           | Data Bit                                                                                                                                    |                                                                                                                                                          | / /                     | / /     |                                                                                                                                |  |  |  |  |  |

| 17       | DB4                                           | Data Bit                                                                                                                                    | · ·                                                                                                                                                      | ノノ                      | 1 (     |                                                                                                                                |  |  |  |  |  |

| 18<br>19 | DB3<br>DB2                                    | Data Bit                                                                                                                                    | _                                                                                                                                                        |                         |         |                                                                                                                                |  |  |  |  |  |

| 20       | DB2<br>DB1                                    | Data Bit                                                                                                                                    |                                                                                                                                                          |                         | ( )     |                                                                                                                                |  |  |  |  |  |

| 21       | DB1<br>DB0                                    |                                                                                                                                             |                                                                                                                                                          | SB                      | _       |                                                                                                                                |  |  |  |  |  |

| 22       | CSMSB                                         |                                                                                                                                             | Data Bit 0. DAC LSB Chip Select Most Significant (MS) Byte. Active LOW input. Asynchronous Load DAC input. Active LOW.                                   |                         |         |                                                                                                                                |  |  |  |  |  |

| 23       | LDAC                                          |                                                                                                                                             |                                                                                                                                                          |                         |         |                                                                                                                                |  |  |  |  |  |

| 24       | CSLSB                                         |                                                                                                                                             |                                                                                                                                                          |                         |         | yte. Active LOW input.                                                                                                         |  |  |  |  |  |

| 25       | $\overline{\mathbf{W}}\mathbf{R}$             |                                                                                                                                             | out. Activ                                                                                                                                               |                         | / .     |                                                                                                                                |  |  |  |  |  |

|          |                                               | •                                                                                                                                           |                                                                                                                                                          |                         |         |                                                                                                                                |  |  |  |  |  |

|          |                                               |                                                                                                                                             | CSLSB                                                                                                                                                    | LDAC                    | WR      | Operation                                                                                                                      |  |  |  |  |  |

|          |                                               | 0                                                                                                                                           | 1                                                                                                                                                        | 1                       | 0       | Load MS Input Register                                                                                                         |  |  |  |  |  |

|          |                                               | 1                                                                                                                                           | 0                                                                                                                                                        | 1                       | 0       | Load LS Input Register                                                                                                         |  |  |  |  |  |

|          |                                               | 0                                                                                                                                           | 0                                                                                                                                                        | 1                       | 0       | Load MS and LS Input Registers                                                                                                 |  |  |  |  |  |

|          |                                               | 1                                                                                                                                           | 1                                                                                                                                                        | 0                       | X       | Load DAC Register from Input Registers                                                                                         |  |  |  |  |  |

|          |                                               | 0                                                                                                                                           | 0                                                                                                                                                        | 0                       | 0       | All Registers are transparent                                                                                                  |  |  |  |  |  |

|          |                                               | 1                                                                                                                                           | 1                                                                                                                                                        | 1                       | X       | No operation                                                                                                                   |  |  |  |  |  |

|          |                                               | X                                                                                                                                           | $\mathbf{x}$                                                                                                                                             | 1                       | 1       | No operation                                                                                                                   |  |  |  |  |  |

|          |                                               | NOTE X                                                                                                                                      | C = Don't                                                                                                                                                | Care                    |         | <del></del>                                                                                                                    |  |  |  |  |  |

| 26<br>27 | $egin{aligned} V_{DD} \ V_{SS} \end{aligned}$ | Bias pin f                                                                                                                                  | or High T                                                                                                                                                | emperati                | ire Low | pply for $V_{DD} = +12V \pm 5\%$ to $+15V \pm 5\%$ .<br>Leakage configuration. To implement low leakage system, the pin should |  |  |  |  |  |

be at a negative voltage. See Figure 5 or 6 for recommended circuitry.

This pin must be connected to the output of the external inverting op-amp. See Figure 3.

28

$V_{\mathbf{INV}}$

Table.

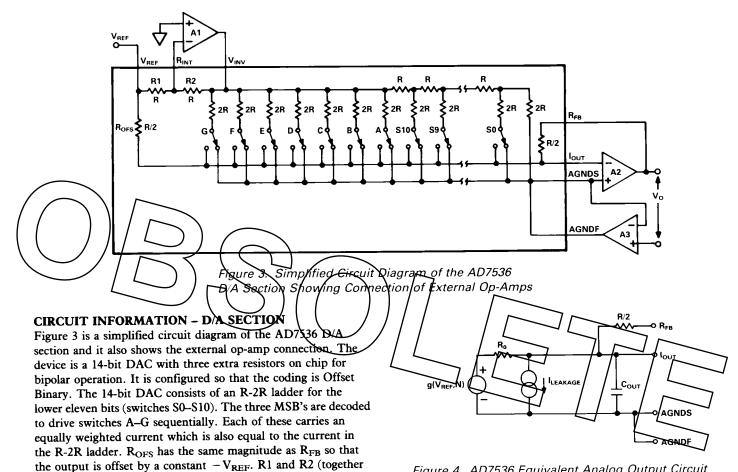

Figure 4. AD7536 Equivalent Analog Output Circuit

#### To eliminate any slight variations in analog ground potential with changing code, there are two analog ground pins. AGNDF sinks all the current flowing through the switches to ground while AGNDS is used as a reference point with minimal current flowing in it. Figure 3 shows A3 maintaining AGNDS at Signal Ground. The connection of AGNDS and AGNDF may be changed depending on required system accuracy and output drive requirements (see Figures 5 and 6).

with external op-amp A1) invert V<sub>REF</sub> and apply it to the 14-bit DAC  $(V_{INV})$ . See Table I for complete Offset Binary Code

#### EQUIVALENT CIRCUIT ANALYSIS

Figure 4 shows an equivalent output circuit for the analog section of the AD7536 D/A converter. The current source ILEAKAGE is composed of surface and junction leakages. The resistor R0 denotes the equivalent output resistance of the DAC and associated resistors. This varies with input code. COUT is the capacitance due to the current steering switches and varies from about 90pF to 180pF (typical values) depending on the digital input. g(V<sub>REF</sub>, N) is the Thevenin equivalent voltage generator due to the reference input voltage, V<sub>REF</sub>, and the circuit transfer function, N.

#### CIRCUIT INFORMATION - DIGITAL SECTION

The digital inputs are designed to be both TTL and 5V CMOS compatible. All logic inputs are static protected MOS gates with typical input currents of less than 1nA. Internal input protection is achieved by an on-chip distributed diode from DGND to each MOS gate. To minimize power supply currents, it is recommended that the digital input voltages be driven as close as possible to 0 and 5V logic levels.

## (4-Quadrant Multiplication)

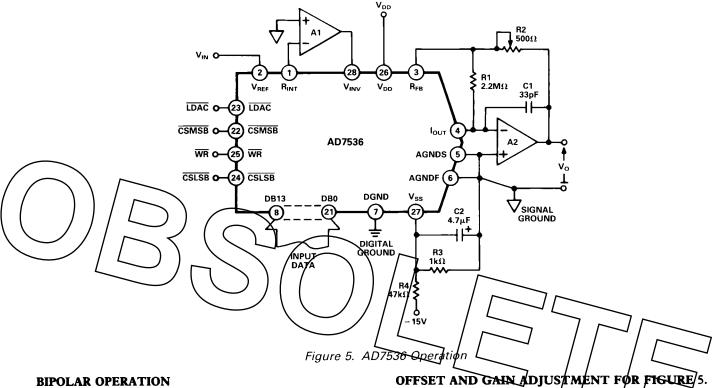

Figure 5 shows the AD7536 connected for bipolar operation. Specified accuracy is attained without the need for expensive closely matched external resistors. R1 and R2 provide an optional gain adjustment and capacitor C1 helps prevent overshoot and ringing when high-speed op-amps are used. The -300mV bias voltage for V<sub>SS</sub> is derived from R3, R4 and C2. Op-amp A3 (Figure 3 and Figure 6) is omitted from Figure 5. AGNDS and AGNDF are externally shorted to Signal Ground.

Table I shows the Offset Binary Code Table obtained with the circuit of Figure 5. It should be noted that the user can get a 2's Complement transfer function by inverting the MSB of the DAC word.

| Binary Number in DAC Register | Analog Output V <sub>OUT</sub>                    |

|-------------------------------|---------------------------------------------------|

| MSB LSB                       | (9101)                                            |

| 11 1111 1111 1111             | $+V_{IN}\left(\frac{8191}{8192}\right)$           |

| 10 0000 0000 0001             | $+V_{IN}\left(\frac{1}{8192}\right)$              |

| 10 0000 0000 0000             | 0V                                                |

| 00 0000 0000 0001             | $-V_{IN}\Big(\frac{8191}{8192}\Big)$              |

| 00 0000 0000 0000             | $-V_{IN}\left(\frac{8192}{8192}\right) = -V_{IN}$ |

Table I. Offset Binary Code Table for AD7536

# Offset Adjustment

- 1. Adjust offset of amplifier A1 so that potential at Rour is <10µV with respect to Signal Ground.

- 2. Load DAC register with 10 0000 0000 0000.

- 3. Adjust offset of amplifier A2 until  $V_O = 0V$  (<10 $\mu$ V).

#### Gain Adjustment

- 1. Load DAC register with all 1's.

- 2. Trim potentiometer R2 so that  $V_O = +V_{IN} \frac{(8191)}{(8192)}$

For high-temperature applications, resistors and potentiometers should have a low Temperature Coefficient. In many applications, because of the excellent Offset Error, Full Scale Error and Gain T.C. specifications of the AD7536, trimming of the Offset and Gain is not necessary.

#### **GROUNDING CONSIDERATIONS**

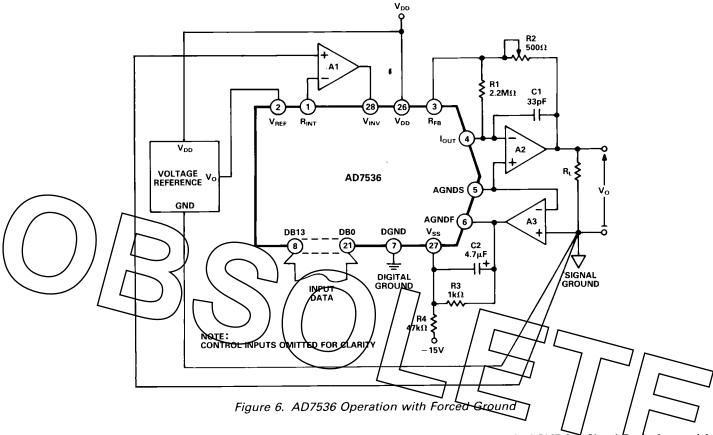

In the circuits of Figures 5 and 6, with  $V_{REF} = +10V$ , 1LSB has a value of 1.2mV. So, factors which are not important in less accurate systems must, in this case, be given careful consideration. Among these, the whole question of grounding is crucial. Voltage reference ground, the  $I_{OUT}$  pin on the DAC, the noninverting pin of A1 and SIGNAL GROUND must all be at the same potential. Note that in Figure 5, AGNDS and AGNDF are externally shorted and A3 is not used. Voltage drops due to bond wire resistance are not compensated for in this circuit. This means that an extra linearity error of less than 0.1LSB is added to the DAC linearity error. If the user wishes to eliminate this extra error, then the circuit of Figure 6 should be used.

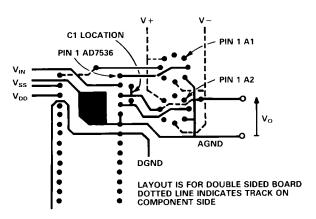

Here, A3 is used to maintain AGNDS at Signal Ground potential.  $I_{OUT}$  is also at Signal Ground potential. By using the Force, Sense technique all switch contacts on the DAC are at exactly the same potential and any error due to bond wire resistance is eliminated. If A3 is not a low offset voltage ( $<100\mu V$ ) op-amp, it should be trimmed with a potentiometer until the voltage at AGNDS is  $<10\mu V$  with respect to SIGNAL GROUND. Figure 7 shows how the circuit of Figure 5 might be be laid out. Gain trim components R1 and R2 have been omitted for clarity. Note how the input to  $V_{REF}$  (pin 2) is shielded to reduce ac feed-through while the digital inputs are shielded to minimize digital feedthrough.

Figure 7. Suggested Layout for AD7536 Circuit of Figure 5

\_

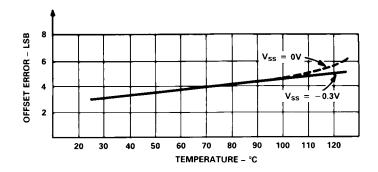

Figure 8. Typical Graph of Offset Error vs. Temperature With and Without Low Leakage Configuration

LOW LEAKAGE CONFIGURATION

Leakage current in CMOS D/A converters has two components. Current leaks from V<sub>DD</sub> into the lour line and is present at all DAC codes. There is also leakage across the off switches in the DAC. The polarity of this current depends on V<sub>IVIV</sub> and its magnitude is related to the code in the DAC register. At high temperatures (above 90°C) it is normal for the leakage current to increase dramatically. By its nature it will affect all critical do parameters (Linearity Error, Gain Error and Offset Error). The AD7536 features a leakage reduction configuration (patent pending) to keep the leakage current low (typically <10nA) over an extended temperature range. This ensures that the DAC maintains its 25°C performance very well at temperatures up to 125°C.

The AD7536 can be operated with or without the leakage reduction configuration. If  $V_{SS}$  (pin 27) is tied to AGND, then the DAC will exhibit normal output leakage current at high temperatures. To use the low leakage facility,  $V_{SS}$  should be tied to -0.3V as in Figures 5 and 6. The current taken by  $V_{SS}$  is very low (<10 $\mu$ A) allowing a simple resistor divider (R3, R4) to produce the required -300 mV from -15V. The capacitor C2 in parallel with R3 is an integral part of the low leakage configuration and must be  $4.7 \mu F$  or greater. Figure 8 is a plot of Offset Error versus temperature for both conditions. It clearly shows the improvement when the low leakage configuration is used.

#### **OP-AMP SELECTION**

In choosing an amplifier to be used with the AD7536, three parameters are of prime importance. These are:

1. Input Offset Voltage (V<sub>OS</sub>) 2/ Input Bias Current (I<sub>B</sub>)

Offset Voltage Drift (TC Vos).

Figures 5 and 6 must have V<sub>OS</sub> < 100μV and/I<sub>B</sub> < 10nA. It is important that the amplifier Open Loop Gain, A<sub>VOL</sub>, be sufficiently large to keep V<sub>OS</sub> < 100μV for the full output voltage range. For a maximum output of 10V, A<sub>VOL</sub> must be greater than 100,000.

In the Forced Ground configuration of Figure 6, one can use an AD OP-07 for amplifier A3, without any external adjustment for  $V_{OS}$ . In low frequency or fixed reference applications where fast output settling time is not required, the AD OP-07 is also recommended for A1 and A2. Because of its low  $V_{OS}$  no external potentiometers are needed. For faster settling time, one can use the AD544 series of op-amps.

Offset Voltage Drift and Bias Current drift are critical parameters for operation over a wide temperature range. The AD OP-07, AD OP-27 and AD OP-37 all exhibit very low offset drift while the AD544 has very low bias current drift. Table II summarizes the important specifications of the op-amps mentioned above.

| Op-Amp     | Input Offset<br>Voltage (V <sub>OS</sub> ) | Input Bias<br>Current (I <sub>B</sub> ) | Offset Voltage<br>Drift (TC V <sub>OS</sub> ) | Settling Time to 0.003% FS |

|------------|--------------------------------------------|-----------------------------------------|-----------------------------------------------|----------------------------|

| AD544L     | 500μV                                      | 25pA                                    | 5μV/°C                                        | 5μs                        |

| AD OP-07H  | 75μV                                       | 3nA                                     | 0.6μV/°C                                      | 50μs typ                   |

| AD OP-27CH | 100μV                                      | 80nA                                    | 0.6μV/°C                                      | 6μs typ                    |

| AD OP-37CH | 100μV                                      | 80nA                                    | 0.6µV/°C                                      | lμs typ                    |

| HA-2620    | 4mV                                        | 35nA                                    | 20μV/°C                                       | 0.8μs typ                  |

|            |                                            |                                         |                                               |                            |

Table II. Guide to Op-Amp Selection

### AD7536

imultangously.

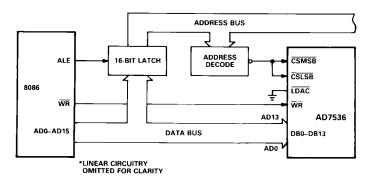

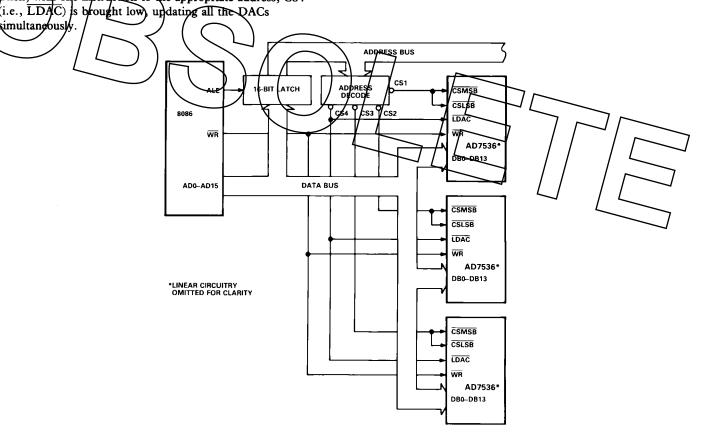

#### MICROPROCESSOR INTERFACING AD7536 - 8086A INTERFACE

The versatility of the AD7536 loading sturcture allows interfacing to both 8- and 16-bit microprocessor systems. Figure 9 shows the 8086 16-bit processor interfacing to a single device. In this circuit the double buffering feature of the DAC is not used. AD0-AD13 of the 16-bit data bus are connected to the DAC data bus (DB0-DB13). The 14-bit word is written to the DAC in one MOV instruction and the analog output responds immediately. In this example the DAC address is D000. A software routine for Figure 9 is given in Table III. In a multiple DAC system the double buffering of the AD7536 allows the user to simultaneously update all DAC's. In Figure 10, a 14-bit word is loaded to the Input Registers of each of the DACs in sequence. Then, with one instruction to the appropriate address, CS4

Figure 9. AD7536 - 8086 Interface Circuit

Figure 10. AD7536 - 8086 Interface: Multiple DAC System

#### ASSUME DS: DACLOAD, CS: DACLOAD **DACLOAD SEGMENT AT 000**

| 00            | 8CC9       | MOV CX, CS       | : | DEFINE DATA SEGMENT REGISTER EQUAL |

|---------------|------------|------------------|---|------------------------------------|

| 02            | 8ED9       | MOV DS, CX       | : | TO CODE SEGMENT REGISTER           |

| 04            | BF00D0     | MOV DI, # D000   | : | LOAD DI WITH D000                  |

| 07            | C705"YZWX" | MOV MEM, # YZWX" | : | DAC LOADED WITH WXYZ               |

| $\mathbf{0B}$ | EA0000     |                  | : | CONTROL IS RETURNED TO THE         |

| 0E            | 00FF       |                  |   | MONITOR PROGRAM                    |

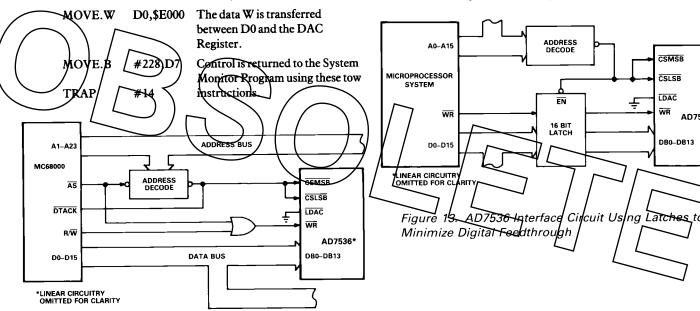

#### AD7536 - MC68000 INTERFACE

Interfacing between the MC68000 and the AD7536 is accomplished using the circuit of Figure 11. The following routine writes data to the DAC input registers and then outputs the data via the DAC register.

#W, D0 01000 MOVE.W

The desired DAC data, W, is loaded into Data Register 0. W may be any value between 0 and 16383 (decimal) or 0 and 3FFF (hexademical).

Figure 11. AD7536 - MC68000 Interface

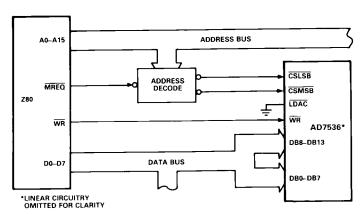

#### AD7536 - Z80 INTERFACE

Though the AD7536 is ideally suited for use either with 16-bit microprocessors or in stand-alone applications, it can also be interfaced to 8-bit processor systems. Figure 12 is an interface circuit for the popular Z80 microprocessor.

Figure 12. AD7536 - Z80 Interface

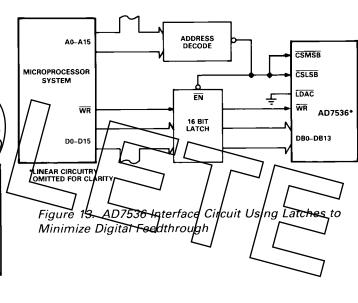

#### DIGITAL FEEDTHROUGH

In the preceding interface configurations, most digital inputs to the AD7536 are directly connected to the microprocessor bus. Even when the device is not selected, these inputs will be constantly changing. The high frequency logic activity on the bus can feed through the DAC package capacitance to show up as noise on the analog output. To minimize this Digital Feedthrough isolate the DAC from the noise source. Figure 13 shows an interface circuit which physically isolates the DAC from the bus. One may also use other means, such as peripheral interface devices, to reduce the Digital Feedthrough.

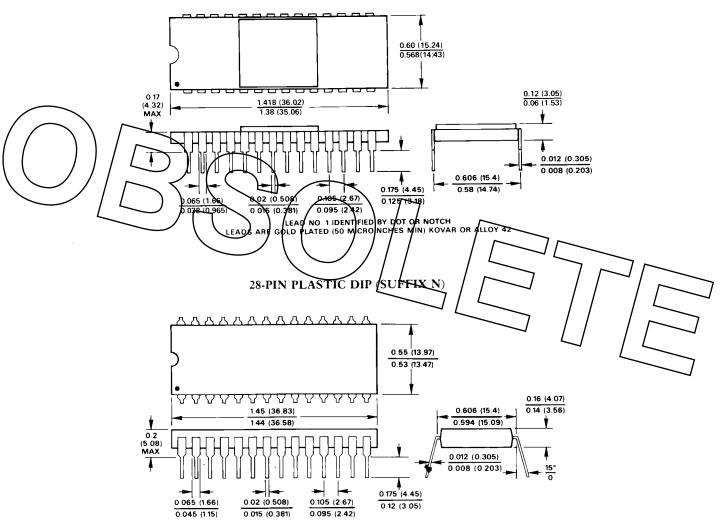

# MECHANICAL INFORMATION OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

#### 28-PIN CERAMIC DIP (SUFFIX D)

LEAD NO. 1 IDENTIFIED BY DOT OR NOTCH LEADS ARE SOLDER OR TIN PLATED KOVAR OR ALLOY 42