T-46-35

# 67C401/13 67C402/23

First-In First-Out (FIFO) 64 x 4, 64 x 5 CMOS MEMORY (Cascadable) Advanced Micro Devices

#### **DISTINCTIVE CHARACTERISTICS**

- Zero standby power

- High-speed 35-MHz shift-in/shift-out rates

- Very low active power consumption

- TTL-compatible inputs and outputs

- Readily expandable in word width and depth

- RAM-based architecture for short fall-through

- Full CMOS cell for maximum noise immunity

- **Asynchronous operation**

- Output Enable feature (67C4013/23)

#### **GENERAL DESCRIPTION**

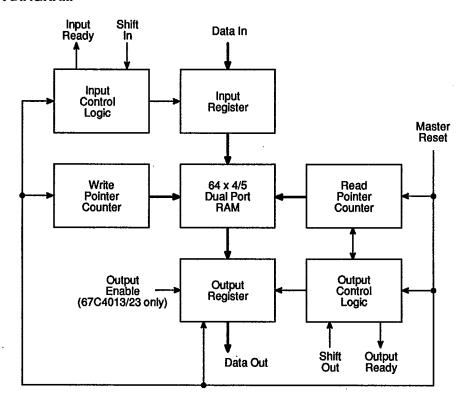

The 67C40X/XX series devices are high-performance CMOS RAM-based First-In First-Out (FIFO) buffer memory products organized as 64 words by 4 or by 5, bits wide. These devices use Advanced Micro Devices latest CMOS process technology and meet the demands for high-speed, low-power operation. By utilizing an on-chip, dual-port RAM, a very short fall-through time is realized, thus improving overall system performance. By using both Read and Write pointers for addressing

each memory location, the data can propagate to the outputs in much less time than in traditional registerbased FIFOs. These FIFOs are easily integrated into many applications and perform particularly well for highspeed disc controllers, graphics, and communication network systems. The 550-µwatt standby power specification makes these devices ideal for ultra-low power and battery-powered systems.

#### **BLOCK DIAGRAM**

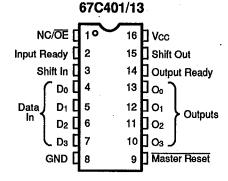

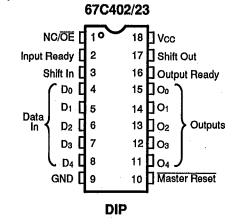

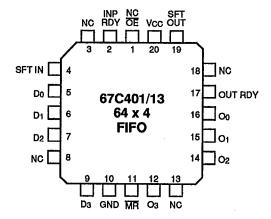

#### **CONNECTION DIAGRAMS**

T-46-35

DIP

**Plastic Leaded Chip Carrier**

**Plastic Leaded Chip Carrier**

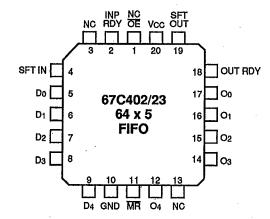

#### ORDERING INFORMATION Standard Products

T-46-35

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

a. Device Number

b. Speed Option (if applicable)

Package Type Temperature Range

d. Optional Processing

| Valid Combinations |          |  |  |  |  |

|--------------------|----------|--|--|--|--|

| AM67C401-10        |          |  |  |  |  |

| AM67C401-15        | ]        |  |  |  |  |

| AM67C4013-10       | ]        |  |  |  |  |

| AM67C4013-15       | ]        |  |  |  |  |

| AM67C402-10        | N, J, NL |  |  |  |  |

| AM67C402-15        |          |  |  |  |  |

| AM67C4023-10       | ]        |  |  |  |  |

| AM67C4023-15       | <u></u>  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

\* Military or Limited Military temperature range products are "NPL" (Non-Compliant Products List) or Non-MIL-STD-883C Compliant products only.

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage Vcc Input Voltage

-0.5 V to +7.0 V

Off-state Output Voltage

~1.5 V to +7.0 V

Storage Temperature **Power Dissipation**

-0.5 to Vcc +0.5 V -65°C to +150°C

1.0 W

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. This is a stress rating only; functional operation of the device at these limits or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure of the device to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

Commercial (C) Devices

Ambient Temperature (TA)

Operating in Free Air

Supply Voltage (Vcc) With Respect to Ground 0°C to +75°C

+4.50 V to +5.50 V

T-46-35

Operating ranges define those limits between which the functionality of the device is guaranteed.

### OPERATING CONDITIONS Commercial: $V_{CC} = 5 \text{ V} \pm 10\%$ , $T_A = 0^{\circ}\text{C}$ to $+70^{\circ}\text{C}$

| Parameter |                                               |        | -10  |      | -15  |      | -25  |      | -35  |      |      |

|-----------|-----------------------------------------------|--------|------|------|------|------|------|------|------|------|------|

| Symbol    | Parameter Description                         | Figure | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

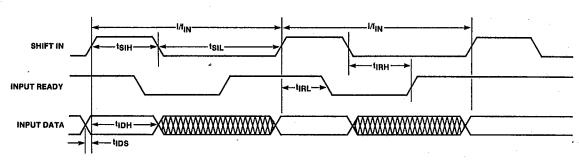

| fin       | Shift in rate                                 | 1      |      | 10   |      | 15   |      | 25   |      | 35   | MHz  |

| tsi#*     | Shift in HIGH time                            | 1      | 14   |      | . 14 |      | 8    |      | 8    |      | ns   |

| tsıL*     | Shift in LOW time                             | 1      | 25   |      | 25   |      | 8    |      | 8    |      | ns   |

| tios ·    | Input data setup to SI (Shift In)             | 1      | 0    |      | 0    |      | 0    |      | 0    |      | ns   |

| tidh      | Input data hold time from SI<br>(Shift In)    | 1      | 40   |      | 40   |      | 20   |      | 15   |      | ns   |

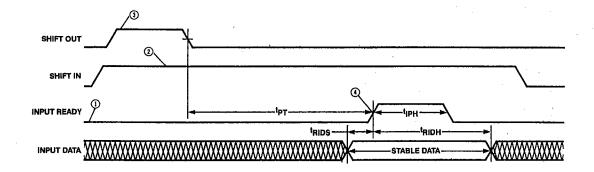

| trios     | Input data setup to IR (Input Ready)          | 3      | 0    |      | 0    |      | 5    |      | 2    |      | ns   |

| tridh     | Input data hold time from IR<br>(Input Ready) | 3      | 30   |      | 30   |      | 20   |      | 15   |      | ns   |

| four      | Shift out rate                                | 4      |      | 10   |      | 15   |      | 25   |      | 35   | MHz  |

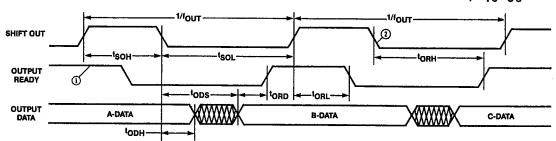

| tsoн*     | Shift out HIGH time                           | 4      | 24   |      | 21   |      | 8    |      | 8    |      | ns   |

| tsoL*     | Shift out LOW time                            | 4      | 25   |      | 25   |      | 8    |      | 8    |      | ns   |

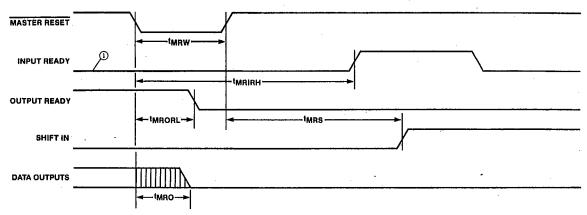

| tmrw .    | Master Reset pulse                            | 8      | 35   |      | 35   |      | 25   |      | 18   |      | ns   |

| tmrs      | Master Reset to SI                            | 8      | 65   |      | 65   |      | 10   |      | 7    |      | ns   |

<sup>\*</sup>See AC test and high-speed application note.

# DC CHARACTERISTICS over operating ranges unless otherwise specified

| Parameter | )                             |                                                                                                                                           | ••                                                                                                                                    |           | -10  |                   | 5    |               | 25   |           | 35   |     |

|-----------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------|------|-------------------|------|---------------|------|-----------|------|-----|

| Symbol    | Parameter Description         | Test Condition                                                                                                                            |                                                                                                                                       | Min.      | Max. | Min.              | Max. | Min.          | Max. | Min.      | Max. | Uni |

| ViL*      | Low-level input voltage       |                                                                                                                                           |                                                                                                                                       |           | 0.8  |                   | 0.8  |               | 0.8  |           | 0.8  | v   |

| VIH*      | High-level input voltage      |                                                                                                                                           |                                                                                                                                       | 2         |      | 2                 |      | -2            |      | 2         |      | V   |

| lin       | Input Current                 | Vcc = Max., GND <vin <vcc<="" td=""><td>-1</td><td>1</td><td>-1</td><td>1</td><td>-1</td><td>1</td><td>-1</td><td>1</td><td>μА</td></vin> |                                                                                                                                       | -1        | 1    | -1                | 1    | -1            | 1    | -1        | 1    | μА  |

| loz       | Off-state output current      | Vcc = Max.                                                                                                                                | GND <vout <vcc<="" td=""><td>5</td><td>5</td><td><b>-</b>5</td><td>5</td><td>-5</td><td>5</td><td>-5</td><td>5</td><td>μA</td></vout> | 5         | 5    | <b>-</b> 5        | 5    | -5            | 5    | -5        | 5    | μA  |

|           |                               | IOL = 20 μA                                                                                                                               |                                                                                                                                       | 0.1       |      | 0.1               | ,    | 0.1           |      | 0.1       | Ë    |     |

| VOL       | Vol. Low-level output voltage | Vcc = Min.                                                                                                                                | lOL ≈ 8 mA                                                                                                                            |           | 0.4  |                   | 0.4  |               | 0.4  |           | 0.4  | ۷   |

| Vон       | High-level output voltage     | V 14:                                                                                                                                     | юн = -20 µА                                                                                                                           | Vcc - 0.1 |      | Vcc - 0.1 Vcc - 0 |      | 0.1 Vcc - 0.1 |      | Vcc - 0.1 |      |     |

|           | migh-lever output voitage     | Vcc = Min.                                                                                                                                | Юн = -4 mA                                                                                                                            | 2.4       |      | 2.4               |      | 2.4           |      | 2.4       |      | ۷   |

| los**     | Output short-circuit current  | Vcc = Max.                                                                                                                                | Vo = 0 V                                                                                                                              | -90       | -20  | -90               | -20  | -90           | 20   | -90       | -20  | m/  |

| la-       | Standby supply current        |                                                                                                                                           | VIH = VCC<br>VIL = GND                                                                                                                |           | 100  |                   | 100  |               | 100  |           | 100  | μ.  |

| lcc       | Operating supply current      |                                                                                                                                           | VIH = Min.,<br>VIL = Max.<br>IN = fout = Max.                                                                                         |           | 35   |                   | 45   |               | 50   |           | 60   | m/  |

# SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                 | Figure | -1<br>Min |     | -1     |     |       | 5<br>Max. |              | 35   | 11    |

|---------------------|---------------------------------------|--------|-----------|-----|--------|-----|-------|-----------|--------------|------|-------|

| <del></del>         |                                       | riguie | Willi.    |     | MIIII. |     | MIII. |           | MID.         | мах. | Unit  |

| tirL•               | Shift in 1 to Input Ready Low         | 1      |           | 60  |        | 55  |       | 21        |              | 18   | ns    |

| tinn.               | Shift in ↓ to Input Ready HIGH        |        |           | 50  |        | 50  |       | 28        |              | 20   | ns    |

| torL*               | Shift Out ↑ to Output Ready LOW       |        |           | 55  |        | 45  |       | 19        |              | 18   | ns    |

| torn•               | Shift Out ↓ to Output Ready HIGH      | _      |           | 50  |        | 41  |       | 34        |              | 20   | ns    |

| todн                | Output Data Hold (previous word)      | 4      | 5         |     | 5      |     | 5     |           | 5            |      | ns    |

| tops                | Output Data Shift (next word)         |        |           | 35  |        | 30  |       | 34        |              | 20   | ns    |

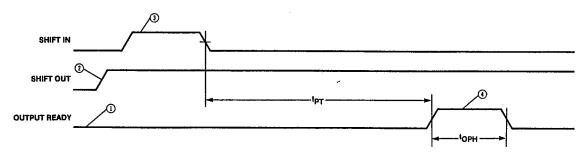

| <b>t</b> PT         | Data throughput                       | 3,6    | -         | 100 |        | 90  |       | 40        |              | 34   | ns    |

| <b>t</b> MRORL      | Master Reset ↓ to Output<br>Ready LOW |        |           | 100 |        | 100 |       | 35        |              | 28   | ns    |

| tmrirh              | Master Reset ↓ to Input<br>Ready HIGH | 8      |           | 100 |        | 100 |       | 35        |              | 28   | ns    |

| tmro                | Master Reset ↓ to Outputs LOW         |        |           | 35  |        | 35  |       | 25        |              | 22   | ns    |

| tıрн                | Input Ready pulse HIGH                | 3      | 19        |     | 16     |     | 8     |           | 8            |      | ns    |

| topн                | Output Ready pulse HIGH               | 6      | 14        |     | 14     |     | 8     |           | 8            |      | ns    |

| tord                | Output Ready ↑ to Data Valid          | 4      |           | -3  |        | -3  |       | 0         | <del>-</del> | 0    | ns    |

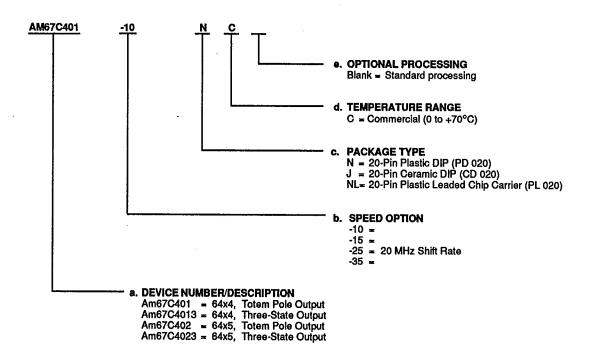

| tpHz**              |                                       |        |           | 25  |        | 25  |       | 15        |              | 12   | - 110 |

| tplz**              | Output Disable Delay                  |        | -         | 25  |        | 25  |       | 15        |              | 12   | ns    |

| tpzL**              |                                       | Α      |           | 30  |        | 30  |       | 20        |              | 15   |       |

| tpzH**              | Output Enable Delay                   | ŀ      |           | 30  |        | 30  |       | 20        |              | 15   | ns    |

<sup>\*</sup>These are absolute voltages with respect to GND and include all overshoots due to system and/or tester noise.

\*\*Not more than one output should be shortened at a time, and duration of the short circuit should not exceed one second.

<sup>\*</sup>See AC test and high-speed application note.

\*\*Enable/Disable delays refer to 67C4013/23 only.

#### **CAPACITANCES\***

| Ţ- | 46 | -3 |

|----|----|----|

|----|----|----|

| Parameter<br>Symbol | Parameter Description | Test Conditions                  | Min. | Max. | Unit |

|---------------------|-----------------------|----------------------------------|------|------|------|

| Cin                 | Input capacitance     | T <sub>A</sub> = 25°C, f = 1 MHz |      | 10   | pF   |

| Соит                | Output capacitance    | Vcc = 4.5 V                      |      | 7    | Ρ'   |

<sup>\*</sup>Not tested in production.

Figure A. Enable and Disable

#### Notes:

- Waveform 1 is for a data output with internal conditions such that the output is low except when disabled by the output control.

- Waveform 2 is for a data output with internal conditions such that the output is high except when disabled by the output control.

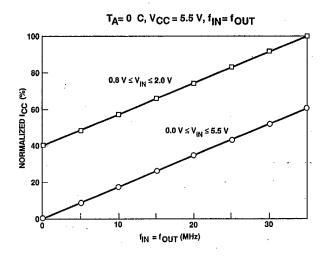

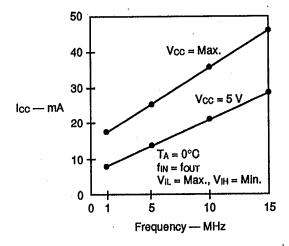

#### ICC vs. Frequency

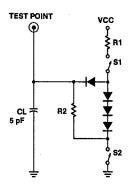

#### STANDARD AC TEST LOAD

# OUTPUT OF R2 TEST POINT

Input Pulse Amplitude = 3 V Input Rise and Fall Time (10%-90%) = 2.5 ns Measurements made at 1.5 V All Diodes are 1N916 or 1N3064

## **RESISTOR VALUES**

T-46-35

| lor  | R1    | R2     |

|------|-------|--------|

| 8 mA | 600 Ω | 1200 Ω |

#### THREE-STATE TEST LOAD

#### **FUNCTIONAL DESCRIPTION**

#### Data Input

The FIFO consists of a dual-port RAM and two ring counters for read and write. After power-up, the Master Reset should be pulsed LOW, which internally resets both the read and write counters. When the input Ready (IR) is HIGH, the FIFO is ready to accept DATA from the  $D_{\rm X}$  inputs. Data then present at the inputs is written into the first location of the RAM when Shift-In (SI) is brought HIGH. A SI HIGH signal causes the IR to go LOW. When the SI is brought LOW and the FIFO is not full, IR will go HIGH, indicating that more room is available. The write pointer now points to the next location in the RAM. If the memory is full, then the IR will remain LOW.

#### **Data Output**

Data is read from the  $O_X$  outputs. Just after the first shift-in, the first data word is available at the outputs, which is indicated by the Output Ready (OR) going HIGH. When the OR is HIGH, data may be shifted out by bringing the Shift-Out (SO) HIGH. A HIGH signal at SO causes the read pointer to point to the next location in the RAM, and also the OR to go LOW. Valid data is maintained while the SO is HIGH. When the SO is brought LOW, the OR goes HIGH, indicating the presence of new valid data. If the FIFO is emptied, OR stays LOW, and  $O_X$  remains as before, (i.e., data does not change if the FIFO is empty). A dual-port RAM inside the chip provides the capability of simultaneous and asynchronous writes (Shift-Ins) and reads (Shift-Outs).

#### **AC TEST AND HIGH-SPEED APP. NOTES**

Since the FIFO is a very-high-speed device, care must be exercised in the design of the hardware and the timing utilized within the design. Device grounding and decoupling is crucial to correct operation as the FIFO will respond to very small glitches due to long reflective lines, high capacitances and/or poor supply decoupling and grounding. Advanced Micro Devices recommends a monolithic ceramic capacitor of 0.1  $\mu$ F directly between VCC and GND with very short lead length. In addition, care must be exercised in how the timing is set up and how the parameters are measured. For example, since an AND gate function is associated with both the Shift-In-Input Ready combination, as well as the Shift-Out-Output Ready combination, timing measurements may be misleading; i.e., a rising edge of the Shift-In

pulse is not recognized until input Ready is HIGH. If Input Ready is not HIGH due to (a) too high a frequency, or (b) FIFO being full or affected by Master Reset, the Shift-In activity will be ignored. This will affect the device from a functional standpoint and will also cause the "effective" timing of Input Data Hold time (t<sub>IDH</sub>) and the next activity of Input Ready (t<sub>IRL</sub>) to be extended relative to Shift-In going HIGH. This same type of problem also relates to t<sub>IRH</sub>, t<sub>ORL</sub>, and t<sub>ORH</sub>. For high-speed applications, proper grounding technique is essential. In order to diminish timing ambiguities between the Shift-In-Input-Ready or Shift-Out-Output-Ready pairs when operating at high frequencies, it is recommended that the t<sub>SIH</sub> and t<sub>SOH</sub> pulse widths be as short as possible within the specified limits.

T-46-35

Figure 1. Input Timing

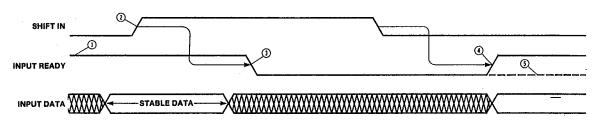

Figure 2. The Mechanism of Shifting Data into the FIFO

- ① Input Ready HIGH indicates space is available and a Shift-In pulse may be applied.

- 1 Input Data is loaded into the first available memory location.

- ① Input Ready goes LOW indicating this memory location is full.

- Shift-in going LOW allows Input Ready to sense the status of the next memory location. The next memory location is empty as indicated by Input Ready HIGH.

- (1) If the FIFO is already full then the Input Ready remains LOW. Note: Shift-In pulses applied while Input Ready is LOW will be ignored.

Figure 3. Data is Shifted in Whenever Shift In and Input Ready are Both HIGH

- (i) FIFO is initially full.

- 3 Shift In is held HIGH.

- 3 Shift Out pulse is applied. An empty location is detected by the internal pointers on the falling edge of SO.

- As soon as Input Ready becomes HIGH the Input Data is loaded into this location.

T-46-35

Figure 4. Output Timing

- ① The diagram assumes that the FIFO contains at least three words: A-Data (first input word), B-Data (second input word), and C-Data (third input word).

- ① Output data changes on the falling edge of SO after a valid Shift-Out Sequence, i.e., OR and SO are both high together.

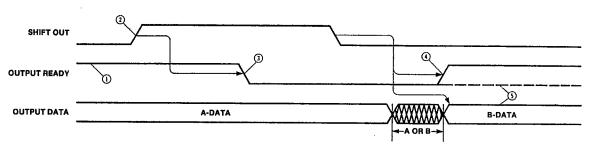

Figure 5. The Mechanism of Shifting Data Out of the FIFO

- ① Output Ready HIGH indicates that data is available and a Shift-Out pulse may be applied.

- ③ Shift-Out goes HIGH causing B-Data (second input word) to advance to the output register. Output data remains as valid A-Data while Shift-Out is HIGH.

- Output Ready goes LOW.

- Shift-out goes LOW causing Output Ready to go HIGH and new data (B) to appear at the data outputs.

- (A-Data) If the FIFO has only one word loaded (A-Data) then Output Ready stays LOW and the output data remains the same (A-Data)

Figure 6. tpT and tOPH Specification

- ① FIFO initially empty.

- ② Shift-Out held HIGH.

- ① Shift-In pulse applied. A full location is detected by the internal pointers on the falling edge of Shift-In.

- (1) As soon as Output Ready becomes HIGH, the word is shifted out.

Figure 7. Data is Shifted Out Whenever Shift Out and Output Ready are Both HIGH

- ① The internal logic does not detect the presence of any words in the FIFO.

- New data (A) arrives at the outputs.

- ① Output Ready goes HIGH indicating arrival of the new data.

- Since Shift Out is held HIGH, Output Ready goes immediately LOW.

- As soon as Shift Outgoes LOW the Output Data is subject to change. Output Ready will go HIGH or remain LOW depending on whether there are any additional words in the FIFO.

① FIFO is initially full.

Figure 8. Master Reset Timing

## NORMALIZED $I_{cc}$ vs FREQUENCY