## Dual IF car radio and audio DSP (N1F)

Rev. 07 — 28 April 2010

Product data sheet

## 1. General description

The SAF7741HV is a combined Intermediate-Frequency (IF) car radio and audio Digital Signal Processor (DSP) with several powerful cores integrated onto a single device. It combines analog IF input, digital radio and audio processing, sample-rate converters and digital and analog audio output to enhance listening clarity and noise suppression while reducing multipath channel effect.

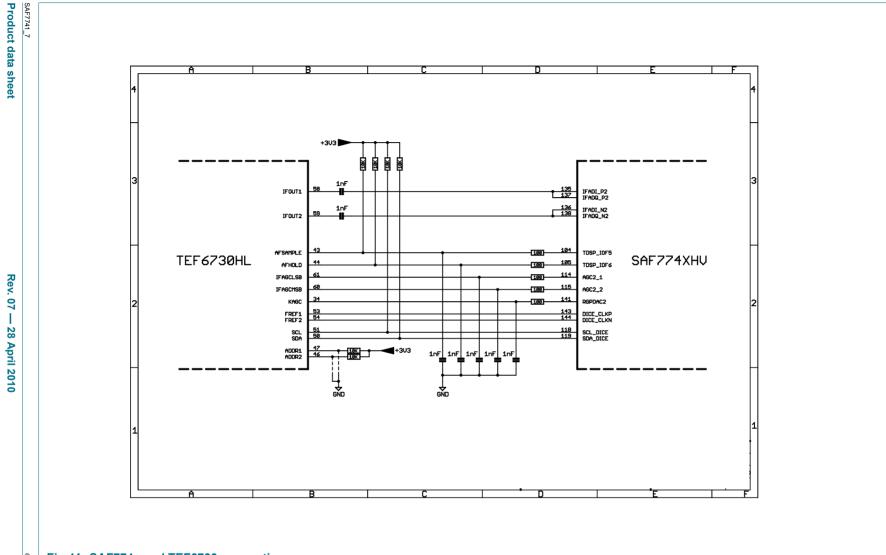

The SAF7741 offers user-specific functions which can be configured to match the software platform required by the systems of individual car-radio manufacturers, thus providing a high level of product differentiation. It is equipped to work with the TEF7000 and TEF6730 integrated tuners for analog and digital AM/FM decoding and sound processing

The SAF7741HV consists of two main processing blocks; one for radio and the other for audio. These blocks demodulate either the IF or the low-IF tuner output, delivering digital audio to internal Digital-to-Analog Converters (DACs). In addition to the main blocks there are a number of interfaces and dedicated sub-circuits.

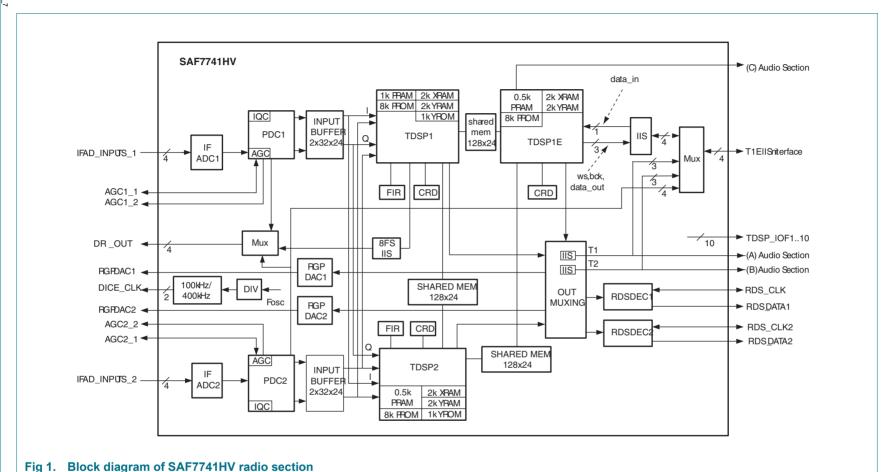

## 1.1 Radio processing

The IF radio block interfaces to the front-end tuner chips and supports either a so-called low-IF frequency (of 60 kHz or 300 kHz ) or an IF frequency of 10.7 MHz. Two tuner interfaces are supported, each of which is suitable for analog Frequency-Modulated/Amplitude-Modulated and Weatherband (FM/AM/WX) radio reception as well as reception of encoded digital signals such as HD Radio and Digital Radio Mondiale (DRM).

Signals received from the tuner front-end chips are digitized with integrated Intermediate-Frequency Analog-to-Digital Converters (IFADCs). The resulting digital signals are then down-sampled, error-corrected and filtered in the digital domain to be suitable for further radio and audio processing by the DSPs.

The low-IF interface to the tuner chip combined with the high level of integration allows cost-effective implementation of the entire tuner/DSP application on a main radio Printed Circuit Board (PCB).

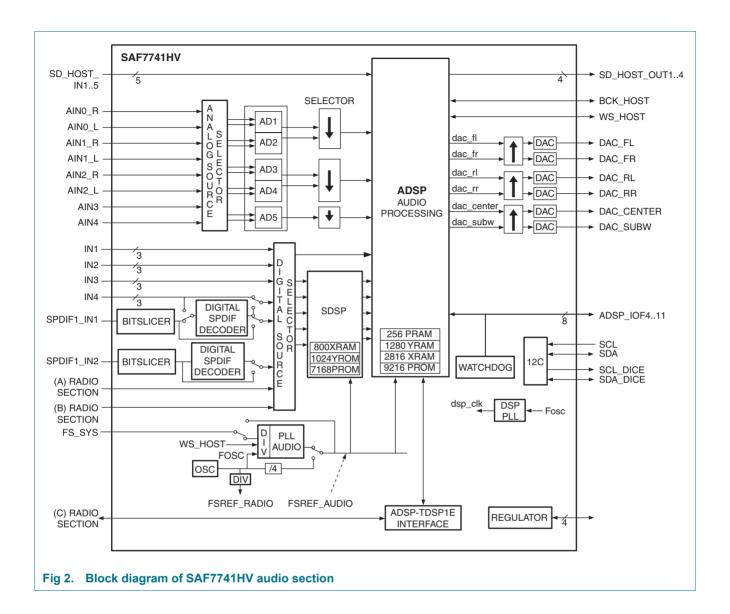

## 1.2 Audio processing

The audio processing block receives either external digital signals, or analog signals which are then digitized by the integrated ADCs. Together with the internal radio audio signals these inputs are available for further audio processing such as equalization, tone control and volume control. The output signals of the audio processing block are provided in digital format on the Host IIS outputs and in analog format on the DAC outputs.

#### 2. **Features**

### 2.1 Hardware features

SAF7741HV hardware is configured by firmware and host software to meet specific customer requirements. The firmware is defined by the Read-Only Memory (ROM) code associated with each DSP.

**Remark:** The list below describes the maximum hardware configuration. Customers should consult with NXP to identify the best method of supporting their own particular requirements.

- Two IF data-paths of either 2 × IF 10.7 MHz or 2 × low IF 300 kHz input **Remark:** The combination of 1 x IF and 1 x low IF is not supported.

- Two 5th order Sigma-Delta ( $\Sigma\Delta$ ) IF ADCs for FM/AM/WB (Weather-band) and digital radio at either IF = 10.7 MHz or low IF = 300 kHz

- IF signal quadrature-mixing and down-sampling with signal level generation

- Automatic Gain Control (AGC) of the radio front-end chip in three steps (6 dB for each step) for the TEF6730 tuner and seven steps (6 dB for each step) for the TEF7000 tuner

- AGC control of the TEF6730 tuner front-end PIN diodes, with an analog signal via the Radio General-Purpose DAC (RGP DAC) output: one DAC for each radio data path

- Integrated IF filter with bandwidth of 100 kHz or 400 kHz

- Two wideband outputs for external digital radio decoding; one output for each data-path

- Two Radio Data System (RDS) decoders

- Five bit-stream, 3rd order audio,  $\Sigma\Delta$  ADCs with an anti-aliasing broadband input-filter

- Eight configurable analog inputs (differential/stereo/mono) connected to any of the five ADCs using an analog switchbox

- Dedicated DSP for the Sample Rate Converter (SRC)

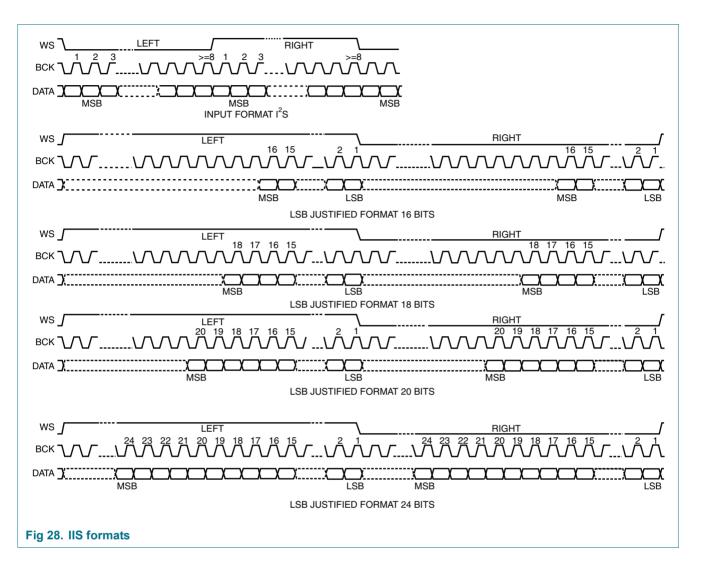

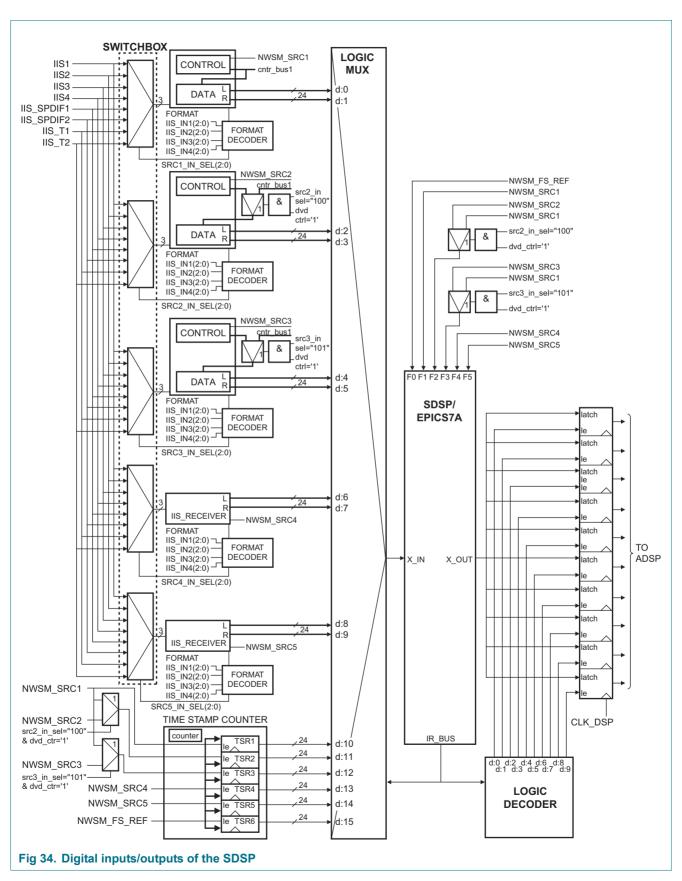

- Audio Host Inter-IC Sound (IIS) Input/Output (I/O) port, with eight/ten outputs and eight inputs with an option for slaving the DSP to an external master sample-rate

- Audio Host IIS Bit-Clock (BCK) and Word-Size (WS) available simultaneously at full-rate and half-rate

- Four independent IIS inputs and two independent digital Sony/Philips Digital Interface Format (SPDIF) inputs also configurable for Digital Versatile Disc/Digital Video Device (DVD) multi-channel data inputs

- Radio Host IIS master with separate data in and out lines

- IIS output with buffer for eight samples for radio applications

- WatchDog (WDOG) to monitor execution of the DSP main software loop

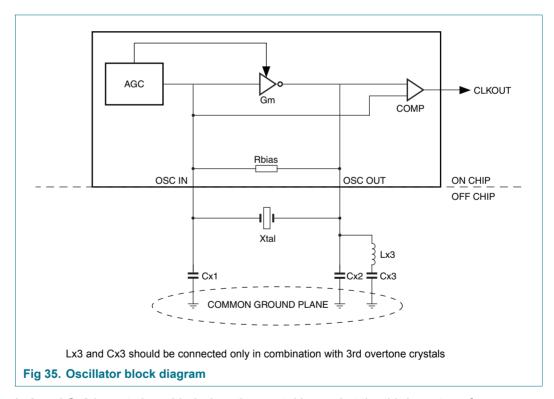

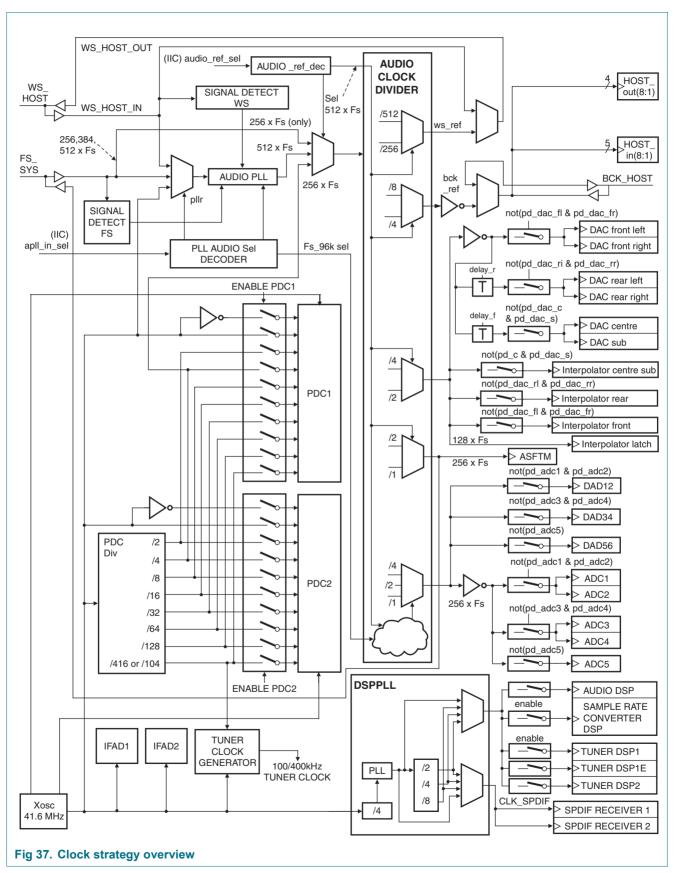

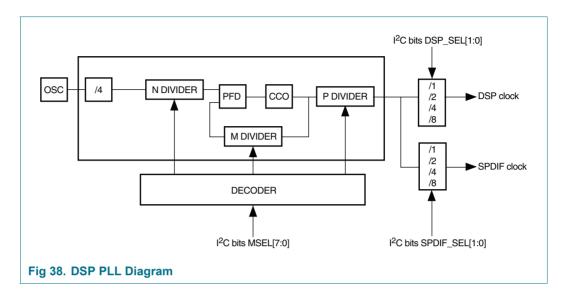

- Phase-Lock Loop (PLL) to generate the DSP clock from the oscillator crystal

- PLL to generate the audio reference sample-rate clock

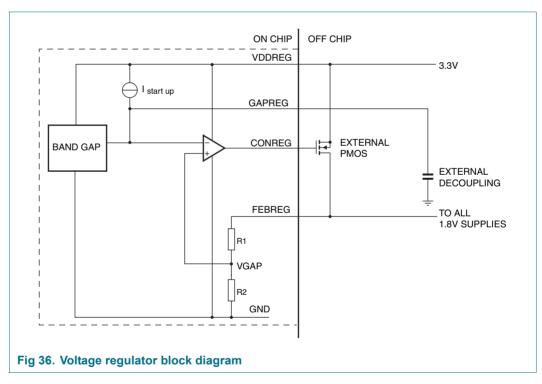

- Internal voltage regulator for the 1.8 V supply

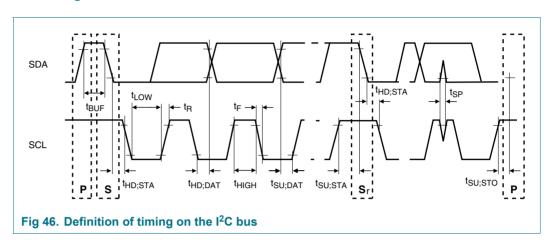

- I<sup>2</sup>C (Inter-IC Communication) bus-controlled

- Possibility of powering down unused blocks to reduce power dissipation

- Qualified in accordance with AEC-Q100

3 of 83

## Dual IF car radio and audio DSP (N1F)

#### 2.2 Software Features

The following software features are available for the SAF7741HV:

- Improved FM weak-signal processing

- Integrated 19 kHz Multiplexed (MPX) filter and de-emphasis

- Electronic adjustment of FM/AM level and FM channel separation

- Variable IF bandwidth. This is controlled partly by the DSP software and depends on the quality of the reception

- Selective IF bandwidth for wideband FM, FM Weatherband and AM

- Variable IF bandwidth on FM, dependent on the adjacent channel interference

- Digital stereo decoder for FM and AM

- Advanced digital Interference Absorption Circuit (IAC) for FM and AM

- Digital Automatic Frequency Control (AFC)

- RDS demodulation

- Pause detection for RDS updates with audio mute during RDS updates

- Baseband audio processing (treble, bass, balance, fader and volume)

- Maximum of five audio SRCs

- Dynamic loudness or bass boost

- Audio level meter

- Compact Disc (CD) dynamics compressor/expander

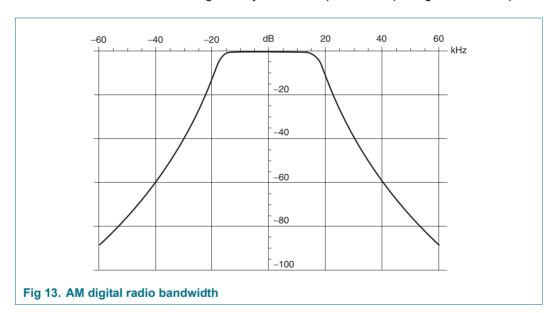

- Improved AM processing with soft mute, high cut control, 6th order low-pass filtering and AM audio IAC

- Soft audio mute

- Extended chime functions

- Signal level, noise and multi-path detection for AM/FM signal quality information

- AM audio AGC

- AGC click suppression in AM mode

## 3. Applications

The SAF7741HV is designed for use in high-performance car radio systems.

## 4. Ordering information

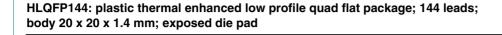

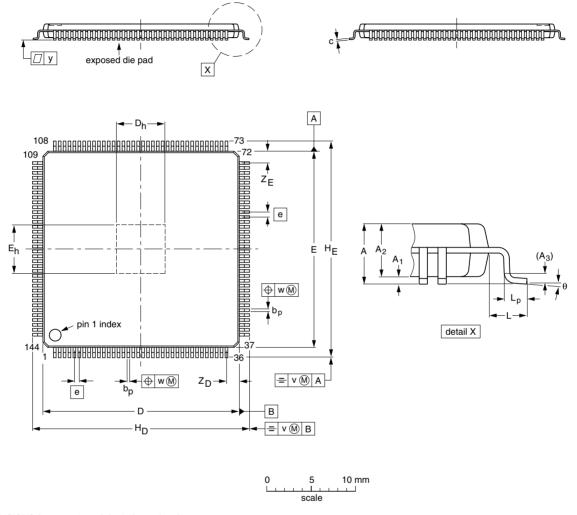

Table 1. Ordering information

| Type Number | Package  |                                                                                    |         |  |

|-------------|----------|------------------------------------------------------------------------------------|---------|--|

|             | Name     | Description                                                                        | Version |  |

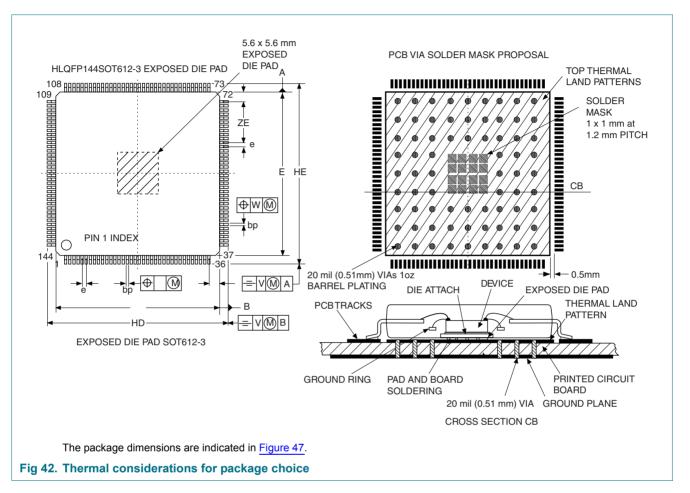

| SAF7741HV   | HLQFP144 | 144 leads; plastic thermal enhanced low profile quad flat package; exposed die pad | N115F   |  |

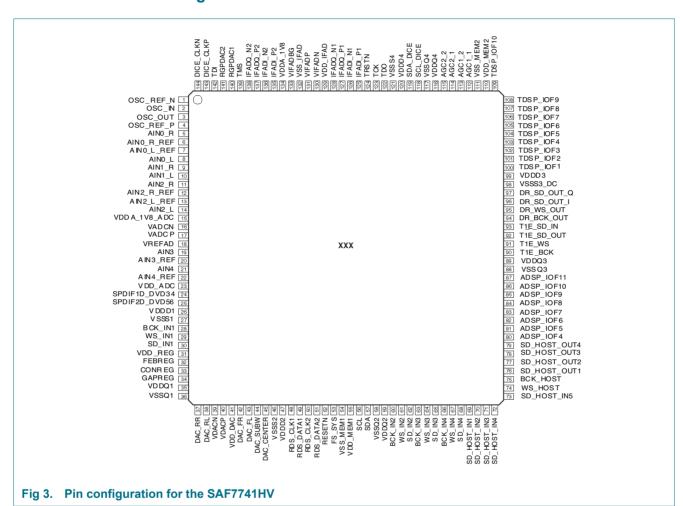

## 6. Pinning information

## 6.1 Pinning

Table 2. Pin allocation table

| Pin Name   | Pin<br>Number | Description                                                           | Pin Type                        |

|------------|---------------|-----------------------------------------------------------------------|---------------------------------|

| OSC_REF_N  | 1             | Ground reference for oscillator, PLLs and tuner clock generator       | vssco                           |

| OSC_IN     | 2             | Crystal oscillator input                                              | apio                            |

| OSC_OUT    | 3             | Crystal oscillator output                                             | apio                            |

| OSC_REF_P  | 4             | 1.8 V reference supply for oscillator, PLLs and tuner clock generator | vddco                           |

| AIN0_R     | 5             | Right channel analog audio input 0                                    | apio                            |

| AIN0_R_REF | 6             | Right common mode reference audio input 0                             | apio                            |

| AIN0_L_REF | 7             | Left common mode reference audio input 0                              | apio                            |

| AIN0_L     | 8             | Left channel analog audio input 0                                     | apio                            |

| AIN1_R     | 9             | Right channel analog audio input 1                                    | apio                            |

| AIN1_L     | 10            | Left channel analog audio input 1                                     | apio                            |

| AIN2_R     | 11            | Right channel analog audio input 2                                    | apio                            |

| SAF7741 7  |               |                                                                       | © NXP B.V. 2010. All rights res |

Table 2. Pin allocation table ...continued

| Pin Name     | Pin<br>Number | Description                                                                              | Pin Type     |

|--------------|---------------|------------------------------------------------------------------------------------------|--------------|

| AIN2_R_REF   | 12            | Right common mode reference audio input 2                                                | apio         |

| AIN2_L_REF   | 13            | Left common mode reference audio input 2                                                 | apio         |

| AIN2_L       | 14            | Left channel analog audio input 2                                                        | apio         |

| VDDA_1V8_ADC | 15            | 1.8 V supply for ADC                                                                     | vddco        |

| VADCN        | 16            | Ground reference for audio ADCs and RGPDACs                                              | apio         |

| VADCP        | 17            | Positive reference voltage for Audio ADCs and RGPDACs                                    | apio         |

| VREFAD       | 18            | Common mode reference voltage ADCs                                                       | apio         |

| AIN3         | 19            | Analog audio input 3                                                                     | apio         |

| AIN3_REF     | 20            | Common mode reference audio input 3                                                      | apio         |

| AIN4         | 21            | Analog audio input 4                                                                     | apio         |

| AIN4_REF     | 22            | Common mode reference audio input 4                                                      | apio         |

| VDD_ADC      | 23            | 3.3 V supply for audio ADCs                                                              | vddco        |

| SPDIF_IN1    | 24            | Input 1 SPDIF analog / input DVD-A channels 3 and 4 🗓                                    | apio         |

| SPDIF_IN2    | 25            | Input 2 SPDIF analog / input DVD-A channels 5 and 6 [1]                                  | apio         |

| VDDD1        | 26            | 1.8 V positive supply (digital core)                                                     | vddi         |

| VSSS1        | 27            | Ground supply (digital core)                                                             | vssis        |

| BCK_IN1      | 28            | Inter-IC Sound (I <sup>2</sup> S) source 1 Bit Clock input                               | bpts5ptpht5v |

| WS_IN1       | 29            | I <sup>2</sup> S source 1 Word Select input                                              | bpts5ptpht5v |

| SD_IN1       | 30            | I <sup>2</sup> S source 1 data input/input DVD-A channels 1 and 2                        | bpts5ptpht5v |

| VDD_REG      | 31            | 3.3 V supply for regulator                                                               | vddco        |

| FEBREG       | 32            | Feedback input monitoring the 1.8 V                                                      | apio         |

| CONREG       | 33            | Control output for external Positive-channel Metal Oxide Semiconductor (PMOS) transistor | apio         |

| GAPREG       | 34            | Decoupling for regulator bandgap voltage                                                 | apio         |

| VDDQ1        | 35            | 3.3 V positive supply (peripheral cells)                                                 | vdde         |

| VSSQ1        | 36            | Ground supply (peripheral cells)                                                         | vsse         |

| DAC_RR       | 37            | Audio output for the rear-right speaker                                                  | apio         |

| DAC_RL       | 38            | Audio output for the rear-left speaker                                                   | apio         |

| VDACN        | 39            | Ground reference voltage for the Audio DACs (ADAC)                                       | apio         |

| VDACP        | 40            | Positive reference voltage for the Audio DACs (ADAC)                                     | apio         |

| VDD_DAC      | 41            | 3.3 V supply for the Audio DACs (ADAC)                                                   | vddco        |

| DAC_FR       | 42            | Audio output for the front-right speaker                                                 | apio         |

| DAC_FL       | 43            | Audio output for the front-left speaker                                                  | apio         |

| DAC_SUBW     | 44            | Audio output for the sub-woofer                                                          | apio         |

| DAC_CENTER   | 45            | Audio output for the centre speaker                                                      | apio         |

| VSSS2        | 46            | Ground supply (digital core)                                                             | vssis        |

| VDDD2        | 47            | 1.8 V positive supply (digital core)                                                     | vddi         |

| RDS_CLK1     | 48            | RDS bit clock (CLK) output 1/RDS external clock input 1                                  | bpts5ptpht5  |

| RDS_DATA1    | 49            | RDS data output 1                                                                        | bpts5ptpht5  |

| RDS_CLK2     | 50            | RDS bit clock output 2/RDS external clock input 2                                        | bpts5ptpht5v |

|              |               |                                                                                          |              |

Table 2.

Pin allocation table ...continued

| Pin Name     | Pin<br>Number | Description                                                                    | Pin Type     |

|--------------|---------------|--------------------------------------------------------------------------------|--------------|

| RDS_DATA2    | 51            | RDS data output 2                                                              | bpts5ptpht5v |

| RESETN       | 52            | General reset of chip (active low)                                             | bpts5ptpht5v |

| FS_SYS       | 53            | Fs system clock in/output                                                      | bpts10thdt5v |

| VSS_MEM1     | 54            | Ground supply (digital core)                                                   | vssi         |

| VDD_MEM1     | 55            | 1.8 V positive supply (memories)                                               | vddcobf      |

| SCL          | 56            | Serial clock input I <sup>2</sup> C bus                                        | iic3m4sclt5v |

| SDA          | 57            | Serial data input/output I <sup>2</sup> C bus                                  | iic3m4sdat5v |

| VSSQ2        | 58            | Ground supply (peripheral cells)                                               | vsse         |

| VDDQ2        | 59            | 3.3 V positive supply (peripheral cells)                                       | vdde         |

| BCK_IN2      | 60            | IIS source 2 Bit Clock input                                                   | bpts5ptpht5v |

| WS_IN2       | 61            | IIS source 2 Word Select input                                                 | bpts5ptpht5v |

| SD_IN2       | 62            | IIS source 2 data input                                                        | bpts5ptpht5v |

| BCK_IN3      | 63            | IIS source 3 Bit Clock input                                                   | bpts5ptpht5v |

| WS_IN3       | 64            | IIS source 3 Word Select input                                                 | bpts5ptpht5v |

| SD_IN3       | 65            | IIS source 3 data input                                                        | bpts5ptpht5v |

| BCK_IN4      | 66            | IIS source 4 Bit Clock input                                                   | bpts5ptpht5v |

| WS_IN4       | 67            | IIS source 4 Word Select input                                                 | bpts5ptpht5v |

| SD_IN4       | 68            | IIS source 4 data input/input SPDIF 1 digital                                  | bpts5ptpht5v |

| SD_HOST_IN1  | 69            | Host I <sup>2</sup> S 1 data input                                             | bpts5ptpht5v |

| SD_HOST_IN2  | 70            | Host I <sup>2</sup> S 2 data input                                             | bpts5ptpht5v |

| SD_HOST_IN3  | 71            | Host I <sup>2</sup> S 3 data input                                             | bpts5ptpht5v |

| SD_HOST_IN4  | 72            | Host I <sup>2</sup> S 4 data input                                             | bpts5ptpht5v |

| SD_HOST_IN5  | 73            | Host I <sup>2</sup> S 5 data input                                             | bpts5ptpht5v |

| WS_HOST      | 74            | Host I <sup>2</sup> S Word Select output/input                                 | bpts10thdt5v |

| BCK_HOST     | 75            | Host I <sup>2</sup> S Bit Clock output/input                                   | bpts10thdt5v |

| SD_HOST_OUT1 | 76            | Host I <sup>2</sup> S 1 data output                                            | bpts10thdt5v |

| SD_HOST_OUT2 | 77            | Host I <sup>2</sup> S 2 data output                                            | bpts10thdt5v |

| SD_HOST_OUT3 | 78            | Host I <sup>2</sup> S 3 data output                                            | bpts10thdt5v |

| SD_HOST_OUT4 | 79            | Host I <sup>2</sup> S 4 data output                                            | bpts10thdt5v |

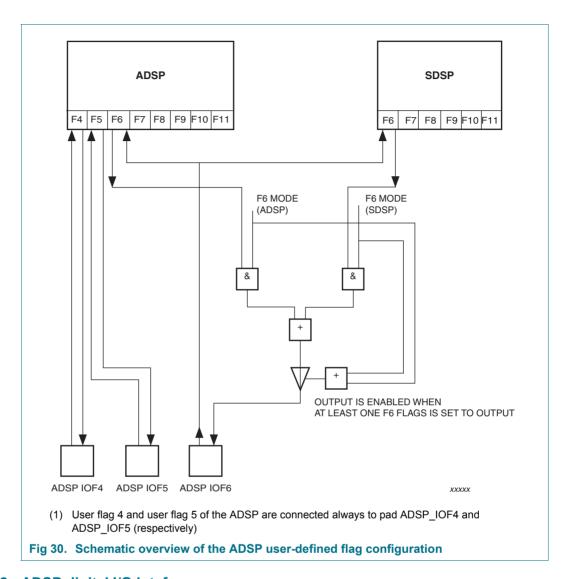

| ADSP_IOF4    | 80            | Audio DSP (ADSP) general purpose I/O flag 4                                    | bpts5ptpht5v |

| ADSP_IOF5    | 81            | ADSP general purpose I/O flag 5                                                | bpts5ptpht5v |

| ADSP_IOF6    | 82            | Audio/SCR DSP general purpose I/O flag 6                                       | bpts5ptpht5v |

| ADSP_IOF7    | 83            | Audio/SRC DSP general purpose I/O flag 7                                       | bpts5ptpht5v |

| ADSP_IOF8    | 84            | Audio/SRC DSP general purpose I/O flag 8                                       | bpts5ptpht5v |

| ADSP_IOF9    | 85            | Audio/SRC DSP general purpose I/O flag 9                                       | bpts5ptpht5v |

| ADSP_IOF10   | 86            | Audio/SRC DSP general purpose I/O flag 10                                      | bpts5ptpht5v |

| ADSP_IOF11   | 87            | Audio/SRC DSP general purpose I/O flag 11                                      | bpts5ptpht5v |

| VSSQ3        | 88            | Ground supply (peripheral cells)                                               | vsse         |

| VDDQ3        | 89            | 3.3 V positive supply (peripheral cells)                                       | vdde         |

| T1E_BCK      | 90            | Tuner I <sup>2</sup> S BCK output / digital radio interface 2 bit clock output | bpts10thdt5v |

Table 2. Pin allocation table ...continued

| Pin Name    | Pin<br>Number | Description                                                                                                                             | Pin Type     |

|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------|

| T1E_WS      | 91            | Tuner I <sup>2</sup> S WS output / digital radio interface 2 word-select output                                                         | bpts10thdt5v |

| T1E_SD_OUT  | 92            | Tuner $I^2S$ Serial data output / Serial data output digital radio interface 2 word select signal                                       | bpts10thdt5v |

| T1E_SD_IN   | 93            | Tuner I <sup>2</sup> S Serial data input / Serial data output digital radio interface 2 Q-signal                                        | bpts10thdt5v |

| DR_BCK_OUT  | 94            | Digital radio interface 1 bit clock output                                                                                              | bpts10thdt5v |

| DR_WS_OUT   | 95            | Digital radio interface 1 word-select output                                                                                            | bpts10thdt5v |

| DR_SD_OUT_I | 96            | Serial data output digital radio interface 1 I-signal                                                                                   | bpts10thdt5v |

| DR_SD_OUT_Q | 97            | Serial data output digital radio interface 1 Q-signal                                                                                   | bpts10thdt5v |

| VSSS3_DC    | 98            | Digital core DC ground connection                                                                                                       | vssis        |

| VDDD3       | 99            | 1.8 V positive supply (digital core)                                                                                                    | vddi         |

| TDSP_IOF1   | 100           | Tuner DSP (TDSP) general purpose I/O flag 1                                                                                             | bpts5ptpht5v |

| TDSP_IOF2   | 101           | Tuner DSP general purpose I/O flag 2                                                                                                    | bpts5ptpht5v |

| TDSP_IOF3   | 102           | Tuner DSP general purpose I/O flag 3                                                                                                    | bpts5ptpht5v |

| TDSP_IOF4   | 103           | Tuner DSP general purpose I/O flag 4                                                                                                    | bpts5ptpht5v |

| TDSP_IOF5   | 104           | Tuner DSP general purpose I/O flag 5                                                                                                    | bpts5ptpht5v |

| TDSP_IOF6   | 105           | Tuner DSP general purpose I/O flag 6                                                                                                    | bpts5ptpht5v |

| TDSP_IOF7   | 106           | Tuner DSP general purpose I/O flag 7                                                                                                    | bpts5ptpht5v |

| TDSP_IOF8   | 107           | Tuner DSP general purpose I/O flag 8                                                                                                    | bpts5ptpht5v |

| TDSP_IOF9   | 108           | Tuner DSP general purpose I/O flag 9                                                                                                    | bpts5ptpht5v |

| TDSP_IOF10  | 109           | Tuner DSP general purpose I/O flag 10                                                                                                   | bpts5ptpht5v |

| VDD_MEM2    | 110           | 1.8 V positive supply (memories)                                                                                                        | vddco        |

| VSS_MEM2    | 111           | Ground supply (digital core)                                                                                                            | vssi         |

| AGC1_1      | 112           | Command input from TEF7000 connected to IFAD1 / Least Significant Bit (LSB) gain control output to TEF6730 tuner connected to IFAD1     | bpts5ptpht5v |

| AGC1_2      | 113           | Request output to TEF7000 tuner connected to IFAD1 / Most Significant Bit (MSB) gain control output to TEF6730 tuner connected to IFAD1 | bpts5ptpht5v |

| AGC2_1      | 114           | Command input from TEF7000 connected to IFAD2 / Least Significant Bit (LSB) gain control output to TEF6730 tuner connected to IFAD2     | bpts5ptpht5v |

| AGC2_2      | 115           | Request output to TEF7000 tuner connected to IFAD2 / Most Significant Bit (MSB) gain control output to TEF6730 tuner connected to IFAD2 | bpts5ptpht5v |

| VDDQ4       | 116           | 3.3 V positive supply (peripheral cells)                                                                                                | vdde         |

| VSSQ4       | 117           | Ground supply (peripheral cells)                                                                                                        | vsse         |

| SCL_DICE    | 118           | SCL output of the tuner I <sup>2</sup> C bus                                                                                            | iic3m4sclt5v |

| SDA_DICE    | 119           | SDA input/output of the tuner I <sup>2</sup> C bus                                                                                      | iic3m4sdat5v |

| VDDD4       | 120           | 1.8 V positive supply (digital core)                                                                                                    | vddi         |

| VSSS4       | 121           | Ground supply (digital core)                                                                                                            | vssis        |

| TDO         | 122           | JTAG Test control data output                                                                                                           | bpts5ptpht5v |

| TCK         | 123           | JTAG Test clock                                                                                                                         | bpts5ptpht5v |

| TRSTN       | 124           | JTAG Test reset, active low                                                                                                             | bpts5ptpht5v |

| IFADI_P1    | 125           | Positive phase of the first differential IF I input                                                                                     |              |

| IFADI_N1    | 126           | Negative phase of the first differential IF I input                                                                                     | aprf3v3      |

Table 2.

Pin allocation table ...continued

| Pin Name  | Pin<br>Number | Description                                                                | Pin Type     |

|-----------|---------------|----------------------------------------------------------------------------|--------------|

| IFADQ_P1  | 127           | Positive phase of the first differential IF Q input                        | aprf3v3      |

| IFADQ_N1  | 128           | Negative phase of the first differential IF Q input                        | aprf3v3      |

| VDD_IFAD  | 129           | 3.3 V supply for IF ADCs and RGPDACs                                       | vddco        |

| VIFADN    | 130           | Ground reference voltage for IF ADCs                                       | apio         |

| VIFADP    | 131           | Decoupling for IF ADCs positive reference voltage                          | apio         |

| VSS_IFAD  | 132           | Ground supply for IF ADCs and RGPDACs                                      | vssco        |

| VIFADBG   | 133           | Decoupling for IF ADCs bandgap voltage                                     | apio         |

| VDDA_1V8  | 134           | 1.8 V supply for IFADC and Audio ADCs                                      | vddco        |

| IFADI_P2  | 135           | Positive phase of the second differential IF I input                       | aprf3v3      |

| IFADI_N2  | 136           | Negative phase of the second differential IF I input                       | aprf3v3      |

| IFADQ_P2  | 137           | Positive phase of the second differential IF Q input                       | aprf3v3      |

| IFADQ_N2  | 138           | Negative phase of the second differential IF Q input                       | aprf3v3      |

| TMS       | 139           | JTAG Test mode select                                                      | bpts5ptpht5v |

| RGPDAC1   | 140           | RGP DAC 1 output                                                           | apio         |

| RGPDAC2   | 141           | RGP DAC 2 output                                                           | apio         |

| TDI       | 142           | JTAG Test control data input                                               | bpts5ptpht5v |

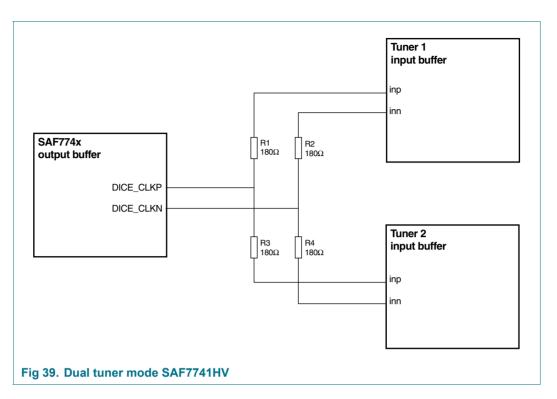

| DICE_CLKP | 143           | 100 kHz/400 kHz clock reference output to TEF6730/TEF7000 tuner (positive) | apio         |

| DICE_CLKN | 144           | 100 kHz/400 kHz clock reference output to TEF6730/TEF7000 tuner (negative) | apio         |

<sup>[1]</sup> The maximum input voltage is 3.3 volts.

## 6.2 Pin description

Table 3. Pad name description

| Pad Name       | Description                                                                                                                                                 |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IICT5V         |                                                                                                                                                             |

| iic3m4sdat5v   | IIC pad: 5 V-tolerant; data signal                                                                                                                          |

| iic3m4sclt5v   | IIC pad: 5 V-tolerant; clock signal                                                                                                                         |

| IOT5V          |                                                                                                                                                             |

| bpts5ptpht5v   | Bi-directional pad; plain input; 3-state output; SSO control; TTL with programmable hysteresis; programmable pull-up and pull-down, repeater; 5 V- tolerant |

| bpts10thdt5v   | Bi-directional pad; plain input; 3-state output; 10 ns slew-rate control; TTL with hysteresis; pull-down; 5 V-tolerant                                      |

| IO3V3          |                                                                                                                                                             |

| apio           | Analog pad; analog input/output for RF applications; ESD diode to VDD supply                                                                                |

| aprf           | Analog pad; analog input/output for RF applications; ESD diode to VDDE supply                                                                               |

| aprf3v3        | Analog pad; analog supply for high-voltage application; high trigger-voltage ESD protection                                                                 |

| IO3V3 (supply) |                                                                                                                                                             |

| vddco          | VDD pad connected to CORE VDD                                                                                                                               |

| vddcobf        | VDD pad connected to CORE VDD with BigFET protection                                                                                                        |

| vdde           | VDD pad connected to external (noisy) VDD supply rail                                                                                                       |

| SAF7741 7      | © NXP B.V. 2010. All rights reserv                                                                                                                          |

Table 3. Pad name description ... continued

| Pad Name | Description                                                                                        |

|----------|----------------------------------------------------------------------------------------------------|

| vddi     | VDD pad connected to CORE VDD and internal VDD supply rail in I/O ring                             |

| vssi     | VSS pad connected to CORE VSS and internal VSS supply rail in I/O ring                             |

| vsse     | VSS pad connected to external (noisy) VSS supply rail                                              |

| vssis    | VSS pad connected to CORE VSS, internal VSS supply rail in I/O ring and substrate rail in I/O ring |

| vssco    | VSS pad connected to CORE VSS                                                                      |

## 7. Functional description

## 7.1 Radio subsystem

The complete radio system is able to receive FM, AM, Weatherband, RDS and FM/AM digital radio. The SAF7741HV radio section will incorporate the following features (see Figure 1):

- Two IFADCs to digitize the incoming analog IF signals from the tuner(s)

- Two Primary Decimation Chains (PDCs) for analog and digital radio reception, including digital mixing to Zero IF (ZIF)

- Software-based radio functionality running on one or more DSPs depending on the features set and dual or single tuner usage

The IFADC digitizes the incoming Near-Zero Intermediate Frequency (NZIF) signals. The IFADC is a baseband  $\Sigma\Delta$  ADC.

The PDC decimates the incoming data stream by a factor of 128 before passing it to the software radio for processing.

For digital radio reception the PDC decimates the incoming data stream by 64 before it is forwarded to the external co-processor.

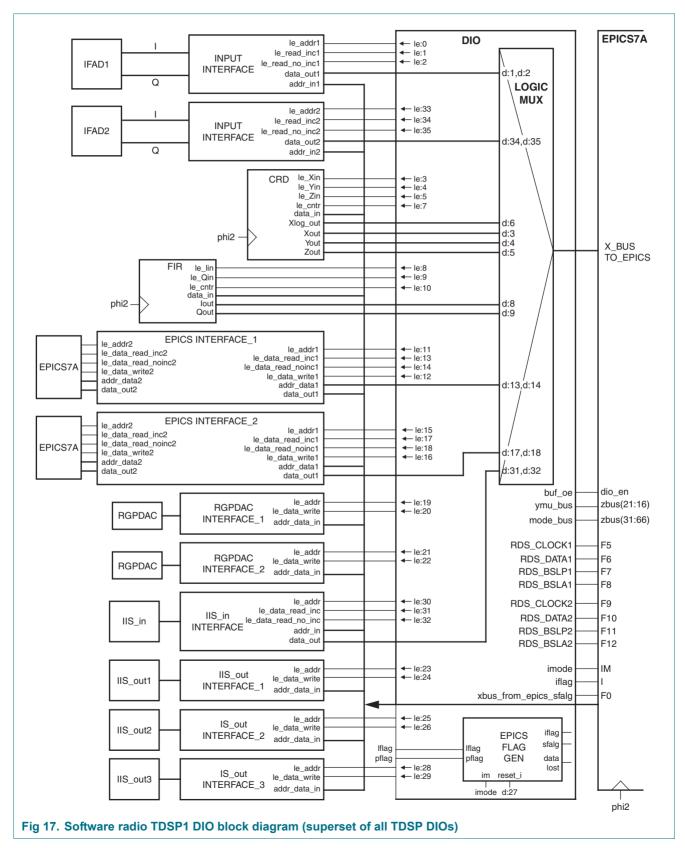

The software radio consists of three Tuner DSPs: TDSP1, TDSP2 and TDSP1E. All three TDSPs have a basically identical structure, but TDSP1 and TDSP2 are extended with:

- A Finite Impulse Response (FIR) filter

- CORDIC (COordinate Rotation Digital Calculation) Rotate and De-rotate (CRD)

TDSP1E is extended with a CRD only. Each FIR (controlled by the TDSP) is used for variable bandwidth control and for the Polar-to-Rectangular (P->R), Rectangular-to-Polar (R->P) and DIV conversions that will be used for demodulation. Added to this block is a 2LOG(LD(x)) function.

In addition, a Radio General-Purpose DAC (RGPDAC) and an RDS decoder are included for each tuner channel.

The SAF7741HV chip is capable of handling full dual radio. Depending on the firmware, several such configurations are possible:

Dual radio with two stereo-audio output channels. The attainable performance depends on the DSP tuner firmware. The available feature set is less than that for one-channel radio

- Dual tuner, which offers antenna, phased-array or MPX diversity

- Single tuner on the smallest possible hardware set: preferably one DSP

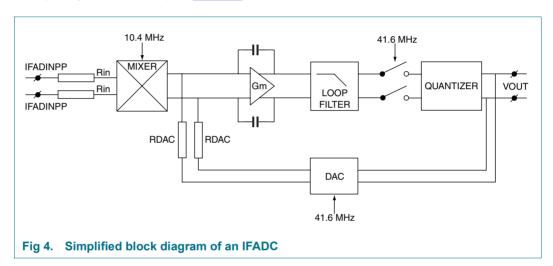

#### **7.1.1 IFADCs**

For each tuner path two fully differential  $\Sigma\Delta$  IFADCs are used for the I and Q paths. For each IFADC two fully differential input nodes are fed with a 300 kHz input signal. This design provides good suppression of even harmonics. The noise is shaped by a 5th order loop filter to get sufficient resolution in the band of interest, and for complex filtering the input signal of the I and Q paths has a 90° phase shift.

The IFADCs are sampled by a 41.6 MHz clock. The output is a 1-bit bitstream signal with a frequency of 41.6 MHz (see Figure 4).

### 7.1.1.1 TEF6730 tuner compatibility mode

In this mode the IF input signal is 10.7 MHz differential. The mixer is in front of the IFADC, and this converts the input signal down to 300 kHz using a quadrature 10.4 MHz square wave. The 300 kHz down-converted signal is then fed to the IFADCs as I and Q signals.

Switching to TEF6730 tuner compatibility mode is performed via the I<sup>2</sup>C interface and is only available to the microprocessor.

### 7.1.2 Primary decimation chain

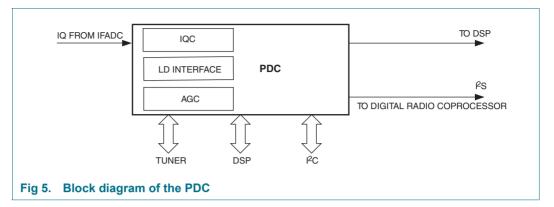

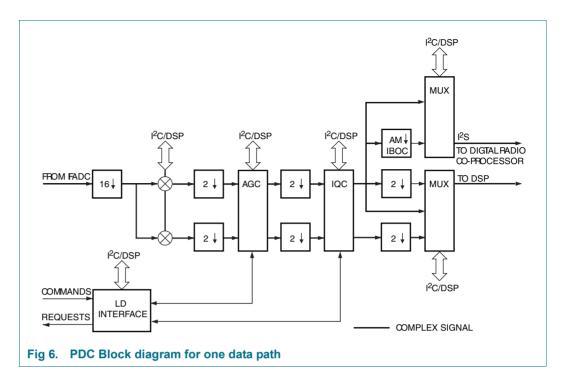

The PDC (see <u>Figure 5</u>) decimates the incoming sample rate from the IFADC, shifts the signal to baseband and applies Amplitude Gain Control (AGC) step compensation, linear AGC correction and IQ Correction (IQC).

## Dual IF car radio and audio DSP (N1F)

The PDC decimates the incoming signal by 16 before shifting it to the baseband and creating two paths: 'wanted' and 'image'. After another decimation by two, the AGC stage takes place to compensate for the tuner gain-reduction steps. The linear gain control stage makes sure that there is maximum use of the dynamic range. After another decimation by two the IQC stage takes place to compensate for imperfections in the analog mixer of the tuner by measuring and correcting possible aliases between the wanted and image signals. The PDC settings allow for different IF bandwidth corrections and for local oscillator swap of the TEF7000. Communication between the tuner and SAF7741HV uses the proprietary two-line LD interface for AGC, injection-mode and bandwidth settings.

The PDC has two data outputs: one parallel interface to the TDSPs and one I<sup>2</sup>S-like interface to the external digital radio co-processor.

## 7.1.2.1 PDC Input

The PDC input is a complex bit stream from the 5th order converter. The I and Q bit streams each have a sample rate of 41.6 MSa/s.

#### 7.1.2.2 Input decimation

The input sample rate of 41.6 MSa/s is decimated by 16 MSa/s to 2.6 MSa/s.

#### 7.1.2.3 Shift-to-baseband mixer

For the wanted signal, the TEF7000 tuner has an IF frequency of 300 kHz for FM and 60 kHz for AM: for the image signal these values are -300 kHz and -60 kHz respectively. The shift-to-baseband mixer shifts the wanted signal by  $-f_{mix}$  to baseband and the image signal by  $+f_{mix}$ . The mixer has two independent registers for the wanted frequency alignment:

- fmix\_0 with high-side injection

- fmix\_1 with low-side injection

In TEF6730 mode fmix 0 and fmix 1 are 300 kHz for both FM and AM

### Dual IF car radio and audio DSP (N1F)

#### 7.1.2.4 Mixer output decimation

The output signal of the shift-to-baseband mixer is decimated by two to 1.3 MSa/s before it enters the AGC stage.

#### 7.1.2.5 Gain control

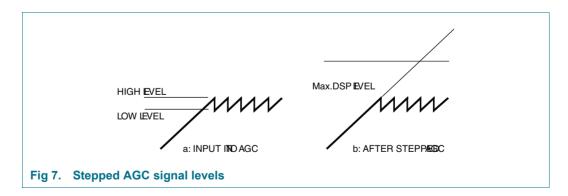

Both the wanted and the image signals are gain-controlled in the AGC stage. This contains a stepped gain stage, a linear gain stage and IF signal level detection. The linear gain stage ensures that maximum use is made of the dynamic range (see Figure 7).

Various gain-step compensation controls are implemented to reduce the audible effects of the gain steps. To increase the dynamic range of the tuner, gain-step compensation takes place in the AGC block of the PDC for:

- Step-response amplitude

- Step-response waveform

- Step-response timing

### 7.1.2.6 Stepped gain amplitude

The tuner communicates a new gain setting to the SAF7741HV via the DL interface. The SAF7741HV has four independent and different stepped AGC banks:

- AGC A

- AGC B

- AGC C

- AGC D

The number of steps for each AGC bank and the associated resolution is listed in Table 4.

Table 4. Stepped AGC gain reduction

| AGC   | Function | Number of Steps | Number of Bits | Resolution |

|-------|----------|-----------------|----------------|------------|

| AGC_A | LNA_1    | 16              | 12             | 50 mdB     |

| AGC_B | LNA_2    | 8               | 11             | 50 mdB     |

| AGC_C | Mixer    | 4               | 10             | 50 mdB     |

| AGC_D | IF       | 4               | 10             | 50 mdB     |

The AGC tables contain the corresponding gain reduction values of the tuner, expressed in bits. Zero gain reduction is at the top of each table. The tuner has random access to the table. The maximum single amplitude change of the AGC is 16 bits –1 LSB. This is equivalent to 96 dB. This maximum amplitude change can be made in any combination of AGC values from AGC\_A up to AGC\_D. The last gain reduction command from the tuner is readable by the DSP in the AGC Change registers. Found in AGC Data Out registers are:

- The total stepped gain reduction

- · The linear gain reduction

- The resulting gain reduction

The TEF7000 tuner uses:

- AGC\_A and AGC\_B for wideband AGC (in this case LNA\_1 and LNA\_2)

- AGC\_C for the mixer AGC

- AGC\_D is used as IF\_AGC

Remark: The AGC\_A, AGC\_B and AGC\_D replace the pin-diode AGC in the TEF6730.

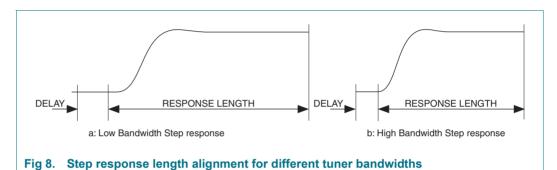

### 7.1.2.7 Step-response waveform

The compensating step-response waveform depends on the step response type to be compensated. Compensating waveforms for the LNA and the mixer gain steps are stored in ROM for both the IF response and the wideband response. The IF response is derived from the PDC response before the AGC stage.

The step-response waveform from the ROM is used when the gain change is less than 12 dB. This results in compensation which is not audible and which therefore does not require muting.

## Dual IF car radio and audio DSP (N1F)

When there is a gain change of more than 12 dB this is made step-wise without running the compensation waveform. This is the case with either Alternate Frequency (AF) updates or a pre-set change. These functions are always used in a muted condition and are therefore not audible.

#### 7.1.2.8 Step-response timing

In order to align for the bandwidth of the analog circuits, an alignment is made between the response length and the response delay. This alignment is separate for the wideband and the IF responses.

Both the delay and the response length for the IF response are dominated by the PDC response before the AGC. These values are independent of the tuner response. The wideband response is different for analog and for digital AM/FM.

#### 7.1.2.9 Perfect step compensation

Perfect step compensation of the tuner gain steps is made possible for signals within the IF signal band by alignments of amplitude, waveform and waveform delay. Near-perfect alignment is possible for off-centre signals within the IF signal band.

#### 7.1.2.10 Non-perfect step compensation

Perfect compensation of the tuner gain steps is not possible for signals outside the IF signal band. In such cases the resulting interference must be suppressed. In the PDC, four signalling bits are provided for this purpose:

- AGC A CHANGE

- AGC B CHANGE

- AGC C CHANGE

- AGC D CHANGE

These bits can be read by the DSP and a soft-mute signal can be generated when required.

#### 7.1.2.11 AGC linear gain

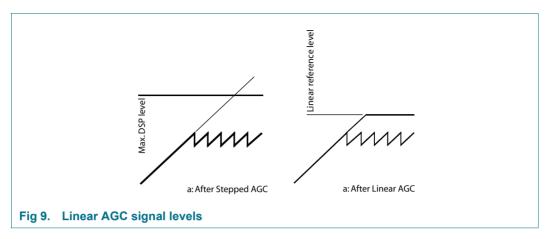

Data-path signals that exceed a certain level are kept constant in a linear controlled-gain stage (see Figure 9). Linear control avoids overload of the following signal stages and makes sure that maximum use is made of the data path's dynamic range. The I<sup>2</sup>C interface sets the reference level for linear control as well as the corresponding attack and delay values.

The linear control reference level should be above the maximum uncontrolled input level of the linear control stage (See <u>Figure 7</u>). Settings of the reference level below the maximum uncontrolled input level will result in a distorted output signal.

### 7.1.2.12 IF signal level detection

Signal level detection for wideband AGC is handled in the tuner. The resulting AGC steps are then interfaced to SAF7741HV and a step compensation is made. The IF AGC is controlled by level detectors within the PDC, and by IF detector high- and low-level settings which can be set via IC. The level detectors in the PDC communicate with the tuner to increase or decrease the level of the incoming signal.

The IF detector bandwidth is shown in Figure 10.

### 7.1.2.13 AGC output decimation

The output signal of the AGC is decimated by two to 650 kSa/s before it enters the IQC stage.

#### 7.1.2.14 IQC stage

The IQC stage suppresses the image mirror co-channel within the wanted signal and corrects for gain and phase imperfections in the analog mixer and the subsequent analog data base. This is done by measuring and correcting possible correlations between the wanted and the image signals.

The IQC is an adaptive algorithm based on a Normalized Least Mean Square (NLMS). Normalization is performed off the data path in the Least Mean Square (LMS) adaptation engine itself, and therefore does not affect the output signals of the PDC. It takes place in steps of 6.0 dB with an associated averaging filter. Four coefficients are available to allow the IQC to manage frequency dependencies introduced by the analog IF filters. The adaptation rate parameter (mu) is controlled automatically at startup to make sure that the coefficients converge correctly.

An adaptation freeze level can be set to prevent tap drift in weak signal conditions.n TEF6730 mode the IQC stage is bypassed.

#### 7.1.2.15 PDC output

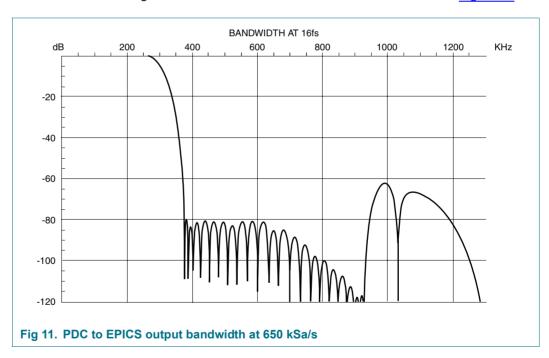

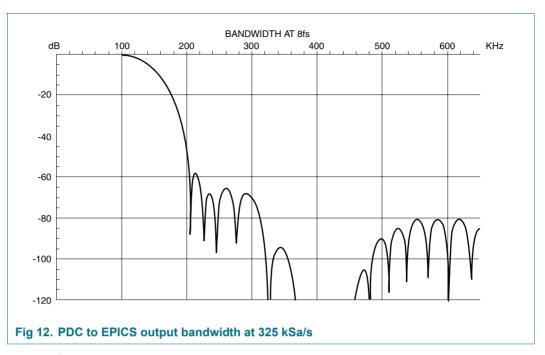

The PDC has two outputs; one to the software radio and the other to the external pins. For the output to the software radio a choice can be made between three signals. The first of these is the wanted signal at 650 kSa/s. The bandwidth for this is shown in .Figure 11

The second choice is the wanted signal at 325 kSa/s. This is shown in <u>Figure 11</u>. The third choice is the wanted/image signal pair at 325 kSa/s. The signal bandwidth for this is shown in <u>Figure 12</u>.

For the I<sup>2</sup>S external output a choice can be made between FM and AM digital radio, both at 650 kSa/s and both wanted-signal only. All PDC input and output signals are complex.

### 7.1.2.16 LD interface

The SAF7741HV is designed for a generic tuner with TEF7000 architecture. Communication between the tuner and the SAF7741HV uses the proprietary two-line LD interface for AGC, injection-mode and bandwidth settings.

The tuner sends commands to the SAF7741HV while the SAF7741HV sends requests to the tuner. A tuner command is always executed unconditionally by the SAF7741HV, but a request from the SAF7741HV to the TEF7000 may be ignored.

AGC commands define the gain compensation required to compensate for the gain change of the tuner, and can also reset detectors in the stepped and the linear AGC.

The LD interface commands and their bit allocation are listed in Table 5. Refer to the tuner data sheet for the different signal bands.

LD interface command bit allocation Table 5.

| Bit | Function | Bit | Function  |

|-----|----------|-----|-----------|

| ы   | Tunction | ы   | Tulletion |

| B22 | Reserved | B10 | AGC_C[1]  |

| B21 | Reserved | B09 | AGC_C[0]  |

| B20 | Reserved | B08 | AGC_D[1]  |

| B19 | Reserved | B07 | AGC_D[0]  |

| B18 | Reserved | B06 | AGC_DM    |

| B17 | AGC_A[3] | B05 | RST_DET_D |

| B16 | AGC_A[2] | B04 | RST_LIN   |

| B15 | AGC_A[1] | B03 | INJ       |

| B14 | AGC_A[0] | B02 | INJM      |

| B13 | AGC_B[2] | B01 | BW        |

| B12 | AGC_B[1] | B00 | BWM       |

| B11 | AGC_B[0] | _   | _         |

The LD interface requests from the SAF7741HV and their bit allocations are listed in Table 6.

Table 6. LD interface request bit allocation

| Bit | Function |

|-----|----------|

| B06 | Reserved |

| B05 | Reserved |

| B04 | Reserved |

| B03 | DET_D[1] |

| B02 | DET_D[0] |

| B01 | INJ      |

| B00 | BW       |

In TEF6730 mode, the DL Interface is replaced by 2 IF-AGC bits.

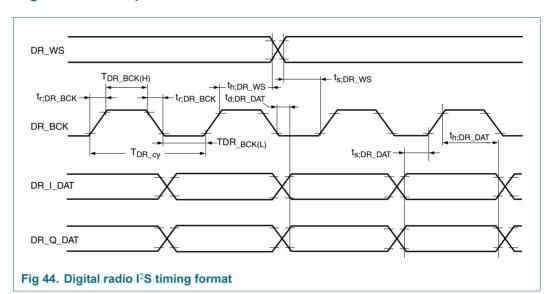

### 7.1.3 Digital radio interface

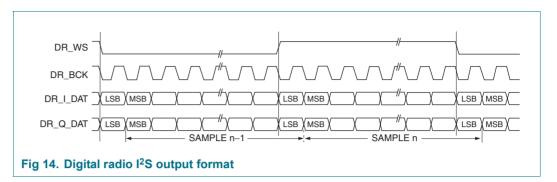

For digital radio an I<sup>2</sup>S output is provided for the I and Q signals (see Figure 14). A GPIO pin can be used as a blend input that makes it possible to switch from conventional FM and AM processing to digital radio processing.

There are two possible ways to get digital radio data:

- Digital radio interface 1 output, from either PDC1 or PDC2

- Digital radio interface 2 output via the T1E I<sup>2</sup>S interface from PDC2

### 7.1.4 RGP DAC

RGP digital-to-analog conversion is performed by a 10-bit DAC with a buffered output. This is part of the radio subsystem and can be used for various functions linked to the radio domain.

A double buffered interface is located between the DSP and the RGP DAC. The buffer is  $2 \times 8$  words in length, which means that data with a maximum sample rate of 8 Fs (i.e. 325 kHz) can be transferred to the output when the DSP is running at 1 Fs (i.e. 40.625 kHz).

#### 7.1.4.1 TEF6730 tuner compatibility

In TEF6730 tuner compatibility mode the general-purpose DAC can be used for controlling the PIN diode in front of the tuner. In addition to its digital AGC function this operates as second-level gain correction for the IFADC.

### 7.1.5 Radio Data System demodulator/decoder

#### 7.1.5.1 General description

There are two Radio Data System (RDS) demodulation and decoder systems available on the SAF7741HV. The description below applies to each of them.

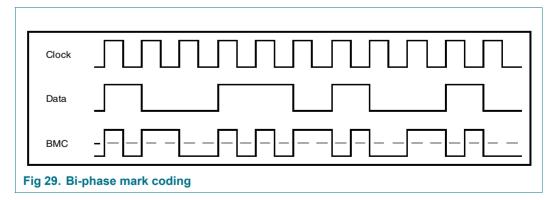

The RDS function recovers the additional and inaudible RDS information transmitted by FM radio broadcasting. The operational functions of the demodulator and the decoder are in accordance with EBU specification EN50067.

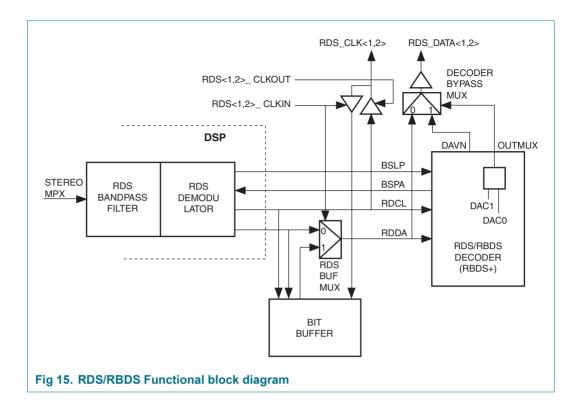

The function processes the RDS signal frequency-multiplexed within the stereo MultiPleX (MPX) signal to recover the information transmitted over the RDS data channel. This processing consists of band-pass filtering, demodulation and RDS/ Radio Broadcast Data System (RBDS) decoding. The RDS band-pass filter discards the audio content from the input signal and reduces the bandwidth.

The RDS demodulator regenerates the raw RDS bitstream (bit rate = 1187.5 Hz) from the modulated RDS signal. Connection to the RDS/RBDS decoder is by means of the DSP flags (see Figure 15).

Under I<sup>2</sup>C control via bit rds\_clkin an internal buffer can be used to read out the raw RDS stream in bursts of 16 bits. With the I<sup>2</sup>C bit rds\_clkout the RDS clock can be either enabled or switched off.

## Dual IF car radio and audio DSP (N1F)

The RDS/RBDS decoder provides:

- Block synchronization

- Error detection

- Error correction

- · Complex flywheel function

- · Programmable block data output

Newly processed RDS/RBDS block information is signaled to the main microcontroller as 'new data available' by use of the DAVN output. The block data itself and the corresponding status information can be read out by means of an I<sup>2</sup>C bus request.

The RDS chain derives data information from the MPX signal independently of either the analog or the digital audio streams. This allows RDS updates during playback from tape or other sources.

### 7.1.5.2 RDS I/O modes

Apart from the control inputs and data outputs via the  $I^2C$  inteface, the inputs and the outputs related to the RDS function are listed in <u>Table 7</u>, <u>Table 8</u> and <u>Table 9</u>

Table 7. Unbuffered raw (direct) RDS output mode (rds<1,2>\_clkin = 0, rds<1,2>\_clkout = 1 and DAVD mode: dac0 = 1, dac1 = 1)

| Name     | Description                                                                                                                                                                                          |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDS_CLK  | Clock of the raw RDS bit stream. This is extracted from the bi-phase coded baseband signal by the RDS demodulator. The clock period is 1.1875 kHz. See Ref. 1 for more details.                      |

| RDS_DATA | Raw RDS bit stream, generated by the demodulator. This allows for external receivers of the RDS data to clock the data on the RDS_CLK signal as well as on its inverse. See Ref. 1 for more details. |

Table 8. Buffered raw RDS output mode (rds<1,2>\_clkin = 1, rds<1,2>\_clkout = 0 and DAVD mode: dac0 = 1, dac1 = 1)

| Name     | Description                                                                                                                                                                                                                                                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDS_CLK  | Burst clock, generated by the multi-processor. Bursts of 17 clock cycles are expected. The average time between bursts = 13.5 ms.                                                                                                                                                |

| RDS_DATA | Bursts of 16 raw RDS bits are put out under the control of the burst clock input. This output is high after a data burst, and is pulled low when 16 new bits are available and a new clock burst is awaited. The microprocessor has to monitor this line at least every 13.4 ms. |

Table 9. DAVA, DAVB and DAVC modes (rds<1,2> clkin = 0, rds<1,2> clkout = 0)

| Name | Description                                                                                                                                   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| davn | Data-available signal for synchronization of a data request between the main controller and the decoder (for further information see Ref. 2). |

**Remark**: Rds<1,2>\_clkin = 1 and rds<1,2>\_clkout = 1 is NOT an allowed mode.

Depending on the mode selected, the same output is used for RDS\_DATA and DAVN (see Figure 15).

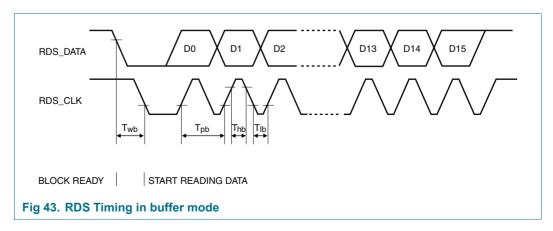

#### 7.1.5.3 RDS timing of clock and data signals in DAVD mode

The timing of the clock and data outputs is derived from the incoming data signal. Under stable conditions the data will remain valid for 400 ms after the clock transition. The timing of the data change is 100 ms before a positive clock change. This timing is well suited to positive- and negative-triggered interrupts on a microprocessor.

It is possible that phase faults will occur during poor reception, in which case the duty cycle of the clock and data signals will vary between a minimum of 0.5 and a maximum of 1.5 times the standard clock period. Faults in phase do not normally occur on a cyclical basis. See also Section 14.1.

#### 7.1.5.4 RDS bit buffer

The repetition frequency of the RDS data is 1187.5 Hz. This results in an interrupt on the microprocessor every 842 ms, but the double 16-bit buffer allows this timing requirement to be relaxed since the two 16-bit buffers are filled alternately. If a buffer has not been read out by the time the other buffer is filled it will be overwritten and the old data will be lost. While a 16-bit buffer is being filled the RDS bit buffer keeps the data line high.

When a 16-bit buffer is full the data line is pulled down. The microprocessor has to monitor the data line at least every 13.5 ms. The data line remains low until the microprocessor pulls the clock line low. This starts reading out of the buffer, and the first bit is put on the data line. The RDS bit buffer puts a bit on the data line after every falling clock edge, and

the data remains valid while the clock is high. After 16 falling and 16 rising edges the whole buffer is read out and the bits are stored by the microprocessor. After a 17th falling clock edge the data line is set high until the other 16-bit buffer is full. The microprocessor stops communication by pulling the clock line high again. See Section 14.1.

#### 7.1.5.5 RDS demodulator

The RDS demodulator is implemented in DSP software. See Ref. 1 for details of its functionality.

**Demodulator decoder interface:** Communication between the RDS demodulator and decoder is provided by Economic Parameterized Integrated Cores (EPICS) flags and consists of four signals as shown in Figure 15.

**Remark:** Instead of the EPICS flags, the RDS decoder connection register can be used for demodulator decoder communication. For further details see Ref. 3.

Table 10. Signals provided by the demodulator

|      | rightalo provided by the demodalate.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| rdcl | Demodulator clock output. Generated by the RDS/RBDS demodulator for every RDS/RBDS clock period (1.1875 kHz). This pulse remains high for about half of an RDS/RBDS clock period ( $\sim$ 420 $\mu$ s). The rising edge of this signal is used as an input shift enable for the decoder internal data buffer (RDS Data Output [RDDA] bit input). It is assumed that the RDDA input will remain unchanged for at least one system clock (10.4 MHz) after a rising RDCL edge. |

| rdda | Demodulator data output.  Represents the actual RDS/RBDS data bit. The RDDA is shifted into the decoder module internal data buffer by detection of a rising edge on the RDCL input signal.                                                                                                                                                                                                                                                                                 |

| bslp | Bit-Slip (BSLP) detected.  This is set to high for at least one RDS/RBDS clock period (1.1875 kHz), but only when the demodulator detects a possible BSLP. The BSLP signal itself has to be reset to low after one RDS/RBDS clock period.                                                                                                                                                                                                                                   |

Table 11. Signals received by the demodulator

| Name | Description                                                                                                            |

|------|------------------------------------------------------------------------------------------------------------------------|

| bspa | Bit-Slip Process Active (BSPA). This is set to HIGH when the RDS decoder detects a BSLP: at all other times it is LOW. |

**Remark:** The current version of the SAF7741HV firmware does not use bslp/bspa signalling. This is implemented in the hardware, and is therefore mentioned here for information only.

#### 7.1.6 8Fs I<sup>2</sup>S interface

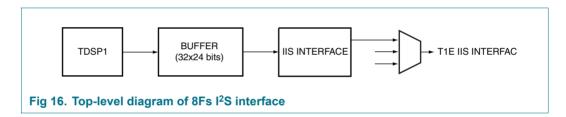

The 8Fs I<sup>2</sup>S interface is used to transform the parallel data outputs of the TDSP1 (24 bits wide) to serial data in I<sup>2</sup>S format, and then make that data available at the digital radio interface 1 (see <u>Figure 16</u>). The TDSP1 has the capability to write data to the interface at 1Fs, 2Fs, 4Fs and 8Fs.

Depending on the flag values, the interface can send data in I<sup>2</sup>S format at 1Fs, 2Fs, 4Fs, 8Fs and 16Fs.

<u>Table 12</u> gives all possible combinations of speeds at which the interface receives and sends data.

Table 12. TDSP1/I<sup>2</sup>S interface receive and send data speeds

| TDSP1 Speed | I <sup>2</sup> S Speed  |

|-------------|-------------------------|

| 1Fs         | 1Fs, 2Fs, 4Fs, 8Fs      |

| 2Fs         | 1Fs,2Fs, 4Fs, 8Fs, 16Fs |

| 4Fs         | 1Fs,2Fs,4Fs, 8Fs,16Fs   |

| 8Fs         | 1Fs,2Fs,4Fs,8Fs, 16Fs   |

The size of the buffer is determined by the largest factor between the speeds of the TDSP1 and the IIS, which is the case when the TDSP1 runs at either 1Fs and the IIS at 8Fs or when the TDSP1 runs at 2Fs and the IIS at 16Fs. In the first case the TDSP1 has to be able to write two words of 24 bits - i.e. left data and right data for stereo samples at 1Fs speed - and the speed at which the read should be performed by the IIS interface is 8Fs. Therefore the required buffer size is  $16 \times 24$  bits. Moreover, the buffer is required to support double buffering; i.e. it can be written to and read from at the same time. This makes the total size of the buffer  $32 \times 24$  bits.

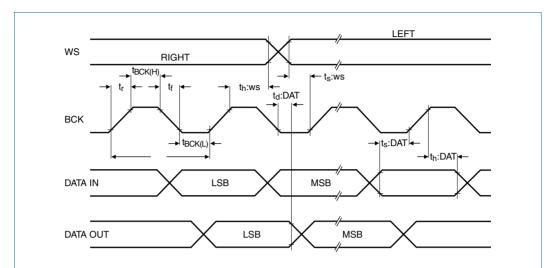

### 7.1.7 Tuner I<sup>2</sup>S interface

The Tuner I<sup>2</sup>S interface provides a connection between the output multiplexer and TDSP1E. There are two data converters, one converting parallel data (24 bits wide) to IIS format and the second converting from I<sup>2</sup>S format to parallel. The two converters both run at the TDSP1E sample rate. The format of the I<sup>2</sup>S data can be configured by setting the applicable registers, and the internal I<sup>2</sup>S generator and I<sup>2</sup>S receiver both work as masters. The result is that the signals 'word select' and 'serial clock' are always generated internally.

## 7.1.8 Output multiplexer

The output multiplexer behind the tuner I<sup>2</sup>S interface maps four different serial data streams to and from the pins:

- Data going to or coming from the tuner I<sup>2</sup>S interface (I<sup>2</sup>S in/out)

- Data T1 coming from the software radio and going to the SRC DSP (SDSP) (I<sup>2</sup>S out)

- Data T2 coming from the software radio and going to the SDSP (I<sup>2</sup>S out)

- Data coming from PDC2 (digital radio format out)

### 7.1.9 Software radio user flags

The user flags of the TDSPs can be programmed for various functions described below. Every TDSP has 13 I/O flags available. <u>Table 13</u> shows all the possibilities for each user flag.

Table 13. TDSP user flags

| User Flag | Chip Pin Name | Function                                                               | Mode <sup>[1]</sup> |         |

|-----------|---------------|------------------------------------------------------------------------|---------------------|---------|

|           |               |                                                                        | I/O                 | Stretch |

| F0        | _             | SFLAG input from EPICS flag generator                                  | IN                  | OFF     |

| F1        | TDSP_IOF1     | User-defined in or out                                                 | IN/OUT              | ON/OFF  |

| F2        | TDSP_IOF2     | User-defined in or out                                                 | IN/OUT              | ON/OFF  |

| F3        | TDSP_IOF3     | User-defined in or out                                                 | IN/OUT              | ON/OFF  |

| F4        | TDSP_IOF4     | User-defined in or out                                                 | IN/OUT              | ON/OFF  |

| F5        | TDSP_IOF5     | User-defined in or out/clock output to RDS decoder1                    | IN/OUT              | ON/OFF  |

| F6        | TDSP_IOF6     | User-defined in or out/data output to RDS decoder1                     | IN/OUT              | ON/OFF  |

| F7        | TDSP_IOF7     | User-defined in or out/BSLP output to RDS decoder1                     | IN/OUT              | ON/OFF  |

| F8        | TDSP_IOF8     | User-defined in or out/bspa input from RDS decoder1                    | IN/OUT              | ON/OFF  |

| F9        | TDSP_IOF9     | User-defined in or out/clock output to RDS decoder2                    | IN/OUT              | ON/OFF  |

| F10       | TDSP_IOF10    | User-defined in or out/data output to RDS decoder2                     | IN/OUT              | ON/OFF  |

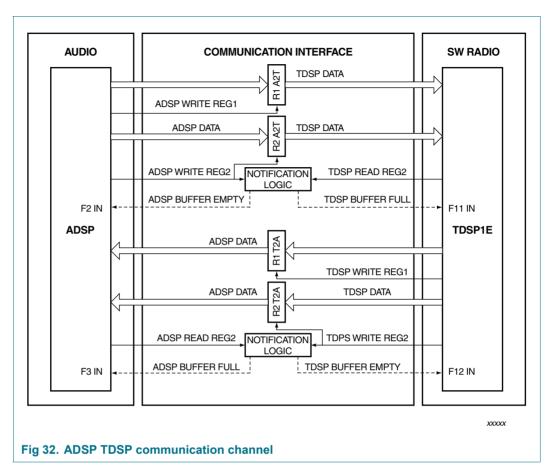

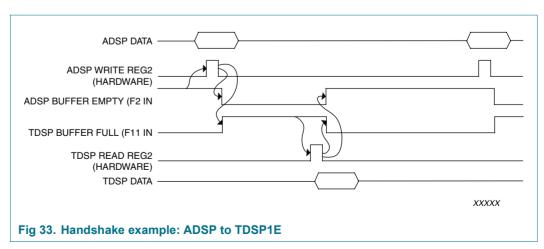

| F11       | _             | ADSP TDSP1E interface/RDS decoder                                      | IN                  | ON/OFF  |

| F12       | -             | Out flag to the WDOG value registers/ADSP TDSP1E interface/RDS decoder | IN                  | ON/OFF  |

<sup>[1]</sup> All I<sup>2</sup>C-controllable

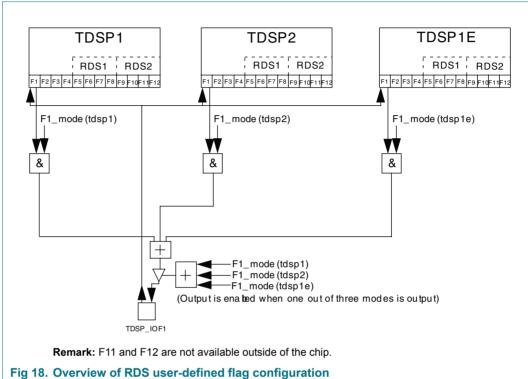

There are 10 general purpose I/O pins available for the software radio. These have to be shared between the available TDSPs as shown in <u>Figure 18</u>. In this diagram only TDSP IOF1 is depicted since all the other flags are connected the same way.

In the description that follows the value of 'n' can be 1 to 10.

- 1. Pin TDSP\_IOFn is wired directly to the input flag 'n' of each TDSP.

- 2. The output flags 'n' of all the TDSPs are OR-ed together and the resulting signal is wired to TDSP IOFn.

- 3. All the flags on all the separate TDSPs can be set to input or output in the I<sup>2</sup>C registers. The pad of TDSP\_IOFn is input when all TDSP flags 'n' are set to input: otherwise it is used as an output.

- 4. All the flags on all separate TDSPs can be set to stretch mode or non-stretch mode in the I<sup>2</sup>C registers.

There are exceptions to the above description. On the chip there are two RDS decoders that can be connected to either of the TDSPs, using predefined pins on the DSP when connected. The corresponding TDSP pins connected to the RDS decoder are then fixed as RDS pins and are no longer available as user-defined. The stretch mode of the

#### **Dual IF car radio and audio DSP (N1F)**

corresponding pins is switched off. Which RDS decoder is connected to which TDSP is controlled in the I<sup>2</sup>C registers. <u>Table 13</u> shows which flags are used for RDS when connected.

#### Tig 10. Overview of NDS user-defined hag configu

#### 7.1.9.1 EPICS flag generator

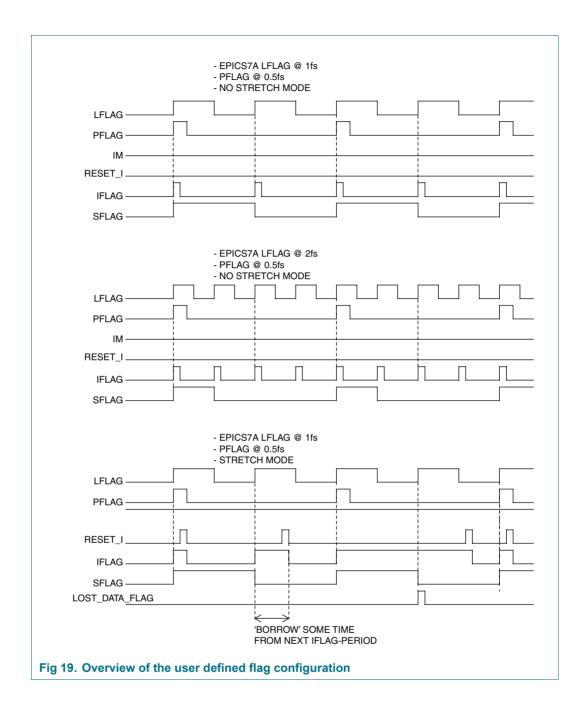

The EPICS flag generator generates two flags: IFLAG and the Sync Flag (SFLAG). IFLAG is connected to the 'I' input flag of the EPICS and SFLAG is connected to the user flag 0. SFLAG indicates that the EPICS should use page0 of the EPICS interface memories to avoid read and/or write errors and conflicts.

The normal duration of IFLAG is four EPICS clock periods. The SFLAG is set until the next IFLAG is generated.

The EPICS can stretch (IMODE) IFLAG via the IM input.

#### 7.1.9.2 Flag overview

When IFLAG is in stretch mode (IM is high) the flag is set at every rising edge of LFLAG. IFLAG can be reset only with the RESET\_I input connected to a DIO address. When this address is read by the EPICS, RESET\_I is pulsed. SFLAG is not stretched. If IFLAG is not cleared before the next LFLAG the LOST\_DATA flag is set.

When IFLAG is not in stretch mode (IM is low) then an IFLAG is generated at every rising edge of the LFLAG. If at this point PFLAG is high, then SFLAG is set until the next rising edge of LFLAG (see <a href="Figure 19">Figure 19</a>). LFLAG and PFLAG are generated in the software radio flag generator.

## 7.2 Audio subsystem

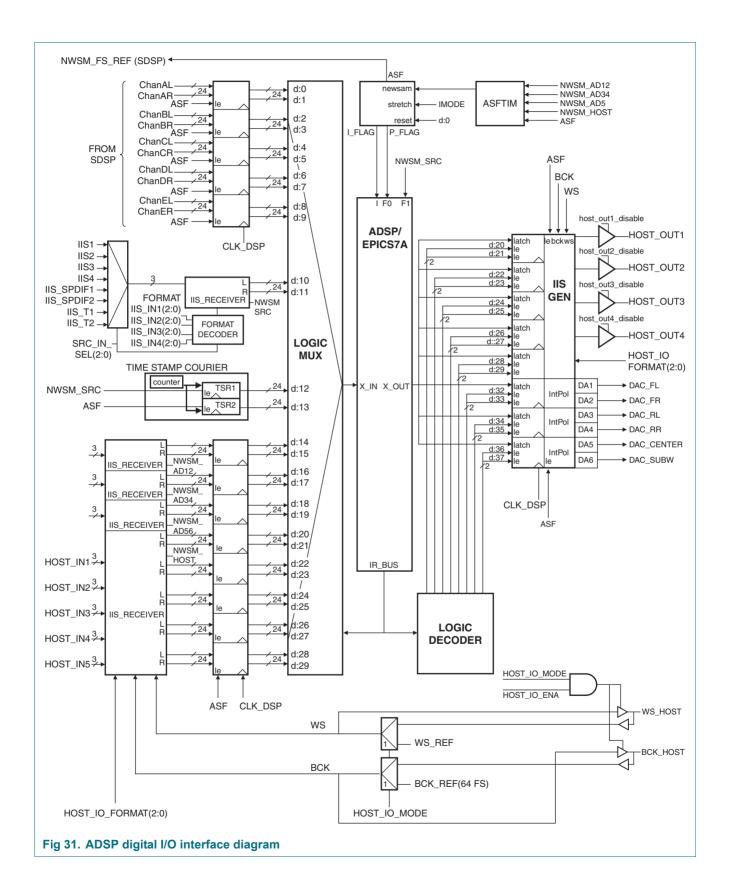

The audio subsystem (see Figure 2) consists mainly of four sequential sections:

- Input section (analog and digital)

- SRC section

- · Audio processing section

- · Audio output section

## 7.2.1 Input section

The audio input section is split into an analog and a digital input.

#### 7.2.1.1 Analog audio input paths

The analog input section consists of an analog source selector and five ADCs. The outputs of the ADCs are connected to the ADSP. The audio sample rate of these inputs can be a maximum of 55 kHz. When the ADSP runs at a higher rate the inputs need to be routed via a software up-sampler.

## 7.2.2 Signal flow of the analog audio input

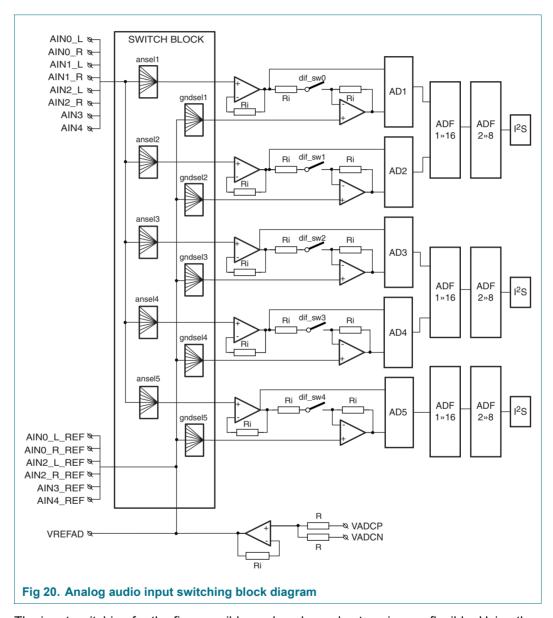

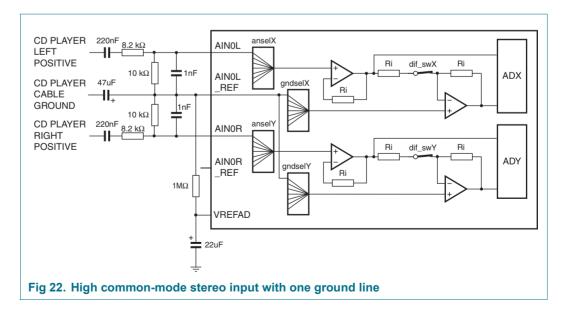

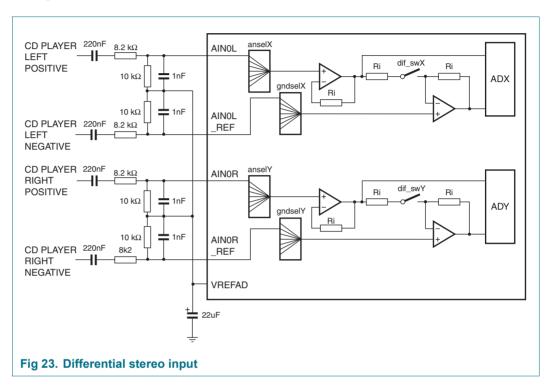

The input switching for the five possible analog channel setups is very flexible. Using the switches gndsel0 to gndsel4 (see ) and ansel0 to ansel4 all combinations can be made either for normal inputs or for high common-mode inputs with a ground connection (see Figure 20)

In principle, any signal input can be connected to any ADC. However, it is possible to make the stereo signals use the even-numbered ADCs (ADC0, ADC 2 and ADC4) for the left channels and the odd-numbered ones (ADC 1 and ADC 3) for the right channels. The only conditions are that:

- When the input signals do not have a ground pin the minus input of the second Op-amp in the signal chain must be connected by means of the gndsel switches to the VREFAD line.

- When there is a high common-mode input with ground input pin the associated gndsel switch must be connected to this pin.

- Some connections to the switching matrix are 'reserved'. These must not be used.

Table 14 and Table 15 show the possible connections.

Table 14. Selection of analog signal switches

| Position | ANSEL1 to ANSEL5 |

|----------|------------------|

| 000      | AIN0_L           |

| 001      | AIN0_R           |

| 010      | AIN2_L           |

| 011      | AIN2_R           |

| 100      | AIN3             |

| 101      | AIN4             |

| 110      | AIN1_L           |

| 111      | AIN1_R           |

Table 15. Selection of the analog ground switches

| Position | ANSEL1 to ANSEL5 |

|----------|------------------|

| 000      | AIN0_L_REF       |

| 001      | AIN0_R_REF       |

| 010      | AIN2_L_REF       |

| 011      | AIN2_R_REF       |

| 100      | AIN3_REF         |

| 101      | AIN4_REF         |

| 110      | VREFAD           |

| 111      | Reserved         |

## 7.2.3 Realization of the common mode inputs

A high Common-Mode Rejection Ratio (CMRR) can be created for all the analog inputs by use of the ground pins. To create a signal input, connect the ground pin that is to be used to the second Op-amp in the signal path by using the gndsel switch. This ensures that the two signal lines that go to the ADC will contain the common-mode signal. The ADC itself will suppress the signal very effectively, so in this way good common-mode signal suppression will be achieved.

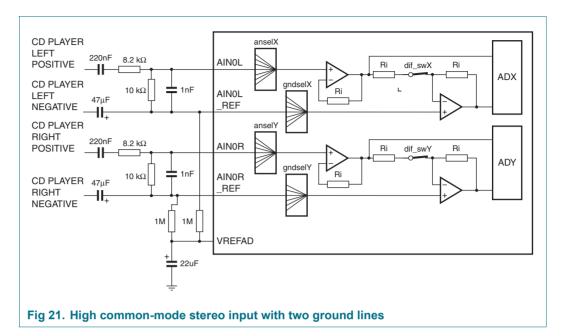

An example of a high common-mode stereo input with two ground shielding lines is shown in Figure 21.

## Dual IF car radio and audio DSP (N1F)

In this example input voltage reduction is accomplished by the external 8.2 k $\Omega$  to 10 k $\Omega$  resistor divider. The rather low-value resistor divider is necessary because in this case the parasitic capacitance on pins AINO\_L and AINO\_R will reduce the common-mode signal on them. The CMRR can be guaranteed when the source and cable impedance do not exceed the specified value as stated in the conditions column of <u>Table 35</u>. This leads to a reduction of the CMRR when the source impedance is too high. Half of the supply voltage is provided as reference by connecting the negative inputs of the second operational amplifier to VREFAD by means of the gnd\_sel switches and the external 1.0 M $\Omega$  resistor. The 1.0 nF capacitors are used for anti-aliasing.

An example of a high common-mode input with only one ground-shielding line is shown in Figure 22.

A full-stereo differential input of a CD changer is shown in Figure 23. The switches dif\_sw are shown open, and only when signals on the inputs (marked POS and NEG) are different will analog-to-digital conversion take place. Common-mode signals on the inputs will also appear as common-mode signals on the ADC inputs and will not be converted to the digital data stream.

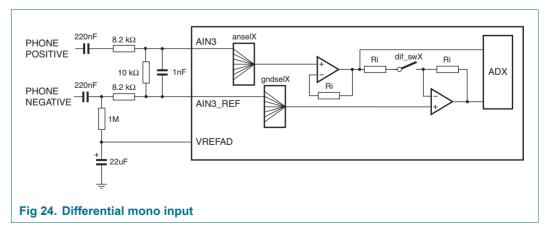

The differential-mode application of a single-ended input is shown in Figure 24. In this case the input voltage is reduced symmetrically with two 82 k $\Omega$  resistors and one100 k $\Omega$  resistor. This neutralizes the effect of parasitic capacitance on the AlN3 input and the AlN3\_GND input to permit a relative high-ohmic resistor divider to be used. In this example common-mode signals which have not been reduced in value are applied to the ADC. The ADC itself has a very good CMRR, so this input also has a high CMRR.

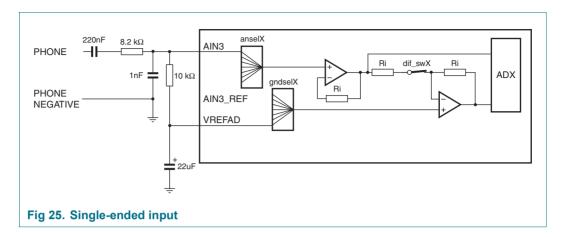

In <u>Figure 25</u> a single-ended input is shown. The reference here is VREFAD which is connected internally, so no common-mode rejection can be expected.

NXP Semiconductors SAF7741HV

#### Dual IF car radio and audio DSP (N1F)

## 7.2.4 Audio ADC decimator paths (DAD)

### 7.2.4.1 Functional description

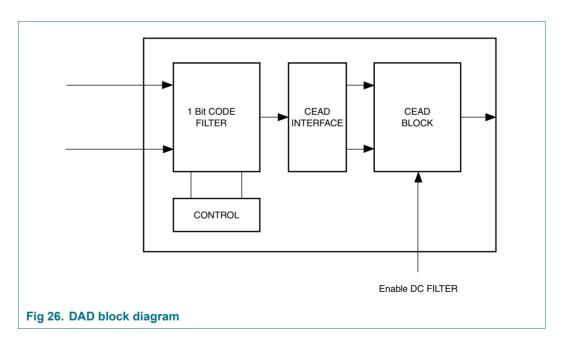

Decimation of the audio ADC signals is completed in a block called DAD. This block can handle the signals from two ADCs, so a stereo signal can be processed.

The input signal has a sample frequency of  $128 \times fs$  and comes from a third-order  $\Sigma\Delta$  ADC. The first step in the decimation process is done by the 1-bit code Cascaded Integrator Comb (CIC) filter and Audio Decimation Filter 1 (ADF1) filter. See <u>Figure 26</u>. The CIC filter decimates the input sample rate by a factor of 16 and thus results in a sample rate of  $8 \times fs$ .

After the 1-bit code filter, sample reworking is necessary to enter the CEAD block and the ADF2. The CEAD block further decimates the audio samples by 8, giving a sample rate of  $1 \times fs$ . The overall gain in the pass band of the decimation filter (including the CIC filter and the CEAD block) becomes 4.85 dB. A nominal input level of -8.45 dB comes from the ADC and results in a -3.6 dB level after decimation.

The DC filter in the CEAD block is controlled by an I<sup>2</sup>C bit that can be found in Ref. 3. Power-on reset circuitry is not implemented, which means that after power-up all filters will go through a brief transient phase before they reach their steady-state behavior.

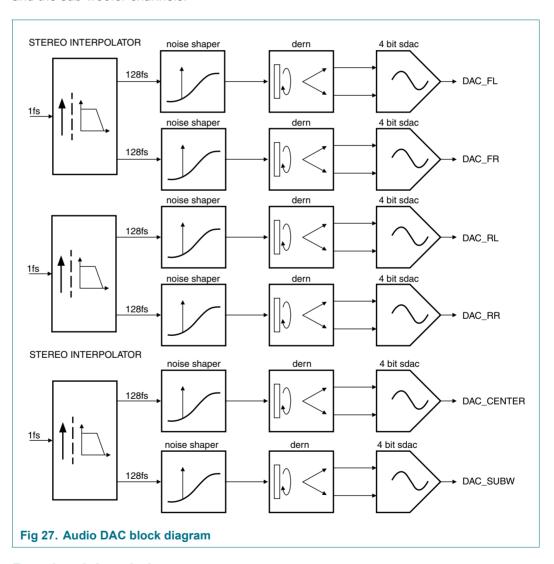

## 7.3 Audio Digital-to-Analog (ADAC) conversion

The ADAC module consists of a DAC, an interpolation filter and a noise shaper for the audio. Both the analog and the digital functions are described here.

The digital part consists of an interpolation filter which increases the sample rate from 1 fs to 128 fs and a third-order noise shaper that runs at 128 fs.

The analog part consists of six single-ended DAC modules for the left, the right, the centre and the sub-woofer channels.

## 7.3.1 Functional description

The audio DAC comprises these functions:

Digital up-sampling filter

© NXP B.V. 2010. All rights reserved.

**Dual IF car radio and audio DSP (N1F)**

- 3rd order noise shaper

- DAC including Compensations and the DEM algorithm

## 7.3.2 Digital filters

The interpolation from 1 fs to 128 fs is done in four stages:

- The first stage is a 99 tap Half-Band (HB) filter that increases the sample rate from 1 fs to 2 fs. It has a steep transition band to correct for the missing inherent filter function of the DAC used

- The second stage is a 31-tap FIR filter that increases the data rate from 2 fs to 8 fs. It compensates for the roll-off caused by the Sample and Hold (SH) function prior to the noise shaper

- The third stage is a simple hardware Linear Interpolator (LIN) function that increases the sample rate from 8 fs to 16 fs. It removes the 8 fs component in the output spectrum

- The fourth and last stage is a SH function increasing the sample rate from 16 fs to 128 fs.

The overall transfer characteristics can be found in Table 16.

Table 16. Digital filter characteristics

| Characteristics | Condition         | Value (dB) |

|-----------------|-------------------|------------|

| Passband ripple | 0 Fs to 0.4535 Fs | +0.02      |

| Stop band       | >0.5465 Fs        | -72        |

| Dynamic range   | 0 Fs to 0.4535 Fs | >143       |

#### 7.3.3 Noise shaper