**OP-01**

INVERTING HIGH-SPEED OPERATIONAL AMPLIFIER

#### Precision Monolithics Inc.

#### **FEATURES**

| • | Fast Settling Time             |

|---|--------------------------------|

| • | High Slew Rate 12V/μs Min      |

| • | Power Bandwidth 150kHz Min     |

| • | Low Power Consumption 90mW Max |

- Excellent DC Specifications

- Internally Compensated

- Ideal DAC Output Amplifier

- MIL-STD-883 Processing Available

- Fits Standard 741 Sockets

- Low Cost

- Available in Die Form

#### ORDERING INFORMATION 1

| T. = 25°C                                            |        | PACKAGE         |                  | OPERATING            |  |

|------------------------------------------------------|--------|-----------------|------------------|----------------------|--|

| T <sub>A</sub> = 25°C<br>V <sub>OS</sub> MAX<br>(mV) | TO-99  | CERDIP<br>8-PIN | PLASTIC<br>8-PIN | TEMPERATURE<br>RANGE |  |

| 0.7                                                  | OP01J* | _               | _                | MIL                  |  |

| 0.7                                                  |        | _               | OP01HP           | COM                  |  |

| 5.0                                                  | OP01GJ | _               | _                | MIL                  |  |

| 5.0                                                  | OP01CJ | OP01CZ          | OP01CP           | СОМ                  |  |

- For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

- Burn-in is available on commercial and industrial temperature range parts in CerDIP, plastic DIP, and TO-can packages. For ordering information, see 1990/91 Data Book, Section 2.

#### **GENERAL DESCRIPTION**

The OP-01 series of monolithic inverting high-speed operational amplifiers combines high slew rate, fast settling time

and excellent DC input characteristics. An internal feed-forward frequency compensation network provides simplicity of application — no external capacitors are required for stable, high-speed performance. The fast output response is achieved without sacrifice of input bias current or power consumption. A 250kHz typical power bandwidth is attained with a small-signal bandwidth of only 2.5MHz, thus board layout is non-critical. The OP-01 is completely protected at both input and output, fits standard 741 sockets, and is offset nulled with a  $10 \mathrm{k}\Omega$  potentiometer.

The fast output response combined with excellent settling time makes the OP-01 ideal for use as a D/A converter output amplifier.

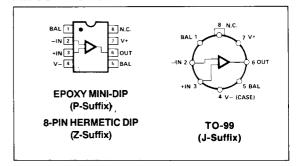

#### PIN CONNECTIONS

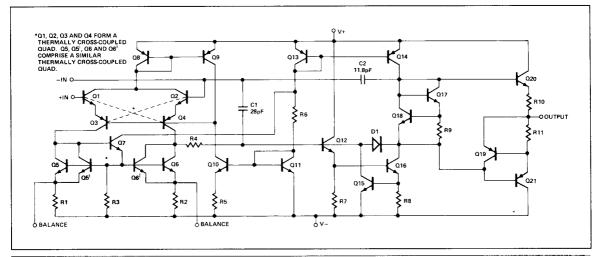

#### SIMPLIFIED SCHEMATIC

| ABSOLUTE MAXIMUM RATINGS               | S (Note 1)         |

|----------------------------------------|--------------------|

| Total Supply Voltage, OP-01, OP-01H    | , OP-01N, OP-01NT, |

| OP-01G, OP-01GT                        | ±22V               |

| OP-01G, OP-01C, OP-01GR                | ±20V               |

| Differential Input Voltage             | ±30V               |

| Input Voltage (Note 2)                 | ±15V               |

| Short-Circuit Duration                 | Indefinite         |

| Operating Temperature Range            |                    |

| OP-01, OP-01G                          | 5°C to +125°C      |

| OP-01H, OP-01C                         | 0°C to +70°C       |

| Junction Temperature (T <sub>i</sub> ) | 65°C to +150C      |

| Storage Temperature                    |                    |

| J and Z Packages                       | 65°C to +150°C     |

| P Packages                             | -65°C to +150°C    |

| Lead Temperature | (Soldering, 60 sec) | +300°C |

|------------------|---------------------|--------|

|                  |                     |        |

| PACKAGE TYPE           | Θ <sub>JA</sub> (NOTE 3) | Θ <sub>JC</sub> | UNITS |

|------------------------|--------------------------|-----------------|-------|

| TO-99 (J)              | 170                      | 24              | °C/W  |

| 8-Pin Hermetic DIP (Z) | 162                      | 26              | °C/W  |

| 8-Pin Plastic DIP (P)  | 110                      | 50              | °C/W  |

#### NOTES:

- Absolute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

- 2. For supply voltages less than  $\pm 15 \text{V}$ , the maximum input voltage is the supply voltage.

- 3.  $\Theta_{j_A}$  is specified for worst case mounting conditions, i.e.,  $\Theta_{j_A}$  is specified for device in socket for TO, CerDIP and P-DIP packages.

## **ELECTRICAL CHARACTERISTICS** at $V_S = \pm 15V$ , $T_A = 25^{\circ}$ C, unless otherwise noted.

|                                                  |                 |                                                             |                  | OP-01<br>OP-01   |     |                  | OP-010         |     | -            |

|--------------------------------------------------|-----------------|-------------------------------------------------------------|------------------|------------------|-----|------------------|----------------|-----|--------------|

| PARAMETER                                        | SYMBOL          | CONDITIONS                                                  | MIN              | TYP              | MAX | MIN              | TYP            | MAX | UNITS        |

| Input Offset Voltage                             | Vos             | $R_S \le 20k\Omega$                                         | _                | 0.3              | 0.7 | -                | 2.0            | 5.0 | mV           |

| Input Offset Current                             | Ios             |                                                             | _                | 0.5              | 2.0 | _                | 2.0            | 20  | nA           |

| Input Bias Current                               | I <sub>B</sub>  |                                                             | _                | 18               | 30  | _                | 25             | 100 | nA           |

| Input Voltage Range                              | IVR             |                                                             | ± 12             | ±13              | _   | ± 12             | ±13            | _   | V            |

| Common-Mode<br>Rejection Ratio                   | CMRR            | $V_{CM} = \pm 10V$ $R_S \le 20k\Omega$                      | 85               | 110              | _   | 80               | 100            |     | dB           |

| Power Supply<br>Rejection Ratio                  | PSRR            | $V_S = \pm 5V \text{ to } \pm 20V$ $R_S \le 20k\Omega$      | _                | 10               | 60  | _                | 100            | 150 | μV/V         |

| Output Voltage Swing                             | v <sub>o</sub>  | $R_L \ge 5k\Omega$ $R_L \ge 2k\Omega$                       | ± 12.5<br>± 12.0 | ± 13.5<br>± 13.0 | _   | ± 12.5<br>± 12.0 | ±13.5<br>±13.0 | _   | v            |

| Large-Signal<br>Voltage Gain                     | A <sub>VO</sub> | $R_L \ge 2k\Omega$<br>$V_O = \pm 10V$                       | 50               | 100              | _   | 25               | 75             | _   | V/mV         |

| Power Consumption                                | P <sub>d</sub>  | V <sub>OUT</sub> = 0                                        | _                | 50               | 90  | _                | 50             | 90  | mW           |

| Settling Time<br>to 0.1% (Summing<br>Node Error) | t <sub>S</sub>  | A <sub>V</sub> = -1<br>(Notes 1, 2)<br>V <sub>IN</sub> = 5V |                  | 0.7              | 1.0 | -                | 0.7            | 1.0 | μS           |

| Slew Rate<br>(Notes 2, 3)                        | SR              | $A_V = -1$ ,<br>$R_S = 3k$ to $5k\Omega$                    | 12               | 18               | _   | 12               | 18             | _   | V/μ <b>s</b> |

| Large-Signal<br>Bandwidth<br>(Notes 3, 4)        |                 |                                                             | 150              | 250              | _   | 150              | 250            | _   | kHz          |

| Small-Signal<br>Bandwidth<br>(Notes 3, 4)        |                 |                                                             | 1.5              | 2.5              |     | 1.5              | 2.5            | _   | MHz          |

| Risetime                                         | t <sub>r</sub>  | A <sub>V</sub> = -1<br>V <sub>IN</sub> = 50mV               | _                | 150              | -   | _                | 150            | _   | ns           |

| Overshoot                                        | os              |                                                             | _                | 2                | _   | _                | 2              | _   | %            |

#### NOTES:

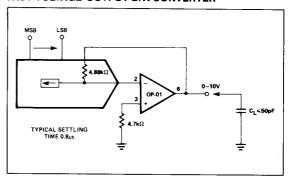

- 1.  $R_L = 25k\Omega$ ;  $C_L = 50pF$ . See Settling Time Test Circuit.

- 2. Sample tested.

- 3. See applications information.

- 4. Guaranteed by design.

**ELECTRICAL CHARACTERISTICS** at  $V_S = \pm 15V$ ,  $-55^{\circ}$  C  $\leq T_A \leq +125^{\circ}$  C for OP-01, OP-01G and  $0^{\circ}$  C  $\leq T_A \leq +70^{\circ}$  C for OP-01H, OP-01C, unless otherwise noted.

|                                 |                   |                                                           |                  | OP-01<br>OP-011 |     |                | OP-010         |              |        |

|---------------------------------|-------------------|-----------------------------------------------------------|------------------|-----------------|-----|----------------|----------------|--------------|--------|

| PARAMETER                       | SYMBOL            | CONDITIONS                                                | MIN              | TYP             | MAX | MIN            | TYP            | MAX          | UNITS  |

| Input Offset Voltage            | v <sub>os</sub>   | $R_S \leq 20k\Omega$                                      | _                | 0.4             | 1.0 |                | 3.0            | 6.0          | mV     |

| Input Offset Current            | Ios               |                                                           | <u> </u>         | 1               | 4   | _              | 4              | 40           | nA     |

| Input Bias Current              | I <sub>B</sub>    |                                                           | _                | 30              | 50  |                | 50             | 200          | nA     |

| Input Voltage Range             | IVR               |                                                           | ± 10             | ±13             | _   | ± 10           | ±13            | _            | ٧      |

| Common-Mode<br>Rejection Ratio  | CMRR              | $V_{CM} = \pm 10V$ $R_S \le 20k\Omega$                    | 85               | 110             | -   | 80             | 100            | -            | dB     |

| Power Supply<br>Rejection Ratio | PSRR              | $V_S = \pm 5V \text{ to } \pm 20V$<br>$R_S \le 20k\Omega$ | _                | 10              | 60  | _              | 100            | 150          | μV/V   |

| Large-Signal<br>Voltage Gain    | A <sub>vo</sub>   | $R_L \ge 2k\Omega$<br>$V_O = \pm 10V$                     | 30               | 60              | _   | 15             | 50             | _            | V/mV   |

| Output Voltage Swing            | v <sub>o</sub>    | $R_{L} \ge 5k\Omega$<br>$R_{L} \ge 2k\Omega$              | ± 12.5<br>± 12.0 | ±13.5<br>±13.0  | _   | ±12.5<br>±12.0 | ±13.5<br>±13.0 | <del>-</del> | ٧      |

| Offset Voltage Drift (Note 1)   | TCV <sub>OS</sub> | R <sub>S</sub> ≤5kΩ                                       | _                | 2               | 8   | _              | 5              | 20           | μV/° C |

#### NOTE:

<sup>1.</sup> Sample tested.

### DICE CHARACTERISTICS (125°C TESTED DICE AVAILABLE)

DIE SIZE  $0.047 \times 0.043$  inch, 2021 sq. mils  $(1.19 \times 1.09 \text{ mm}, 1.30 \text{ sq. mm})$

- 1. NULL

- 2. INVERTING INPUT

- 3. NONINVERTING INPUT

- 4. V-

- 5. NULL

- 6. OUTPUT

- 7. V+

For additional DICE ordering information, refer to 1990/91 Data Book, Section 2.

**WAFER TEST LIMITS** at  $V_S = \pm$  15V,  $T_A = 25$  °C for OP-01N, OP-01G and OP-01GR devices;  $T_A = 125$  °C for OP-01NT and OP-01GT devices, unless otherwise noted.

| PARAMETER                       | SYMBOL          | CONDITIONS                                                | OP-01NT        | OP-01N<br>LIMIT | OP-01GT          | OP-01G         | OP-01GR          | UNITS    |

|---------------------------------|-----------------|-----------------------------------------------------------|----------------|-----------------|------------------|----------------|------------------|----------|

| Input Offset Voltage            | v <sub>os</sub> | R <sub>S</sub> ≤20kΩ                                      | 1.0            | 0.7             | 3.0              | 2.0            | 5.0              | mV MAX   |

| Input Offset Current            | los             |                                                           | 4              | 2               | 10               | 5              | 20               | пА МАХ   |

| Input Bias Current              | I <sub>B</sub>  |                                                           | 50             | 30              | 100              | 50             | 100              | nA MAX   |

| Input Voltage Range             | IVR             |                                                           | ± 10           | ±12             | ±10              | ±12            | ± 12             | V MIN    |

| Common-Mode<br>Rejection Ratio  | CMRR            | $V_{CM} = \pm 10V$ $R_S \le 20k\Omega$                    | 85             | 85              | 80               | 80             | 80               | dB MIN   |

| Power Supply<br>Rejection Ratio | PSRR            | $V_S = \pm 5V \text{ to } \pm 20V$<br>$R_S \le 20k\Omega$ | 60             | 60              | 100              | 100            | 150              | μV/V MAX |

| Output Voltage<br>Swing         | V <sub>OM</sub> | $R_L \ge 5k\Omega$<br>$R_L \ge 2k\Omega$                  | ±12.5<br>±12.0 | ±12.5<br>±12.0  | ± 12.5<br>± 12.0 | ±12.5<br>±12.0 | ± 12.5<br>± 12.0 | V MIN    |

| Large-Signal<br>Voltage Gain    | A <sub>VO</sub> | $R_L \ge 2k\Omega$<br>$V_O = \pm 10V$                     | 30             | 50              | 25               | 50             | 25               | V/mV MIN |

| Power Consumption               | Pd              | V <sub>OUT</sub> = 0                                      | _              | 90              | _                | 90             | 90               | mW MAX   |

#### NOTES:

For 25°C characteristics of NT & GT devices, see N & G characteristics respectively.

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

## TYPICAL ELECTRICAL CHARACTERISTICS at $V_S = \pm 15 V$ , $T_A = 25^{\circ}$ C, unless otherwise noted.

| PARAMETER                                    | SYMBOL         | CONDITIONS                                                                                       | ALL GRADES TYPICAL | UNITS |

|----------------------------------------------|----------------|--------------------------------------------------------------------------------------------------|--------------------|-------|

| Slew Rate                                    | SR             | $A_{VCL} = -1$ , $R_S = 3k\Omega$ to $5k\Omega$                                                  | 18                 | V/μs  |

| Settling Time to<br>0.1%<br>(Summing Node Er | t <sub>S</sub> | $V_{IN} = 5V$ $A_V = -1$ $R_L = 2k\Omega \text{ (See Settling Time Test Circuit)}$ $C_L = 50 pF$ | 1.0                | μs    |

| Large-Signal<br>Bandwidth                    |                |                                                                                                  | 250                | kHz   |

| Small-Signal<br>Bandwidth                    |                |                                                                                                  | 2.5                | MHz   |

| Risetime                                     | t <sub>r</sub> | $V_{IN} = 50 \text{mV}$ $A_V = -1$                                                               | 150                | ns    |

#### TYPICAL PERFORMANCE CHARACTERISTICS

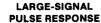

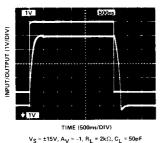

# SMALL-SIGNAL PULSE RESPONSE

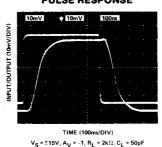

# UNITY-GAIN BANDWIDTH

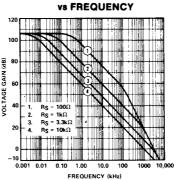

# OPEN-LOOP GAIN

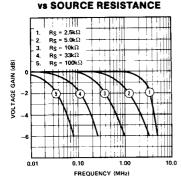

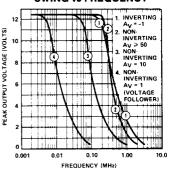

#### LARGE-SIGNAL OUTPUT SWING VS FREQUENCY

#### **APPLICATIONS INFORMATION**

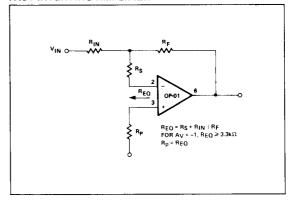

The OP-01 incorporates an internal feed-forward compensation network to provide fast slewing and settling times in all inverting and moderate-to-high-gain noninverting applications. Unity-gain bandwidth is a function of the total equivalent source resistance seen by the inverting terminal. Proper choice of this resistance will allow the user to maxmize bandwidth while assuring proper stability. The equivalentinverting-terminal-resistance is defined as  $R_{\text{IN}} ||\, R_{\text{F}},$  and it must be greater than  $3.3k\Omega$  to assure stability in all closedloop gain configurations including unity gain. Should  $R_{IN} || R_F \le 3.3 k\Omega$ , a resistor  $(R_S)$  may be placed between the inverting input and the sum node to provide the required resistance. (See Fast Inverting Amplifier Diagram.) Lower values of total equivalent resistance may be used to improve bandwidth in higher closed-loop gain configurations, as indicated by the Open-Loop Gain vs. Frequency plot.

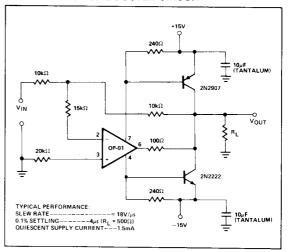

#### **FAST INVERTING AMPLIFIER**

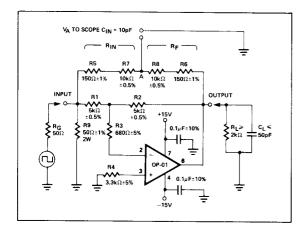

#### **SETTLING-TIME TEST CIRCUIT**

Settling time may be measured using the circuit shown below. This circuit incorporates the "false sum node" technique to produce accurate, repeatable results. For a 5V input step, 0.1% settling will be achieved when the false sum node settles to within  $\pm 2.5 \text{mV}$  of its final value. The oscilloscope used for observation of the false sum node should have wide bandwidth, fast overload recovery time, and be used with a low capacity probe ( $\leq 10 \text{pF}$ , including strays). A Tektronix 7504 scope with a 7A11 probe or equivalent is suggested. The pulse generator should have a  $50\Omega$  output impedance and be capable of a 5V rise time in  $\leq 20 \text{ns}$  with ringing less than 2.5 mV after  $0.5 \mu \text{s}$ . Measurements to 0.1% require  $R_{\text{IN}}$  to equal  $R_{\text{F}}$  within 0.01%,  $R_{\text{S}}$  and  $R_{\text{G}}$  are used as trimming resistors to achieve this matching.

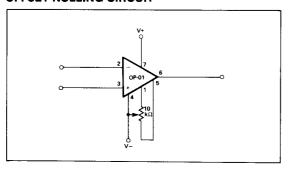

#### **OFFSET NULLING CIRCUIT**

#### **TYPICAL APPLICATIONS**

### **FAST VOLTAGE-OUTPUT D/A CONVERTER**

#### PRECISION POWER-BOOSTER CIRCUIT