UC1637 UC2637 UC3637

# Switched Mode Controller for DC Motor Drive

#### **FEATURES**

- Single or Dual Supply Operation

- ±2.5V to ±20V Input Supply Range

- ±5% Initial Oscillator Accuracy; ± 10% Over Temperature

- Pulse-by-Pulse Current Limiting

- Under-Voltage Lockout

- Shutdown Input with Temperature Compensated 2.5V Threshold

- Uncommitted PWM Comparators for Design Flexibility

- Dual 100mA, Source/Sink Output Drivers

#### **DESCRIPTION**

The UC1637 is a pulse width modulator circuit intended to be used for a variety of PWM motor drive and amplifier applications requiring either uni-directional or bi-directional drive circuits. When used to replace conventional drivers, this circuit can increase efficiency and reduce component costs for many applications. All necessary circuitry is included to generate an analog error signal and modulate two bi-directional pulse train outputs in proportion to the error signal magnitude and polarity.

This monolithic device contains a sawtooth oscillator, error amplifier, and two PWM comparators with  $\pm 100$ mA output stages as standard features. Protection circuitry includes under-voltage lockout, pulse-by-pulse current limiting, and a shutdown port with a 2.5V temperature compensated threshold.

The UC1637 is characterized for operation over the full military temperature range of -55 $^{\circ}$ C to +125 $^{\circ}$ C, while the UC2637 and UC3637 are characterized for -25 $^{\circ}$ C to +85 $^{\circ}$ C and 0 $^{\circ}$ C to +70 $^{\circ}$ C, respectively.

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Supply Voltage (±Vs)                                          | 20V |

|---------------------------------------------------------------|-----|

| Output Current, Source/Sink (Pins 4, 7)                       | mΑ  |

| Analog Inputs (Pins 1, 2, 3, 8, 9, 10, 11 12, 13, 14, 15, 16) | ∶Vs |

| Error Amplifier Output Current (Pin 17) ±20                   | mΑ  |

| Oscillator Charging Current (Pin 18)2                         | mΑ  |

| Power Dissipation at TA = 25°C (Note 2)                       | тW  |

| Power Dissipation at Tc = 25°C (Note 2)                       | пW  |

| Storage Temperature Range65°C to +150                         | 0°C |

| Lead Temperature (Soldering, 10 Seconds)+300                  | )°C |

|                                                               |     |

Note 1: Currents are positive into, negative out of the specified terminal.

Note 2: Consult Packaging Section of Databook for thermal limitations and considerations of package.

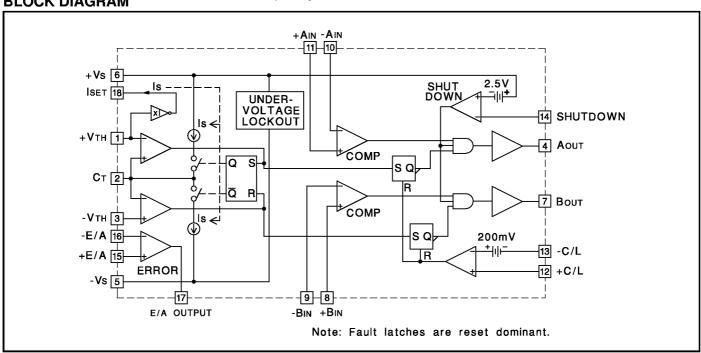

#### **BLOCK DIAGRAM**

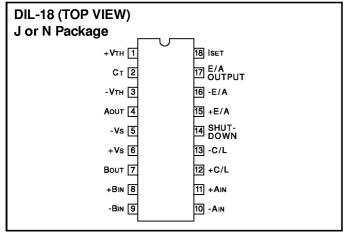

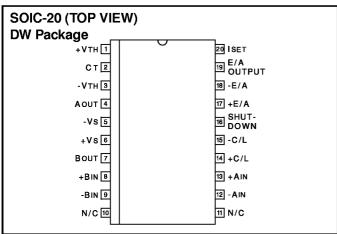

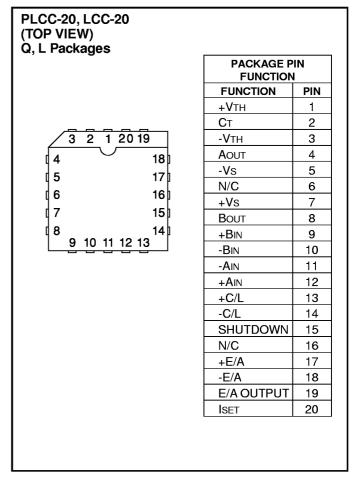

## **CONNECTION DIAGRAM**

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications apply for Ta = -55°C to +125°C for the UC1637; -25°C to +85°C for the UC2637; and 0°C to +70°C for the UC3637; + $\frac{1}{2}$  +15V, -Vs = -15V, +VTH = 5V, -VTH = -5V, RT = 16.7kΩ, CT = 1500pF, Ta=TJ.

| PARAMETER               | TEST CONDITIONS                                              | UC1   | UC1637/UC2637 |       |       | UC3637 |       |      |

|-------------------------|--------------------------------------------------------------|-------|---------------|-------|-------|--------|-------|------|

|                         |                                                              | MIN   | TYP           | MAX   | MIN   | TYP    | MAX   |      |

| Oscillator              |                                                              | •     |               |       |       |        |       |      |

| Initial Accuracy        | T <sub>J</sub> = 25 °C (Note 6)                              | 9.4   | 10            | 10.6  | 9     | 10     | 11    | kHz  |

| Voltage Stability       | $Vs = \pm 5V \text{ to } \pm 20V, VPIN 1 = 3V, VPIN 3 = -3V$ |       | 5             | 7     |       | 5      | 7     | %    |

| Temperature Stability   | Over Operating Range (Note 3)                                |       | 0.5           | 2     |       | 0.5    | 2     | %    |

| +Vтн Input Bias Current | VPIN 2 = 6V                                                  | -10   | 0.1           | 10    | -10   | 0.1    | 10    | μΑ   |

| -Vтн Input Bias Current | VPIN 2 = 0V                                                  | -10   | -0.5          |       | -10   | -0.5   |       | μΑ   |

| +Vтн, -Vтн Input Range  |                                                              | +Vs-2 |               | -Vs+2 | +Vs-2 |        | -Vs+2 | ٧    |

| Error Amplifier         |                                                              | •     |               |       |       |        |       |      |

| Input Offset Voltage    | VCM = 0V                                                     |       | 1.5           | 5     |       | 1.5    | 10    | mV   |

| Input Bias Current      | VCM = 0V                                                     |       | 0.5           | 5     |       | 0.5    | 5     | μΑ   |

| Input Offset Current    | VCM = 0V                                                     |       | 0.1           | 1     |       | 0.1    | 1     | μΑ   |

| Common Mode Range       | Vs = ±2.5 to 20V                                             | -Vs+2 |               | +Vs   | -Vs+2 |        | +Vs   | ٧    |

| Open Loop Voltage Gain  | RL = 10k                                                     | 75    | 100           |       | 80    | 100    |       | dB   |

| Slew Rate               |                                                              |       | 15            |       |       | 15     |       | V/µs |

| Unity Gain Bandwidth    |                                                              |       | 2             |       |       | 2      |       | MHz  |

| CMRR                    | Over Common Mode Range                                       | 75    | 100           |       | 75    | 100    |       | dB   |

| PSRR                    | Vs = ±2.5 to ±20V                                            | 75    | 110           |       | 75    | 110    |       | dB   |

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications apply for Ta = -55°C to +125°C for the UC1637; -25°C to +85°C for the UC2637; and 0°C to +70°C for the UC3637: $\frac{1}{2}$  +15V, -Vs = -15V, +VTH = 5V, -VTH = -5V, RT = 16.7kΩ, CT = 1500pF, Ta=TJ.

| PARAMETERS                  | TEST CONDITIONS                     | UC1   | 637/UC | 2637  | UC3637 |       |       | UNITS |

|-----------------------------|-------------------------------------|-------|--------|-------|--------|-------|-------|-------|

|                             |                                     | MIN   | TYP    | MAX   | MIN    | TYP   | MAX   |       |

| Error Amplifier (Continued) |                                     |       |        |       |        |       |       |       |

| Output Sink Current         | VPIN 17 = <b>0V</b>                 |       | -50    | -20   |        | -50   | -20   | mA    |

| Output Source Current       | VPIN 17 = <b>0V</b>                 | 5     | 11     |       | 5      | 11    |       | mA    |

| High Level Output Voltage   |                                     | 13    | 13.6   |       | 13     | 13.6  |       | ٧     |

| Low Level Output Voltage    |                                     |       | -14.8  | -13   |        | -14.8 | -13   | V     |

| PWM Comparators             |                                     |       |        |       |        |       |       |       |

| Input Offset Voltage        | VcM = 0V                            |       | 20     |       |        | 20    |       | mV    |

| Input Bias Current          | VcM = 0V                            |       | 2      | 10    |        | 2     | 10    | μΑ    |

| Input Hysteresis            | Vcm = 0V                            |       | 10     |       |        | 10    |       | mV    |

| Common Mode range           | Vs = ±5V to ±20V                    | -Vs+1 |        | +Vs-2 | -Vs+1  |       | +Vs-2 | V     |

| Current Limit               |                                     |       |        |       |        |       |       |       |

| Input Offset Voltage        | Vcm = 0V, TJ = 25°C                 | 190   | 200    | 210   | 180    | 200   | 220   | mV    |

| Input Offset Voltage T.C.   |                                     |       | -0.2   |       |        | -0.2  |       | mV/°C |

| Input Bias Current          |                                     | -10   | -1.5   |       | -10    | -1.5  |       | μΑ    |

| Common Mode Range           | $Vs = \pm 2.5V \text{ to } \pm 20V$ | -Vs   |        | +Vs-3 | -Vs    |       | +Vs-3 | V     |

| Shutdown                    |                                     |       |        |       |        |       |       |       |

| Shutdown Threshold          | (Note 4)                            | -2.3  | -2.5   | -2.7  | -2.3   | -2.5  | -2.7  | ٧     |

| Hysteresis                  |                                     |       | 40     |       |        | 40    |       | mV    |

| Input Bias Current          | VPIN 14 = +VS to -VS                | -10   | -0.5   |       | -10    | -0.5  |       | μΑ    |

| Under-Voltage Lockout       |                                     |       |        |       |        |       |       |       |

| Start Threshold             | (Note 5)                            |       | 4.15   | 5.0   |        | 4.15  | 5.0   | V     |

| Hysteresis                  |                                     |       | 0.25   |       |        | 0.25  |       | mV    |

| Total Standby Current       |                                     |       |        |       |        |       |       |       |

| Supply Current              |                                     |       | 8.5    | 15    |        | 8.5   | 15    | mA    |

| Output Section              |                                     |       |        |       |        |       |       |       |

| Output Low Level            | ISINK = 20mA                        |       | -14.9  | -13   |        | -14.9 | -13   | V     |

|                             | ISINK = 100mA                       |       | -14.5  | -13   |        | -14.5 | -13   |       |

| Output High Level           | ISOURCE = 20mA                      | 13    | 13.5   |       | 13     | 13.5  |       | ٧     |

|                             | ISOURCE = 100mA                     | 12    | 13.5   |       | 12     | 13.5  |       |       |

| Rise Time                   | (Note 3) CL = Inf, TJ = 25°C        |       | 100    | 600   |        | 100   | 600   | ns    |

| Fall Time                   | (Note 3) CL = Inf, TJ = 25°C        |       | 100    | 300   |        | 100   | 300   | ns    |

- Note 3: These parameters, although guaranteed over the recommended operating conditions, are not 100% tested in production.

- Note 4: Parameter measured with respect to +Vs (Pin 6).

- Note 5: Parameter measured at +Vs (Pin 6) with respect to -Vs (Pin 5).

- Note 6: RT and CT referenced to Ground.

#### **FUNCTIONAL DESCRIPTION**

Following is a description of each of the functional blocks shown in the Block Diagram.

## Oscillator

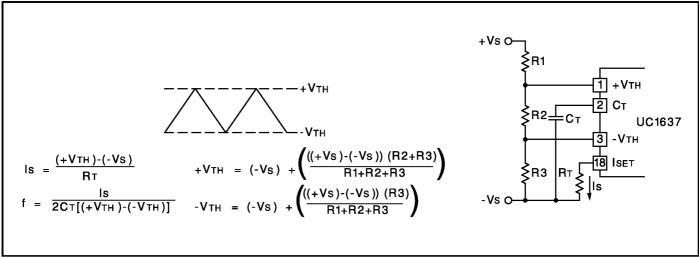

The oscillator consists of two comparators, a charging and discharging current source, a current source set terminal, ISET and a flip-flop. The upper and lower threshold of the oscillator waveform is set externally by applying a voltage at pins +VTH and -VTH respectively. The +VTH ter-

minal voltage is buffered internally and also applied to the ISET terminal to develop the capacitor charging current through RT. If RT is referenced to -Vs as shown in Figure 1, both the threshold voltage and charging current will vary proportionally to the supply differential, and the oscillator frequency will remain constant. The triangle waveform oscillators frequency and voltage amplitude is determined by the external components using the formulas given in Figure 1.

Figure 1. Oscillator Setup

#### **PWM Comparators**

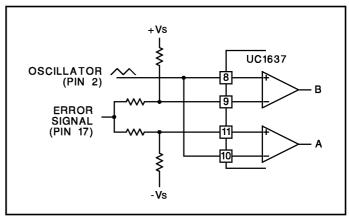

Two comparators are provided to perform pulse width modulation for each of the output drivers. Inputs are uncommitted to allow maximum flexibility. The pulse width of the outputs A and B is a function of the sign and amplitude of the error signal. A negative signal at Pin 10 and 8 will lengthen the high state of output A and shorten the high state of output B. Likewise, a positive error signal reverses the procedure. Typically, the oscillator waveform is compared against the summation of the error signal and the level set on Pin 9 and 11.

## **MODULATION SCHEMES**

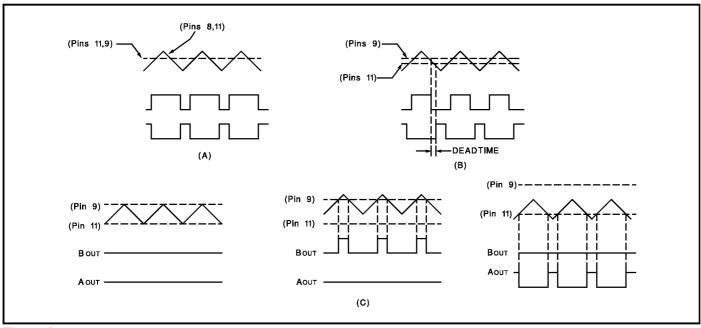

Case A Zero Deadtime (Equal voltage on Pin 9 and Pin 11) In this configuration, maximum holding torque or stiffness and position accuracy is achieved. However, the power input into the motor is increased. Figure 3A shows this configuration.

## Case B Small Deadtime (Voltage on Pin 9 > Pin 11)

A small differential voltage between Pin 9 and 11 provides the necessary time delay to reduce the chances of momentary short circuit in the output stage during transitions, especially where power-amplifiers are used. Refer to Figure 3B.

# Case C Increased Deadtime and Deadband Mode (Voltage on Pin 9 > Pin 11)

With the reduction of stiffness and position accuracy, the power input into the motor around the null point of the servo loop can be reduced or eliminated by widening the window of the comparator circuit to a degree of acceptance. Where position accuracy and mechanical stiffness is unimportant, deadband operation can be used. This is shown in Figure 3C.

Figure 2. Comparator Biasing

#### **Output Drivers**

Each output driver is capable of both sourcing and sinking 100mA steady state and up to 500mA on a pulsed basis for rapid switching of either POWERFET or bipolar transistors. Output levels are typically -Vs + 0.2V @50mA low level and +Vs - 2.0V @50mA high level.

#### **Error Amplifier**

The error amplifier consists of a high slew rate ( $15V/\mu s$ ) op-amp with a typical 1MHz bandwidth and low output impedance. Depending on the  $\pm Vs$  supply voltage, the common mode input range and the voltage output swing is within 2V of the Vs supply.

#### **Under-Voltage Lockout**

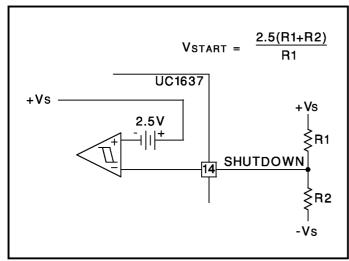

An under-voltage lockout circuit holds the outputs in the low state until a minimum of 4V is reached. At this point, all internal circuitry is functional and the output drivers are enabled. If external circuitry requires a higher starting voltage, an over-riding voltage can be programmed through the shutdown terminal as shown in Figure 4.

Figure 3. Modulation Schemes Showing (A) Zero Deadtime (B) Deadtime and (C) Deadband Configurations

### **Shutdown Comparator**

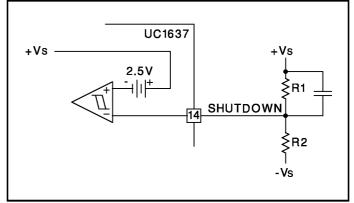

The shutdown terminal may be used for implementing various shutdown and protection schemes. By pulling the terminal more than 2.5V below VIN, the output drivers will be enabled. This can be realized using an open collector gate or NPN transistor biased to either ground or the negative supply. Since the threshold is temperature stabilized, the comparator can be used as an accurate low voltage lockout (Figure 4) and/or delayed start as in Figure 5. In the shutdown mode the outputs are held in the low state.

Figure 4. External Under-Voltage Lockout

#### **Current Limit**

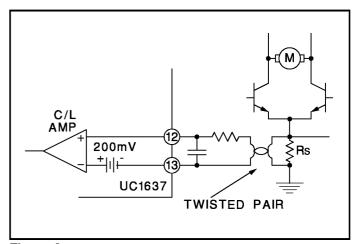

A latched current limit amplifier with an internal 200mV offset is provided to allow pulse-by-pulse current limiting. Differential inputs will accept common mode signals from

Figure 5. Delayed Start-Up

-Vs to within 3V of the +Vs supply while providing excellent noise rejection. Figure 6 shows a typical current sense circuit.

Figure 6. Current Limit Sensing

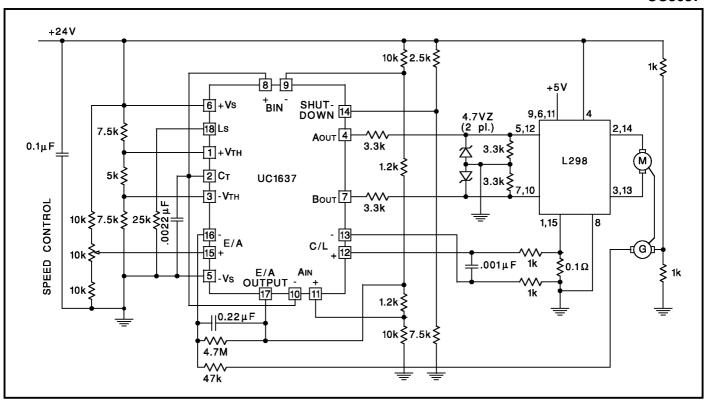

Figure 7. Bi-Directional Motor Drive with Speed Control Power-Amplifier

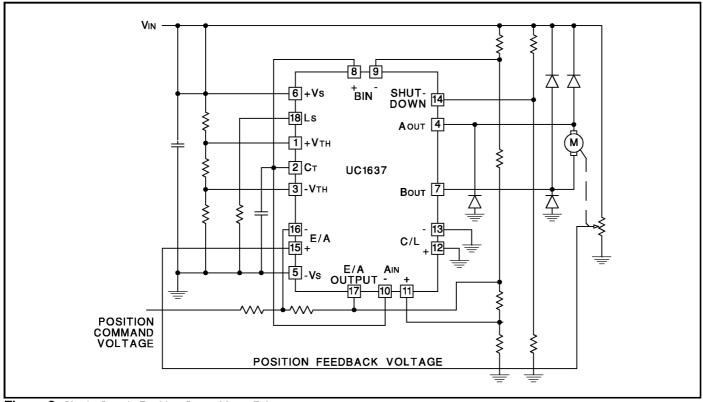

Figure 8. Single Supply Position Servo Motor Drive

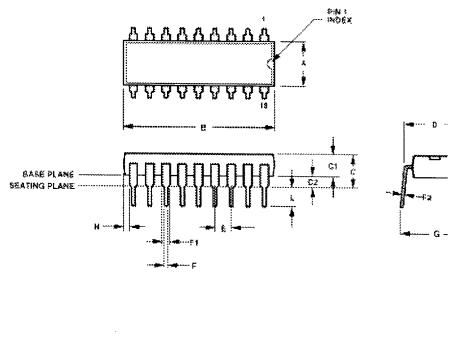

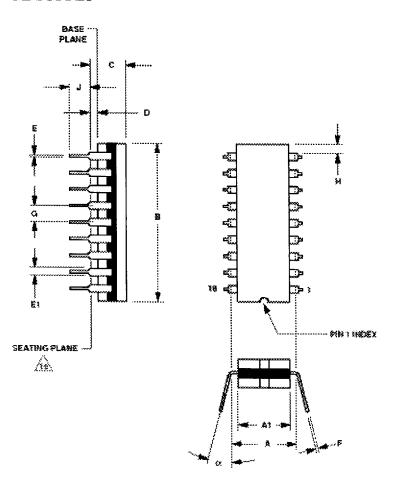

# 18-PIN PLASTIC DIP ~ N PACKAGE SUFFIX

|    | INC      | HES  | MILLIM | MILLIMETERS |   |  |

|----|----------|------|--------|-------------|---|--|

|    | MIN      | MAX  | MIN    | MAX         |   |  |

| Α  | .245     | .260 | 6.22   | 6.60        | 1 |  |

| В  | .890     | .920 | 22.61  | 23.39       | 1 |  |

| С  | -        | .210 | -      | 5.33        |   |  |

| C1 | .125     | .150 | 3.18   | 3.81        |   |  |

| C2 | .015     | .055 | 0.38   | 1.40        | 2 |  |

| D  | .300     | .325 | 7.62   | 8.26        | 3 |  |

| E  | .100 BSC |      | 2.54   | BSC         | 4 |  |

| F  | .014     | .022 | 0.35   | 0.56        |   |  |

| F1 | .045     | .070 | 1.14   | 1.78        |   |  |

| F2 | .008     | .014 | 0.20   | 0.35        |   |  |

| G  | 300      | .400 | 7.62   | 10.16       | 5 |  |

| Н  | .005     | -    | 0.13   | -           |   |  |

| L  | .115     | .160 | 2.92   | 4.06        |   |  |

- 1. 'A' AND 'B' DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 IN. PER SIDE.

- 2. 'C2' SHALL BE MEASURED FROM THE SEATING PLANE TO THE BASE PLANE.

- 3. 'D' SHALL BE MEASURED WITH THE LEADS CONSTRAINED TO BE PERPENDICULAR TO THE BASE PLANE.

- 4. THE BASIC LEAD SPACING IS 0.100 IN. BETWEEN CENTERLINES. EACH LEAD CENTERLINE SHALL BE LOCATED WITHIN  $\pm 0.010$  IN. OF ITS EXACT TRUE POSITION.

- 5. 'G' SHALL BE MEASURED AT THE LEAD TIPS WITH THE LEADS UNCONSTRAINED.

- 6. CONTROLLING DIMENSION: INCHES. MILLIMETERS SHOWN FOR REFERENCE ONLY.

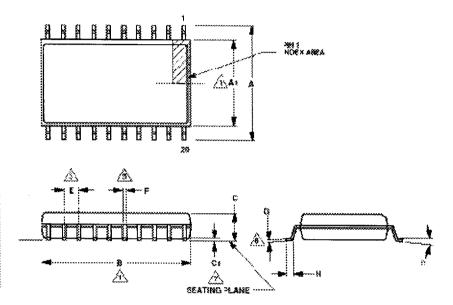

# 20-PIN SOIC SURFACE MOUNT~ DW PACKAGE SUFFIX

|    | DIMENSIONS |      |        |       |  |  |  |  |

|----|------------|------|--------|-------|--|--|--|--|

|    | INC        | HES  | MILLIM | ETERS |  |  |  |  |

|    | MIN        | MAX  | MIN    | MAX   |  |  |  |  |

| Α  | .394       | .419 | 10.00  | 10.64 |  |  |  |  |

| A1 | .292       | 299  | 7.42   | 7.59  |  |  |  |  |

| В  | .504       | .511 | 12.80  | 12.98 |  |  |  |  |

| С  | .097       | .104 | 2.46   | 2.64  |  |  |  |  |

| C1 | .004       | .011 | 0.10   | 0.28  |  |  |  |  |

| E  | .050       | BSC  | 1.27   | BSC   |  |  |  |  |

| F  | .014       | .019 | 0.36   | 0.48  |  |  |  |  |

| G  | .009       | .012 | 0.23   | 0.30  |  |  |  |  |

| Н  | .018       | .035 | 0.46   | 0.89  |  |  |  |  |

| Ð  | 0°         | 8°   | 0°     | 8°    |  |  |  |  |

- 'A1' AND 'B' DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 IN. PER SIDE.

- 2. LEADS SHALL BE COPLANAR WITHIN 0.004 IN. AT THE SEATING PLANE.

- THE BASIC LEAD SPACING IS 0.050 IN. BETWEEN CENTERLINES. EACH LEAD CENTERLINE SHALL BE LOCATED WITHIN ±0.004 IN. OF ITS EXACT TRUE POSITION.

- 4. CONTROLLING DIMENSION: INCHES. MILLIMETERS SHOWN FOR REFERENCE ONLY.

- DIMENSION 'F' DOES NOT INCLUDE DAMBAR PROTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 'F' MAXIMUM BY MORE THAN 0.003 IN. DAMBAR CAN NOT BE LOCATED ON THE LOWER RADIUS OR THE LEAD FOOT.

- THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.004 IN. AND 0.010 IN. FROM THE LEAD TIP.

- 'C1' IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY (BASE PLANE).

# 18-PIN CERAMIC DIP ~ J PACKAGE SUFFIX

|    | 1<br>1<br>1 |       |        |       |   |

|----|-------------|-------|--------|-------|---|

|    | INC         | HES   | MILLIN | NOTES |   |

|    | MIN         | MAX   | MIN    | MAX   |   |

| Α  | 0.290       | 0.320 | 7.37   | 8,13  | 7 |

| A1 | 0.220       | 0.310 | 5.59   | 7.87  | 4 |

| В  | -           | 0.960 | -      | 24.38 | 4 |

| С  | -           | 0.200 | -      | 5.08  |   |

| D  | 0.015       | 0.060 | 0.38   | 1.52  | 3 |

| E  | 0.014       | 0.026 | 0.36   | 0.66  | 8 |

| E1 | 0.045       | 0.065 | 1.14   | 1.65  | 2 |

| F  | 0.008       | 0.018 | 0.20   | 0.46  | 8 |

| G  | 0.100 BSC   |       | 2.54   | 5     |   |

| Н  | 0.005       | -     | 0.13   | -     | 6 |

| J  | 0.125       | 0.200 | 3.18   | 5.08  |   |

| 68 | 0°          | 15°   | 0°     | 15°   |   |

- 1. INDEX AREA: A NOTCH OR A PIN ONE IDENTIFICATION MARK SHALL BE LOCATED ADJACENT TO PIN ONE. THE MANUFACTURER'S IDENTIFICATION SHALL NOT BE USED AS A PIN ONE IDENTIFICATION MARK.

- 2. THE MINIMUM LIMIT FOR DIMENSION 'E1' MAY BE 0.023 (0.58mm) FOR LEADS NUMBER 1, 9, 10 AND 18 ONLY.

- 3. DIMENSION 'D' SHALL BE MEASURED FROM THE SEATING PLANE TO THE BASE PLANE.

- THIS DIMENSION ALLOWS FOR OFF-CENTER LID, MENISCUS AND GLASS OVERRUN.

- 5. THE BASIC PIN SPACING IS 0.100 (2.54mm) BETWEEN CENTERLINES. EACH PIN CENTERLINE SHALL BE LOCATED WITHIN ±0.010 (0.25mm) OF ITS EXACT TRUE POSITION.

- 6. APPLIES TO ALL FOUR CORNERS (LEADS NUMBER 1, 9, 10 AND 18).

- 7. DIMENSION 'A' SHALL BE MEASURED AT THE CENTERLINE OF THE LEADS WHEN  $\omega = 0^{\circ}$ .

- 8. THE MAXIMUM LIMITS OF DIMENSIONS 'E' AND 'F' SHALL BE MEASURED AT THE CENTER OF THE FLAT WHEN SOLDER DIP IS APPLIED.

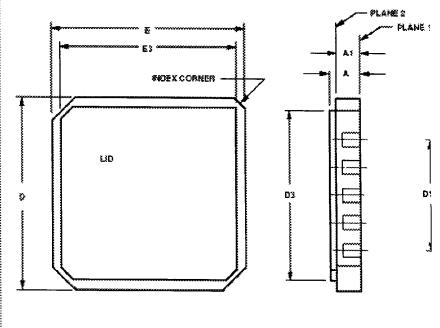

## 20-PIN CERAMIC LEADLESS SURFACE MOUNT ~ L PACKAGE SUFFIX

|       | INC      | HES  | MILLIM | NOTES    |     |  |

|-------|----------|------|--------|----------|-----|--|

|       | MIN      | MAX  | MIN    | MAX      |     |  |

| Α     | .060     | .100 | 1.52   | 2.54     | 6   |  |

| A1    | .050     | .088 | 1.27   | 2.24     |     |  |

| B1    | .022     | .028 | 0.56   | 0.71     | 1,3 |  |

| B2    | .072     | REF. | 1.83   | REF.     |     |  |

| В3    | .006     | .022 | 0.15   | 0.56     | 8   |  |

| D/E   | .342     | .358 | 8.69   | 9.09     |     |  |

| D1/E1 | .200 BSC |      | 5.08   | 5.08 BSC |     |  |

| D2/E2 | .100 BSC |      | 2.54   | BSC      |     |  |

| D3/E3 | -        | .358 | -      | 9.09     | 4   |  |

| L     | .045     | .055 | 1.14   | 1.40     |     |  |

| L1    | .045     | .055 | 1.14   | 1.40     |     |  |

| L2    | .075     | .095 | 1.90   | 2.41     | 5   |  |

| L3    | .003     | .015 | 0.08   | 0.38     |     |  |

| N     | 2        | 20   |        | 20       |     |  |

| ND/NE |          | 5    |        | 2        |     |  |

| е     | .050 BSC |      | 1.27   | 10       |     |  |

- 1. A MINIMUM CLEARANCE OF 0.015 IN. (0.38mm) SHALL BE MAINTAINED BETWEEN ADJACENT TE

- 2. 'N' IS THE MAXIMUM QUANTITY OF TERMINAL POSITIONS. 'ND' AND 'NE' ARE THE NUMBERS OF AND 'E' RESPECTIVELY.

- 3. ELECTRICAL CONNECTION TERMINALS ARE REQUIRED ON PLANE 1 AND OPTIONAL ON PLANE THEY SHALL BE ELECTRICALLY CONNECTED TO OPPOSING TERMINALS ON PLANE 1.

- 4. A MINIMUM CLEARANCE OR 0.015 IN. (0.38mm) SHALL BE MAINTAINED BETWEEN A METAL LID TERMINALS, METALLIZED CASTELLATIONS, ETC.) THE LID SHALL NOT EXTEND BEYOND THE E

- 5. THE INDEX FEATURE FOR NUMBER 1 TERMINAL IDENTIFICATION, OPTIONAL ORIENTATION OR AREA DEFINED BY DIMENSIONS 'B2' AND 'L2' ON PLANE 1.

- 6. DIMENSION 'A' CONTROLS THE OVERALL PACKAGE THICKNESS.

- 7. CONTROLLING DIMENSION: INCHES. MILLIMETERS SHOWN FOR REFERENCE ONLY.

- 8. CASTELLATIONS ARE REQUIRED ON BOTTOM TWO LAYERS. CASTELLATIONS IN THE TOP LAYE

- 9. WHEN SOLDER DIP LEAD FINISH APPLIES, SOLDER BUMP HEIGHT SHALL NOT EXCEED 0.007 INC NOT EXCEED 0.006 INCHES.

- 10. THE BASIC TERMINAL SPACING IS 0.050 INCHES BETWEEN CENTERLINES. EACH TERMINAL CEN INCHES OF ITS EXACT TRUE POSITION.

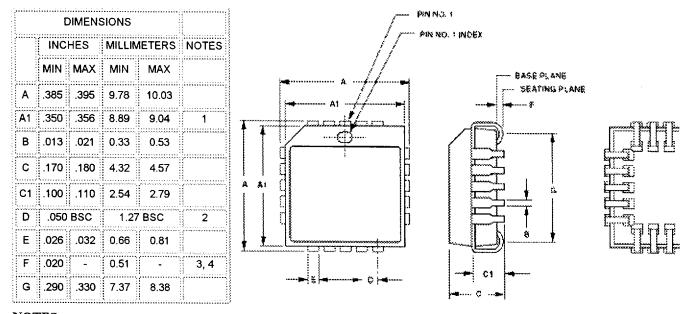

# 20-PIN PLASTIC PLCC SURFACE MOUNT~ Q PACKAGE SUFFIX

- 1. 'A1' DOES NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 IN. PER SIDE.

- 2. THE BASIC LEAD SPACING IS 0.050 IN. BETWEEN CENTERLINES. EACH LEAD CENTERLINE SHALL LOCATED WITHIN  $\pm 0.004$  IN. OF ITS EXACT TRUE POSITION.

- 3. 'F' IS MEASURED FROM THE SEATING PLANE TO THE BASE PLANE.

- 4. LEADS SHALL BE COPLANAR WITHIN 0.004 IN. AT THE SEATING PLANE.

- 5. CONTROLLING DIMENSION: INCHES. MILLIMETERS SHOWN FOR REFERENCE ONLY.