#### **General Description**

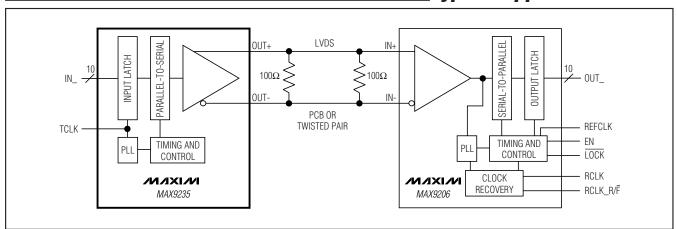

The MAX9235 serializer transforms 10-bit-wide parallel LVCMOS/LVTTL data into a serial high-speed, low-voltage differential signaling (LVDS) data stream. The serializer typically pairs with deserializers like the MAX9206, which receives the serial output and transforms it back to 10-bit-wide parallel data.

The MAX9235 transmits serial data at speeds up to 450Mbps over PCB traces or twisted-pair cables. Since the clock is recovered from the serial data stream, clock-to-data and data-to-data skew that would be present with a parallel bus are eliminated.

The MAX9235 serializer requires no external components and no control signals and can lock to a 16MHz to 45MHz system clock. The serializer output is held in high impedance until the device is fully locked to the local system clock.

The MAX9235 operates from a single +3.3V supply, is specified for operation from -40°C to +105°C, and is available in a 16-pin TQFN (3mm x 3mm) package.

#### **Applications**

Lane Departures Security Cameras Rear View Cameras **Production Line Monitoring**

#### **Features**

- ♦ Stand-Alone Serializer (vs. SERDES) Ideal for **Unidirectional Links**

- **♦** Framing Bits for Deserializer Resync Allow Hot **Insertion Without System Interruption**

- ♦ LVDS Serial Output Rated for Point-to-Point **Applications**

- ♦ Wide Reference Clock Input Range 16MHz to 45MHz

- ♦ Low 31mA Supply Current

- **♦ 10-Bit Parallel LVCMOS/LVTTL Interface**

- ♦ Up to 450Mbps Payload Data Rate

- ♦ Small 16-Pin TQFN (3mm x 3mm) Package

#### **Ordering Information**

| PART        | PIN-        | REF CLOCK   | PKG     |

|-------------|-------------|-------------|---------|

|             | PACKAGE     | RANGE (MHz) | CODE    |

| MAX9235ETE+ | 16 TQFN-EP* | 16 to 45    | TI633-5 |

<sup>+</sup>Denotes a lead-free package.

**Note:** The device is specified over the -40°C to +105°C temperature range.

Pin Configuration and Functional Diagram appear at end of data sheet.

### Typical Application Circuit

<sup>\*</sup>EP = Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| Output Short-Circuit DurationContinuous Lead Temperature (soldering, 10s)+30 | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) | Storage Temperature Range65°C to +150°C  Junction Temperature+150°C  Operating Temperature Range40°C to +105°C  Lead Temperature (soldering, 10s)+300°C  ESD Protection (Human Body Model, OUT+, OUT-)+2kV  ESD Protection (Human Body Model, IN, TOLK)+2kV |

|------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, R_L = 50\Omega \pm 1\%, C_L = 10 \text{pF}, T_A = -40 ^{\circ}\text{C} \text{ to } +105 ^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.) (Notes 1, 2, 3)

| PARAMETER                                                        | SYMBOL           | CON                                                   | MIN               | TYP   | MAX   | UNITS |      |  |  |  |

|------------------------------------------------------------------|------------------|-------------------------------------------------------|-------------------|-------|-------|-------|------|--|--|--|

| LVCMOS/LVTLL LOGIC INPUTS (IN0 TO IN9, EN, TCLK)                 |                  |                                                       |                   |       |       |       |      |  |  |  |

| High-Level Input Voltage                                         | VIH              |                                                       |                   | 2.0   |       | Vcc   | V    |  |  |  |

| Low-Level Input Voltage                                          | VIL              |                                                       |                   | GND   |       | 0.8   | V    |  |  |  |

| Input Current                                                    | I <sub>IN</sub>  | $V_{IN}$ = 0 or $V_{CC}$                              |                   | -20   |       | +20   | μΑ   |  |  |  |

| LVDS OUTPUTS (OUT+, OUT-)                                        |                  |                                                       |                   |       |       |       |      |  |  |  |

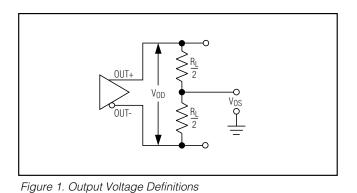

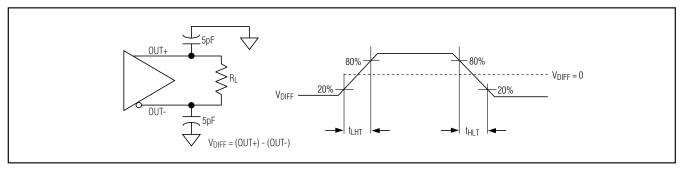

| Differential Output Voltage                                      | Von              | Figure 1                                              | $R_L = 100\Omega$ | 600   | 735   | 950   | mV   |  |  |  |

| Differential Output Voltage                                      | V <sub>OD</sub>  | Figure 1                                              | $R_L = 50\Omega$  | 250   | 370   | 470   | IIIV |  |  |  |

| Change in V <sub>OD</sub> Between<br>Complementary Output States | ΔV <sub>OD</sub> | Figure 1                                              |                   | 1     | 35    | mV    |      |  |  |  |

| 0.1.10".17"                                                      | Vos              | Figure 1                                              | $R_L = 100\Omega$ | 1.025 | 1.265 | 1.375 |      |  |  |  |

| Output Offset Voltage                                            |                  |                                                       | $R_L = 50\Omega$  | 1.125 | 1.265 | 1.375 | V    |  |  |  |

| Change in V <sub>OS</sub> Between<br>Complementary Output States | ΔV <sub>OS</sub> | Figure 1                                              |                   | 3     | 35    | mV    |      |  |  |  |

| Output Short-Circuit Current                                     | los              | OUT+ or OUT- = GN<br>IN0 to IN9 = EN = V <sub>C</sub> |                   | -13   | -15   | mA    |      |  |  |  |

| Power-Off Output Current                                         | I <sub>OX</sub>  | $V_{CC} = 0$ , $V_{OUT+}$ or $V$                      | -10               |       | +10   | μΑ    |      |  |  |  |

| POWER SUPPLY                                                     |                  |                                                       |                   |       |       |       |      |  |  |  |

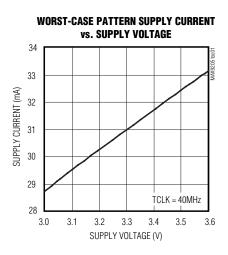

| Supply Current                                                   | Icc              | $R_L = 100\Omega$ or $50\Omega$ worst-case pattern    | 16MHz             |       | 22    | 35    | - mA |  |  |  |

|                                                                  |                  | (Figures 2, 4)                                        | 45MHz             |       | 31    | 45    | IIIA |  |  |  |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, R_L = 50\Omega \pm 1\%, C_L = 5 \text{pF}, T_A = -40 ^{\circ}\text{C} \text{ to } +105 ^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.) (Notes 2, 4)

| PARAMETER                                 | SYMBOL           |          | CONDITIONS        | MIN                        | TYP                  | MAX                          | UNITS       |  |  |  |

|-------------------------------------------|------------------|----------|-------------------|----------------------------|----------------------|------------------------------|-------------|--|--|--|

| TRANSMIT CLOCK (TCLK) TIMING REQUIREMENTS |                  |          |                   |                            |                      |                              |             |  |  |  |

| TCLK Center Frequency                     | fTCCF            |          |                   | 16                         |                      | 45                           | MHz         |  |  |  |

| TCLK Frequency Variation                  | TCFV             |          |                   | -200                       |                      | +200                         | ppm         |  |  |  |

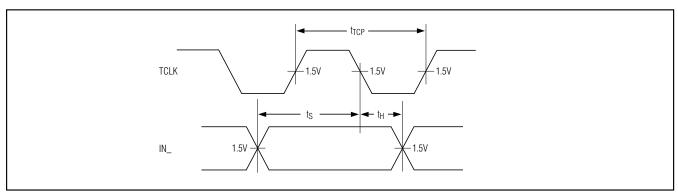

| TCLK Period                               | tTCP             |          |                   | 22.2                       |                      | 62.5                         | ns          |  |  |  |

| TCLK Duty Cycle                           | TCDC             |          |                   | 40                         |                      | 60                           | %           |  |  |  |

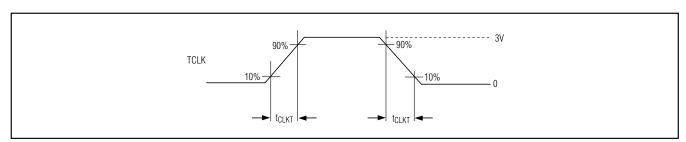

| TCLK Input Transition Time                | tCLKT            | Figure 3 |                   |                            | 3                    | 6                            | ns          |  |  |  |

| TCLK Input Jitter                         | tJI⊤             |          |                   |                            |                      | 150                          | ps<br>(RMS) |  |  |  |

| SWITCHING CHARACTERISTIC                  | cs               |          |                   | •                          |                      |                              |             |  |  |  |

| Low-to-High Transition Time               | t                | Figure 4 | $R_L = 100\Omega$ |                            | 370                  | 500                          | ps          |  |  |  |

| Low-to-riight transition time             | t <sub>LHT</sub> |          | $R_L = 50\Omega$  |                            | 350                  | 500                          |             |  |  |  |

| High to Low Transition Time               | t                | Figure 4 | $R_L = 100\Omega$ |                            | 370                  | 500                          | ne          |  |  |  |

| High-to-Low Transition Time               | tHLT             |          | $R_L = 50\Omega$  |                            | 350                  | 500                          | ps          |  |  |  |

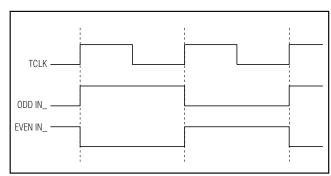

| IN_ Setup to TCLK                         | ts               | Figure 5 |                   | 1                          |                      |                              | ns          |  |  |  |

| IN_ Hold from TCLK                        | tH               | Figure 5 |                   | 3                          |                      |                              | ns          |  |  |  |

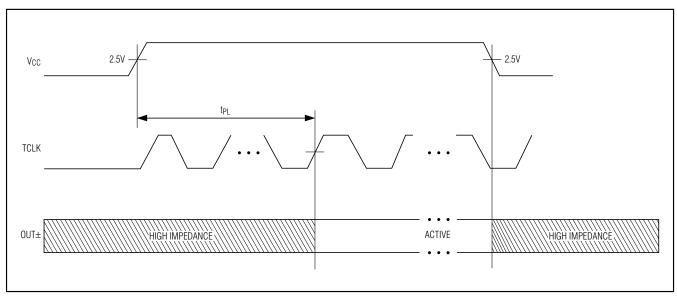

| PLL Lock Time                             | tpL              | Figure 6 |                   | 2048 x<br>t <sub>TCP</sub> |                      | 2049 x<br>t <sub>TCP</sub>   | ns          |  |  |  |

| Bus LVDS Bit Width                        | t <sub>BIT</sub> |          |                   |                            | t <sub>TCP</sub> /12 |                              | ns          |  |  |  |

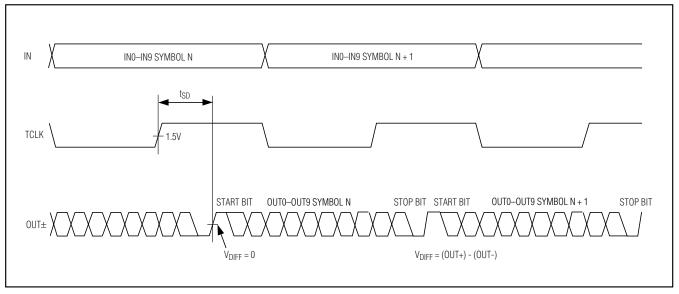

| Serializer Delay                          | tsD              | Figure 7 |                   | t <sub>TCP</sub> /6        |                      | (t <sub>TCP</sub> /6)<br>+ 5 | ns          |  |  |  |

Note 1: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground except V<sub>OD</sub>, ΔV<sub>OD</sub>, and V<sub>OS</sub>.

Note 2: C<sub>L</sub> includes scope probe and test jig capacitance.

**Note 3:** Parameters 100% tested at  $T_A = +25$ °C. Limits over operating temperature range guaranteed by design and characterization.

**Note 4:** AC parameters are guaranteed by design and characterization.

Figure 2. Worst-Case I<sub>CC</sub> Test Pattern

Figure 3. Input Clock Transition Time Requirement

Figure 4. Output Load and Transition Times

Figure 5. Data Input Setup and Hold Times

Figure 6. PLL Lock Time

Figure 7. Serializer Delay

### **Typical Operating Characteristics**

$(V_{CC} = +3.3V, R_L = 50\Omega, C_L = 5pF, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

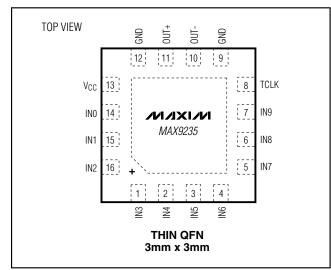

### **Pin Description**

| PIN             | NAME                      | FUNCTION                                                                                                                                                                              |

|-----------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–7, 14, 15, 16 | IN3-IN9, IN0,<br>IN1, IN2 | LVCMOS/LVTTL Data Inputs. Data is loaded into a 10-bit latch by the rising TCLK edge. Each input is internally pulled to ground.                                                      |

| 8               | TCLK                      | LVCMOS/LVTTL Reference Clock Input. Accepts a 16MHz to 45MHz clock. TCLK provides a frequency reference to the PLL and strobes parallel data into the input latch on the rising edge. |

| 9, 12           | GND                       | Ground                                                                                                                                                                                |

| 10              | OUT-                      | Inverting Bus LVDS Differential Output                                                                                                                                                |

| 11              | OUT+                      | Noninverting Bus LVDS Differential Output                                                                                                                                             |

| 13              | Vcc                       | Power-Supply Input. Bypass V <sub>CC</sub> to ground with a 0.1µF capacitor and a 0.001µF capacitor as close to V <sub>CC</sub> as possible.                                          |

| EP              | EP                        | Exposed Pad. Solder EP to ground for improved heat dissipation.                                                                                                                       |

### **Detailed Description**

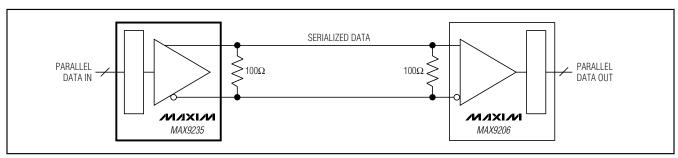

The MAX9235 10-bit serializer transmits data over balanced media that may be a standard twisted-pair cable or PCB traces at 100Mbps to 450Mbps. The interface may be single- or double-terminated point-to-point. A double-terminated point-to-point interface uses a 100 $\Omega$ -termination resistor at each end of the interface, resulting in a 50 $\Omega$  load. The serializer requires a deserializer such as the MAX9206 for a complete data transmission application.

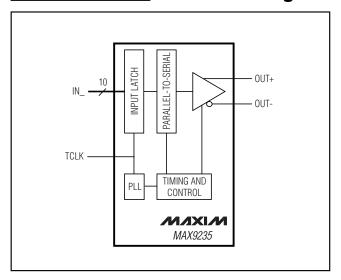

A high-state start bit and a low-state stop bit, added internally, frame the 10-bit parallel input data and ensure a transition in the serial data stream. Therefore, 12 serial bits are transmitted for each 10-bit parallel input. The MAX9235 accepts a 16MHz to 45MHz reference clock, producing a serial data rate of 192Mbps (12 bits x 16MHz) to 540Mbps (12 bits x 45MHz). Since only 10 bits are from input data, the actual throughput is 10 times the TCLK frequency.

To transmit data, the serializer sequences through two modes: initialization mode and data transmission mode.

#### **Initialization Mode**

When VCC is applied, the outputs are held in high impedance and internal circuitry is disabled by on-chip power-on-reset circuitry. When VCC reaches 2.35V, the PLL starts to lock to a local reference clock. The reference clock, TCLK, is provided by the system. The serializer locks within 2049 cycles of TCLK. Once locked, the serializer is ready to send data.

#### **Data Transmission Mode**

After initialization, input data at IN0-IN9 are clocked into the serializer by the TCLK input. Data strobes on the rising edge of TCLK.

A start bit high and a stop bit low frame the 10-bit data and function as the embedded clock edge in the serial data stream. The serial rate is the TCLK frequency times the data and appended bits. For example, if TCLK is 40MHz, the serial rate is  $40 \times 12 (10 + 2 \text{ bits}) = 480\text{Mbps}$ . Since only 10 bits are from input data, the payload rate is  $40 \times 10 = 400\text{Mbps}$ .

#### **High-Impedance State**

The serializer output pins (OUT+ and OUT-) are held in high impedance when  $V_{\rm CC}$  is first applied and while the PLL is locking to the local reference clock. If the serializer goes into high impedance, the deserializer loses PLL lock and needs to reestablish phase lock before data transfer can resume. This is done by transmitting all zeroes for at least one frame.

### Applications Information

#### **Power-Supply Bypassing**

Bypass  $V_{CC}$  with high-frequency surface-mount ceramic 0.1 $\mu$ F and 0.001 $\mu$ F capacitors in parallel as close to the device as possible, with the smaller valued capacitor closest to  $V_{CC}$ .

#### **Differential Traces and Termination**

Use controlled-impedance media and terminate at both ends of the transmission line in the media's characteristic impedance. Termination with a single resistor at the end of a point-to-point link typically provides acceptable performance. The MAX9235 output levels are specified for double-terminated point-to-point applications. With a single  $100\Omega$  termination, the output swing is larger.

Avoid the use of unbalanced cables such as ribbon or simple coaxial cable. Balanced cables such as twisted pair offer superior signal quality and tend to generate less EMI due to canceling effects. Balanced cables tend to pick up noise as common mode, which is rejected by a differential receiver.

Eliminate reflections and ensure that noise couples as common mode by running the differential traces close together. Reduce skew by matching the electrical length of the traces. Excessive skew can result in a degradation of magnetic field cancellation.

The differential output signals should be routed close to each other to cancel their external magnetic field. Maintain a constant distance between the differential traces to avoid discontinuities in differential impedance. Avoid 90° turns and minimize the number of vias to further prevent impedance discontinuities.

#### **Topologies**

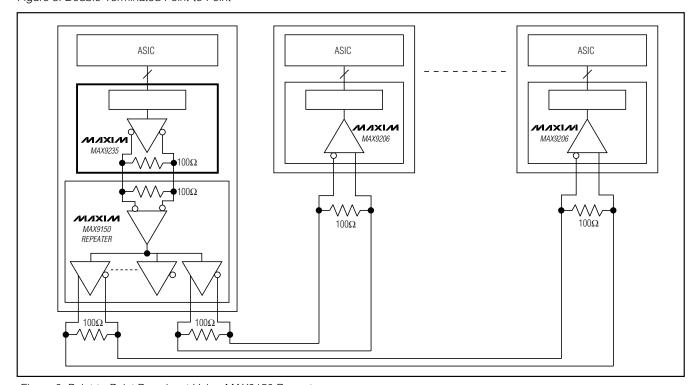

The MAX9235 can operate in point-to-point or broadcast topologies.

A point-to-point connection terminated at each end in the characteristic impedance of the cable or PCB traces is shown in Figure 8. The total load seen by the serializer is  $50\Omega.$  The double termination typically reduces reflections compared to a single  $100\Omega$  termination. A single  $100\Omega$  termination at the deserializer input is feasible and will make the differential signal swing larger.

A point-to-point broadcast configuration is shown in Figure 9. The low-jitter MAX9150 10-port repeater is

used to reproduce and transmit the serializer output over 10 double-terminated point-to-point links.

The repeater eliminates nine serializers compared to 10 individual point-to-point serializer-to-deserializer connections. Since repeater jitter subtracts from the serializer-deserializer timing margin, a low-jitter repeater is essential in most high data rate applications.

#### **Board Layout**

For LVDS applications, a four-layer PCB that provides separate power, ground, and input/output signals is recommended. Separate LVTTL/LVCMOS and LVDS signals from each other to prevent coupling into the LVDS lines.

Figure 8. Double-Terminated Point-to-Point

Figure 9. Point-to-Point Broadcast Using MAX9150 Repeater

### **Functional Diagram**

# Pin Configuration

\_Chip Information

PROCESS: CMOS

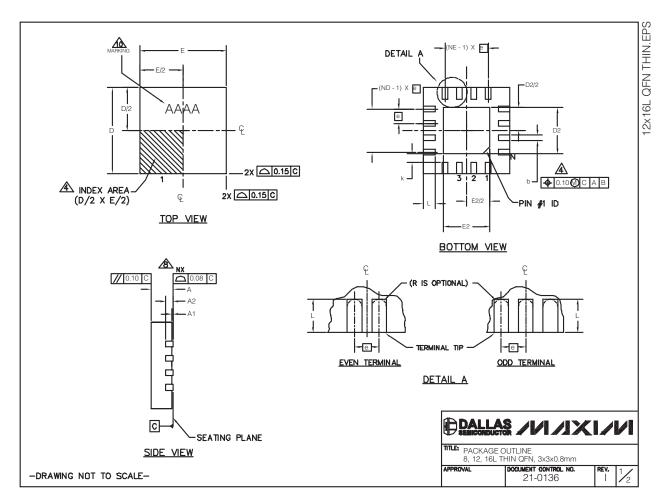

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

| PKG  | 8L 3x3    |          |      | 1    | 12L 3x3           |      | 16L 3x3   |      |      |  |

|------|-----------|----------|------|------|-------------------|------|-----------|------|------|--|

| REF. | MIN.      | NOM.     | MAX. | MIN. | NOM.              | MAX. | MIN.      | NOM. | MAX. |  |

| Α    | 0.70      | 0.75     | 0.80 | 0.70 | 0.75              | 0.80 | 0.70      | 0.75 | 0.80 |  |

| b    | 0.25      | 0.30     | 0.35 | 0.20 | 0.25              | 0.30 | 0.20      | 0.25 | 0.30 |  |

| D    | 2.90      | 3.00     | 3.10 | 2.90 | 3.00              | 3.10 | 2.90      | 3.00 | 3.10 |  |

| Е    | 2.90      | 3.00     | 3.10 | 2.90 | 3.00              | 3.10 | 2.90      | 3.00 | 3.10 |  |

| е    | 0.65 BSC. |          |      | 0    | .50 BS0           | ).   | 0.50 BSC. |      |      |  |

| L    | 0.35      | 0.55     | 0.75 | 0.45 | 0.55              | 0.65 | 0.30      | 0.40 | 0.50 |  |

| N    |           | 8        |      |      | 12                |      |           | 16   |      |  |

| ND   | 2         |          |      | 3    |                   |      | 4         |      |      |  |

| NE   |           | 2        |      |      | 3                 |      |           | 4    |      |  |

| A1   | 0         | 0.02     | 0.05 | 0    | 0.02              | 0.05 | 0         | 0.02 | 0.05 |  |

| A2   | C         | 0.20 REF |      |      | 0.20 REF 0.20 REF |      |           |      |      |  |

| k    | 0.25      | -        | -    | 0.25 | -                 | -    | 0.25      | -    | -    |  |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |             |        |  |

|------------------------|------|------|------|------|------|------|-------------|--------|--|

| PKG.                   | D2   |      |      | E2   |      |      | PIN ID      | JEDEC  |  |

| CODES                  | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. | PINID       | JEDEC  |  |

| TQ833-1                | 0.25 | 0.70 | 1.25 | 0.25 | 0.70 | 1.25 | 0.35 x 45°  | WEEC   |  |

| T1233-1                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |

| T1233-3                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |

| T1233-4                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |

| T1633-2                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |

| T1633F-3               | 0.65 | 0.80 | 0.95 | 0.65 | 0.80 | 0.95 | 0.225 x 45° | WEED-2 |  |

| T1633FH-3              | 0.65 | 0.80 | 0.95 | 0.65 | 0.80 | 0.95 | 0.225 x 45° | WEED-2 |  |

| T1633-4                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |

| T1633-5                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- 4 THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- ⚠ DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.20 mm AND 0.25 mm FROM TERMINAL TIP.

- ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- ⚠ COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS

- 9. DRAWING CONFORMS TO JEDEC MO220 REVISION C.

MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- 11. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- 12. WARPAGE NOT TO EXCEED 0.10mm.

-DRAWING NOT TO SCALE-

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | REVISION DESCRIPTION                                                                                                                                                        | PAGES<br>CHANGED |

|--------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 7/07          | Initial release                                                                                                                                                             | _                |

| 1                  | 12/07         | Max clock frequency increased to 45MHz; min value decreased for TCLK period; changed conditions for Output Short-Circuit and Power-Off Output Current; various style edits. | 1, 2, 3, 6, 7    |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.