Datasheet

### Octal channel high-side driver

#### **Features**

- Operating output current: 0.7 A (IPS8160HQ) or 1.0 A (IPS8160HQ-1) per channel

- CMOS compatible input

- · Very low standby current

- · Undervoltage shutdown

- Overload and short-circuit protection with output current limitation

- Junction overtemperature protection

- · Case overtemperature protection for thermal independence of the channels

- · Protection against loss of ground

- · Thermal shutdown diagnostic pin

- Designed to meet IEC 61000-4-2, IEC 61000-4-4, IEC 61000-4-5

- Package: QFN48L 8x6x0.9 mm

#### **Applications**

- Programmable logic control

- · Vending machines

- Industrial PC peripheral input/output

- · Numerical control machines

- General high-side switch applications

# Product status link IPS8160HQ

IPS8160HQ-1

#### Product label

#### **Description**

The IPS8160HQ and IPS8160HQ-1 are monolithic devices designed with STMicroelectronics VIPower M0-3 technology, intended to drive any kind of load with one side connected to ground. They can be driven by using a 3.3 V logic supply.

They are suitable for applications with up to 0.7 A (IPS8160HQ) or 1 A (IPS8160HQ-1) steady-state operating current.

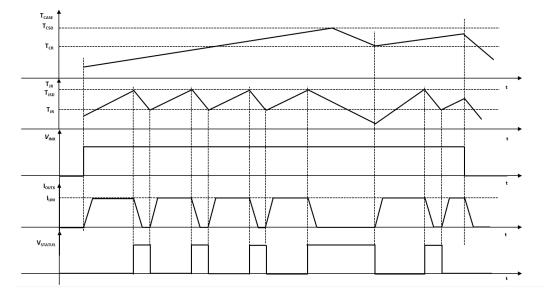

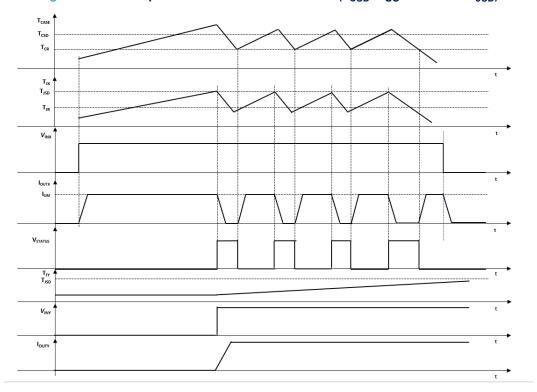

Active current limitation combined with thermal shutdown and automatic restart protect the devices against overload. In overload conditions, the channel turns OFF and ON again automatically to maintain the junction temperature between  $T_{JSD}$  and  $T_R.$  If this condition causes the case temperature to trigger  $T_{CSD},$  then overloaded channels are turned OFF and can be turned back ON only when the case temperature decreases down to  $T_{CR}.$  Non-overloaded channels continue to operate normally.

The devices automatically turn OFF in case of ground pin disconnection.

Devices are especially suitable for industrial applications conforming to IEC 61131.

# 1 Block diagram

UVLO vcc IN1 OUT1 IN2 OUT2 GATE CONTROL LOGIC STAGE DRIVERS IN8 OUT8 LOAD CURRENT LIMITATION (x8) STATUS GND THERMAL JUNCTION THERMAL CASE

Figure 1. IPS8160HQ, IPS8160HQ-1 block diagram

DS13934 - Rev 2 page 2/30

# **Pin connections**

OUT8

OUT7

OUT7

OUT7

OUT6

OUT6

OUT6

OUT5

OUT7

OUT7

OUT7

OUT7

OUT7

OUT7 STATUS III GND NC 32 NC

Figure 2. Connection diagram (top through view)

OUT1 ■ OUT1 NC 31 NC Vcc (TAB) NC 5 29 NC NC Z 28 NC NC NC 9 26 NC NC 10

**Table 1. Pin functions**

| Pin      | Symbol | Description                                               |

|----------|--------|-----------------------------------------------------------|

| 1, 2     | OUT1   | Channel 1 power output                                    |

| 1, 2     | 0011   | Short both pins on the same net of the application board  |

| 3 to 13, | NC     | Internally not connected.                                 |

| 22 to 32 | NC     | If necessary, these pins can be routed in the application |

| 14       | IN1    | Channel 1 input                                           |

| 15       | IN2    | Channel 2 input                                           |

| 16       | IN3    | Channel 3 input                                           |

| 17       | IN4    | Channel 4 input                                           |

| 18       | IN5    | Channel 5 input                                           |

| 19       | IN6    | Channel 6 input                                           |

| 20       | IN7    | Channel 7 input                                           |

| 21       | IN8    | Channel 8 input                                           |

| 33       | GND    | Output power ground                                       |

| 34       | STATUS | Common open source diagnostic for overtemperature         |

| 35, 36   | OUT8   | Channel 8 power output                                    |

| 35, 36   | 0018   | Short both pins on the same net of the application board  |

| 37, 38   | OUT7   | Channel 7 power output                                    |

| 31, 30   | 0017   | Short both pins on the same net of the application board  |

| 39, 40   | OUT6   | Channel 6 power output                                    |

| 38, 40   | 0010   | Short both pins on the same net of the application board  |

DS13934 - Rev 2 page 3/30

| Pin    | Symbol          | Description                                              |

|--------|-----------------|----------------------------------------------------------|

| 41, 42 | OUT5            | Channel 5 power output                                   |

| ,      | 33.3            | Short both pins on the same net of the application board |

| 42 44  | OUT4            | Channel 4 power output                                   |

| 43, 44 | 0014            | Short both pins on the same net of the application board |

| 45, 46 | OUT3            | Channel 3 power output                                   |

| 45, 40 | 0013            | Short both pins on the same net of the application board |

| 47, 48 | OUT2            | Channel 2 power output                                   |

| 47,40  | 0012            | Short both pins on the same net of the application board |

| EP     | V <sub>CC</sub> | Supply voltage                                           |

DS13934 - Rev 2 page 4/30

# 3 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol            | Parameter                                                                                                                           | Value              | Unit |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|

| V <sub>CC</sub>   | DC supply voltage                                                                                                                   | 45                 | V    |

| -امىيە            | DC ground reverse current                                                                                                           | 250                | mA   |

| -I <sub>GND</sub> | Transient ground reverse current (pulse duration < 1 ms)                                                                            | 6                  | Α    |

| I <sub>OUT</sub>  | DC output current                                                                                                                   | Internally limited | Α    |

| -l <sub>OUT</sub> | Reverse DC output current                                                                                                           | 6 <sup>(1)</sup>   | Α    |

| I <sub>IN</sub>   | DC input current range                                                                                                              | -1, +10            | mA   |

| V <sub>IN</sub>   | Input voltage range                                                                                                                 | -0.3, +5.5         | V    |

| V <sub>ESD</sub>  | Electrostatic discharge (R = 1.5 KΩ; C = 100 pF)                                                                                    | 2000               | V    |

| P <sub>TOT</sub>  | Power dissipation at Tc = 25 °C                                                                                                     | 5.8                | W    |

| EAS               | Single pulse Avalanche Energy per channel, all channels driven simultaneously (Tamb = 125 °C, I <sub>OUT</sub> = 0.6 A per channel) | 0.5                | J    |

| TJ                | Junction operating temperature                                                                                                      | Internally limited | °C   |

| T <sub>C</sub>    | Case operating temperature                                                                                                          | Internally limited | °C   |

| T <sub>STG</sub>  | Storage temperature range                                                                                                           | -40, +150          | °C   |

<sup>1.</sup> limit intended with each couple of OUTx (x = 1...8) pin shorted on the application board

DS13934 - Rev 2 page 5/30

# 4 Thermal data

Table 3. Thermal data

| Symbol                             | Parameter                                        | Max. Value | Unit |

|------------------------------------|--------------------------------------------------|------------|------|

| R <sub>th(JC)</sub> <sup>(1)</sup> | Thermal Resistance, Junction-to-case per channel | 1.5        | °C/W |

| R <sub>th(JA)</sub> <sup>(2)</sup> | Thermal Resistance, Junction-to-ambient          | 30         | C/VV |

<sup>1.</sup> Rth between the die and the bottom case surface measured by cold plate as per JESD51.

DS13934 - Rev 2 page 6/30

<sup>2.</sup> JESD51-7.

# 5 Electrical characteristics

10.5 V < V $_{CC}$  < 32 V; -40 °C < T $_{J}$  < 125 °C; unless otherwise specified.

Table 4. Power section

| Symbol                | Parameter                                       | Test Condition                                                                                                                                      | Min. | Тур. | Max.       | Unit     |

|-----------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------------|----------|

| $V_{USD}$             | V <sub>CC</sub> undervoltage turn-off threshold |                                                                                                                                                     | 7    |      | 10.5       | V        |

| R <sub>ON</sub>       | ON-state resistance                             | $I_{OUT} \le 1 \text{ A}; T_J = 25 \text{ °C}; V_{CC} \le 36 \text{ V}$<br>$I_{OUT} \le 1 \text{ A}; T_J = 125 \text{ °C}; V_{CC} \le 36 \text{ V}$ |      |      | 160<br>280 | mΩ<br>mΩ |

| Is                    | Supply current                                  | OFF-state V <sub>CC</sub> = 24 V; T <sub>CASE</sub> = 25 °C                                                                                         |      |      | 150        | μA       |

| '5                    | Зирру сипен                                     | ON-state (all channels ON) V <sub>CC</sub> = 24 V; T <sub>CASE</sub> = 100 °C                                                                       |      |      | 12         | mA       |

| I <sub>LGND</sub>     | Output current at turn-off                      | $V_{CC} = V_{GND} = 24 \text{ V};$<br>$V_{STAT} = V_{IN} = 5 \text{ V}; V_{OUT} = 0 \text{ V}; T_{J} = 25 \text{ °C}$                               |      |      | 0.5        | mA       |

| iLGND                 | Output current at turn-on                       | $V_{CC} = V_{GND} = 24 \text{ V};$<br>$V_{STAT} = V_{IN} = 5 \text{ V}; V_{OUT} = 0 \text{ V}; T_{J} = 125 \text{ °C}$                              |      |      | 0.55       | mA       |

| I <sub>L(OFF)</sub>   | OFF-state output current                        | V <sub>IN</sub> = V <sub>OUT</sub> = 0 V                                                                                                            | 0    |      | 5          | μA       |

| V <sub>OUT(OFF)</sub> | OFF-state output voltage                        | V <sub>IN</sub> = 0 V; I <sub>OUT</sub> = 0 A                                                                                                       |      |      | 3          | V        |

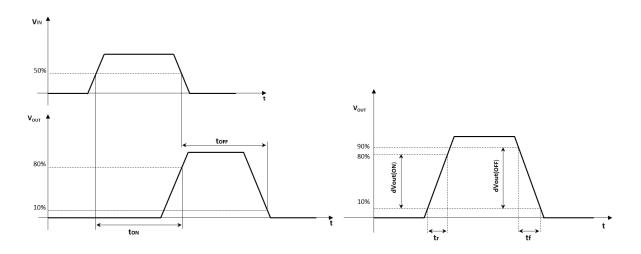

Table 5. Switching (V<sub>CC</sub> = 24 V)

| Symbol                                 | Parameter                                | Test Condition                                                                               | Min. | Тур. | Max. | Unit |

|----------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>ON</sub>                        | Turn-ON time                             | R <sub>L</sub> = 48 $\Omega$ ; from 50% V <sub>IN</sub> to 80% V <sub>OUT</sub> see Figure 3 | 20   | 30   | 60   | μs   |

| t <sub>OFF</sub>                       | Turn-OFF time                            | $R_L$ = 48 Ω; from 50% $V_{IN}$ to 10% $V_{OUT}$ see Figure 3                                | 20   | 40   | 80   | μs   |

| t <sub>OFF</sub> - t <sub>ON</sub>     | Turn-OFF, Turn-ON matching               |                                                                                              | -40  | 10   | 60   | μs   |

| dV <sub>OUT</sub> /dt <sub>(ON)</sub>  | Turn-ON voltage slope                    | $R_L$ = 48 Ω; from $V_{OUT}$ = 2.4 V to $V_{OUT}$ = 19.2 V see Figure 3                      |      | 0.7  |      | V/µs |

| dV <sub>OUT</sub> /dt <sub>(OFF)</sub> | Turn-OFF voltage slope                   | $R_L$ = 48 Ω; from $V_{OUT}$ = 21.6 V to $V_{OUT}$ = 2.4 V see Figure 3                      |      | 1.5  |      | V/µs |

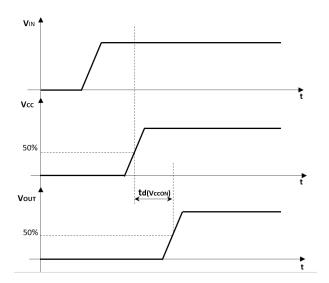

| t <sub>d(VCCON)</sub>                  | Power on delay time from VCC rising edge | see Figure 4                                                                                 |      | 1    |      | ms   |

DS13934 - Rev 2 page 7/30

Figure 3. Turn-ON and turn-OFF

Figure 4. V<sub>CC</sub> turn-ON

Table 6. Input pins

| Symbol                | Parameter                | Test Condition           | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------|--------------------------|------|------|------|------|

| V <sub>INL</sub>      | Input low level          |                          |      |      | 1.25 | V    |

| I <sub>INL</sub>      | Low level input current  | V <sub>IN</sub> = 1.25 V | 1    |      |      | μA   |

| V <sub>INH</sub>      | Input high level         |                          | 2.25 |      |      | V    |

| I <sub>INH</sub>      | High level input current | V <sub>IN</sub> = 2.25 V |      |      | 10   | μA   |

| V <sub>IN(HYST)</sub> | Input hysteresis voltage |                          | 0.25 |      |      | V    |

| V <sub>CL</sub>       | Innut olama voltago      | I <sub>IN</sub> = 1 mA   | 6.0  | 6.8  | 8.0  | V    |

| ▼ CL                  | Input clamp voltage      | I <sub>IN</sub> = -1 mA  |      | -0.7 |      | V    |

page 8/30

**Table 7. Protections**

| Symbol             | Parameter                                         | Test Condition                                          | Min.                | Тур.                | Max.                | Unit |

|--------------------|---------------------------------------------------|---------------------------------------------------------|---------------------|---------------------|---------------------|------|

| T <sub>CSD</sub>   | Case shutdown temperature                         |                                                         | 125                 | 130                 | 135                 | °C   |

| T <sub>CR</sub>    | Case reset temperature                            |                                                         | 110                 |                     |                     | °C   |

| T <sub>CHYST</sub> | Case thermal hysteresis                           |                                                         | 7                   | 15                  |                     | °C   |

| T <sub>JSD</sub>   | Junction shutdown temperature                     |                                                         | 150                 | 175                 | 200                 | °C   |

| T <sub>R</sub>     | Junction reset temperature                        |                                                         | 135                 |                     |                     | °C   |

| T <sub>HYST</sub>  | Junction thermal hysteresis                       |                                                         | 7                   | 15                  |                     | °C   |

| I <sub>PEAK</sub>  | Maximum DC output current before limitation       | $V_{CC}$ = 24 V; $R_{LOAD}$ = 10 m $\Omega$             | 1.1                 |                     | 2.6                 | Α    |

| 1                  | DC short-circuit current limitation per channel   | $V_{CC} = 24 \text{ V; } R_{LOAD} = 10 \text{ m}\Omega$ | 0.7 (1)             |                     | 1.7                 | Α    |

| I <sub>LIM</sub>   | Do short-circuit current illilitation per channel | VCC - 24 V, INDAD - 10 IIIZ2                            | 1 (2)               |                     | 1.7                 | A    |

| V <sub>DEMAG</sub> | Turn-OFF output clamp voltage                     | I <sub>OUT</sub> = 0.5 A; L= 6 mH                       | V <sub>CC</sub> -57 | V <sub>CC</sub> -52 | V <sub>CC</sub> -47 | V    |

- 1. IPS8160HQ

- 2. IPS8160HQ-1

Table 8. Status Pin

| Symbol              | Parameter                     | Test Condition                                                     | Min. | Тур. | Max. | Unit |

|---------------------|-------------------------------|--------------------------------------------------------------------|------|------|------|------|

| I <sub>HSTAT</sub>  | STATUS pin high level current | $V_{CC}$ = 18 to 32 V; $R_{STAT}$ = 1 k $\Omega$ (Fault condition) | 2    | 3    | 4    | mA   |

| I <sub>LSTAT</sub>  | STATUS pin leakage current    | Normal operation; V <sub>CC</sub> = 32 V                           |      |      | 0.1  | μA   |

| V <sub>CLSTAT</sub> | STATUS pin clamp voltage      | I <sub>STAT</sub> = 1 mA<br>I <sub>STAT</sub> = -1 mA              | 6.0  | 6.8  | 8.0  | V    |

DS13934 - Rev 2 page 9/30

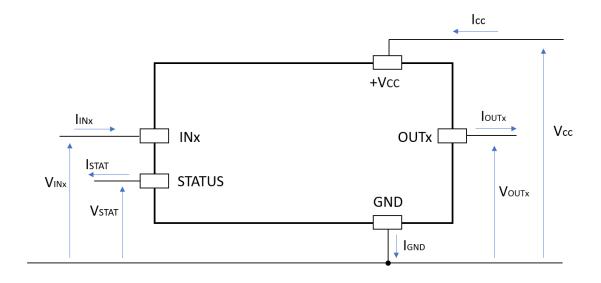

# 6 Current, voltage conventions and truth table

Figure 5. Current and voltage conventions

Table 9. Truth table

| Conditions                                     | INPUTx | OUTPUTx          | STATUS |

|------------------------------------------------|--------|------------------|--------|

| Normal operation                               | L      | L                | L      |

| Normal operation                               | Н      | Н                | L,     |

| Current limitation                             | L      | L                | L      |

| Current innitiation                            | Н      | X <sup>(1)</sup> | L.     |

| Overtemperature (see Figure 10 and Figure 11.) | L      | L                | L      |

| Overtemperature (see Figure 10 and Figure 11 ) | Н      | L                | н      |

| Lindanialtaga                                  | L      | L                | X      |

| Undervoltage                                   | Н      | L                | X      |

1. Pin voltage =  $I_{OUT} * R_{LOAD}$

DS13934 - Rev 2 page 10/30

### 7 Power Section

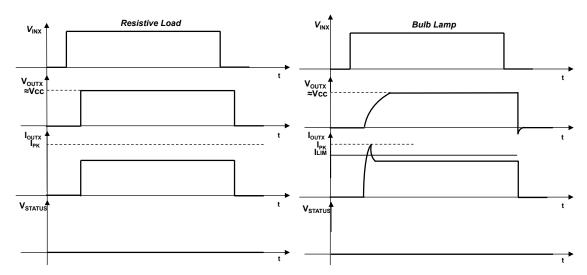

#### 7.1 Current limitation

Current limitation process is activated when the current sense connected on the output stage measures a current value higher than a fixed threshold.

When this condition is verified, the gate voltage is modulated to prevent the output current from rising above the limitation value.

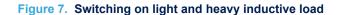

The following figures show typical output current waveforms with different load conditions.

Figure 6. Switching on resistive and on bulb lamp load

DS13934 - Rev 2 page 11/30

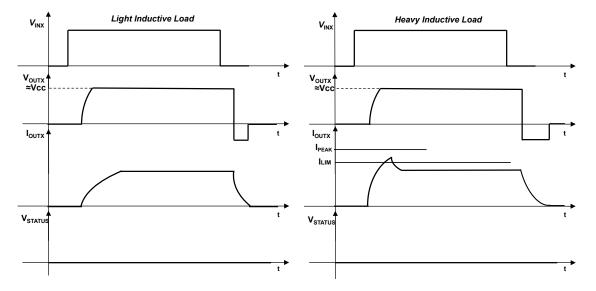

Figure 8. Short circuit during ON-state and Turn-on in short circuit

### 7.2 Thermal protection

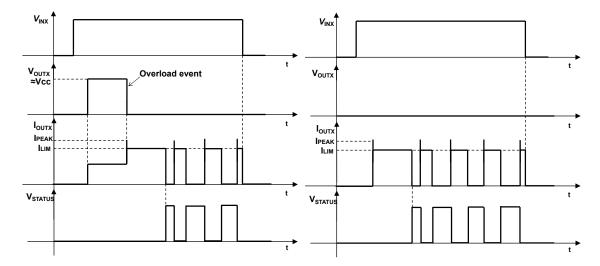

The device is protected against overheating due to overload conditions. During the driving period, if the output is overloaded, the device suffers two different thermal stresses, the first is related to the junction, and the second related to the case.

The two faults have different trigger thresholds: the junction protection threshold  $(T_{JSD})$  is higher than the case protection one  $(T_{CSD})$ ; generally the first protection that is activated in thermal stress conditions is the junction thermal shutdown. The output is turned off when the temperature is higher than the related threshold and turned back on when it goes below the reset threshold  $(T_{JR})$ . This behavior continues until the fault on the output is present.

If the thermal protection is active and the temperature of the package increases over the fixed case protection threshold, the case protection is activated and the output is switched off and back on when the junction temperature, of each channel in fault and case temperature, are below the respective reset thresholds.

DS13934 - Rev 2 page 12/30

Figure 9. Thermal protection flowchart

#### 7.3 Status indication

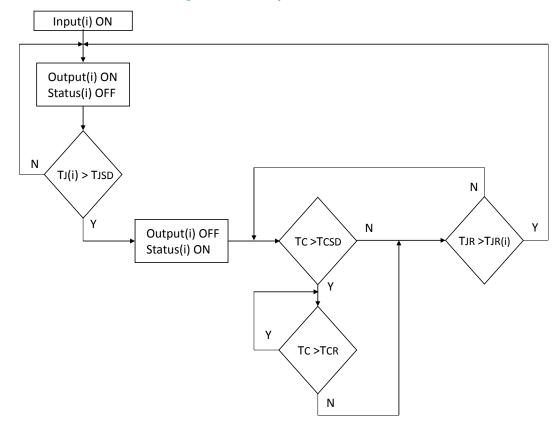

The Status pin is an active high common open source output indicating fault conditions. This pin is activated in case of junction overtemperature ( $T_{JX} > T_{JSD}$ ) of one or more output channels. Figure 10 and Figure 11 show the STATUS behavior when  $T_{JSD}$  is triggered before  $T_{CSD}$  and when  $T_{CSD}$  is triggered before  $T_{JSD}$  respectively.

Figure 10. Thermal protection and STATUS behavior (T<sub>JSD</sub> triggered before T<sub>CSD</sub>)

DS13934 - Rev 2 page 13/30

Figure 11. Thermal protection and STATUS behavior (T<sub>CSD</sub> triggered before T<sub>JSD</sub>)

DS13934 - Rev 2 page 14/30

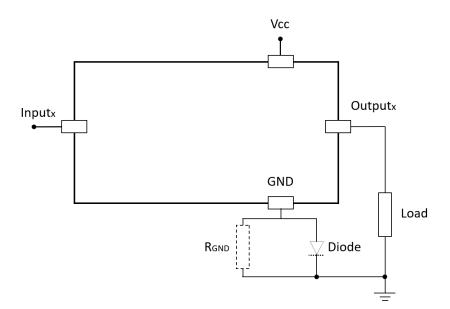

# 8 Reverse polarity protection

Reverse polarity protection can be implemented on board using two different solutions:

- 1. Placing a resistor (R<sub>GND</sub>) between IC GND pin and load GND

- 2. Placing a diode between IC GND pin and load GND

If option 1 is selected, the minimum resistance value has to be selected according to the following equation:

where I<sub>GND</sub> is the DC reverse ground pin current and can be found in Section 3 of this datasheet.

Power dissipated by  $R_{GND}$  (when  $V_{CC} < 0$ , reverse polarity situations) is:

$$P_D = (V_{CC})^2 / R_{GND}$$

If option 2 is selected, the diode has to be chosen by taking into account VRRM >  $|V_{cc}|$  and its power dissipation capability:

$$P_D \ge I_S \times V_f$$

Note:

In normal operation (no reverse polarity), there is a voltage drop ( $\Delta V$ ) between GND of the device and GND of the system. Using option 1,  $\Delta V = R_{GND} \times I_{CC}$ ; using option 2,  $\Delta V = VF \otimes (IF)$ .

Figure 12. V<sub>CC</sub> Reverse Polarity Protection

This schematic can be used with any type of load.

DS13934 - Rev 2 page 15/30

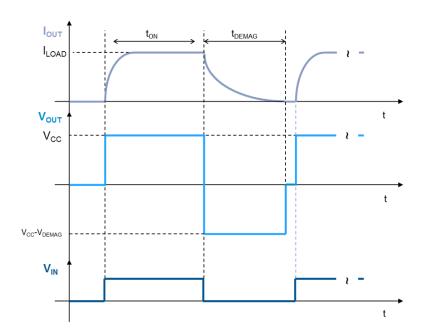

# 9 Active clamp

Active clamp is also known as Fast Demagnetization of inductive loads or Fast Current Decay. When a high-side driver turns off an inductance, an undervoltage on the output is detected.

The OUT pin is pulled down to  $V_{CC}$ - $V_{DEMAG}$ . The conduction state is modulated by an internal circuitry in order to keep the OUT pin voltage at  $\sim V_{DEMAG}$  until the load energy has been dissipated. The energy is dissipated in both IC internal switch and load resistance.

Figure 13. Active clamp typical waveforms

DS13934 - Rev 2 page 16/30

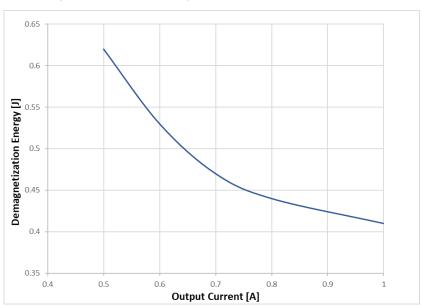

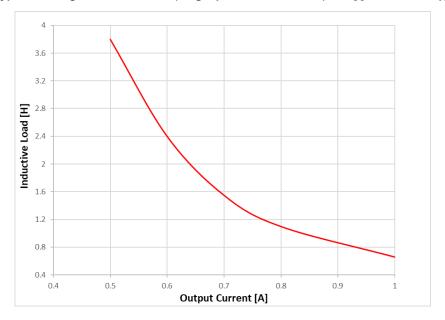

Figure 15. Typical demagnetization: L vs I (single pulse, all channels) at  $V_{CC}$  = 24 V and  $T_{AMB}$  = 125 °C

DS13934 - Rev 2 page 17/30

# 10 Thermal information

### 10.1 Thermal impedance

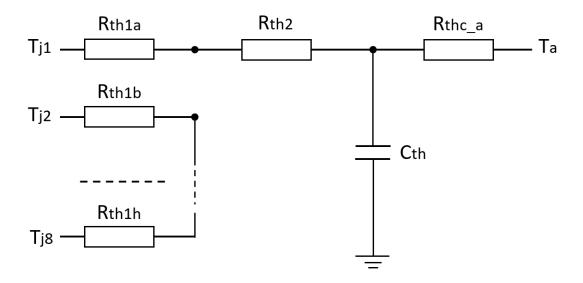

Figure 16. Simplified thermal model of the process stage

Contact ST for details on the thermal model.

DS13934 - Rev 2 page 18/30

bbb(M) C A B

# 11 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com

ECOPACK is an ST trademark.

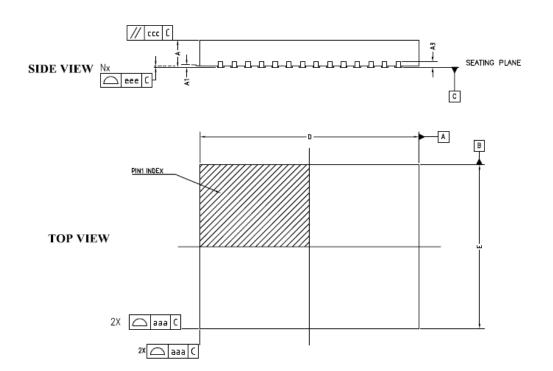

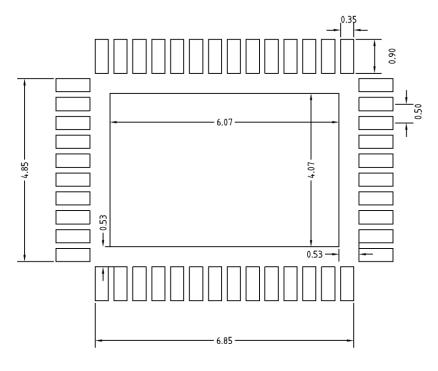

### 11.1 QFN48L 8x6 mm package mechanical data

BOTTOM VIEW

PINI NOEX

<u>0000000000000</u>

Figure 17. QFN48L 8x6 mm package information

DS13934 - Rev 2 page 19/30

8

| Symbol |       | [mm]     |       | Note            |

|--------|-------|----------|-------|-----------------|

| Зушьог | Min.  | Nom.     | Max.  | Note            |

| Α      | 0.80  | 0.85     | 0.90  | 12              |

| A1     | 0.00  | -        | 0.05  | 9, 12           |

| A3     |       | 0.2 REF  |       |                 |

| b      | 0.20  | 0.25     | 0.30  | 5, 6, 7, 12, 13 |

| D      |       | 8 BSC    |       | 4, 12           |

| е      |       | 0.50 BSC |       |                 |

| E      |       | 6.00 BSC |       | 4, 12           |

| D2     | 5.97  | 6.02     | 6.07  |                 |

| E2     | 3.97  | 4.02     | 4.07  |                 |

| L      | 0.365 | 0.40     | 0.435 | 12, 13          |

| k      | 0.53  |          |       |                 |

Table 10. QFN48L 8x6 mm package mechanical data

Table 11. Tolerance of forms and positions

48

| Symbol | Tolerance of form and position |  |

|--------|--------------------------------|--|

| aaa    | 0.10                           |  |

| bbb    | 0.10                           |  |

| ccc    | 0.10                           |  |

| ddd    | 0.05                           |  |

| eee    | 0.08                           |  |

| fff    | 0.10                           |  |

| Note   | 1,12                           |  |

| REF    |                                |  |

**NOTES** (to be reported on column "Note" of package mechanical data table)

- 1. Dimensioning and tolerancing schemes conform to ASME Y14.5M-1994.

- 2. All the dimensions are in mm.

Ν

- 3. Terminal A1 identifier and terminal numbering convention shall conform to JEP95 SPP-002. Terminal A1 identifier must be located within the zone indicated on the outline drawing. Topside terminal A1 indicator may be molded, or metallized feature. Optional indicator on bottom surface may be a molded, marked, or metallized feature.

- 4. Outlines with "D" and "E" increments less than 0.5 mm should be registered as "standalone" outlines. These outlines should use as many of the algorithms and dimensions states in the design standard as possible to ensure predictability in manufacturing.

- 5. Dimension "b" applies to the metalized terminal and is measured between 0.15 mm and 0.30 mm from the terminal tip. If the terminal has the optional radius on the other end of the terminal, the dimension "b" should not be measured in that radius area.

- 6. Inner edge of corner terminals may be chamfered or rounded in order to achieve minimum gap "k". This feature should not affect the terminal with "b", which is measured L/2 from the edge of the package body.

- 7. Exact shape of the leads at the edge of the package is optional.

DS13934 - Rev 2 page 20/30

- 8. "N" is the maximum number of terminal positions for the specified body size. Depopulation is allowed, but only under the following conditions:

- Depopulation scheme must be consistent in each quadrant of the package

- Non-symmetric variations should be broken out as separate mechanical outline variations, including depopulation graphics.

- 9. A1 is defined as the distance from the seating plane to the lowest point on the package body (standoff).

- 10. Dimension D2 and E2 refer to exposed pad. For exposed pad dimensions see Variation Table.

- 11. For tolerance of form and position see Table below.

- 12. Critical dimensions:

- A

- A1

- D&E

- b&L

- е

- D2 & E2

- 13. Dimensions "b" and "L" are measured at terminal plating surface.

- 14. Depending on the method of lead termination at the edge of the package, pull back (L1) maybe present. L minus L1 to be equal to or greater than 0.3 mm.

- 15. For Symbols, Recommended Values and Tolerances see Table below: (ACCORDING TO PACKAGE OR JEDEC SPEC IF REGISTERED).

**Table 12. Definitions**

| Symbol | Definition                                                                                                                                                                                                                   | Notes                                                                           |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| aaa    | The bilateral profile tolerance that controls the position of the plastic body sides. The centers of the profile zones are defined by the basic dimensions D and E.                                                          |                                                                                 |

| bbb    | The tolerance that controls the position of the entire terminal pattern with respect to Datum's A and B. The center of the tolerance zone for each terminal is defined by basic dimension "e" as related to Datum's A and B. |                                                                                 |

| ccc    | The tolerance located parallel to the seating plane in which the top surface of the package must be located.                                                                                                                 |                                                                                 |

| ddd    | The tolerance that controls the position of the terminals to each other. The centers of the profile zones are defined by basic dimension "e"                                                                                 | This tolerance is normally compounded with tolerance zone defined by bbb.       |

| eee    | The unilateral tolerance located above the seating plane where in the bottom surface of all terminals must be located.                                                                                                       | This tolerance is commonly known as the "coplanarity" of the package terminals. |

| fff    | The tolerance that controls the position of the exposed metal heat feature. The center of the tolerance zone is the datum's defined by the centerlines of the package body.                                                  |                                                                                 |

DS13934 - Rev 2 page 21/30

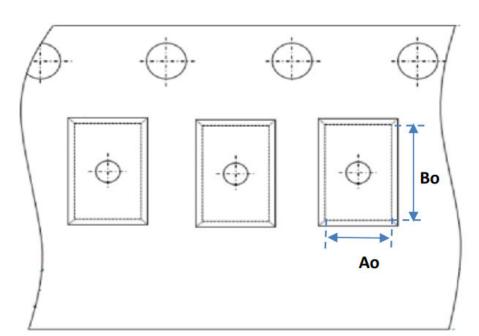

Figure 18. QFN48 8x6 mm suggested footprint [mm]

STMicroelectronics is not responsible for PCB-related issues. The footprint shown in the above figure is a suggestion which may differ from the customer PCB supplier design rules.

DS13934 - Rev 2 page 22/30

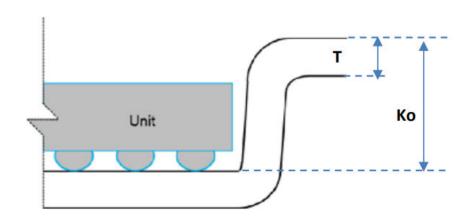

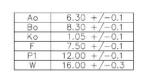

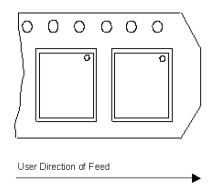

#### **Packing information 12**

Figure 19. QFN48L 8x6 mm reel shipment reference

Table 13. Standard SPC parameters

| Item | Description    |

|------|----------------|

| Ao   | Pocket Length  |

| Во   | Pocket Width   |

| Ko   | Pocket Depth   |

| Т    | Tape Thickness |

page 23/30

Po 4.0±0.1 (II) P2 - 2.0±0.1 (I) Do Ø1.55±0.05 E1 - 1.75±0.1  $\oplus$  $\oplus$  $\oplus$ 0  $\oplus$  $\oplus$  $\oplus$ F(III) D1 ø1.6±0.1

Figure 20. QFN48L 8x6 mm tape dimensions

SECTION Y-Y

0.30±0.05

P1

- (I) Measured from centreline of sprocket hole to centreline of pocket.

(II) Cumulative tolerance of 10 sprocket holes is ± 0.20.

(III) Measured from centreline of sprocket hole to centreline of pocket.

(IV) Other material available.

DETAIL 'A'

ALL DIMENSIONS IN MILLIMETRES UNLESS OTHERWISE STATED.

Figure 21. QFN48L 8x6 mm tape, Pin 1 indication

DS13934 - Rev 2 page 24/30

# 13 Ordering information

**Table 14. Ordering information**

| Part number | Package       | Packaging     |  |

|-------------|---------------|---------------|--|

| IPS8160HQ   | QFN48L 8x6 mm | Tong and real |  |

| IPS8160HQ-1 |               | Tape and reel |  |

DS13934 - Rev 2 page 25/30

# **Revision history**

**Table 15. Document revision history**

| Date        | Version | Changes                                                                                                                                                              |

|-------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23-Dec-2022 | 1       | Initial release.                                                                                                                                                     |

| 08-May-2023 | 2       | Modified Table 2; changed -I <sub>OUT</sub> and P <sub>TOT</sub> values in Table 3; changed figures Figure 6, Figure 7, Figure 8; add Figure 15; some minor changes. |

DS13934 - Rev 2 page 26/30

# **Contents**

| 1     | Bloc          | ck diagram                                | 2  |  |

|-------|---------------|-------------------------------------------|----|--|

| 2     | Pin           | connections                               | 3  |  |

| 3     | Max           | Maximum ratings5                          |    |  |

| 4     | Thermal data6 |                                           |    |  |

| 5     | Elec          | ctrical characteristics                   | 7  |  |

| 6     | Cur           | rent, voltage conventions and truth table | 10 |  |

| 7     | Pow           | ver Section                               | 11 |  |

|       | 7.1           | Current limitation                        | 11 |  |

|       | 7.2           | Thermal protection                        | 12 |  |

|       | 7.3           | Status indication                         | 13 |  |

| 8     | Rev           | verse polarity protection                 | 15 |  |

| 9     | Acti          | ive clamp                                 | 16 |  |

| 10    | The           | rmal information                          | 18 |  |

|       | 10.1          | Thermal impedance                         | 18 |  |

| 11    | Pac           | kage information                          | 19 |  |

|       | 11.1          | QFN48L 8x6 mm package mechanical data     | 19 |  |

| 12    | Pac           | cking information                         | 23 |  |

| 13    | Ord           | lering information                        | 25 |  |

| Rev   | ision         | history                                   | 26 |  |

| Cor   | itents        | S                                         | 27 |  |

| List  | of ta         | bles                                      | 28 |  |

| l ist | of fic        | gures                                     | 29 |  |

# **List of tables**

| Table 1.  | Pin functions                      |

|-----------|------------------------------------|

| Table 2.  | Absolute maximum ratings           |

| Table 3.  | Thermal data                       |

| Table 4.  | Power section                      |

| Table 5.  | Switching (V <sub>CC</sub> = 24 V) |

| Table 6.  | Input pins                         |

| Table 7.  | Protections                        |

| Table 8.  | Status Pin                         |

| Table 9.  | Truth table                        |

| Table 10. |                                    |

| Table 11. | Tolerance of forms and positions   |

| Table 12. |                                    |

| Table 13. | Standard SPC parameters            |

| Table 14. | Ordering information               |

| Table 15. | Document revision history          |

DS13934 - Rev 2 page 28/30

# **List of figures**

| Figure 1.  | IPS8160HQ, IPS8160HQ-1 block diagram                                                                   | . 2 |

|------------|--------------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Connection diagram (top through view)                                                                  | . 3 |

| Figure 3.  | Turn-ON and turn-OFF                                                                                   | . 8 |

| Figure 4.  | V <sub>CC</sub> turn-ON                                                                                | . 8 |

| Figure 5.  | Current and voltage conventions                                                                        | 10  |

| Figure 6.  | Switching on resistive and on bulb lamp load                                                           | 11  |

| Figure 7.  | Switching on light and heavy inductive load                                                            | 11  |

| Figure 8.  | Short circuit during ON-state and Turn-on in short circuit                                             | 12  |

| Figure 9.  | Thermal protection flowchart                                                                           |     |

| Figure 10. | Thermal protection and STATUS behavior (T <sub>JSD</sub> triggered before T <sub>CSD</sub> )           | 13  |

| Figure 11. | Thermal protection and STATUS behavior (T <sub>CSD</sub> triggered before T <sub>JSD</sub> )           | 14  |

| Figure 12. | V <sub>CC</sub> Reverse Polarity Protection                                                            | 15  |

| Figure 13. | Active clamp typical waveforms                                                                         | 16  |

| Figure 14. | Typical demagnetization: E vs I (single pulse, all channels) at $V_{CC}$ = 24 V and $T_{AMB}$ = 125 °C | 16  |

| Figure 15. | Typical demagnetization: L vs I (single pulse, all channels) at $V_{CC}$ = 24 V and $T_{AMB}$ = 125 °C | 17  |

| Figure 16. | Simplified thermal model of the process stage                                                          | 18  |

| Figure 17. | QFN48L 8x6 mm package information                                                                      | 19  |

| Figure 18. | QFN48 8x6 mm suggested footprint [mm]                                                                  | 22  |

| Figure 19. | QFN48L 8x6 mm reel shipment reference                                                                  | 23  |

| Figure 20. | QFN48L 8x6 mm tape dimensions                                                                          | 24  |

| Figure 21. | QFN48L 8x6 mm tape, Pin 1 indication                                                                   | 24  |

|            |                                                                                                        |     |

DS13934 - Rev 2 page 29/30

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics - All rights reserved

DS13934 - Rev 2 page 30/30