# Two-channel Universal Asynchronous Receiver/Transmitter Dual UART

# **FEATURES** ☐ Two independent full duplex serial data lines ☐ Programmable baud rates individually selectable for each line's transmitter/receiver (50 to 19,200 baud) Summary registers that allow a single read to detect a data set change or to determine the cause of an interrupt on any line ☐ Triple buffers for each receiver Device scanner mechanism that reports interrupt request due transmitter/receiver interrupts Independently programmable lines for interrupt-driven operation ☐ Modem status change detection for Data Set Ready (DSR) and Data Carrier Detect (DCD) signals ☐ Programmable interrupts for modem status changes Synchronizes critical read-only registers Single 5V Power Supply TTL Compatible ☐ Compatible with SMC COM78C808 OCTAL UART and COM78C804 QUART

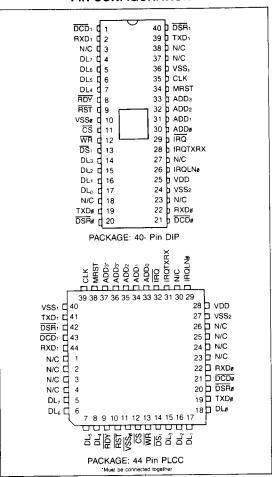

### PIN CONFIGURATION

### **GENERAL DESCRIPTION**

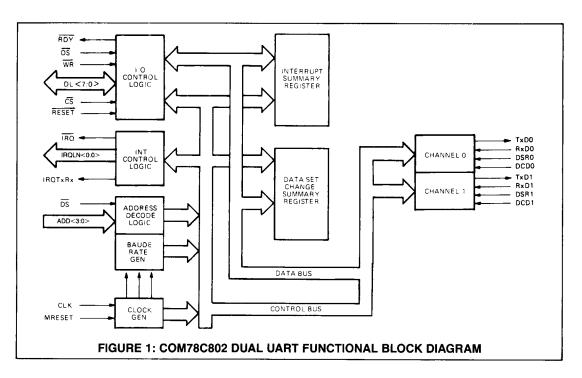

The COM78C802 Two-channel Asynchronous Receiver/ Transmitter (Dual UART) is a VLSI device for new generations of asynchronous serial communication designs and for microcomputer systems. This device performs the basic

operations necessary for simultaneous reception and transmission of asynchronous messages on two independent lines. Figure 1 is a functional block diagram of the COM78C802 Dual UART.

TABLE 1-COM78C802 PIN AND SIGNAL SUMMARY

| Pin-PLCC  | Pin-Dip   | Signal          | Input/Output | Definition/Function                                                                                                   |  |

|-----------|-----------|-----------------|--------------|-----------------------------------------------------------------------------------------------------------------------|--|

| 5-8,15-18 | 4-7,14-17 | DL<7:0>         | input/output | Data lines <7:0>-Receives and transmits the parallel data.                                                            |  |

| 33-37     | 30-33     | ADD<3:0>        | input        | Address < 3:0> - Selects the internal registers in the Dual UART. (Pins 36 and 37 must be connected in PLCC package.) |  |

| 12        | 11        | CS              | input        | Chip select—Activates the Dual UART to receive and transmit data over the DL<7:0> lines.                              |  |

| 14        | 13        | DS              | input        | Data strobe—Receives timing information for data transfers.                                                           |  |

| 13        | 12        | WR              | input        | Write-Specifies direction of data transfer on the DL<7:0> lines.                                                      |  |

| 9         | 8         | RDY             | output       | Ready-Indicates when the Dual UART is ready to participate in data transfer cycles.                                   |  |

| 10        | 9         | RESET           | input        | Reset-Initializes the internal logic.                                                                                 |  |

| 38        | 34        | MRST            | input        | Manufacturing reset-For manufacturing use.                                                                            |  |

| 39        | 35        | CLK             | input        | Clock-Clock input for timing.                                                                                         |  |

| 20,42     | 20,40     | DSR<1:0>        | inputs       | Data set ready—Monitor data set ready (DSR) signals from modems.                                                      |  |

| 21,43     | 1,21      | DCD<1:0>        | inputs       | Data set carrier detect—Monitor data set carrier detect (DCD) signals from modems.                                    |  |

| 32        | 29        | IRQ             | output       | Interrupt request–Requests a processor interrupt.                                                                     |  |

| 29        | 26        | IRQLN <c></c>   | output       | Interrupt request line number—Indicates the line number of originating interrupt request.                             |  |

| 31        | 28        | IRQTxRx         | output       | Interrupt request transmit/receive—Indicates whether an interrupt request is for transmitting or receiving data.      |  |

| 19,41     | 19,39     | TxD<1:0>        | outputs      | Transmit data—Provides asynchronous bit-serial data output streams.                                                   |  |

| 22,44     | 2,22      | RxD<1:0>        | input        | Receive data-Accepts asynchronous bit-serial data input streams.                                                      |  |

| 28        | 25        | V <sub>DD</sub> | input        | Voltage-Power supply voltage +5 Vdc.                                                                                  |  |

| 11,27,40  | 10,24,36  | V <sub>ss</sub> | input        | Ground-Ground reference                                                                                               |  |

# **DATA AND ADDRESS**

Data lines (DL<7:0>)—These lines are used for the parallel transmission and reception of data between the CPU and the Dual UART. The receivers are active when the data strobe ( $\overline{DS}$ ) signal is asserted. The output drivers are active only when the chip select ( $\overline{CS}$ ) signal is asserted, the data strobe ( $\overline{DS}$ ) signal is asserted, and the write ( $\overline{WR}$ ) signal is deasserted. The drivers will become inactive (high-impedance) within 50 nanoseconds when one or more of the following occurs: the chip select ( $\overline{CS}$ ) signal is deasserted, the data strobe ( $\overline{DS}$ ) signal is deasserted, or the write ( $\overline{WR}$ ) signal is asserted.

**Address (ADD<3:0>)**—These lines select which Dual UART internal register is accessible through the data I/O lines (DL<7:0>) when the data strobe ( $\overline{DS}$ ) and chip select ( $\overline{CS}$ ) signals are asserted. Table 2 lists the addresses corresponding to each register. The receiver buffer and transmitter holding register for each line have the same address. When the ( $\overline{WR}$ ) signal is deasserted, the address accesses the receiver buffer register and when asserted, it accesses the transmitter holding register.

TABLE 2-COM78C802 REGISTERS ADDRESS SELECTION

| ADD Line* | <3> | <2> | <1> | <0> | Read/Write | Register                   |

|-----------|-----|-----|-----|-----|------------|----------------------------|

|           |     | 0   | 0   | 0   | Read       | Line 0 Receiver Buffer     |

|           | 0   | 0   | Ö   | 0   | Write      | Line 0 Transmitter Holding |

|           | n   | Ô   | Ō   | 1   | Read       | Line 0 Status              |

|           | 0   | Ö   | 1   | 0   | Read/Write | Line 0 Mode Registers 1,2  |

|           | Ö   | Ö   | 1   | 1   | Read/Write | Line 0 Command             |

|           |     |     | 0   | 0   | Read       | Line 1 Receiver Buffer     |

|           | 1   | 0   | ň   | Ô   | Write      | Line 1 Transmitter Holding |

|           | 1   | ň   | ñ   | 1   | Read       | Line 1 Status              |

|           | 1   | 0   | 1   | 0   | Read/Write | Line 1 Mode Register 1,2   |

|           | 1   | ő   | 1   | 1   | Read/Write | Line 1 Command             |

|           | x   |     | 0   | 0   | Read       | Interrupt Summary          |

|           | X   | 1   | 0   | 1   | Read       | Data Set Change Summary    |

<sup>\*</sup>X = Either 0 or 1.

# **BUS TRANSACTION CONTROL**

Chip select ( $\overline{\text{CS}}$ )—This signal is asserted to permit data transfers through the DL<7:0> lines to or from the internal registers. Data transfer is controlled by the data strobe ( $\overline{\text{DS}}$ ) signal and write ( $\overline{\text{WR}}$ ) signal.

Data strobe (DS)— This input receives timing information for data transfers. During a write cycle, the CPU asserts the data strobe signal when valid output data is available and deasserts the data strobe signal before the data is removed. During a read cycle, the CPU asserts the data strobe signal and the Dual UART transfers the valid data. When the data strobe signal is deasserted, the DL<7:0> lines become a high impedance.

Write ( $\overline{WR}$ )—The write ( $\overline{WR}$ ) signal specifies the direction of data transfer on the DL<7:0> pins. If the  $\overline{WR}$  signal is asserted during a data transfer (the  $\overline{CS}$  and  $\overline{DS}$  signals asserted), the Dual UART is receiving data from DL<7:0>. If the  $\overline{WR}$  signal is deasserted during a write data transfer, the Dual UART is driving data onto the DL<7:0> lines.

#### INTERRUPT REQUEST

Interrupt request IRQ—The IRQ pin is an open drain output. The integral interrupt scanner asserts the IRQ signal when it has detected an interrupt condition on one of the two serial data lines.

Interrupt Request transmit/receive (IRQTxRx)—This signal indicates when the interrupt scanner in the Dual UART stops and asserts IRQ because of a transmitter interrupt condition (the IRQTxRx signal is asserted) or because of a receiver interrupt condition (the IRQTxRx signal is deasserted). The signal is valid only while IRQ is asserted. The state of IRQTxRx signal also appears as bit 0 of the interrupt summary register.

Interrupt request line number (IRQLN<0:0>)—This line indicates the line number at which the Dual UART interrupt scanner stopped and asserted the interrupt request (IRQ) signal. The number on this line is valid only while the IRQ signal is asserted. The state of this signal also appears a bit in the interrupt summary register: IRQLN<0> as bit 1. Table 3 shows the line numbers corresponding to settings of IRQLN.

# TABLE 3-COM78C802 INTERRUPT REQUEST LINE ASSIGNMENTS

| IRQ Line | Line |

|----------|------|

| 0        | 0    |

| <b>1</b> | 1    |

#### SERIAL DATA

**Transmit data (TxD<1:0>)**—These outputs transmit the asynchronous bit-serial data streams. They remain at a high level when no data is being transmitted and a low level when the TxBRK bit in the associated line's command register is set

Receive data (RxD<1:0>)—These lines accept asynchronous bit-serial data streams. The input signals must remain in the high state for at least one-half bit time before a high-to-low transition is recognized. (A high-to-low transition is required to signal the beginning of a "start" bit and initiate data reception).

#### **MODEM SIGNALS**

Data set ready (DSR<1:0>)—These two input pins, one for each serial data line on the COM78C802, are typically connected via intervening level converters to the data set ready outputs of modems. A TTL low at a DSR pin causes the DSR bit (bit 7) in the corresponding line's status register to be asserted. A TTL high at a DSR pin causes the DSR bit in the corresponding line's status register to be deasserted. A change of this input from high-to-low, or low-to-high, causes the assertion of the data set change (DSCHNG) bit that corresponds to this line in the data set change summary register. Changes from one state to the other and back again that occur within one microsecond may not be detected.

Carrier detect (DCD<1:0>)—These two input pins, one for each serial data line of the Dual UART, are typically connected through intervening level converters to the received line signal detect (also called carrier detect) outputs of modems. A TTL low at a DCD pin causes the DCD bit of the corresponding line's status register to be deasserted. A change of this input from high-to-low, or low-to-high, causes the assertion of the data set change (DSCHNG) bit corresponding to this line in the data set change summary register. Changes from one state to the other and back again that occur within one microsecond may not be detected.

## **GENERAL CONTROL SIGNALS**

Ready (RDY)—The RDY pin is an open drain output. Upon detecting a negative transition of chip select (CS), the Dual UART asserts the RDY signal to indicate readiness to take part in data transfer cycles. The RDY signal deasserts after the trailing edge of CS.

**Reset (RESET)**—When the RESET input in asserted, the TxD<1:0> lines are asserted and all internal status bits listed in the "Architecture Summary" discussion are cleared.

**Manufacturing reset (MRESET)**—This signal is for manufacturing use only and the input should be connected to ground for normal operation.

### MISCELLANEOUS SIGNALS

**Clock in (CLK)**–All baud rates and internal clocks are derived from this input. Normal operating frequency is 4.9152 MHz  $\pm 0.1$  percent and duty cycle is 50 percent  $\pm 5$  percent.

### **POWER AND GROUND**

Voltage (V<sub>DD</sub>)—Power supply 5 Vdc Ground (V<sub>SS</sub>)—Ground reference

### **ARCHITECTURE SUMMARY**

The Dual UART functions as a serial-to-parallel, parallel-to-serial converter/controller. It can be programmed by a microprocessor to provide different characteristics for each of its two serial data lines (stop bits, parity, character length, split baud rates, etc.)

Each serial line functions the same as a one-line UARTtype device thereby reducing the number of chips and conserving space on communication devices that require multiple communications lines.

An integral interrupt scanner checks for device interrupt conditions on the two lines. Its scanning algorithm gives priority to receivers over transmitters. The scanner can also check for interrupts resulting from changes in modem control signals  $\overline{DSR}$  and  $\overline{DCD}$ .

### Line-specific Registers

Each of the two serial data lines in the Dual UART has a set of registers for buffering data into and out of the line and for external control of the line's characteristics. These registers are selected for access by setting the appropriate address on lines ADD<3:0>. Lines ADD<4:3> select one of the two data lines. Lines ADD<2:0> selects the specific register for that line. Refer to Table 2 for the register address assignments.

Receiver buffer register—Each line's receiver consists of a character assembly register and a two-entry FIFO that is the receiver buffer register. When the RxEN bit in a line's command register is set, received characters are moved automatically into the line's receiver buffer as soon as they have been deserialized from the associated communications line. When there are characters in this FIFO, the RxRDY bit is set in the status register for the line.

The assertion of the RxRDY signal for a line that already has the RxIE bit of its command register set causes the interrupt scanner logic to stop and generate an interrupt condition (the IRQ signal is asserted). When the receiver buffer is read, the interrupt condition is cleared (the IRQ signal is deasserted) and the interrupt scanner resumes operation.

If there is another entry in a line's FIFO, the RxRDY bit remains asserted. When the interrupt scanner reaches this line again, the assertion of RxRDY causes the scanner to halt and assert the  $\overline{\mbox{IRQ}}$  again.

Asserting the RESET signal or clearing the RxEN bit initializes the receiver logic of Dual UART. The RxRDY flag is cleared and the receiver buffer register outputs become undefined. Any data in the FIFO at that time is lost.

**Transmitter holding register**—Each line has a writable transmitter holding register. When the TxEN bit in the line's command register is set, characters are moved automatically from the output of this register into the transmitter serialization logic whenever the serialization logic becomes idle.

When this register is empty, the TxRDY bit in the line's status register is set. If the transmitter interrupt enable (TxIE) bit in the line's command register is also set, the interrupt scanner logic halts and generates an interrupt condition. If a character is then loaded into the register, the interrupt is cleared and the scanner resumes operation.

Assertion of the RESET signal initializes the transmitter logic of the Dual UART. The TxRDY flag is cleared and the transmitter holding register's contents are lost. The transmitter enable (TxEN) bit in the line's command register is also cleared by RESET. If at the end of the reset process, the TxEN is reasserted and TxRDY bit is reasserted. Software clearing of TxEN alone produces results different from the full RESET in that the transmitter holding register's contents are not lost; they are transmitted when TxEN is set again.

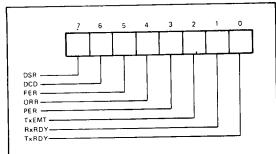

Status register—Each line has a read-only status register that provides information about the current state of the given line. This register indicates a line's readiness for transmission or reception of data and flags error conditions in its bit fields. Figure 3 shows the format of the status register. Table 3 lists the flag bits in each status register.

FIGURE 3: COM78C802 STATUS REGISTERS (LINE 0:1) FORMAT

# TABLE 4-COM78C802 STATUS REGISTERS (LINES 0-1) DESCRIPTION

|     | TABLE 4-COM/ COCCE CIAI CO II. E.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7   | DSR (Data set ready)—This bit is the inverted state of the DSR line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6   | DCD (Data set carrier detect)—This bit is the inverted state of the DCD line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5   | FER (Frame error)—Set when the received character currently displayed in the receiver buffer register was not framed by a stop bit. Only the first stop bit is checked to determine that a framing error exists. Subsequent reading of the receiver buffer register that indicates all zeros (including the parity bit, if any) can be interpreted as a Break condition. This bit is cleared by clearing RxEN (bit 2) of the command register, by asserting the RESET input or by setting the reset error RERR (bit 4) of the command register.                                                                                                                         |

| 4   | ORR (Overrun error)—Set when the character in the receiver buffer register was not read before another character was received. Cleared by clearing RXEN (bit 2) of the command register, by asserting the RESET input, or by setting reset error RERR (bit 4) of the command register.                                                                                                                                                                                                                                                                                                                                                                                  |

| 3   | PER (Parity error)—If parity is enabled and this bit is set, the received character in the receiver buffer register has an incorrect parity bit. This bit is cleared by clearing RxEN (bit 2) of the command register, by asserting the RESET input, by setting reset error RERR (bit 2) of the command register, or by reading the current character in the receiver buffer register.                                                                                                                                                                                                                                                                                  |

| 2   | TxEMT (Transmitter empty)—Set when the transmitter serialization logic for the associated line has completed transmission of a character, and no new character has been loaded into the transmitter holding register. Cleared by loading the transmitter holding register, by clearing TxEN (0) of the command register, or by asserting the RESET input.                                                                                                                                                                                                                                                                                                               |

| 1   | RxRDY (Receiver buffer ready)—When set, a character has been loaded into the FIFO buffer from the deserial-<br>ization logic. Cleared by reading the receiver buffer register, by clearing RxEN (bit 2) in the command register,<br>or by asserting the RESET input.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0   | TxRDY (Transmitter holding register ready)—When set, this bit indicates that the transmitter holding register is empty. Cleared when the program has loaded a character into the transmitter holding register, when the transmitter for this line is disabled by clearing TxEN (bit 0) in the command register, or by asserting the RESET input. This bit is initially set when the transmitter logic is enabled by the setting of TxEN (bit 0) and the transmitter holding register is empty. This bit is not set when the automatic echo or remote loopback modes are programmed. Data can be overwritten if a consecutive write is performed while TxRDY is cleared. |

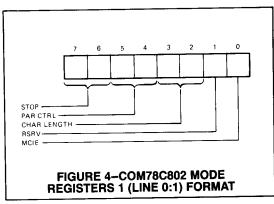

**Mode registers 1 and 2**—These read/write registers control the attributes (including parity, character length, and line speed) of the communications line.

Each of the two communications lines has two of these registers, both accessed by the same address on ADD<3:0>. Successive access operations (either read or write, in any combination) alternate between the two registers at that address by use of an internal pointer. The first operation addresses mode register 1, the next address mode register 2, and another after that would recycle the pointer to mode register 1. The pointer is reset to point to mode register 1 by RESET or by a read of the command register for this line. These registers should not be accessed by bit-oriented instructions that do read/modify/write cycles.

Figure 4 shows the format of mode registers 1 and Table 5 describes the function of the register information.

TABLE 5-COM78C802 MODE REGISTERS 1 (LINES 0-1) DESCRIPTION

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7,6 | STOP-These bits determine the number of stop bits that are appended to the transmitted characters as follows. These bits are cleared by asserting the RESET input.  Bits Stop Bits 7 6 0 0 Invalid 0 1 1.0 1 0 1.5 1 1 2.0                                                                                                                                                                                                                                                                         |

| 5,4 | PAR CTRL (Parity control)—These bits determine parity as follows and are cleared by asserting the RESET input. X = either 1 or 0.  Bits Parity Type  5 4  1 1 Even 0 1 Odd X 0 Disabled                                                                                                                                                                                                                                                                                                            |

| 3,2 | CHAR LENGTH (Character length)—These bits determine the length (excluding start bit, parity, and stop bits) of the characters received and sent. Received characters of less than 8 bits are "right aligned" in the receiver buffer with unused high-order bits equal to zero. Parity bits are not shown in the receiver buffer. The character length bits are cleared by asserting the RESET input. The character length bits are defined as follows:  Bit Bit Length 3 2 0 0 5 0 1 6 1 0 7 1 1 8 |

| 1   | RSRV (Reserved and cleared by asserting the RESET input.)                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0   | MCIE (Modern control interrupt enable)—When set and RxIE (bit 5) of the command register is set, the modern control interrupts are enabled. Refer to the Interrupt Scanner and Interrupt Handling information. Cleared by asserting the RESET input.                                                                                                                                                                                                                                               |

Figure 5 shows the format of mode registers 2 and Table 6 indicates the baud rate selections of the register. Bits 7 through 4 of the mode register 2 control the transmitter baud rate and bits 3 through 0 control the receiver baud rate. These registers are cleared by asserting RESET input.

XMIT RATE RECV RATE

FIGURE 5-COM78C802 MODE REGISTERS 2 (LINE 0-1) FORMAT

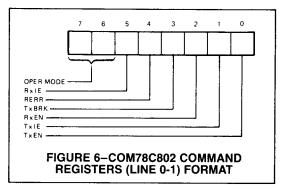

**Command register**—These read/write registers control various functions on the selected line. Figure 6 shows the format of the command registers and Table 7 describes the function of the register information.

# TABLE 6-COM78C802 MODE REGISTERS 2 (LINES 0-1) DESCRIPTION

| Bit | Descri  | ption                |         |          |   |   |                    |    |                     |         | <u> </u> |

|-----|---------|----------------------|---------|----------|---|---|--------------------|----|---------------------|---------|----------|

| 7:0 | receive | RATE/R<br>er (bits 3 | 3:0) as | follows: |   |   | er Rate<br>er Bits |    | ts the baud rate of | Actual  | Error*   |

|     | 7       | 6                    | 5       | 4        | 3 | 2 | 1                  | 0  | Rate                | Rate    | (percent |

|     | i n     | ñ                    | õ       | Ó        | 0 | 0 | 0                  | 0  | 50                  | same    | _        |

|     | ĺŏ      | ñ                    | ň       | 1        | 0 | 0 | 0                  | 1  | 75                  | same    |          |

|     | 0       | n                    | 1       | 'n       | ō | Ō | 1                  | 0  | 110                 | 109.09  | 0.826    |

|     | 1 6     | ñ                    | i       | 1        | Õ | 0 | 1                  | 1  | 134.5               | 133.33  | 0.867    |

|     | 0       | 1                    | 'n      | ò        | ñ | 1 | Ô                  | 0  | 150                 | same    | _        |

|     | 0       | ,                    | ñ       | 1        | ñ | 1 | ō                  | 1  | 300                 | same    | _        |

|     | ŏ       | 1                    | 1       | 'n       | ň | 1 | 1                  | 0  | 600                 | same    | _        |

|     | 0       | 1                    | i       | 1        | ñ | 1 | 1                  | 1  | 1200                | same    | _        |

|     | 1 0     | 'n                   | 'n      | 'n       | 1 | ń | ń                  | Ó  | 1800                | 1745.45 | 3.03     |

|     | 1 1     | 0                    | 0       | 1        | 1 | ñ | ň                  | 1  | 2000                | 2021.05 | 1.05     |

|     | -       | 0                    | 1       | ò        | i | ñ | 1                  | Ó  | 2400                | same    |          |

|     |         | 0                    | 1       | 1        | i | ñ | i .                | 1  | 3600                | 3490.91 | 3.03     |

|     | 1 1     | 0                    | 0       | _        |   | 1 | 'n                 | 'n | 4800                | same    |          |

|     | 1 1     | 1                    | Ü       | 4        | 1 | 4 | 0                  | 1  | 7200                | 6981.81 | 3.03     |

|     | 1 !     | 1                    | 0       | _        |   |   | 1                  | 'n | 9600                | same    | _        |

|     | 1 1     | 1                    | 1       | 0        | 1 | 1 | 1                  | 1  | 19200               | same    | _        |

<sup>\*</sup>The frequency of the clock input (CLK) is 4.9152 MHz. The clock input may vary by 0.1 percent. This variance results in an error that must be added to the error listed.

# TABLE 7-COM78C802 COMMAND REGISTERS (LINES 0-1) DESCRIPTION

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7,6 | OPER MODE (Operating mode)—These bits control the operating mode of the channel as follows. These bits are cleared by asserting the RESET input.  Bit Operating Mode  7 6 0 0 Normal operation 0 1 Automatic echo 1 0 Local loopback 1 1 Remote loopback                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 5   | RxIE (Receiver interrupt enable)—When set, the RxRDY flag (bit 1) of the status register for this line will generate an interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 4   | RERR (Reset error)—When set, this bit clears the framing error, over <u>run error</u> , and parity error of the status register associated with this line. This bit is cleared by asserting the RESET input (not self-clearing).                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 3   | TxBRK (Transmit break)—When set, this bit forces the appropriate TxD<1:0> line to the spacing state at the conclusion of the character presently being transmitted. When the program clears this bit, normal operation is restored, and any character pending in the transmitter holding register is moved into the serialization logic and transmitted. The minimum break length obtainable is twice the character length plus 1 bit time. The maximum break length depends on the amount of time between the program setting and clearing this bit, but is an integral number of bit times. This bit is cleared by asserting the RESET input. |  |  |  |  |  |  |

| 2   | RxEN (Receiver enable)—When set, this bit enables the receiver logic. When cleared, it stops the assembling of the received character, clears all receiver error bits and the RxRDY (bit 1) of the status register, clears any receiver interrupt conditions associated with this line, and initializes all receiver logic. This bit is cleared by asserting the RESET input.                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 1   | TxIE (Transmit interrupt enable)—When set, the state of the associated TxRDY flag (bit 0) of the status register is made available to the interrupt scanner logic. When the interrupt scanner logic scans this line, it determines if the TxRDY flag is asserted and generates an interrupt by asserting the IRQ signal.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 0   | TxEN (Transmitter enable)—When set, this bit enables the transmitter logic. When cleared, it inhibits the serialization of the characters that follow but the serialization of the current character is completed. It also clears the TxRDY flag (bit 0) of the status register, clears any transmitter interrupt conditions associated with this line, and initializes all transmitter logic except that associated with the transmitter holding register. The character in the transmitter holding register is retained so that XON/XOFF situations can be properly processed. This bit is cleared by asserting the RESET input.              |  |  |  |  |  |  |

Bits 5 through 0 enable the line's receiver and transmitter, enable handling of interrupts, initiate the transmission of break characters, and reset error bits for the line. Refer to "Interrupt Scanner" and "Interrupt Handling" paragraphs for detailed interrupt information. Bits 7 and 6 control the operating mode of the line. The four modes that can be set are:

□ Normal operation—The serial data received is assembled in the receiver logic and transferred in parallel to the receiver buffer register. (The RxEN bit must be set.) Data to be transmitted is loaded in parallel into the transmitter holding register, then automatically transferred into the transmitter logic and serialized for transmission. (The TxEN bit must be set.)

☐ Automatic echo—The serial data received is assembled into parallel in the receiver logic (the RxEN bit must be set) and transferred to the receiver buffer register. Arriving serial data is also routed to the line's TxD<n> pin for serial output. TxEN is ignored and the transmitter logic is disabled. TxRDY flags and TxEMT indications are cleared. No transmitter interrupts are generated.

□ Local loopback—The serial data from the RxD<n> input is ignored and the receiver serial input receives data from the transmitter serial output. The data is assembled into parallel form in the receiver logic (the RxEN bit must be set) and transferred to the receiver buffer register where it can be read by the program. Data to be transmitted to the receiver is loaded in parallel form into the transmitter holding register from which it is automatically moved into the transmitter logic and serialized for transmission. (The TxEN bit must be set.) The transmission goes only to the receiver serial input; the TxD<n> output is held high. As normal operation, transmission and reception baud rates are controlled by the transmitter speed and receiver speed entries in mode register 2.

☐ Remote loopback—The serial data received on the RxD<n> line is returned to the TxD<n> line without further action. No data is received or transmitted. The RxRDY, TxRDY, and TxEMT flags are disabled. The TxEN and RxEN bits of the command register are held cleared, causing the transmitter and receiver logic to be disabled.

#### **SUMMARY REGISTERS**

The Dual UART contains two registers that summarize the current status of all two serial data lines, making it possible to determine that a line's status has changed with a single read operation. These registers are selected for access by setting the appropriate address on pins ADD <2:0>. Because the registers are shared by two serial lines, the line-selection bits (ADD <4:3>) are ignored when these registers are accessed. Refer to "Interrupt Scanner and Interrupt Handling" for detailed interrupt information.

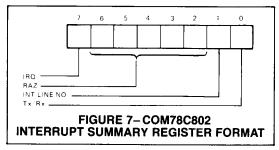

Interrupt summary register—This read-only register indicates that a transmitter or receiver interrupt condition has occurred, and indicates the line number that generated the interrupt. Figure 7 shows the format of the interrupt summary register and Table 8 describes register information.

### TABLE 8-COM78C802 INTERRUPT SUMMARY REGISTER DESCRIPTION

| Bit | Description                                                                                                                                                                                                                                                  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IRQ (Interrupt request)—When set, this bit indicates that the interrupt scanner has found an interrupting condition among the two serial lines of the Dual UART. These conditions also result in the Dual UART asserting the IRQ signal.                     |

| 6:2 | RAZ (Read as zero)-Not used                                                                                                                                                                                                                                  |

| 1*  | INT LINE NO (Interrupting line number)—This bit indicates the line number upon which an interrupting condition was found. Refer to Table 3.                                                                                                                  |

| 0*  | Tx/Rx (Transmit/receive)—This bit indicates whether the interrupting condition was caused by a transmitter (Tx/Rx equals 1) or a receiver (Tx/Rx equals 0). This bit corresponds to the IRQTxRx signal of the Dual UART and is set when IRQTxRx is asserted. |

<sup>\*</sup>Bits 1-0 above represent the outputs of a free-running counter and are valid only when bit 7 is set.

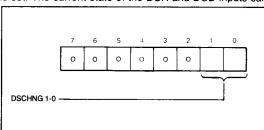

Data set change summary register—When the DSR or DCD inputs that are associated with a line change state, the bit corresponding to that line in this read-only register is set. The current state of the DSR and DCD inputs can

FIGURE 8-COM78C802 DATA SET CHANGE SUMMARY REGISTER FORMAT

then be obtained from that line's status register. If the state of a line changes twice within one microsecond, the change in state may not be detected. Figure 8 shows the format of the data set change summary register.

When the MCIE bit in a line's mode register 1 is set and RxIE is also set, the modem control interrupts are enabled for that line. If DSCHNG for that line is then set, the interrupt scanner will halt and assert the  $\overline{\text{IRQ}}$  signal. The data set change summary register bits are cleared by writing a 1 into the bit position. A program that uses this register should read and save a copy of its contents. The copy can then be written back to the register to clear the bits that were set. The system interrupts should be disabled and writeback should directly follow the read operation.

Assertion of the RESET signal disables and initializes the data set change logic. When the RESET signal is deasserted, future changes in DSR and DCD are reported as they occur.

# INTERRUPT SCANNER AND INTERRUPT HANDLING

The interrupt scanner sequentially checks each line for a receive interrupt and then checks each one in the same order for a transmitter interrupt. If the scanner detects an interrupt condition, it stops and the IRQ signal is asserted. An interrupt must be serviced by software or no other interrupt request can be posted.

The scanner determines that a line has a receiver interrupt if the line's receiver buffer is ready and receiver interrupts are enabled for that line (RxRDY and RxIE = 1) or either of the line's modem status signals has changed state and both receiver and modem control interrupts are enabled for that line (DSCHNG and RxIE and MCIE = 1).

The scanner determines that a line has a transmitter interrupt if the line's transmitter holding the register is empty and transmitter interrupts are enabled for that line (TxRDY and TxIE = 1).

When the scanner detects an interrupt, it reports the line number on the IRQ<0> line. The IRQTxRx signal is asserted for a transmitter interrupt and deasserted for a receiver interrupt. The appropriate bits are also updated in the interrupt summary register. The  $\overline{\text{IRQ}}$  line is deasserted and the scanner is restarted for each of the following three types of interrupt conditions.

- ☐ Reading the receiver buffer or resetting the RxIE bit of the interrupting line for the first type of receiver interrupt previously described.

- Resetting the MCIE, RxIE, or DSCHNG bit of the interrupting line for the second type of receiver interrupt previously described.

- Loading the transmitter holding register or resetting the TxIE bit of the interrupting line for transmitter interrupts.

If the scanner was originally stopped by a receiver interrupt condition, the scanner resumes sequential operation from where it stopped, thus providing receivers with equal priority. If the scanner was stopped by a transmitter condition, the scanner restarts from position 0 (line 0's receiver), thus giving receivers priority over transmitters.

# EDGE-TRIGGERED AND LEVEL-TRIGGERED INTER-RUPT SYTSTEMS

If the interrupt system of the Dual UART is used only for generating interrupts for the RxRDY and/or TxRDY flags, the  $\overline{IRQ}$  line can be connected to a processor having either edge-triggered or level-triggered interrupt capability. If the modem control interrupts are being used (MCIE in mode register 1 = 1), the  $\overline{IRQ}$  line can be connected only to a processor that uses level-triggered interrupts.

### MODEM HANDLING

The TxEMT (transmitter empty) bit of the status register is typically used to indicate when a program can disable the transmission medium, as when deasserting the request-to-send line of a modem. A typical program will load the last character for transmission and then monitor the TxEMT bit of the status register.

The assertion of the TxEMT bit to indicate the transmission is complete may occur a substantial time after the loading of the last character. After the last character is loaded, one character is in the transmitter holding register and one character is in the serialization logic. Therefore, it will be two character times before the transmission process is completed. Waiting for the TxRDY signal to assert before monitoring the TxEMT status shortens this by one character time because the TxRDY status bit indicates that there are no characters in the transmitter holding register. The times involved are calculated by taking the reciprocal of the baud rate being used, multiplying by the number of bits per character (a starter bit-5,6,7, or 8 data bits; plus parity bit if enabled; and 1,1.5, or 2 stop bits), and multiplying by either two characters or one, depending on when TxEMT monitoring begins.

# MAXIMUM GUARANTEED RATINGS\*

| Operating Temperature Range                             | 0°C to +70°C     |

|---------------------------------------------------------|------------------|

| Storage Temperature Range                               | – 55° to + 125°C |

| Lead Temperature (soldering, 10 sec.)                   | +300°C           |

| Positive Voltage on any I/O Pin, with respect to ground | $V_{cc} + 0.3V$  |

| Negative Voltage on any I/O Pin, with respect to ground | – 0.3V           |

| Maximum V.                                              | +7V              |

<sup>\*</sup>Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

NOTE: When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes or "glitches" on their outputs when the AC power is switched on and off. In addition, voltage transients on the AC power line may appear on the DC output. For example, the bench power supply programmed to deliver  $+\tilde{5}$  volts may have large voltage transients when the AC power is switched on and off. If this possibility exists it is suggested that a clamp circuit be used.

### **TABLE 9-COM78C802**

### DC ELECTRICAL CHARACTERISTICS

| Symbol                        | Parameter                                                                                  | Test Condition                                                                                                                               |              | rements<br>yp. Max. | Units    |

|-------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|----------|

| V <sub>IH</sub>               | High-level input voltage                                                                   |                                                                                                                                              | 2.0          |                     | V        |

| V <sub>IL</sub>               | Low-level input voltage                                                                    |                                                                                                                                              |              | 0.8                 | ٧        |

| V <sub>OH</sub>               | High-level output voltage                                                                  | V <sub>DC</sub> = Min.<br>I <sub>DH</sub> = 3.5 mA for DL<7:0><br>I <sub>DH</sub> = 2.0 mA for all<br>remaining output except IRQ<br>and RDY | 2.4          |                     | V        |

| V <sub>OL</sub>               | Low-level output voltage                                                                   | $V_{DD}$ = Min.<br>$I_{OL}$ = 5.5 mA for DL <7:0><br>$I_{OL}$ = 3.5 mA for all remaining outputs                                             |              | 0.4                 | ٧        |

| I <sub>IH</sub>               | Input current at maximum input voltage                                                     | $V_{DD} = Max.$<br>$V_{I} = V_{DD}(Max.)$                                                                                                    |              | 10                  | μΑ       |

| I <sub>IL</sub>               | Input current at miminum input voltage                                                     | $V_{DD} = Max.$<br>$V_1 = 0.0V$                                                                                                              |              | - 10                | μΑ       |

| l <sub>os</sub> ¹             | Short-circuit output<br>current for DL<7:0> all<br>remaining outputs except<br>IRQ and RDY | $V_{DD} = Max$ .                                                                                                                             | - 50<br>- 30 | - 180<br>- 110      | mA<br>mA |

| l <sub>OZL</sub> <sup>2</sup> | Three-state output current                                                                 | $V_{DD} = Max.$<br>$V_{O} = 0.4V$                                                                                                            |              | 10                  | μΑ       |

| l <sub>OZH</sub> <sup>2</sup> | Three-state output current                                                                 | $V_{DD} = Max.$<br>$V_{O} = 2.4V$                                                                                                            |              | 10                  | μΑ       |

| I <sub>DD</sub>               | Supply current                                                                             | $V_{DD} = Max.$ $T_A = 0^{\circ}$                                                                                                            |              | 15                  | mA       |

| C <sub>in.</sub>              | Input capacitance                                                                          |                                                                                                                                              |              | 4                   | pF       |

| C <sub>IO</sub> <sup>3</sup>  | Input/output capacitance                                                                   |                                                                                                                                              |              | 5                   | pF       |

<sup>&#</sup>x27;No more than one ouput should be short circuited at a time, and the duration of the short should not exceed 1 second.

### **TIMING PARAMETERS**

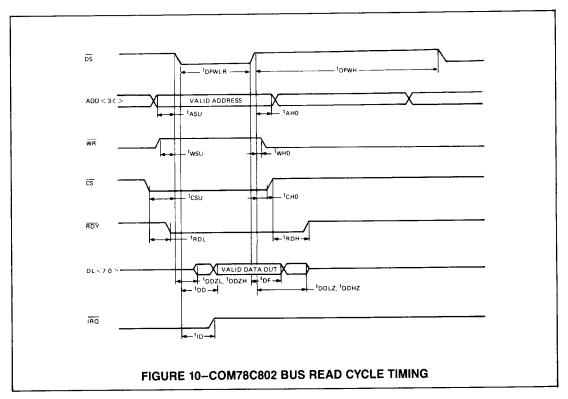

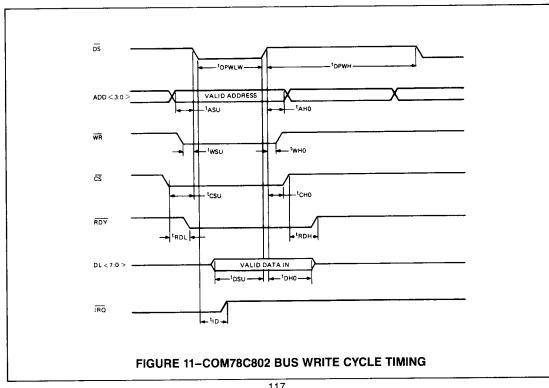

information from the Dual UART to the processor. Figure 11 the timing parameters for the read and write cycles.

shows the signal timing for a write cycle to transfer infor-Figure 10 shows the signal timing for a read cycle to transfer mation from the processor to the Dual UART. Table 11 lists

<sup>2</sup>All three-state output drivers are wired in an I/O configuration. The parameters include the driver and input receiver leakage currents.

<sup>&</sup>lt;sup>3</sup>The parameters include the capacitive loads of the output driver and the input receiver.

## TABLE 10-COM78C802 BUS READ AND WRITE TIMING PARAMETERS

| Symbol              | Definition                                                                                                                                                                                                                                                                                            | Requirer<br>Min. | nents (ns)<br>Max.               | Load<br>Circuit <sup>1</sup>                                                                       |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------|----------------------------------------------------------------------------------------------------|

| t <sub>AHO</sub>    | Hold time of a valid ADD <3:0> to a valid high level of DS.                                                                                                                                                                                                                                           | 10               |                                  |                                                                                                    |

| t <sub>asu</sub>    | Setup time of a valid ADD <3:0> to the falling edge of DS.                                                                                                                                                                                                                                            | 30               |                                  |                                                                                                    |

| t <sub>cHO</sub>    | Hold time of a valid low level of $\overline{CS}$ to a valid high level of $\overline{DS}$ .                                                                                                                                                                                                          | 10               |                                  |                                                                                                    |

| t <sub>csu</sub>    | Setup time of a valid low level of CS to the falling edge of DS.                                                                                                                                                                                                                                      | 30               |                                  |                                                                                                    |

| too                 | Propagation delay of a valid low level on $\overline{\rm DS}$ (if $\overline{\rm CS}$ is low and $\overline{\rm WR}$ is high) to valid high or low data on DL <0>.                                                                                                                                    | 165              |                                  | C <sub>L</sub> = 150 pF                                                                            |

| t <sub>ooLZ</sub> ² | Propagation delay of a valid high level on DS (if CS is low and WR is high) to DL <0> output drivers disabled.  1-DDLZ |                  | 50<br>50<br>60<br>60<br>65<br>65 | $C_{L} = 50pF \\ C_{L} = 50pF \\ C_{L} = 100pF \\ C_{L} = 100pF \\ C_{L} = 150pF \\ C_{L} = 150pF$ |

| todzi               | Propagation delay of a valid low level on DS (if CS is low and WR is high) to DL <7:0> output driver enabled.  today of a valid low level on DS (if CS is low and WR is high) to DL <7:0> output driver enabled.                                                                                      | 0                | 165<br>165                       | C <sub>L</sub> = 150pF<br>C <sub>L</sub> = 150pF                                                   |

| t <sub>DF</sub>     | Hold time provided during a read cycle by Dual UART of valid high or low data on DL <7:0> after the rising edge of DS.                                                                                                                                                                                | 0                | ,                                |                                                                                                    |

| t <sub>DHO</sub>    | Hold time of a valid DL $<7:0>$ to a valid high level of $\overline{DS}$ .                                                                                                                                                                                                                            | 30               |                                  |                                                                                                    |

| t <sub>opwh</sub>   | Pulse width high of DS.                                                                                                                                                                                                                                                                               | 450              |                                  |                                                                                                    |

| topwer              | Pulse width low of $\overline{\rm DS}$ when $\overline{\rm WR}$ is high (read operation). Refer to timing parameter t <sub>DPMLW</sub> also.                                                                                                                                                          | 180              | 10,000                           |                                                                                                    |

| t <sub>opwlw</sub>  | Pulse width low of $\overline{DS}$ when $\overline{WR}$ is low (write operation). Refer to timing parameter $t_{DPWLR}$ also.                                                                                                                                                                         | 130              | 10,000                           |                                                                                                    |

| t <sub>osu</sub>    | Setup time of a valid DL $<7:0>$ to the rising edge of $\overline{DS}$ .                                                                                                                                                                                                                              | 50               |                                  |                                                                                                    |

| t <sub>ID</sub> 3   | Propagation delay of a valid low level on $\overline{DS}$ (if $\overline{CS}$ is low) to a high level on $\overline{IRQ}$ .                                                                                                                                                                           |                  | 635                              | C <sub>L</sub> = 50pF                                                                              |

| t <sub>RDH</sub> 4  | Propagation delay of a valid high level of $\overline{\text{CS}}$ to a valid high level on $\overline{\text{RDY}}$ .                                                                                                                                                                                  |                  | 210                              | C <sub>L</sub> = 50pF                                                                              |

| t <sub>RÓL</sub>    | Propagation <u>delay</u> of a valid low level on <del>CS</del> to a valid low level on <del>RDY</del> .                                                                                                                                                                                               |                  | 90                               | C <sub>⊾</sub> = 50pF                                                                              |

| t <sub>who</sub>    | Hold time of a valid high or low level of WR to a valid high level of DS.                                                                                                                                                                                                                             | 10               |                                  |                                                                                                    |

| t <sub>wsu</sub>    | Setup time of a valid high or low level of $\overline{\text{WR}}$ to the falling edge of $\overline{\text{DS}}$ .                                                                                                                                                                                     | 30               |                                  |                                                                                                    |

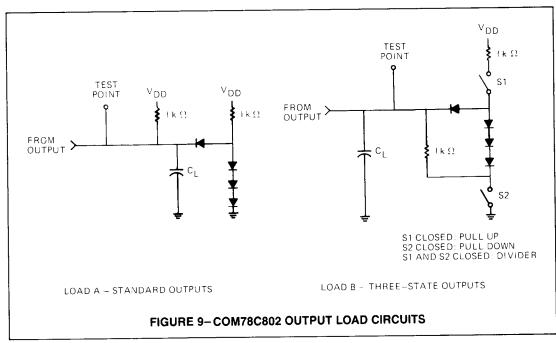

'Refer to Figure 9 for the load circuits used with these measurements.

<sup>&</sup>lt;sup>2</sup>The t<sub>obuz</sub> and t<sub>obuz</sub> parameters are measured with C<sub>L</sub> = 150 pF. The values of t<sub>obuz</sub> and t<sub>obuz</sub> for C<sub>L</sub> = 50pF and C<sub>L</sub> = 100 pF have been derived for user convenience.

Total rise time depends on internal delay plus the pullup delay introduced by the external resistor being used. The  $t_{\text{ID}}$  parameter can be calculated by the following:  $t_{\text{D}} = 500 + \text{RC}_{\text{L}}$  where R = value of the resistor that connects to capacitor  $C_{\text{L}}$  in load A, Figure 9.

<sup>\*</sup>Total rise time depends on internal delay plus the pullup delay introduced by the external resistor being used. The t<sub>RDH</sub> parameter can be calculated by the following: t<sub>RDH</sub> = 75 + RC<sub>L</sub> where R = value of the resistor that connects to capacitor C<sub>L</sub> in load A, Figure 9.

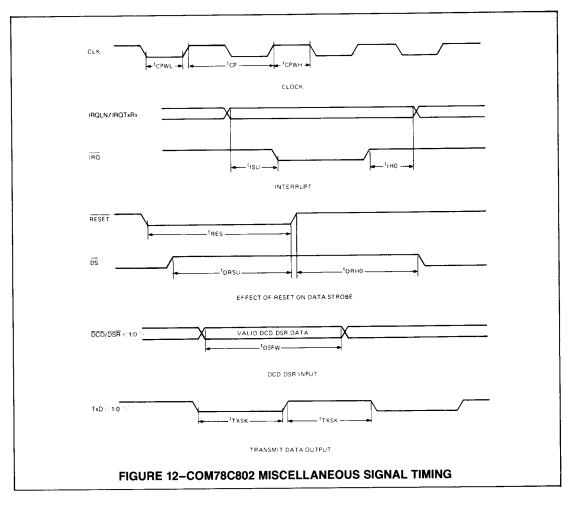

# TABLE 11-MISCELLANEOUS WRITE TIMING PARAMETERS

| Symbol            | Definition                                                                                                                                                                                                                                        | Requirements (ns)<br>Min. | Load Circuit          |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|--|

| t <sub>CP</sub>   | Period of CLK.                                                                                                                                                                                                                                    | 203.45 (4.9152 MHz)       |                       |  |

| t <sub>CPWH</sub> | Pulse width high of CLK.                                                                                                                                                                                                                          | 95                        |                       |  |

| t <sub>CPWL</sub> | Pulse width low of CLK.                                                                                                                                                                                                                           | 95                        |                       |  |

| t <sub>ояно</sub> | Hold time of a valid high level of $\overline{\text{DS}}$ to a valid high level of RESET.                                                                                                                                                         | 1,000                     |                       |  |

| t <sub>DRSU</sub> | Setup time of a valid high level of $\overline{\text{DS}}$ to the rising edge of RESET.                                                                                                                                                           | 900                       |                       |  |

| t <sub>DSPW</sub> | Pulse width high or low of DCD <1:0> and DSR <1:0>.                                                                                                                                                                                               | 1,000                     |                       |  |

| t <sub>IHO</sub>  | Hold time provided by Dual UART from a valid IRQLN and IRQTxRx to a valid high level of IRQ.                                                                                                                                                      | 100                       | C <sub>L</sub> = 50pF |  |

| t <sub>isu</sub>  | Setup time provided by Dual UART from a valid IRQLN and IRQTxRx to a valid low level of IRQ.                                                                                                                                                      | 100                       | C <sub>L</sub> = 50pF |  |

| t <sub>RES</sub>  | Pulse width low of RESET.                                                                                                                                                                                                                         | 1,000                     |                       |  |

| t <sub>txsk</sub> | Pulse width high or low provided by Dual UART on the $TxD < 1:0>$ lines. At each baud rate, the actual pulse widths provided vary by $t_{\tau xsx}$ . This timing parameter should be used to determine cumulative reception/transmission errors. | 250                       | C <sub>L</sub> = 50pF |  |

<sup>\*</sup>Refer to Figure 9 for the load circuits used with these measurements.

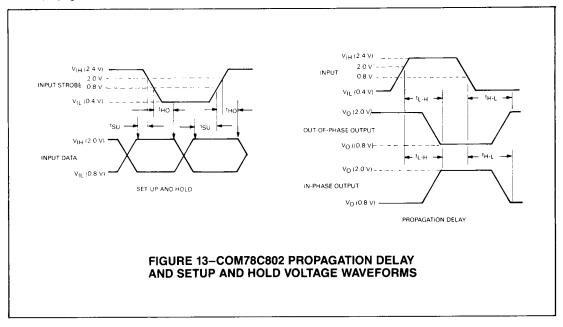

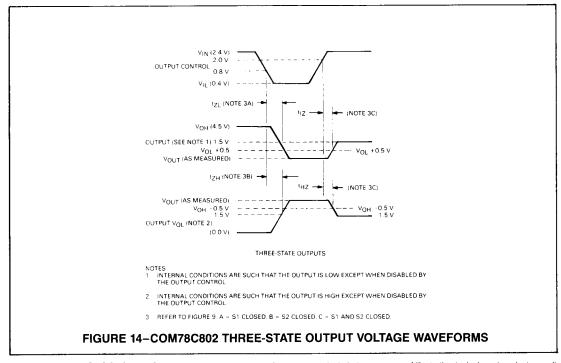

Figure 13 shows the input and output voltage waveforms for the propagation delay and setup and hold measure-

ments. Figure 14 shows the waveforms for the three-state outputs measurement.

Circuit diagrams utilizing SMC products are included as a means of illustrating typical semiconductor applications: consequently complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of SMC or others. SMC reserves the right to make changes at any time in order to improve design and supply the best product possible.