# 8-BIT BUS INTERFACE FLIP-FLOPS WITH 3-STATE OUTPUTS

D2829, JANUARY 1986-REVISED MARCH 1988

01671)

- Functionally Equivalent to AMD AM29825 and AM29826

- Improved IOH Specifications

- Multiple Output Enables Allow Multiuser Control of the Interface

- **Outputs Have Undershoot Protection** Circuitry

- Power-Up High-Impedance State

- Package Options Include "Small-Outline" Packages, Plastic Chip Carriers, and Standard Plastic 300-mil DIPs

- **Buffered Control Inputs to Reduce DC Loading Effect**

- Dependable Texas Instruments Quality and Reliability

#### description

These 8-bit flip-flops feature three-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. They are particularly suitable for implementing multiuser registers, I/O ports, bidirectional bus drivers, and working registers.

With the clock enable (CLKEN) low, the eight Dtype edge-triggered flip-flops enter data on the low-to-high transitions of the clock. Taking CLKEN high will disable the clock buffer, thus latching the outputs. The 'ALS29825 has noninverting D inputs and the 'ALS29826 has inverting D inputs. Taking the CLR input low causes the eight Q outputs to go low independently of the clock.

Multiuser buffered output-control inputs (OC1, OC2, and OC3) can be used to place the eight outputs in either a normal logic state (high or low level) or a high-impedance state. The outputs are also in the high-impedance state during powerup and power-down conditions. The outputs remain in the high-impedance state while the device is powered-down. In the high-impedance state the outputs neither load nor drive the bus lines significantly. The high-impedance state and increased drive provide the capability to drive the bus lines in a bus-organized system without need

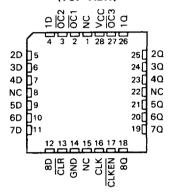

## SN74ALS29825 . . . DW OR NT PACKAGE (TOP VIEW)

## SN74ALS29825 . . . FN PACKAGE

(TOP VIEW)

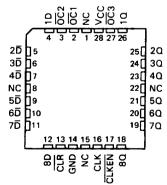

## SN74ALS29826 . . . DW OR NT PACKAGE

(TOP VIEW)

# SN74ALS29826 . . . FN PACKAGE

(TOP VIEW)

NC-No internal connection

INSTRUMENTS

## description (continued)

for interface or pull-up components. The output controls do not affect the internal operation of the flipflops. Old data can be retained or new data can be entered while the outputs are in the high-impedance state.

The SN74ALS29825 and SN74ALS29826 are characterized for operation from 0°C to 70°C.

### 'ALS29825 FUNCTION TABLE

|     | OUTPUT |       |     |   |              |

|-----|--------|-------|-----|---|--------------|

| OC* | CLR    | CLKEN | CLK | D | Q            |

| L   | L      | Х     | Х   | Х | L            |

| L   | Н      | L     | 1   | н | н            |

| L   | Н      | L     | 1   | L | L            |

| L   | н      | Н     | X   | x | $\sigma_{0}$ |

| Н   | X      | Х     | X   | x | z            |

$\overline{OC}^* = H$  if any of  $\overline{OC}1$ ,  $\overline{OC}2$ , or OC3 is high.

$\overline{OC}^* = L$  if all of  $\overline{OC}1$ ,  $\overline{OC}2$ , and OC3 are low

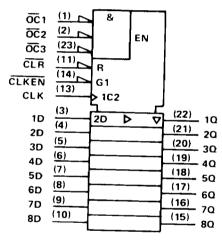

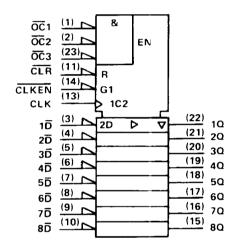

## logic symbol†

#### 'ALS29825

<sup>&</sup>lt;sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers are for DW and NT packages.

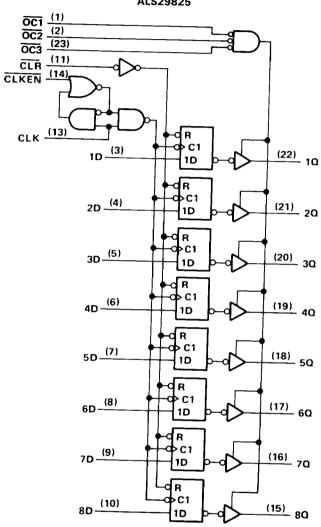

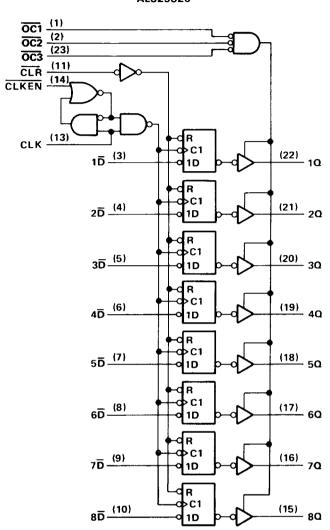

## logic diagram (positive logic)

#### 'ALS29825

Pin numbers are for DW and NT packages.

#### 'ALS29826 FUNCTION TABLE

|     | OUTPUT |       |     |   |            |

|-----|--------|-------|-----|---|------------|

| OC* | CLR    | CLKEN | CLK | D | Q          |

| L   | L      | Х     | Х   | Х | L          |

| L   | Н      | L     | 1   | н | L          |

| L   | Н      | L     | t   | L | Н          |

| L   | Н      | Н     | X   | x | $\sigma_0$ |

| Н   | Х      | Х     | Х   | х | z          |

$\overline{OC}^* = H \text{ if any of } \overline{OC1}, \overline{OC2}, \text{ or } OC3 \text{ is high.}$

$\overline{OC}^* = L$  if all of  $\overline{OC}1$ ,  $\overline{OC}2$ , and OC3 are low

### logic symbol†

#### 'ALS29826

<sup>&</sup>lt;sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers are for DW and NT packages.

#### logic diagram (positive logic)

#### 'ALS29826

Pin numbers are for DW and NT packages.

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC                          | . 7 | <i>,</i> v |

|----------------------------------------------|-----|------------|

| Input voltage                                | . 7 | <i>!</i> V |

| Voltage applied to a disabled 3-state output |     |            |

| Operating free-air temperature range         | 70  | °C         |

| Storage temperature range65°C to 1           | 150 | °C         |

# SN74ALS29825, SN74ALS29826 8-BIT BUS INTERFACE FLIP-FLOPS WITH 3-STATE OUTPUTS

### recommended operating conditions

|                               |                                |                   | MIN | NOM | MAX | MIN  | NOM | MAX  | UNIT |

|-------------------------------|--------------------------------|-------------------|-----|-----|-----|------|-----|------|------|

| Vcc                           | Supply voltage                 |                   |     | 5   |     | 4.75 | 5   | 5.25 | ٧    |

| VIH                           | High-level input voltage       |                   |     |     |     | 2    |     |      | V    |

| VIL                           | Low-level input voltage        |                   |     |     |     |      |     | 0.8  | ٧    |

| ЮН                            | High-level output current      |                   |     |     |     |      |     | - 24 | mA   |

| lOL                           | Low-level output current       |                   |     |     |     |      |     | 48   | mA   |

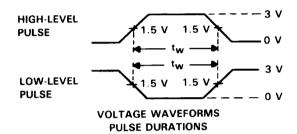

| t <sub>w</sub> Pulse duration |                                | CLR low           | 5   |     |     | 7    |     |      |      |

|                               | Pulse duration                 | CLK high          | 5   |     |     | 7    |     |      | ns   |

| ••                            |                                | CLK low           | 5   |     |     | 7    |     |      |      |

| -                             |                                | CLR inactive      | 5   |     |     | 7    |     |      |      |

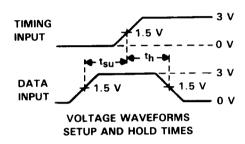

| t <sub>su</sub>               | Setup time before CLK1         | Data              | 2   |     |     | 4    |     |      | ns   |

| ou                            |                                | CLKEN high or low | 6   |     |     | 6    |     |      |      |

|                               |                                | Data              | 2   |     |     | 2    |     |      | ns   |

| th                            | Hold time, data after CLK1     | CLKEN             | 0   |     |     | 2    |     |      |      |

| TA                            | Operating free-air temperature | 9                 |     | 25  |     | 0    |     | 70   | °C   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise

| PARAMETER        |                           | TEST CONDITIONS          | MIN  | TYP <sup>†</sup> | MAX         | UNIT |

|------------------|---------------------------|--------------------------|------|------------------|-------------|------|

| VIK              | $V_{CC} = 4.5 V$          | I <sub>I</sub> = -18 mA  |      |                  | -1.2        | ٧    |

|                  | $V_{CC} = 4.5 \text{ V},$ | I <sub>OH</sub> = -15 mA | 2.4  | 3.3              |             | V    |

| ∨он              | $V_{CC} = 4.5 \text{ V},$ | I <sub>OH</sub> = -24 mA | 2    | 3.1              |             |      |

| V <sub>OL</sub>  | $V_{CC} = 4.5 \text{ V},$ | I <sub>OL</sub> = 48 mA  |      | 0.35             | 0.5         | V    |

| lozh             | $V_{CC} = 5.5 \text{ V},$ | V <sub>O</sub> = 2.4 V   |      |                  | 20          | μΑ   |

| IOZL             | V <sub>CC</sub> = 5.5 V,  | V <sub>O</sub> = 0.4 V   |      |                  | <b>- 20</b> | μΑ   |

| 1                | $V_{CC} = 5.5 \text{ V},$ | V <sub>I</sub> = 5.5 V   |      |                  | 0.1         | mA   |

| liн              | $V_{CC} = 5.5 V$          | V <sub>I</sub> = 2.7 V   |      |                  | 20          | μΑ   |

| III.             | $V_{CC} = 5.5 V$          | V <sub>1</sub> = 0.4 V   |      |                  | -0.2        | mA   |

| los <sup>‡</sup> | V <sub>CC</sub> = 5.5 V,  | V <sub>O</sub> = 0 V     | - 75 |                  | - 250       | mA   |

| lcc              | V <sub>CC</sub> = 5.5 V,  | Outputs open             |      | 70               | 100         | mA   |

$<sup>^{\</sup>dagger}$  All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.  $^{\ddagger}$  Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second.

# SN74ALS29825, SN74ALS29826 8-BIT BUS INTERFACE FLIP-FLOPS WITH 3-STATE OUTPUTS

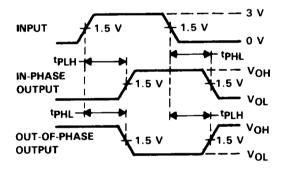

## switching characteristics

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST<br>CONDITIONS      |                       | C = 5 |     |     | N TO MAX, <sup>†</sup><br>N TO MAX <sup>†</sup> | UNIT |    |

|------------------|-----------------|----------------|-------------------------|-----------------------|-------|-----|-----|-------------------------------------------------|------|----|

|                  |                 | (0017017       | See Figure 1            | MIN                   | TYP   | MAX | MIN | MAX                                             |      |    |

| tPLH             |                 |                | C <sub>l</sub> = 50 pF  | 2                     |       | 8.5 | 2   | 10                                              |      |    |

| tPHL             | CLK             | Any Q          | CE = 50 pr              | 2                     |       | 8.5 | 2   | 10                                              |      |    |

| tPLH             | CLIK            |                | $C_1 = 300  pF$         |                       |       | 14  |     | 16                                              | ns   |    |

| tPHL             |                 |                | CL = 300 pr             |                       |       | 14  |     | 16                                              |      |    |

| tPHL             | CLR             | Any Q          | Cլ = 50 pF              |                       | 6     | 10  |     | 12                                              | ns   |    |

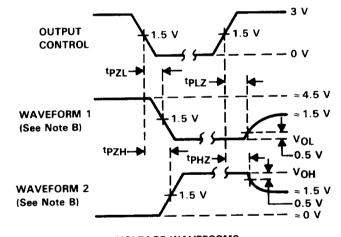

| <sup>t</sup> PZH |                 |                | C <sub>L</sub> = 50 pF  |                       | 11.5  | 12  |     | 14                                              |      |    |

| tPZL             | ОC              | Any Q          | С[ = 50 рг              |                       | 11    | 12  | L   | 14                                              | D.O. |    |

| <sup>t</sup> PZH | OC .            | Ally Q         | C <sub>L</sub> = 300 pF |                       |       | 17  |     | 20                                              | ns   |    |

| <sup>t</sup> PZL |                 |                | C[ = 300 pr             |                       |       | 21  |     | 23                                              |      |    |

| <sup>t</sup> PHZ |                 |                | C: - 50 p5              |                       |       | 11  |     | 14                                              |      |    |

| tPLZ             | <del>oc</del>   | Any O          | C <sub>L</sub> = 50 pF  |                       |       | 9   |     | 12                                              |      |    |

| t <sub>PHZ</sub> | UC .            | Any Q          | Any Q                   | C <sub>L</sub> = 5 pF |       | 5.2 | 8   |                                                 | 9    | ns |

| tPLZ             |                 |                | CL = 5 pr               |                       | 5.2   | 8   |     | 9                                               |      |    |

<sup>&</sup>lt;sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

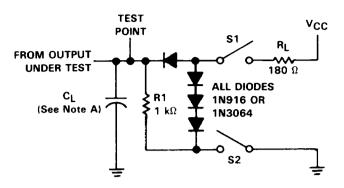

#### PARAMETER MEASUREMENT INFORMATION

SWITCH POSITION TABLE

| TEST             | S1     | S2     |

|------------------|--------|--------|

| tpLH             | Closed | Closed |

| tPHL             | Closed | Closed |

| <sup>t</sup> PZH | Open   | Closed |

| tPZL             | Closed | Open   |

| tPHZ             | Closed | Closed |

| tPLZ             | Closed | Closed |

LOAD CIRCUIT

VOLTAGE WAVEFORMS

PROPAGATION DELAY TIMES

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES, THREE-STATE OUTPUTS

NOTES: A.CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>0</sub> = 50  $\Omega$ , t<sub>f</sub>  $\leq$  2.5 ns, t<sub>f</sub>  $\leq$  2.5 ns.

FIGURE 1