# USB Charging Port Controller with Load Detection Supporting CDP, DCP Modes

#### DESCRIPTION

The MP5030D integrates a USB current-limit switch and charging port identification circuitry. The MP5030D achieves 3A of continuous output current over a wide input supply range.

The output of the USB switch is current-limit programmable. The MP5030D supports dedicated charging port (DCP) and charging downstream port (CDP) schemes for battery charging specification (BC1.2), divider mode, and 1.2V/1.2V mode without the need for external user interaction.

The MP5030D provides linear line drop compensation, load current detection, and status indication.

Full protection features include hiccup current limiting, input over-voltage protection (OVP), and thermal shutdown.

The MP5030D requires a minimal number of readily available, standard, external components to complete the USB switch and charging mode auto-detection solution. The MP5030D is available in a QFN-10 (1.5mmx2mm) package.

#### **FEATURES**

- Load Current Detection and Status Indication

- Up to 14V Operating Input Voltage Range

- Support DCP Schemes for BC1.2, Divider Mode, and 1.2V/1.2V Mode

- Supports CDP Mode Handshaking

- Line Drop Compensation

- Programmable High-Accuracy Current Limit

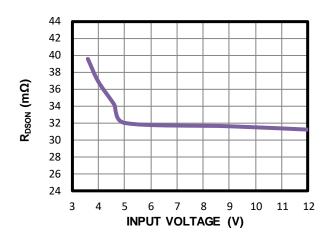

- 32mΩ Low R<sub>DS(ON)</sub> Power MOSFET

- Input Over-Voltage Shutdown Protection

- Compatible with Buck, Boost, and AC/DC Converters

- Available in a QFN-10 (1.5mmx2mm) Package

#### **APPLICATIONS**

- USB Power Supplies

- AC/DC Wall Adapter with USB Ports

- Cigarette Lighter Adapters

- Power Bank

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

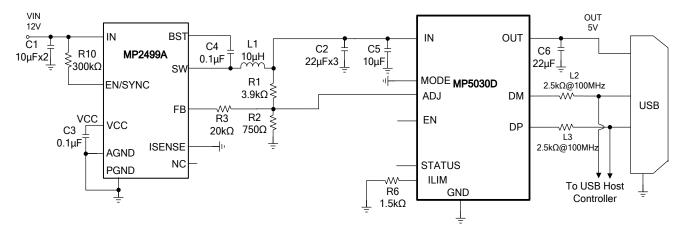

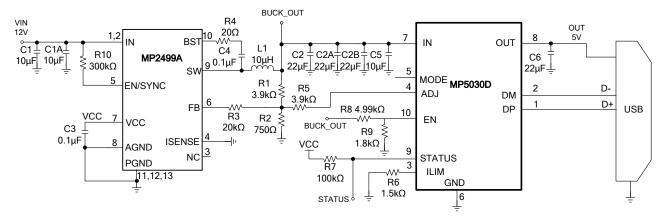

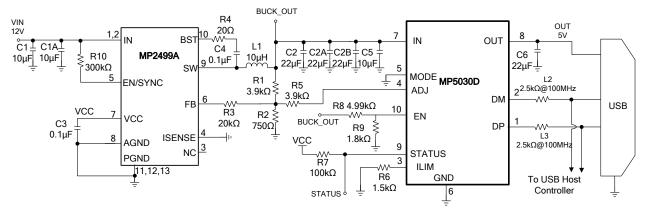

#### TYPICAL APPLICATION

CDP Mode Set-Up for USB2.0 Application

# **ORDERING INFORMATION**

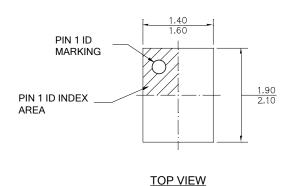

| Part Number* | Package            | Top Marking |

|--------------|--------------------|-------------|

| MP5030DGQH   | QFN-10 (1.5mmx2mm) | See Below   |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP5030DGQH-Z).

### **TOP MARKING**

HQ

LL

HQ: Product code of MP5030DGQH

LL: Lot number

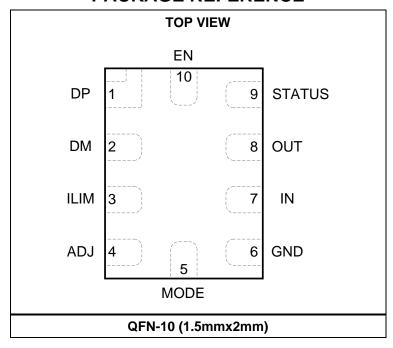

### **PACKAGE REFERENCE**

#### PIN FUNCTIONS

| Package<br>Pin # | Name   | Description                                                                                                                                                                                                     |  |

|------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                | DP     | <b>D+</b> data line to the USB connector. DP is the input/output pin used fo handshaking with portable devices.                                                                                                 |  |

| 2                | DM     | <b>D- data line to USB connector.</b> DM is the input/output pin used for handshaking with portable devices.                                                                                                    |  |

| 3                | ILIM   | <b>Current-limit level set.</b> Place a resistor between ILIM and GND to achieve a high-accuracy current limit.                                                                                                 |  |

| 4                | ADJ    | <b>Output voltage adjustment.</b> ADJ sinks a current from the upstream DC/D converter's FB pin to ground to regulate the DC/DC converter's output voltage. AE also supports a line drop compensation function. |  |

| 5                | MODE   | <b>USB mode control.</b> Float MODE to operate the USB in DCP mode. Pull MODE low to operate the USB in CDP mode. MODE has a $1M\Omega$ pull-up resistor to an internal +1.2V source.                           |  |

| 6                | GND    | Ground.                                                                                                                                                                                                         |  |

| 7                | IN     | Supply voltage.                                                                                                                                                                                                 |  |

| 8                | OUT    | Output of the USB current-limit switch.                                                                                                                                                                         |  |

| 9                | STATUS | <b>Open-drain output.</b> Pull STATUS low when the load current is higher than the typical 90mA threshold. STATUS is an open drain during no-load conditions.                                                   |  |

| 10               | EN     | <b>Enable pin for the IC.</b> EN has an internal auto pull-up current to VCC. Float EN or apply a logic high voltage to EN to enable the IC. Pull EN to logic low to disable the IC.                            |  |

### **ABSOLUTE MAXIMUM RATINGS (1)**

| Supply voltage (V <sub>IN</sub> )  | 0.3V to +16V                               |

|------------------------------------|--------------------------------------------|

| Output voltage (V <sub>OUT</sub> ) |                                            |

| All other pins                     | 0.3V to +6V                                |

| Junction temperature               | 150°C                                      |

| Lead temperature                   | 260°C                                      |

| Continuous power dissipati         | on (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                                    | 2.23W                                      |

| Storage temperature                |                                            |

# Recommended Operating Conditions (3)

| recommended operating                     | Conditions        |

|-------------------------------------------|-------------------|

| Supply voltage (V <sub>IN</sub> )         | 5V <sup>(4)</sup> |

| Output voltage (V <sub>OUT</sub> )        |                   |

| Output current (I <sub>OUT</sub> )        | Up to 3A          |

| Operating junction temp (T <sub>1</sub> ) | -40°C to +125°C   |

| Thermal Resistance      | $oldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}$ JC |      |

|-------------------------|-------------------------|--------------------------|------|

| QFN-10 (1.5mmx2mm)      |                         |                          |      |

| EV5030D-QH-00A (5)      | 56                      | 18                       | °C/W |

| JESD51-7 <sup>(6)</sup> | 130                     | 25                       | °C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $\mathsf{T}_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $\mathsf{T}_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $\mathsf{P}_D$  (MAX) = ( $\mathsf{T}_J$  (MAX)- $\mathsf{T}_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage. Measured on EV5030D-QH-00A, 2-layer PCB, 4.4cmx2.9cm, 2Oz copper.

- The device is not guaranteed to function outside of its operating conditions.

- 4) For lower  $V_{\text{IN}}$  applications, refer to the Operation section on page 12.

- Measured on EV5030D-QH-00A, 4.4cmx2.9cm, 2-layer PCB, 2Oz copper.

- 6) The value of θ<sub>JA</sub> given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 5V$ ,  $T_J = -40$ °C to 125°C (7), typical value tested at  $T_J = +25$ °C unless otherwise noted.

| Parameter                                                     | Symbol                   | Condition                                                                                                | Min  | Тур  | Max  | Units |

|---------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>IN</sub> under-voltage lockout rising threshold        | VIN_UVLO1                | ADJ begins working                                                                                       | 2.7  | 3    | 3.3  | V     |

| UVLO hysteresis                                               | Vuvlohys1                |                                                                                                          |      | 880  |      | mV    |

| Second V <sub>IN</sub> under-voltage lockout rising threshold | VIN_UVLO2                | Power MOSFET turns on                                                                                    | 3.7  | 3.9  | 4.1  | V     |

| Second UVLO hysteresis                                        | Vuvlohys2                |                                                                                                          |      | 500  |      | mV    |

| EN rising threshold                                           | V <sub>EN_R</sub>        |                                                                                                          | 1.15 | 1.21 | 1.27 | V     |

| EN hysteresis                                                 | V <sub>EN_HYS</sub>      |                                                                                                          |      | 200  |      | mV    |

| EN auto pull-up current                                       | I <sub>EN_UP</sub>       |                                                                                                          | 11   | 16   | 21   | μA    |

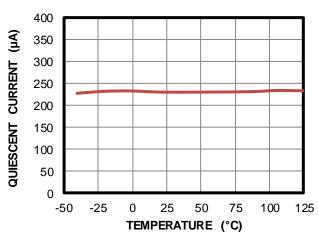

| Supply current                                                | ΙQ                       | V <sub>IN</sub> = 5V, no load                                                                            |      | 250  | 320  | μA    |

| Shutdown current                                              | $I_{Q\_STD}$             |                                                                                                          |      | 40   | 60   | μA    |

| USB Power MOSFET                                              |                          |                                                                                                          |      |      |      |       |

| On resistance                                                 | RDSON                    | $V_{IN} = 5V$                                                                                            |      | 32   | 50   | mΩ    |

| Input discharge resistance                                    | Rdis                     | Turn-on during V <sub>IN</sub> OVP or high-<br>to-low voltage change period                              |      | 72   |      | Ω     |

| Soft-start time                                               | Tss                      | V <sub>IN</sub> = 5V, no load, 10 - 90%                                                                  |      | 290  |      | μs    |

| Current Limit                                                 |                          |                                                                                                          |      | •    |      |       |

|                                                               | Ішміт                    | $R_{ILIM} = 1.5k\Omega$ , $V_{IN} = 5V$ , $V_{OUT}$ drops 10%, $T_J = +25^{\circ}C$                      | 3.13 | 3.35 | 3.57 | А     |

| USB current limit                                             | LIMIT                    | $R_{ILIM} = 1.5k\Omega$ , $V_{IN} = 5V$ , $V_{OUT}$ drops 10%, $T_{J} = -40^{\circ}C$ to $+125^{\circ}C$ | 3    | 3.35 | 3.7  | А     |

| Load current detect rising                                    | ILOADDEC_R               | STATUS pulls low, T <sub>J</sub> = +25°C                                                                 | 30   | 90   | 140  | mA    |

| Load current detect falling                                   | ILOADDEC_F               | STATUS open drain, T <sub>J</sub> = +25°C                                                                | 20   | 80   | 130  | mA    |

| STATUS                                                        | •                        |                                                                                                          |      |      |      |       |

| STATUS pin leakage                                            | Istatus                  | Pull up to 5V                                                                                            |      |      | 1    | μA    |

| STATUS output                                                 | Vstatus                  | Sink 1mA                                                                                                 |      |      | 250  | mV    |

| STATUS pull-low deglitch                                      | Tstatus_Low              |                                                                                                          | 100  | 200  | 300  | ms    |

| Output Voltage Control                                        |                          |                                                                                                          |      |      |      |       |

| Default                                                       | V <sub>IN_Def1</sub>     | $I_{OUT} = 0A, T_J = +25^{\circ}C$                                                                       | -1%  | 5.0  | +1%  | V     |

| Default V <sub>IN</sub>                                       | V <sub>IN_Def2</sub>     | $I_{OUT} = 0A$ , $T_{J} = -40^{\circ}C$ to $+125^{\circ}C$                                               | -2%  | 5.0  | +2%  | V     |

| V <sub>ADJ</sub> sink current capability                      | Isink                    | V <sub>FB</sub> = 800mV                                                                                  | 500  |      |      | μA    |

| Line drop compensation                                        | V <sub>IN_5_C</sub>      | I <sub>OUT</sub> = 2.4A, only 5V <sub>IN</sub> active                                                    |      | 240  | 400  | mV    |

| Protection                                                    |                          |                                                                                                          |      | •    |      |       |

| V <sub>IN</sub> OVP threshold                                 | V <sub>OV_TH</sub>       | V <sub>IN</sub> rising edge, V <sub>IN</sub> = 5V                                                        | 110  | 115  | 120  | %     |

| V <sub>IN</sub> OVP recovery threshold                        | V <sub>OV_Recovery</sub> | Reset mode to 5V default                                                                                 | 5.25 | 5.4  | 5.55 | V     |

| OVP deglitch time (8)                                         | T <sub>OVP_DE</sub>      |                                                                                                          |      | 10   |      | μs    |

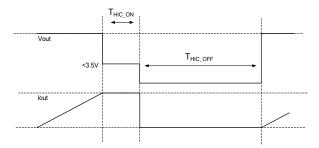

| OCP on time of hiccup                                         | THIC_ON                  |                                                                                                          |      | 2    |      | ms    |

| OCP off time of hiccup                                        | T <sub>HIC_OFF</sub>     |                                                                                                          |      | 2    |      | s     |

| <u> </u>                                                      | _                        |                                                                                                          |      | 150  |      | °C    |

| Shutdown temperature (8)                                      | T <sub>STD</sub>         |                                                                                                          |      | 130  |      |       |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 5V$ ,  $T_J = -40$ °C to 125°C (7), typical value tested at  $T_J = +25$ °C, unless otherwise noted.

| Parameter                                                             | Symbol                     | Condition                                                             | Min   | Тур  | Max  | Units |

|-----------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------|-------|------|------|-------|

| BC 1.2 DCP Mode                                                       |                            |                                                                       |       |      |      |       |

| DP/DM short resistance                                                | R <sub>DP/DM_Short</sub>   | V <sub>DP</sub> = 0.8V, I <sub>DM</sub> = 1mA, T <sub>J</sub> = +25°C |       |      | 50   | Ω     |

| 1.2V/1.2V Mode                                                        |                            |                                                                       |       |      |      |       |

| DP/DM output voltage                                                  | V <sub>DP/DM_1.2V</sub>    |                                                                       | 1.1   | 1.2  | 1.3  | V     |

| DP/DM output impedance                                                | R <sub>DP/DM_1.2V</sub>    |                                                                       |       | 300  |      | kΩ    |

| Divider Mode                                                          |                            |                                                                       |       |      |      |       |

| DP/DM output voltage                                                  | V <sub>DP/DM</sub>         | $V_{IN} = V_{OUT} = 5V$                                               | 2.5   | 2.7  | 2.85 | V     |

| DP/DM output impendence                                               | R <sub>DP/DM</sub>         |                                                                       | 18    | 22   | 28   | kΩ    |

| CDP Mode                                                              | •                          |                                                                       |       |      |      |       |

| MODE pin logic low voltage                                            | V <sub>MODE_L</sub>        | To enable CDP mode                                                    |       |      | 0.5  | V     |

| DM CDP output voltage                                                 | V <sub>DM_SRC</sub>        | VDP = 0.6V                                                            | 0.5   | 0.6  | 0.7  | V     |

| DP rising lower window threshold for V <sub>DM_SRC</sub> activation   | Vdat_re                    |                                                                       | 0.3   | 0.35 | 0.4  | V     |

| DP rising lower window threshold hysteresis for VDM_SRC activation    | VDAT_RE_HYS                |                                                                       |       | 50   |      | mV    |

| DP rising upper window threshold for V <sub>DM_SRC</sub> deactivation | V <sub>LGC_SRC</sub>       |                                                                       | 0.8   | 0.9  | 1    | V     |

| DP rising upper window threshold hysteresis for VDM_SRC de-activation | VLGC_SRC_HYS               |                                                                       |       | 50   |      | mV    |

| VDM_SRC on/off deglitch time                                          | V <sub>DM_SRC_Deglit</sub> |                                                                       | 3     | 5    | 7.5  | ms    |

| RDP down, RDM down                                                    | R <sub>DP/DM_Down</sub>    | Only enabled when V <sub>DP</sub> > 0.35V/5µs                         | 14.25 | 19.5 | 24.8 | kΩ    |

| DP, DM to ground leakage                                              | IDP/DM_LKG                 | $V_{DM} = 1V$ , $V_{DP} = 1V$                                         |       |      | 1    | μA    |

#### NOTES:

<sup>7)</sup> Not tested in production, guaranteed by over-temperature correlation.

<sup>8)</sup> Guaranteed by engineering sample characterization.

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 5V$ ,  $V_{OUT} = 5V$ ,  $R_{ILIM} = 1.5k\Omega$ ,  $T_A = 25$ °C, unless otherwise noted.

#### R<sub>DS(ON)</sub> vs. Input Voltage

#### **Quiescent Current vs. Temperature**

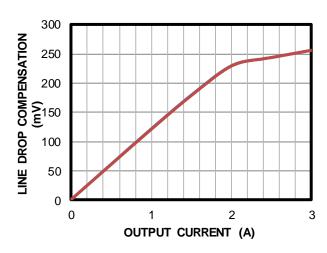

### **Line Drop Compensation**

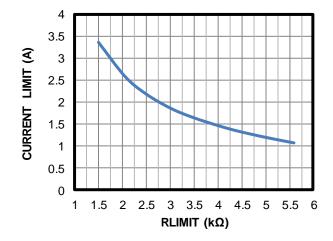

Current Limit vs. RLIMIT

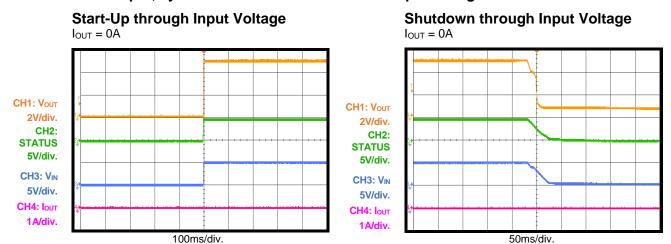

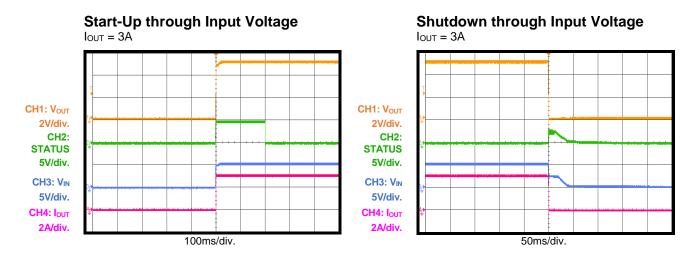

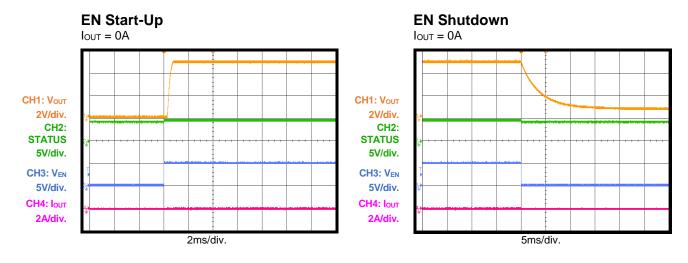

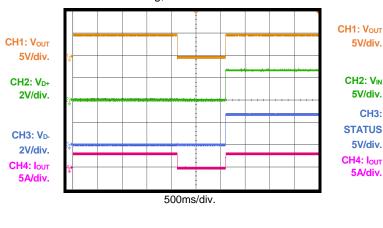

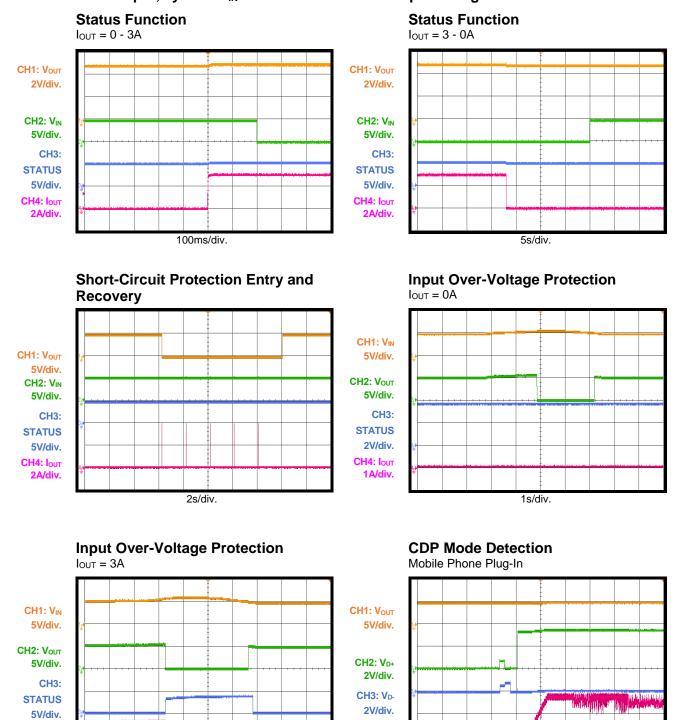

$V_{IN}$  = 5V,  $V_{OUT}$  = 5V,  $R_{ILIM}$  = 1.5k $\Omega$ ,  $T_A$  = 25°C, unless otherwise noted. Connect the MP5030D input to the MP2499A output, system  $V_{IN}$  = 12V is the MP2499A input voltage.

$V_{IN} = 5V$ ,  $V_{OUT} = 5V$ ,  $R_{ILIM} = 1.5k\Omega$ ,  $T_A = 25$ °C, unless otherwise noted. Connect the MP5030D input to the MP2499A output, system  $V_{IN} = 12V$  is the MP2499A input voltage.

CH1: Vout

5V/div. CH2: V<sub>IN</sub>

5V/div.

**CH3:**

**STATUS**

5V/div. CH4: lout

5A/div.

5V/div.

CH2: VIN

5V/div.

5V/div.

5A/div.

CH4: I<sub>OUT</sub>

**CH3: STATUS**

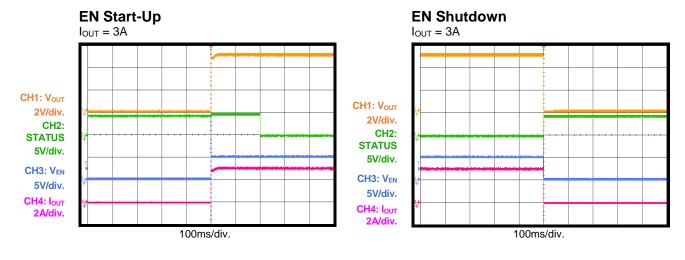

# **MODE Changes from Float to GND**

D+ and D- floating, IouT = 3A

# **MODE Changes from Float to GND**

D+ and D- floating, IouT = 3A

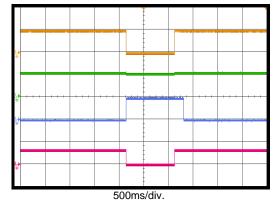

#### **MODE Changes from GND to Float**

D+ and D- floating, IouT = 3A

#### **MODE Changes from GND to Float**

D+ and D- floating, IouT = 3A

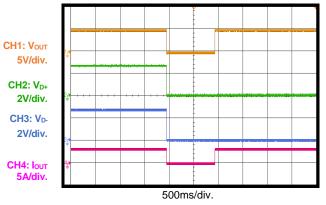

$V_{IN}$  = 5V,  $V_{OUT}$  = 5V,  $R_{ILIM}$  = 1.5k $\Omega$ ,  $T_A$  = 25°C, unless otherwise noted. Connect the MP5030D input to the MP2499A output, system  $V_{IN}$  = 12V is the MP2499A input voltage.

CH4: I<sub>OUT</sub>

5A/div.

1s/div.

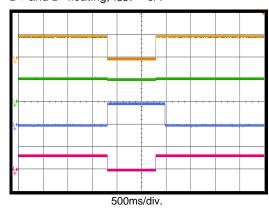

CH4: Iout

1A/div.

200ms/div.

$V_{IN}$  = 5V,  $V_{OUT}$  = 5V,  $R_{ILIM}$  = 1.5k $\Omega$ ,  $T_A$  = 25°C, unless otherwise noted. Connect the MP5030D input to the MP2499A output, system  $V_{IN}$  = 12V is the MP2499A input voltage.

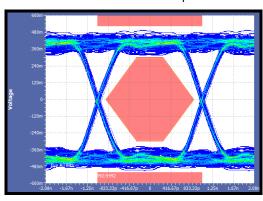

### **Eye Pattern Test**

Recommended CDP Mode Set-Up

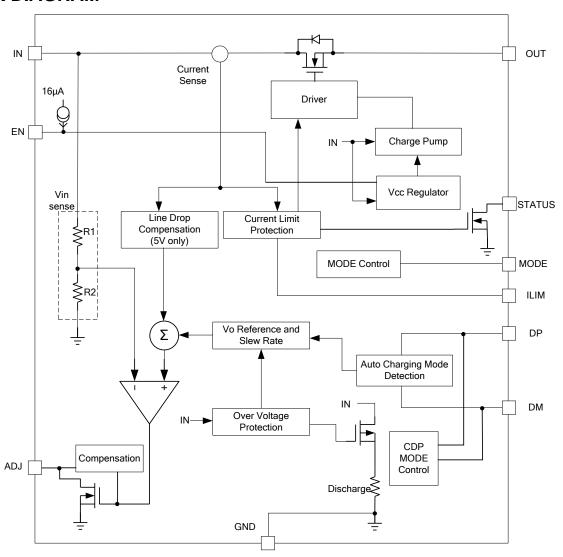

# **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

#### **OPERATION**

The MP5030D integrates a USB current-limit switch and charging port identification circuitry. The MP5030D achieves 3A of continuous output current over a wide input supply range.

The output of the USB switch is current-limited with an adjustable current-limit threshold. The MP5030D supports DCP and CDP schemes for battery charging specification (BC1.2), divider mode, and 1.2V/1.2V mode without the need for external user interaction.

The MP5030D provides line drop compensation, load current detection, and status indication. Full protection features include hiccup current limiting, input overvoltage protection (OVP), and thermal shutdown.

#### **Operation Supply Voltage**

The MP5030D has a two-stage input voltage threshold: the first threshold is around 3V, and the second threshold is the under-voltage lockout (UVLO) of the power MOSFET. When  $V_{\rm IN}$  is higher than the first threshold, the MP5030D's ADJ block beings working. This sinks a current to adjust the upstream regulator's output to an accurate 5V. Afterward, the MP5030D enters a fully working state.

#### **Under Voltage Lockout (UVLO)**

UVLO protects the chip from operating at an insufficient supply voltage. The MP5030D's second UVLO comparator monitors the input voltage. Once the input voltage is higher than the second UVLO threshold, the power MOSFET starts to turn-on after a fixed delay with a controlled slew rate.

#### Internal Soft Start (SS)

The internal soft start prevents the output voltage from overshooting during start-up and prevents inrush current at the input.

#### **MODE Selection**

The MP5030D supports DCP and CDP mode through the MODE pin control. Pull MODE low to set the USB in CDP mode. Float MODE to set the USB in DCP mode (see Table 1).

The MP5030D supports dynamic changing USB charging modes. For example, when pulling MODE from floating to logic low, V<sub>BUS</sub> turns off

with an output discharge. Afterward,  $V_{\text{BUS}}$  restarts and enters CDP mode.

In DCP mode, the MP5030D can provide power for the USB devices with protocol auto-detection. The MP5030D supports the following charging schemes:

- USB battery charging specification BC1.2/Chinese Telecommunications Industry Standard YD/T 1591-2009

- Divider mode

- 1.2V/1.2V mode

In CDP mode, the MP5030D performs CDP handshaking with a portable device. The MP5030D follows the BC1.2 CDP handshaking specification.

V<sub>BUS</sub> is always around 5V with current limit and line drop compensation.

**Table 1: MODE Selection**

| MODE Pin Status | Supported Charge Mode                     |  |  |

|-----------------|-------------------------------------------|--|--|

| Float           | DCP mode, divider mode,<br>1.2V/1.2V mode |  |  |

| Logic low       | CDP mode                                  |  |  |

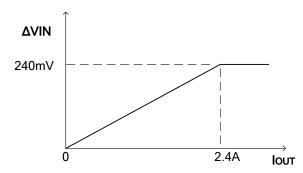

# **Line Drop Compensation**

The MP5030D can compensate for an output voltage drop, such as high impedance caused by a long trace, to maintain a fairly constant 5V load-side voltage. Line drop compensation is achieved through ADJ. The MP5030D increases the input voltage by 240mV at an output of 2.4A (see Figure 2).

Figure 2: Line Drop Compensation

V<sub>ADJ</sub> sinks a controlled current slowly. The line drop compensation amplitude linearly increases as the load current increases.

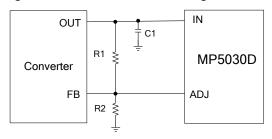

In no-load condition, if the input voltage is lower than 5V (typically), ADJ sinks a current to regulate the upstream regulator's output voltage to 5V. If the input voltage is higher than 5V (typically), MP5030D stops regulating the input voltage. For a quick load transient response, ADJ should always be working while the IC is on. Configure the R1/R2 default output voltage to be <5V. It is recommend to set the buck output as 4.9V, so R1 =  $3.9k\Omega$  and R2 =  $0.75k\Omega$ .

Figure 3 shows the typical ADJ usage. The ADJ sink current capability is 500μA. ADJ requires the feedback current through R1 to be less than 500μA. Calculate R1 with Equation (1):

$$R1(k\Omega) > \frac{\Delta V(V)}{0.5}$$

(1)

Where  $\Delta V$  is the maximum line drop compensation value. To this, add the differential voltage between 5V and the voltage buck set.

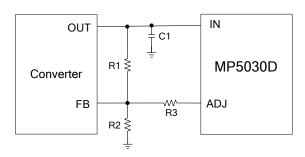

Figure 3: ADJ Configure

#### Input Over-Voltage and Discharge

To protect the downstream device from an over-voltage condition, the MP5030D provides an input over-voltage protection (OVP) shutdown function.

An accurate and fast comparator monitors the over-voltage condition of the input. If the input voltage rises above the threshold, the gate of the internal MOSFET is pulled low quickly and the power MOSFET is shut down. The input-to-ground discharge path is active at this time. When the input voltage falls below 5.4V (typically), the MP5030D exits OVP mode.

#### **Over-Current Protection (OCP)**

The MP5030D provides a constant current limit. The current-limit threshold is adjustable via an external resistor.

Once the device reaches its current limit threshold, the internal circuit regulates the gate voltage to keep the power MOSFET current

constant.

For the current limit setting, refer to the Current Limit vs.  $R_{\text{Limit}}$  curve on page 6. If the set current limit is less than 500mA, the current limit accuracy worsens slightly. An external  $R_{\text{Limit}}$  resistor can set the current limit threshold. If an over-current (OC) condition occurs but  $V_{\text{OUT}} > 3.5V$ , the MP5030D works in constant-current (CC) limit mode without hiccup. If OCP is triggered and  $V_{\text{OUT}} < 3.5V$  for 2ms, the MP5030D enters hiccup mode. In hiccup mode, the MP5030D turns off the power MOSFET (see Figure 4).

**Figure 4: Over-Current Protection**

#### **Short-Circuit Protection (SCP)**

If the load current increases rapidly due to a short circuit, the current may greatly exceed the current-limit threshold before the control loop can respond. If the current reaches the internal secondary current-limit level (about 6A), a fast turn-off circuit activates to turn off the power MOSFET. This limits the peak current through the switch to limit the input voltage drop. The fast-off response time value is 700ns, typically. If the fast-off works, the power MOSFET remains off for 80µs. Afterward, the power MOSFET turns on again if the part is still in a short-circuit condition. The MP5030D treats this as an over-current condition again to enter hiccup or thermal shutdown. After the shortcircuit condition is removed, the MP5030D recovers automatically.

#### Thermal Shutdown

Thermal shutdown prevents the chip from operating at exceedingly high temperatures. When the silicon die temperature exceeds 150°C, the entire chip shuts down. When the temperature falls below its lower threshold (typically 125°C), the chip is enabled again.

# Load Current Detection and Status Indication

STATUS is an open-drain output. When the load current is larger than 90mA (typically) for longer than 200ms, STATUS is pulled low by a  $<100\Omega$  resistor. When the load current is smaller than 80mA (typically) for longer than 15s, STATUS becomes an open-drain output.

During the first power-up, STATUS is an opendrain output.

During the MODE transition,  $V_{\text{BUS}}$  restarts with a fixed delay time, and STATUS resets to an open-drain output.

If a fault condition occurs (OTP, OCP, SCP, OVP), STATUS resets to an open-drain output.

#### APPLICATION INFORMATION

### **Selecting the Input Capacitor**

Use low ESR capacitors for the best performance. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. A 22µF ceramic capacitor is recommended for most applications. When selecting an input capacitor, be sure to consider the pre-stage converter stability as well. The input capacitor of the MP5030D will be the output capacitor of the converter. Ensure that the converter is stable with additional output capacitors.

# **Selecting the Output Capacitor**

Use low ESR capacitors for the best performance. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. A 22µF ceramic capacitor is recommended for most applications.

#### Selecting the ILIM Resistor

The current-limit value can be set by the ILIM resistor. For the programmable current limit, refer to the Current Limit vs. R<sub>Limit</sub> curve on page 6.

The current-limit threshold is recommended to be 10% higher than the maximum load current. For example, if the system's full load is 3A, set the current limit to 3.3A.

#### Selecting the V<sub>ADJ</sub> Resistor

ADJ has an internal, controlled current sink. Line drop compensation is achieved through ADJ. The ADJ sink current capability is  $500\mu A$ . The pre-side converter should be a  $k\Omega$  level feedback resistor. The current through the high-side feedback resistor should be less than  $500\mu A$  (see Figure 5).

There is another  $V_{ADJ}$  configuration to limit the maximum output voltage by inserting R3 between FB and  $V_{ADJ}$ . With R3, the maximum output voltage can be limited by Equation (2):

$$V_{\text{OUT\_MAX}}(V) = \frac{R_1 + R_2 / / R_3}{R_2 / / R_3} \times V_{FB}(V)$$

(2)

Figure 5: VADJ-Set Maximum Vout

#### Other Considerations

The upstream DC/DC converter should have a higher current-limit threshold than the MP5030D's current limit.

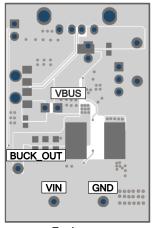

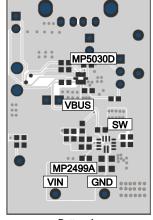

#### PCB Layout Guidelines (9)

Efficient PCB layout is critical for stable operation and thermal dissipation. For the best results, refer to Figure 6 and follow the guidelines below.

- Use short, direct and wide traces to connect the IC's IN and OUT pins.

- 2. Add vias under the IC.

- 3. Route the OUT trace on both PCB layers.

- Place a ceramic input decoupling capacitor as close to the IN and GND pins as possible to improve EMI performance.

- Keep the V<sub>ADJ</sub> trace to the pre-side converter FB pin as short as possible to avoid noise injection.

#### NOTE

9) The recommended layout is based on the Typical Application Circuit shown in Figure 7.

Top Layer

**Bottom Layer**

Figure 6: Recommended Layout

# TYPICAL APPLICATION CIRCUITS

Figure 7: MP5030D + MP2499A for CLA Car Charger, DCP Mode (10)

Figure 8: MP5030D + MP2499A for CDP Mode (10)

#### NOTE:

10) Pull STATUS up to the MP2499A's VCC pin through a 10 -  $100k\Omega$  resistor.

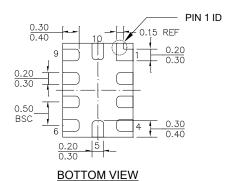

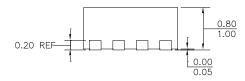

# **PACKAGE INFORMATION**

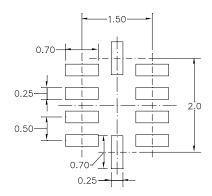

# QFN-10 (1.5mmx2mm)

SIDE VIEW

**RECOMMENDED LAND PATTERN**

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX.

- 3) JEDEC REFERENCE IS MO-220.

- 4) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.