T-46-19-07

FINAL

COM'L: -12/15/20

MIL: -20

# **L** Ivanced

# MACH110-12/15/20

## **High-Density EE CMOS Programmable Logic**

Advanced Micro Devices

## DISTINCTIVE CHARACTERISTICS

- **44** Pins

- 32 Macrocells

- 12 ns tpp Commercial 20 ns tpp Military

- 66.7 MHz f<sub>MAX</sub> Commercial 40 MHz f<sub>MAX</sub> Military

- 38 Inputs

- 32 Outputs

- 32 Flip-flops; 2 clock choices

- 2 "PAL22V16" Blocks

- Pin-compatible with MACH210, MACH215

## **GENERAL DESCRIPTION**

The MACH110 is a member of AMD's high-performance EE CMOS MACH 1 family. This device has approximately three times the logic macrocell capability of the popular PAL22V10 with no loss of speed.

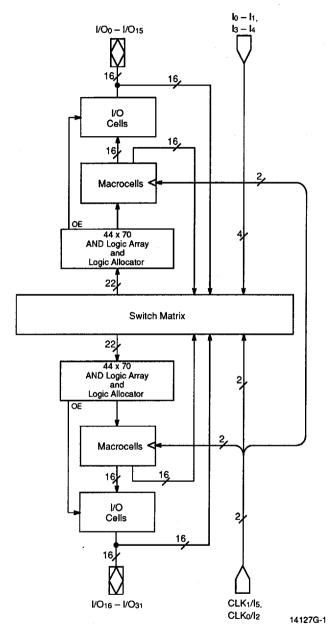

The MACH110 consists of two PAL blocks interconnected by a programmable switch matrix. The two PAL blocks are essentially "PAL22V16" structures complete with product-term arrays and programmable macrocells. The switch matrix connects the PAL blocks to each other and to all input pins, providing a high degree of connectivity between the fully-connected PAL blocks. This allows designs to be placed and routed efficiently.

The MACH110 macrocell provides either registered or combinatorial outputs with programmable polarity. If a registered configuration is chosen, the register can be configured as D-type or T-type to help reduce the number of product terms. The register type decision can be made by the designer or by the software. All macrocells can be connected to an I/O cell. If a buried macrocell is desired, the internal feedback path from the macrocell can be used, which frees up the I/O pin for use as an input.

## **BLOCK DIAGRAM**

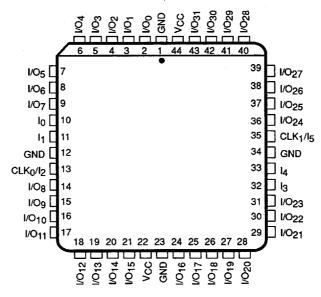

# CONNECTION DIAGRAM Top View

## PLCC/CQFP

14127G-2

Note: Pin-compatible with MACH210, MACH215.

### **PIN DESIGNATIONS**

CLK/I = Clock or Input

GND = Ground

I = Input

I/O = Input/Output

Vcc = Supply Voltage

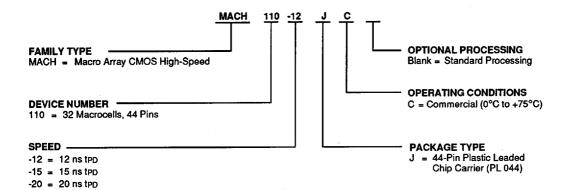

## **ORDERING INFORMATION**

#### **Commercial Products**

AMD programmable logic products for commercial applications are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |    |  |

|--------------------|----|--|

| MACH110-12         |    |  |

| MACH110-15         | JC |  |

| MACH110-20         |    |  |

#### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

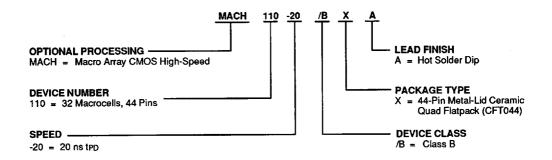

## **ORDERING INFORMATION**

#### **APL Products**

AMD programmable logic products for Aerospace and Defense applications are available with several ordering options. APL (Approved Product List) products are fully compliant with MIL-STD-883 requirements. The order number (Valid Combination) is formed by a combination of:

Valid Combinations

MACH110-20/BXA

#### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

#### **FUNCTIONAL DESCRIPTION**

The MACH110 consists of two PAL blocks connected by a switch matrix. There are 32 I/O pins and 6 dedicated input pins feeding the switch matrix. These signals are distributed to the two PAL blocks for efficient design implementation. There are two clock pins that can also be used as dedicated inputs.

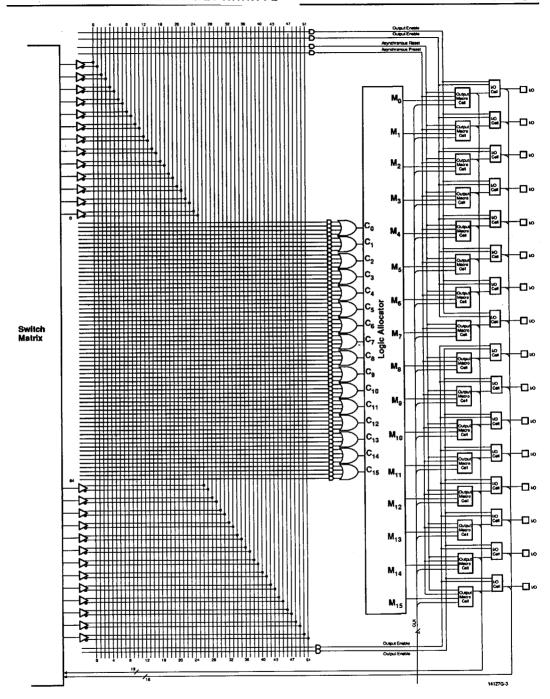

### The PAL Blocks

Each PAL block in the MACH110 (Figure 8) contains a 64-product-term logic array, a logic allocator, 16 macrocells and 16 I/O cells. The switch matrix feeds each PAL block with 22 inputs. This makes the PAL block look effectively like an independent "PAL22V16".

There are four additional output enable product terms in each PAL block. For purposes of output enable, the 16 I/O cells are divided into 2 banks of 8 macrocells. Each bank is allocated two of the output enable product terms.

An asynchronous reset product term and an asynchronous preset product term are provided for flip-flop initialization. All flip-flops within the PAL block are initialized together.

#### The Switch Matrix

The MACH110 switch matrix is fed by the inputs and feedback signals from the PAL blocks. Each PAL block provides 16 internal feedback signals and 16 I/O feedback signals. The switch matrix distributes these signals back to the PAL blocks in an efficient manner that also provides for high performance. The design software automatically configures the switch matrix when fitting a design into the device.

## The Product-Term Array

The MACH110 product-term array consists of 64 product terms for logic use, and 6 special-purpose product terms. Four of the special-purpose product terms provide programmable output enable, one provides asynchronous reset, and one provides asynchronous preset. Two of the output enable product terms are used for the first eight I/O cells; the other two control the last eight macrocells.

## The Logic Allocator

The logic allocator in the MACH110 takes the 64 logic product terms and allocates them to the 16 macrocells as needed. Each macrocell can be driven by up to 12 product terms. The design software automatically configures the logic allocator when fitting the design into the device.

Table 5 illustrates which product term clusters are available to each macrocell within a PAL block. Refer to Figure 8 for cluster and macrocell numbers.

Table 5. Logic Allocation

| Output Macrocell | Available<br>Clusters                            |

|------------------|--------------------------------------------------|

| Mo               | C <sub>0</sub> , C <sub>1</sub>                  |

| M <sub>1</sub>   | C <sub>0</sub> , C <sub>1</sub> , C <sub>2</sub> |

| M <sub>2</sub>   | C <sub>1</sub> , C <sub>2</sub> , C <sub>3</sub> |

| M <sub>3</sub>   | C <sub>2</sub> , C <sub>3</sub> , C <sub>4</sub> |

| M4               | C3, C4, C5                                       |

| M5               | C4, C5, C6                                       |

| М <sub>6</sub>   | C5, C6, C7                                       |

| М7               | C6, C7                                           |

| Мв               | C8, C9                                           |

| М9               | C8, C9, C10                                      |

| M10              | C9, C10, C11                                     |

| M11              | C10, C11, C12                                    |

| M <sub>12</sub>  | C11, C12, C13                                    |

| M <sub>13</sub>  | C12, C13, C14                                    |

| M <sub>14</sub>  | C13, C14, C15                                    |

| M <sub>15</sub>  | C14, C15                                         |

#### The Macrocell

The MACH110 macrocells can be configured as either registered or combinatorial, with programmable polarity. The macrocell provides internal feedback whether configured as registered or combinatorial. The flip-flops can be configured as D-type or T-type, allowing for product-term optimization.

The flip-flops can individually select one of two clock pins, which are also available as data inputs. The registers are clocked on the LOW-to-HIGH transition of the clock signal. The flip-flops can also be asynchronously initialized with the common asynchronous reset and preset product terms.

#### The I/O Cell

The I/O cell in the MACH110 consists of a three-state output buffer. The three-state buffer can be configured in one of three ways: always enabled, always disabled, or controlled by a product term. If product term control is chosen, one of two product terms may be used to provide the control. The two product terms that are available are common to eight I/O cells. Within each PAL block, two product terms are available for selection by the first eight three-state outputs; two other product terms are available for selection by the last eight three-state outputs.

These choices make it possible to use the macrocell as an output, an input, a bidirectional pin, or a three-state output for use in driving a bus.

Figure 8. MACH110 PAL Block

#### **ABSOLUTE MAXIMUM RATINGS**

| ABSOLUTE MAXIMUM RATINGS                             |

|------------------------------------------------------|

| Storage Temperature65°C to +150°C                    |

| Ambient Temperature With Power Applied55°C to +125°C |

| Supply Voltage with Respect to Ground0.5 V to +7.0 V |

| DC Input Voltage0.5 V to Vcc + 0.5 V                 |

| DC Output or I/O                                     |

| Pin Voltage0.5 V to Vcc + 0.5 V                      |

| Static Discharge Voltage 2001 V                      |

| Latchup Current                                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

$(T_A = 0^{\circ}C \text{ to } 75^{\circ}C) \dots 200 \text{ mA}$

## **OPERATING RANGES**

### Commercial (C) Devices

Ambient Temperature (TA)

Operating in Free Air . . . . . 0°C to +75°C

Supply Voltage (Vcc)

with Respect to Ground . . . . +4.75 V to +5.25 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                        | Min | Max  | Unit |

|---------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|------|------|

| Vон                 | Output HIGH Voltage                      | lo <sub>H</sub> = -3.2 mA, Vcc = Min<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>           | 2.4 |      | ٧    |

| Vol                 | Output LOW Voltage                       | I <sub>OL</sub> = 16 mA, V <sub>CC</sub> = Min<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> |     | 0.5  | V    |

| ViH                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                                       | 2.0 |      | ٧    |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW Voltage for all Inputs (Note 1)                                           |     | 0.8  | ٧    |

| liH                 | Input HIGH Current                       | V <sub>IN</sub> = 5.25 V, V <sub>CC</sub> = Max (Note 2)                                               |     | 10   | μА   |

| lı.                 | Input LOW Current                        | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = Max (Note 2)                                                  |     | -10  | μΑ   |

| lozн                | Off-State Output Leakage<br>Current HIGH | Vout = 5.25 V, Vcc = Max<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 2)              |     | 10   | μА   |

| lozu                | Off-State Output Leakage<br>Current LOW  | Vout = 0 V, Vcc = Max<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 2)                 |     | -10  | μА   |

| Isc                 | Output Short-Circuit Current             | V <sub>OUT</sub> = 0.5 V, V <sub>CC</sub> = Max (Note 3)                                               | -30 | -160 | mA   |

| lcc                 | Supply Current                           | V <sub>IN</sub> = 0 V, Outputs Open (I <sub>OUT</sub> = 0 mA)<br>Vcc = Max, f = 0 MHz (Note 4)         |     | 150  | mA   |

- 1. These are absolute values with respect to device ground and all overshoots due to system and/or tester noise are included.

- 2. I/O pin leakage is the worst case of IIL and IOZL (or IIH and IOZH).

- Not more than one output should be shorted at a time. Duration of the short-circuit should not exceed one second.

VOUT = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

- 4. This parameter is guaranteed worst case. An actual lcc value can be calculated by using the "Typical Dynamic lcc Characteristics" Chart towards the end of this data sheet.

## OE D 📟 0257526 0033016 453 🗪 AMD2

# ADV MICRO PLA/PLE/ARRAYS

## **CAPACITANCE** (Note 1)

| Parameter<br>Symbol | Parameter Description | Test Conditions                                                        | Тур | Unit |

|---------------------|-----------------------|------------------------------------------------------------------------|-----|------|

| Cin                 | Input Capacitance     | V <sub>IN</sub> = 2.0 V V <sub>CC</sub> = 5.0 V, T <sub>A</sub> = 25°C | 6   | рF   |

| Соит                | Output Capacitance    | V <sub>OUT</sub> = 2.0 V f = 1 MHz                                     | 8   | ρF   |

#### Note:

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

## **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)**

| Parameter |                      |                                                          |                |        | -1   | 2 .  | -1   | 5    | -20  |     |      |

|-----------|----------------------|----------------------------------------------------------|----------------|--------|------|------|------|------|------|-----|------|

| Symbol    | Parameter De         | scription                                                |                |        | Min  | Max  | Min  | Max  | Min  | Max | Unit |

| teo       |                      | Input, I/O, or Feedback to Combinatorial Output (Note 3) |                |        | 12   |      | 15   |      | 20   | ns  |      |

| 4-        | Setup Time fro       | m Input, I/O, or Feed                                    | back           | D-type | 7    |      | 10   |      | 13   |     | ns   |

| ts        | to Clock             |                                                          |                | T-type | 8    |      | 11   |      | 14   |     | ns   |

| tн        | Hold Time            |                                                          |                |        | 0    |      | 0    |      | 0    |     | ns   |

| tco       | Clock to Outpu       | it (Note 3)                                              |                |        |      | 8    |      | 10   |      | 12  | ns   |

| twL       | Clock Width          |                                                          |                | LOW    | 6    |      | 6    |      | 8    |     | ns   |

| twn       |                      |                                                          |                | HIGH   | 6    |      | 6    |      | 8    |     | ns   |

|           |                      | External Feedback 1/(ts-                                 |                | D-type | 66.7 |      | 50   |      | 40   |     | MHz  |

|           |                      |                                                          | 1/(ts + tco)   | T-type | 62.5 |      | 47.6 |      | 38.5 |     | MHz  |

| fmax      | Maximum<br>Frequency | D-type                                                   |                | 76.9   |      | 66.6 |      | 47.6 |      | MHz |      |

|           | (Note 4)             | Internal Feedback                                        | (ICNT)         | T-type | 71.4 |      | 55.5 |      | 43.5 |     | MHz  |

|           |                      | No Feedback                                              | 1/(twL + twH)  |        | 83.3 |      | 83.3 |      | 62.5 |     | MHz  |

| tan       | Asynchronous         | Reset to Registered                                      | Output         |        |      | 16   |      | 20   |      | 25  | ns   |

| tanw      | Asynchronous         | Reset Width (Note 4                                      | .)             |        | 12   |      | 15   |      | 20   |     | ns   |

| tarr      | Asynchronous         | Reset Recovery Tim                                       | e (Note 4)     |        | 8    |      | 10   |      | 15   |     | ns   |

| tap       | Asynchronous         | Preset to Registered                                     | Output         |        |      | 16   |      | 20   |      | 25  | ns   |

| tapw      | Asynchronous         | nous Preset Width (Note 4)                               |                | 12     |      | 15   |      | 20   |      | ns  |      |

| TAPR      | Asynchronous         | nchronous Preset Recovery Time (Note 4)                  |                | 8      |      | 10   |      | 15   |      | ns  |      |

| tea       | Input, I/O, or F     | eedback to Output E                                      | nable (Note 3) |        |      | 12   |      | 15   |      | 20  | ns   |

| ten       |                      | eedback to Output D                                      |                |        |      | 12   |      | 15   |      | 20  | ns   |

- 2. See Switching Test Circuit, for test conditions.

- 3. Parameters measured with 16 outputs switching.

- 4. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where frequency may be affected.

| ABSOLUTE MAXIMUM RATINGS                             |

|------------------------------------------------------|

| Storage Temperature65°C to +150°C                    |

| Ambient Temperature With Power Applied55°C to +125°C |

| Supply Voltage with Respect to Ground0.5 V to +7.0 V |

| DC Input Voltage –0.5 V to Vcc + 0.5 V               |

| DC Output or I/O                                     |

| Pin Voltage0.5 V to Vcc + 0.5 V                      |

| Static Discharge Voltage 2001 V                      |

| Latchup Current                                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

(T<sub>A</sub> = -55°C to 125°C) . . . . . . . . . . . . . . . . 200 mA

## **OPERATING RANGES**

Military (M) Devices (Note 1)

Ambient Temperature (T<sub>A</sub>)

Operating in Free Air . . . . . . -55°C to +125°C

Supply Voltage (Vcc)

with Respect to Ground ..... +4.5 V to +5.5 V

#### Note:

Military products are tested at T<sub>C</sub> = +25°C, +125°C and -55°C, per MIL-STD-883.

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over MILITARY operating ranges unless otherwise specified (Note 2)

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                          | Min | Max  | Unit |

|---------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|------|------|

| Vон                 | Output HIGH Voltage                      | lo <sub>H</sub> = -2.0 mA, V <sub>CC</sub> = Min<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | 2.4 |      | ٧    |

| Vol                 | Output LOW Voltage                       | loL = 12 mA, Vcc = Min<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>                           |     | 0.5  | ٧    |

| Vін                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 3)                                         | 2.0 |      | ٧    |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 3)                                          |     | 0.8  | ٧    |

| lıн                 | Input HIGH Leakage Current               | V <sub>IN</sub> = 5.5 V, V <sub>CC</sub> = Max (Note 4)                                                  |     | 10   | μА   |

| llr                 | Input LOW Leakage Current                | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = Max (Note 4)                                                    |     | -10  | μΑ   |

| lozн                | Off-State Output Leakage<br>Current HIGH | Vout = 5.5 V, Vcc = Max<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 4)                 |     | 40   | μΑ   |

| lozi.               | Off-State Output Leakage<br>Current LOW  | Vout = 0 V, Vcc = Max<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 4)                   |     | -40  | μΑ   |

| Isc                 | Output Short-Circuit Current             | Vout = 0.5 V, Vcc = Max (Note 5)                                                                         | -30 | -200 | mA   |

| lcc                 | Supply Current                           | V <sub>IN</sub> = 0 V, Outputs Open (lout = 0 mA)<br>V <sub>CC</sub> = Max, f = 0 MHz (Note 6)           |     | 170  | mA   |

- 2. For APL products, Group A, Subgroups 1, 2 and 3 are tested per MIL-STD-883, Method 5005, unless otherwise noted.

- VIL and VIH are input conditions of output tests and are not themselves directly tested. VIL and VIH are absolute voltages with

respect to device ground and include all overshoots due to system and/or tester noise. Do not attempt to test these values

without suitable equipment.

- 4. I/O pin leakage is the worst case of IIL and lozL (or IIH and lozH).

- 5. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second. VOUT = 0.5 V has been chosen to avoid test problems caused by tester ground degradation. This parameter is not 100% tested, but is evaluated at initial characterization and at any time the design is modified where Isc may be affected.

- This parameter is guaranteed worst case. An actual Icc value can be calculated by using the "Typical Dynamic Icc Characteristics" Chart towards the end of this data sheet.

# OE D 🔳 0257526 0033018 226 🖿 AMD2

## 'ADV MICRO PLA/PLE/ARRAYS \_

AMD 🎵

## **CAPACITANCE (Note 1)**

| Parameter<br>Symbol | Parameter Description | Test Condition           | ons                    | Тур | Unit |

|---------------------|-----------------------|--------------------------|------------------------|-----|------|

| Cin                 | Input Capacitance     | V <sub>IN</sub> = 2.0 V  | Vcc = 5.0 V, TA = 25°C | 8   | ρF   |

| Соит                | Output Capacitance    | V <sub>OUT</sub> = 2.0 V | f = 1 MHz              | 9   | рF   |

#### Note:

## **SWITCHING CHARACTERISTICS over MILITARY operating ranges (Note 2)**

| Parameter        |                                  |                              |                              |        | -2   | 0   |      |

|------------------|----------------------------------|------------------------------|------------------------------|--------|------|-----|------|

| Symbol           | Parameter D                      | escription                   |                              | Ī      | Min  | Max | Unit |

| tpD              | Input, I/O, or                   | Feedback to Comb             | oinatorial Output (No        | te 3)  |      | 20  | ns   |

|                  | Setup Time for                   | rom Input, I/O, or F         | eedback                      | D-type | 13   |     | ns   |

| ts               | to Clock                         | •                            |                              |        | 15   |     | ns   |

| , t <sub>H</sub> | Hold Time                        |                              |                              |        | 0    |     | ns   |

| tco              | Clock to Out                     | out (Note 3)                 |                              |        |      | 12  | ns   |

| twL              | Object Marie                     |                              | 110.00 07                    |        | 8    |     | ns   |

| twн              | Clock Width                      |                              | HIGH                         | 8      |      | ns  |      |

|                  | <u> </u>                         |                              |                              | D-type | 40   |     | MHz  |

|                  | Maximum<br>Frequency<br>(Note 4) | External Feedback 1/(ts+tco) | ck 1/(ts + tco)              | T-type | 37   |     | MHz  |

| fmax             |                                  | I Internal Feedback (fcnт)   | D-type                       | 47.6   |      | MHz |      |

|                  |                                  |                              | K (ICNT)                     | T-type | 43.5 |     | MHz  |

|                  |                                  | No Feedback                  | 1/(twL + twH)                |        | 62.5 |     | MHz  |

| tar              | Asynchronou                      | us Reset to Registe          | red Output                   |        |      | 25  | ns   |

| tarw             | Asynchronou                      | ıs Reset Width (No           | te 4)                        |        | 20   |     | ns   |

| tarr             | Asynchronou                      | s Reset Recovery             | Time (Note 4)                |        | 15   |     | ns   |

| tap              | Asynchronou                      | us Preset to Registe         | ered Output                  |        | ·    | 25  | ns   |

| tapw             | Asynchronou                      | us Preset Width (Note 4)     |                              |        | 20   |     | ns   |

| t <sub>APR</sub> | Asynchronou                      | s Reset Recovery             | Reset Recovery Time (Note 4) |        | 15   |     | ns   |

| tea              | Input, I/O, or                   | Feedback to Outpo            | ut Enable (Notes 3, 4        | 1)     |      | 20  | ns   |

| ten              | Input, I/O, or                   | Feedback to Outpo            | ut Disable (Notes 3,         | 4)     |      | 20  | ns   |

- See Switching Test Circuit for test conditions. For APL products, Group A, Subgroups 9, 10 and 11 are tested per MIL-STD-883, Method 5005, unless otherwise noted.

- 3. Parameters measured with 16 outputs switching.

- 4. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where these parameters may be affected.

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

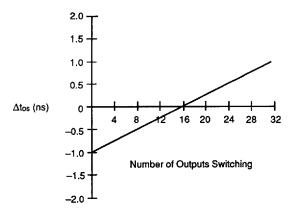

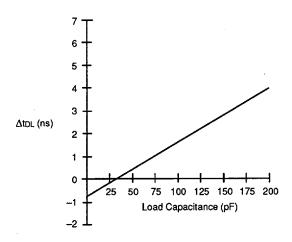

## TYPICAL SWITCHING CHARACTERISTICS

Vcc = 5.0 V, TA = 25°C. These parameters are not tested.

14127G-10

### **Derating for Number of Outputs Switching**

#### Note:

Applies to tpp, tco. Calculate as:

$t_{derated} = t_{16} O/P + \Delta t_{os}$

Datasheet numbers (t16 O/P) are specified at 16 outputs switching

14127G-11

## **Capacitive Load Derating**

#### Note:

Applies to all AC specifications and rise and fall times. Calculate as:

$tderated = t35 pF + \Delta tDL$

Datasheet numbers (t35 pF) are specified with 35 pF.

For typical rise and fall rates, use 1V/ns at 35 pF.

AMD 🗔

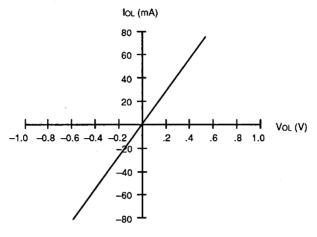

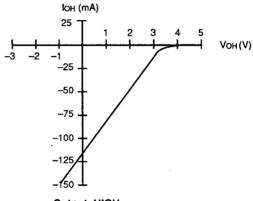

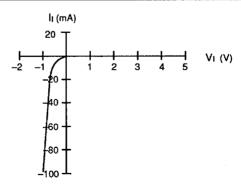

## TYPICAL CURRENT VS. VOLTAGE (I-V) CHARACTERISTICS

Vcc = 5.0 V, TA = 25°C

**Output, LOW**

14127G-7

**Output, HIGH**

14127G-8

14127G-9

Input

## TYPICAL DYNAMIC Icc CHARACTERISTICS

These parameters are not tested. Please refer to the General Information section for a discussion on the usage of these parameters.

| Parameter<br>Symbol | Parameter Description             | , | Тур   | Unit           |

|---------------------|-----------------------------------|---|-------|----------------|

| Icco                | Base static loc                   |   | 90    | mA             |

| i,                  | Incremental input current         |   | 15    | μ <b>Α/MHz</b> |

| ĺв                  | Incremental current per PAL block |   | 13    | μ <b>Α/MHz</b> |

| io                  | Incremental output current        | • | 90    | μΑ⁄ΜΗz         |

| İv                  | Voltage dependence                |   | 40    | %/V            |

| iτ                  | Temperature dependence            |   | -0.17 | %/°C           |

### TYPICAL DATA DESIGN GUIDELINES

The following parameters are provided in response to questions from designers. They are intended only as design guidelines, and should be used with care. They are not guaranteed or tested.

| Parameter Description                                                        | Тур | Unit |

|------------------------------------------------------------------------------|-----|------|

| Delay Minimums (Note 1)                                                      |     |      |

| Combinatorial propagation delay minimum                                      | 3   | ns   |

| Clock-to-output delay minimum                                                | 2   | ns   |

| Edge Rates (Note 2)                                                          |     |      |

| Rise rate                                                                    | 1   | V/ns |

| Fall rate                                                                    | 1   | V/ns |

| Skew (Note 3)                                                                |     |      |

| Clock-to-output skew, same clock polarity and same output polarity           | 1   | ns   |

| Clock-to-output skew, same clock polarity only                               | 2   | ns   |

| Clock-to-output skew, same output polarity only                              | 2   | ns   |

| Clock-to-output skew, different clock polarity and different output polarity | 2   | ns   |

| Internal Delay Savings (Note 4)                                              |     |      |

| Propagation delay savings                                                    | 2   | ns   |

| Clock-to-output delay savings                                                | 3   | ns   |

| Ground Bounce (Note 5)                                                       |     |      |

| Ground bounce noise level on low output                                      | 0.5 | V    |

- Minimum delays shown anticipate some future technology improvements, but it cannot be guaranteed that process and design changes will not increase the best-case performance beyond the values below.

- 2. Rise and fall rates are for unloaded outputs.

- 3. Skew values assume equal output loading.

- 4. Internal delay savings gives the typical amount of delay saved by not going through an output buffer.

- 5. The ground bounce noise level should be added to the static Vol. under normal load conditions as applied to a silent low output when all other I/O pins are switching from high to low.

AMD I

## **TYPICAL THERMAL CHARACTERISTICS**

Measured at 25°C ambient. These parameters are not tested.

| Parameter | Parameter Description                                |              | Тур  |      |      |

|-----------|------------------------------------------------------|--------------|------|------|------|

| Symbol    |                                                      |              | PLCC | CQFP | Unit |

| θjc       | Thermal impedance, junction to case                  |              | 14   | 13   | °C/W |

| θja       | Thermal impedance, junction to ambient               |              | 39   | 44   | °C/W |

| θjma      | Thermal impedance, junction to ambient with air flow | 200 lfpm air | 33   | 38   | •c/w |

|           |                                                      | 400 lfpm air | 30   | 35   | •c/w |

|           |                                                      | 600 lfpm air | 27   | 33   | °C/W |

|           |                                                      | 800 lfpm air | 25   | 31   | •c/w |

## Plastic θjc Considerations

The data listed for plastic 0 jc are for reference only and are not recommended for use in calculating junction temperatures. The heat-flow paths in plastic-encapsulated devices are complex, making the 0 jc measurement relative to a specific location on the package surface. Tests indicate this measurement reference point is directly below the die-attach area on the bottom center of the package. Furthermore, 0 jc tests on packages are performed in a constant-temperature bath, keeping the package surface at a constant temperature. Therefore, the measurements can only be used in a similar environment.