# Description

The P9242-R is a highly integrated, magnetic induction, wireless power transmitter supporting up to 15W. The system-on-chip operates with an input voltage range of 4.25V to 21V.

The transmitter includes an industry-leading 32-bit ARM® Cortex®-M0 processor offering a high level of programmability while consuming extremely low standby power. The P9242-R features two LED outputs with pre-defined user-programmable blinking patterns, buzzer, and programmable over-current protection supporting a wide range of applications. The I2C serial communication allows the user to read information such as voltage, current, frequency, and fault conditions. The P9242-R includes an under-voltage lockout and thermal management circuit to safe guard the device under fault conditions. Together with the P9221-R receiver ( $R_X$ ), the P9242-R is a complete wireless power system solution.

The P9242-R is available in a lead-free, space-saving 48-VFQFN package. The product is rated for a -40°C to +85°C operating temperature range.

# **Typical Applications**

- Charging pad

- Accessories

- Cradle

- Tablets

## Features

- Power transfer up to 15W

- Wide input voltage range: 4.25V to 21V

- WPC-1.2 compliant, MP-A2 coil configuration

- Integrated step-down switching regulator

- Embedded 32-bit ARM® Cortex®-M0 processor

- Integrated drivers for external power FETs

- Simultaneous voltage and current demodulation scheme for communication

- Integrated current sense amplifier

- Low standby power

- Dedicated remote temperature sensing

- Programmable current limit

- Power transfer LED indicator

- User programmable foreign objects detection (FOD)

- Pre-defined user-programmable LED pattern

- Active-LOW enable pin for electrical on/off

- Over-current and over-temperature protection

- Supports I2C interface

- -40 to +85°C ambient operating temperature range

- 48-VFQFN (6 × 6 mm) RoHS-compliant package

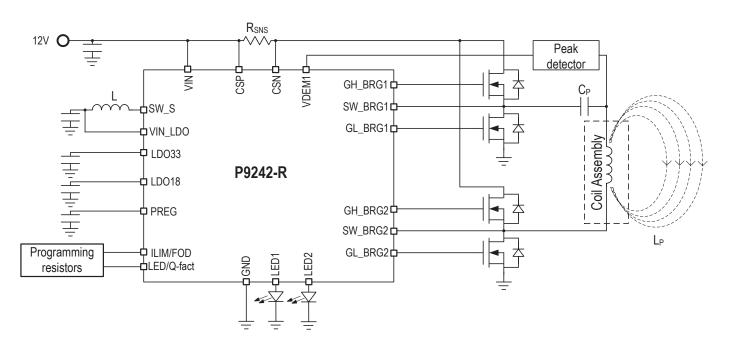

# **Basic Application Circuit**

# Contents

| 1.  | Pin A | Assignments                                                                | 5  |

|-----|-------|----------------------------------------------------------------------------|----|

| 2.  | Pin D | Descriptions                                                               | 6  |

| 3.  | Abso  | lute Maximum Ratings                                                       | 8  |

| 4.  | Elect | trical Characteristics                                                     | 9  |

| 5.  | Туріс | cal Performance Characteristics                                            | 11 |

| 6.  | Func  | tion Block Diagram                                                         | 13 |

| 7.  | Theo  | bry of Operation                                                           | 14 |

|     | 7.1   | Foreign Object Detection                                                   | 14 |

|     | 7.2   | Configuring Foreign Object Detection and Over-Current Limit – ILIM/FOD Pin | 14 |

|     | 7.3   | Enable Pin – EN                                                            | 16 |

|     | 7.4   | Buzzer – BUZR Pin                                                          | 16 |

|     | 7.5   | Voltage Demodulation – VDEM1 Pin                                           | 16 |

|     | 7.6   | Current Demodulation – IDEMI                                               | 16 |

|     | 7.7   | Thermal Protection                                                         | 17 |

|     | 7.8   | External Temperature Sensing – TS                                          | 17 |

|     | 7.9   | Q-Factor and LED Pattern Selection – LED/Q-Fact Pin                        | 18 |

|     | 7.10  | Input Voltage Requirement                                                  | 19 |

|     | 7.11  | Integrated Step-Down Regulator                                             | 19 |

|     | 7.12  | Integrated Linear Regulators – PREG, LDO33, and LDO18                      | 19 |

|     | 7.13  | Under-Voltage Lock-Out (UVLO) Protection                                   | 19 |

|     | 7.14  | LC Resonant Circuit                                                        | 20 |

| 8.  | Wire  | less Communication Interface                                               | 21 |

|     | 8.1   | Modulation/Communication                                                   | 21 |

|     | 8.2   | Bit Decoding Scheme for ASK                                                | 22 |

|     | 8.3   | Byte Decoding for ASK                                                      | 22 |

|     | 8.4   | Packet Structure                                                           | 22 |

| 9.  | WPC   | CMode Characteristics                                                      | 23 |

|     | 9.1   | Selection Phase                                                            | 23 |

|     | 9.2   | Ping Phase (Digital Ping)                                                  | 23 |

|     | 9.3   | Identification and Configuration Phase                                     | 24 |

|     | 9.4   | Negotiation Phase                                                          | 24 |

|     | 9.5   | Calibration Phase                                                          | 24 |

|     | 9.6   | Power Transfer Phase                                                       | 24 |

| 10. | Func  | tional Registers                                                           | 25 |

|     | 10.1  | I2C Interface                                                              | 25 |

|     | 10.2  | Register Addresses and Definitions                                         | 26 |

| 11. | Appli | ication Information                                                        | 29 |

|     | 11.1  | Power Dissipation and Thermal Requirements                                 | 29 |

|     |       |                                                                            |    |

|     | 11.2 Recommended Coils                       | 29 |

|-----|----------------------------------------------|----|

|     | 11.3 Typical Application Schematic           | 30 |

|     | 11.4 Bill of Materials (BOM)                 |    |

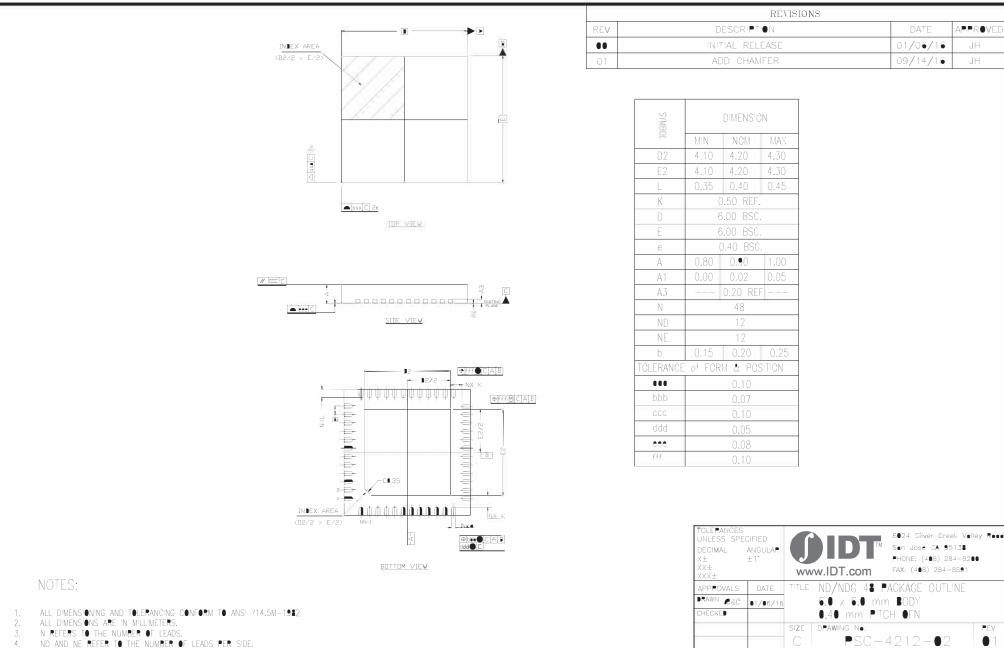

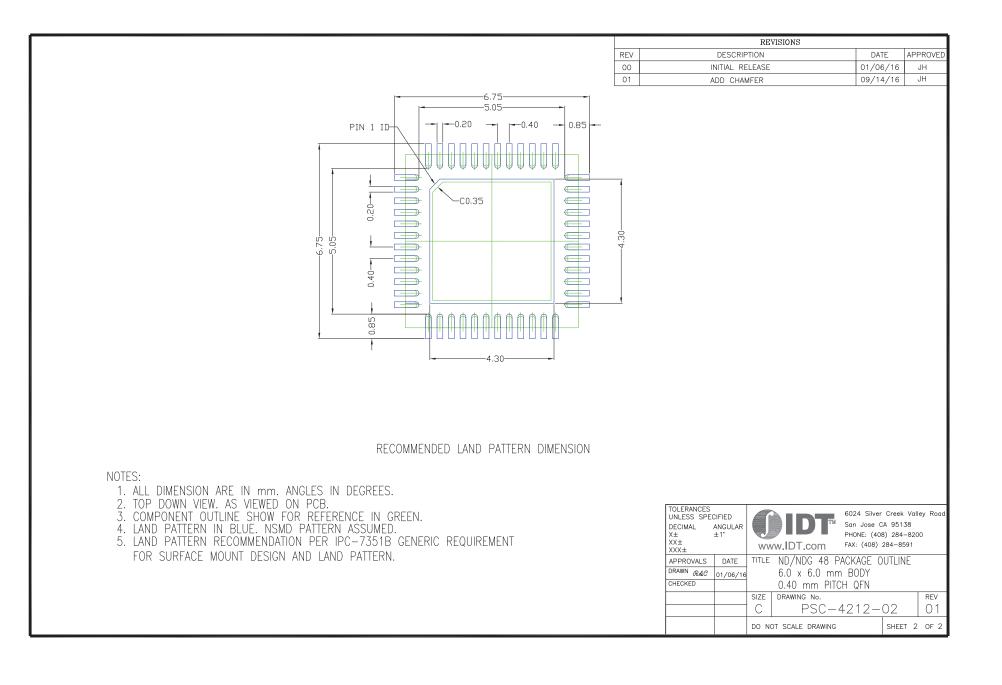

| 12. | Package Outline Drawings                     | 34 |

| 13. | Special Notes: NDG 48-VFQFN Package Assembly | 34 |

| 14. | Marking Diagram                              | 34 |

| 15. | Ordering Information                         | 34 |

| 16. | Revision History                             | 35 |

# **List of Figures**

| Figure 1.  | Pin Assignments                                                     | 5   |

|------------|---------------------------------------------------------------------|-----|

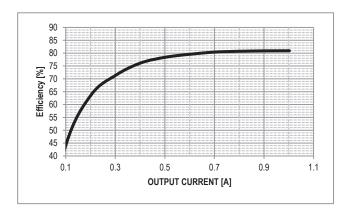

| Figure 2.  | Efficiency vs. Output Load: V <sub>OUT_RX</sub> = 12V               | 11  |

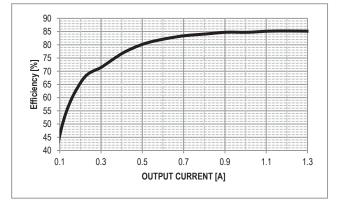

| Figure 3.  | Efficiency vs. Output Load: V <sub>OUT_RX</sub> = 9V                | 11  |

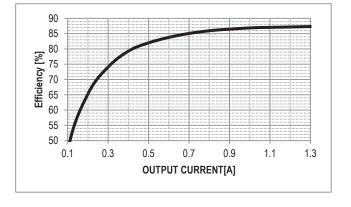

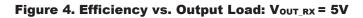

| Figure 4.  | Efficiency vs. Output Load: V <sub>OUT_RX</sub> = 5V                | 11  |

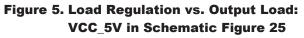

| Figure 5.  | Load Regulation vs. Output Load: VCC_5V in Schematic Figure 25      | 11  |

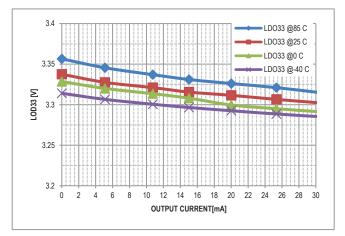

| Figure 6.  | Load Regulation vs. Output Load: LDO33                              | 11  |

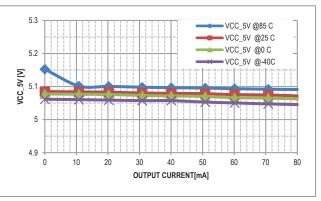

| Figure 7.  | Load Regulation vs. Output Load: LDO18                              | 11  |

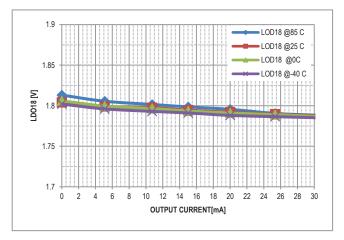

| Figure 8.  | Over-Current Limit vs. VILIM                                        | 12  |

| Figure 9.  | Voltage and Current Signal for Demodulation                         | 12  |

| Figure 10. | Enable Startup                                                      | .12 |

| Figure 11. | Communication Packet during R <sub>x</sub> Load Step from 0 to 1.3A | .12 |

| Figure 12. | Communication Packet during Rx Load Step from 1.3A to 0             | .12 |

| Figure 13. | Functional Block Diagram                                            | 13  |

| Figure 14. | Voltage Mode Envelope Detector                                      | 16  |

| Figure 15. | Current Mode Envelope Detector                                      | 16  |

| Figure 16. | NTC Thermistor Connection to TS Pin                                 | .17 |

| Figure 17. | UVLO Threshold Definition                                           | 19  |

| Figure 18. | Example of Differential Bi-phase Encoding for FSK                   | 21  |

| Figure 19. | Example of Asynchronous Serial Byte Format for FSK                  | 21  |

| Figure 20. | Bit Decoding Scheme                                                 | .22 |

| Figure 21. | Byte Decoding Scheme                                                | .22 |

| Figure 22. | Communication Packet Structure                                      | 22  |

| Figure 23. | WPC Power Transfer Phases Flow Chart                                | 23  |

| Figure 24. | I2C Access Read Protocol and Write Protocol                         | 25  |

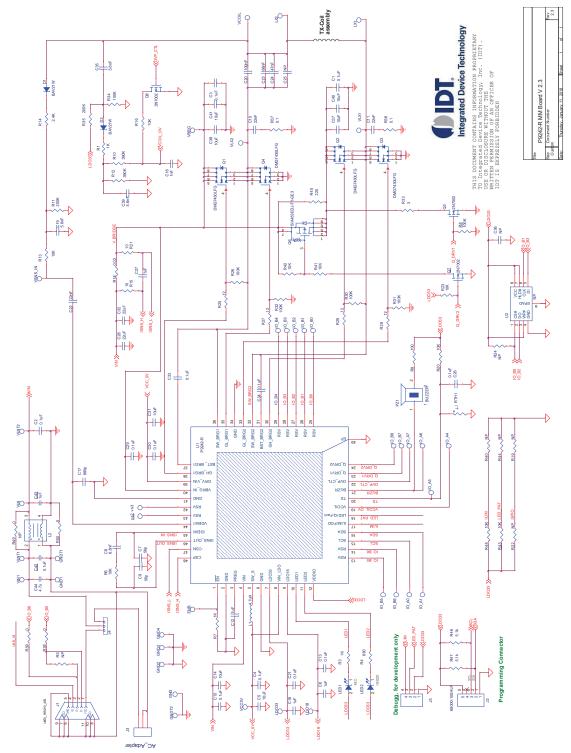

| Figure 25. | P9242-R Typical Application Schematic V2.3                          | 30  |

# **List of Tables**

| Table 1.  | Pin Descriptions                                                                            | 6  |

|-----------|---------------------------------------------------------------------------------------------|----|

| Table 2.  | Absolute Maximum Ratings                                                                    | 8  |

| Table 3.  | Package Thermal Information                                                                 | 8  |

| Table 4.  | ESD Information                                                                             |    |

| Table 5.  | Electrical Characteristics                                                                  | 9  |

| Table 6.  | External Resistor Values for Setting Current Limiting (ILIM) to 2.5A and FOD Threshold      | 15 |

| Table 7.  | External Resistor Values for Setting Current Limiting (ILIM) to 2.0A and FOD Threshold      | 15 |

| Table 8.  | External Resistor Values for Setting Current Limiting (ILIM) to 1.5A and FOD Threshold      | 15 |

| Table 9.  | Resistors for Setting the LED Pattern and Enabling/Disabling the Q-factor Detection for FOD |    |

| Table 10. | Device ID Register                                                                          | 26 |

| Table 11. | Firmware Major Revision                                                                     | 26 |

|           | Firmware Minor Revision                                                                     |    |

| Table 13. | State Register                                                                              | 27 |

| Table 14. | Status Register                                                                             | 27 |

| Table 15. | Read Register – Input Current                                                               | 27 |

| Table 16. | Read Register – Input Voltage                                                               | 28 |

| Table 17. | Read Register – Remote Temperature Sensing Voltage                                          | 28 |

| Table 18. | Read Register – Operating Frequency                                                         | 28 |

| Table 19. | Read Register – Operating Duty Cycle                                                        | 28 |

| Table 20. | Read Register – Full/Half Bridge Status                                                     | 28 |

| Table 21. | Recommended Coil Manufactures                                                               | 29 |

| Table 22. | P9242-R MM Evaluation Kit V2.3 Bill of Materials                                            | 31 |

|           |                                                                                             |    |

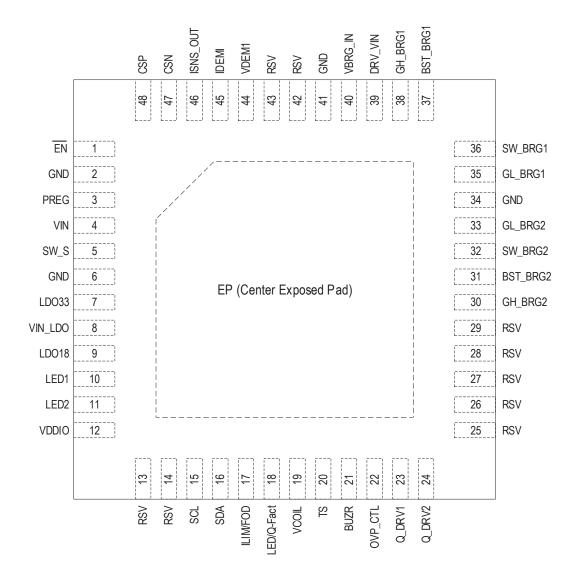

# **1. Pin Assignments**

### Figure 1. Pin Assignments

# 2. Pin Descriptions

### Table 1. Pin Descriptions

| Pins                                     | Name       | Туре   | Function                                                                                                                                                                                                                                                       |  |

|------------------------------------------|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                                        | EN         | Input  | Active-LOW enable pin. When connected to logic HIGH, the P9242-R enters the Shut Down Mode, which has a typical current consumption of 25µA. When connected to logic LOW, the device is in normal operation.                                                   |  |

| 2, 6, 34, 41, EP                         | GND        | -      | Ground connection.                                                                                                                                                                                                                                             |  |

| 3                                        | PREG       | Output | Regulated 5V output used for internal device biasing. Connect a $1\mu$ F capacitor from this pin to ground. This pin must not be externally loaded.                                                                                                            |  |

| 4                                        | VIN        | Input  | Input power supply. Connect a $10\mu F$ capacitor from this pin to ground.                                                                                                                                                                                     |  |

| 5                                        | SW_S       | Output | Step-down regulator`s switch node. Connect one of the terminals of the $4.7\mu H$ inductor to this pin.                                                                                                                                                        |  |

| 7                                        | LDO33      | Output | Regulated 3.3V output used for internal device biasing. Connect a $1\mu F$ capacitor from this pin to ground. This pin should not be externally loaded.                                                                                                        |  |

| 8                                        | VIN_LDO    | Input  | Linear regulator input power supply. Connected this pin to the 5V output of the step-down regulator.                                                                                                                                                           |  |

| 9                                        | LDO18      | Output | Regulated 1.8V output used for internal device biasing. Connect a $1\mu$ F capacitor from this pin to ground. This pin should not be externally loaded.                                                                                                        |  |

| 10                                       | LED1       | Input  | Open-drain output. Connect an LED to this pin                                                                                                                                                                                                                  |  |

| 11                                       | LED2       |        | Open-drain output. Connect an LED to this pin.                                                                                                                                                                                                                 |  |

| 12                                       | VDDIO      | Input  | Input power supply for internal biasing. This pin must be connected to LDO33.                                                                                                                                                                                  |  |

| 15                                       | SCL        | Input  | I2C interface clock input. Connect a 5.1k $\Omega$ pull-up resistor to LDO33 rail.                                                                                                                                                                             |  |

| 16                                       | SDA        | I/O    | I2C interface data input and data output, connect a 5.1k $\Omega$ pull-up resistor to LDO33 rail.                                                                                                                                                              |  |

| 17                                       | ILIM/FOD   | Input  | Programmable over-current limit and foreign object detection pin. Connect the center tap of the resistor divider to this pin to set the current-limit threshold and FOD threshold. For more information on setting the current limit and FOD, see section 7.2. |  |

| 18                                       | LED/Q-Fact | Input  | Programmable LED pattern selection and Q-factor enable/disable. Connect the center tap of a resistor divider to this pin. For more information on setting the LED pattern and Q-factor enable/disable, see section 7.9.                                        |  |

| 19                                       | VCOIL      | Input  | Input for coil voltage sensing.                                                                                                                                                                                                                                |  |

| 20                                       | TS         | Input  | Remote temperature sensor for over-temperature shutdown. Connect to the NTC thermistor network. If not used, connect to the LDO33 pin through the $10k\Omega$ resistor.                                                                                        |  |

| 21                                       | BUZR       | Output | Buzzer output. Connect a buzzer to this pin.                                                                                                                                                                                                                   |  |

| 22                                       | OVP_CTL    | I/O    | Logic HIGH during power transfer phase used to scale down the voltage to detect over-<br>voltage for VCOIL pin.                                                                                                                                                |  |

| 23                                       | Q_DRV1     | I/O    | Control signal for Q factor measurement circuit.                                                                                                                                                                                                               |  |

| 24                                       | Q_DRV2     | I/O    | Control signal for Q factor measurement circuit.                                                                                                                                                                                                               |  |

| 13, 14, 25, 26,<br>27, 28, 29, 42,<br>43 | RSV        | -      | Reserved for internal use. Do not connect.                                                                                                                                                                                                                     |  |

| Pins | Name     | Туре   | Function                                                                                                                                               |  |

|------|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 30   | GH_BRG2  | Output | Gate driver output for the high-side FET of half bridge 2. Connect this pin to a series $12\Omega$ resistor to the respective bridge FET gate.         |  |

| 31   | BST_BRG2 | Input  | Bootstrap pin for half bridge 2. Tie an external capacitor from this pin to the SW_BRG2 pin to generate a drive voltage higher than the input voltage. |  |

| 32   | SW_BRG2  | Output | Switch node for half bridge 2.                                                                                                                         |  |

| 33   | GL_BRG2  | Output | Gate driver output for the low-side FET of half bridge 2. Connect this pin to a series $12\Omega$ resistor to the respective bridge FET gate.          |  |

| 35   | GL_BRG1  | Output | Gate driver output for the low-side FET of half bridge 1. Connect this pin to a series $12\Omega$ resistor to the respective bridge FET gate.          |  |

| 36   | SW_BRG1  | Output | Switch node for half bridge 1.                                                                                                                         |  |

| 37   | BST_BRG1 | Output | Bootstrap pin for half bridge 1. Tie an external capacitor from this pin to the SW_BRG1 to generate a drive voltage higher than the input voltage.     |  |

| 38   | GH_BRG1  | Output | Gate driver output for the high-side FET of half bridge 1. Connect this pin to a series $12\Omega$ resistor to the respective bridge FET gate.         |  |

| 39   | DRV_VIN  | Input  | Input power supply for the internal gate drivers. Connect a $10\mu F$ capacitor from this pin to ground.                                               |  |

| 40   | VBRG_IN  | Input  | Bridge voltage input sense.                                                                                                                            |  |

| 44   | VDEM1    | Input  | High-pass filter input. Voltage demodulation pin for data packets based on coil voltage variation; transmitted by power receiver.                      |  |

| 45   | IDEMI    | Input  | High-pass filter input. Current demodulation pin for data packets based on coil current variation; transmitted by power receiver.                      |  |

| 46   | ISNS_OUT | Output | Input current sense output.                                                                                                                            |  |

| 47   | CSN      | Input  | Low-side input current sense (VBRIDGE).                                                                                                                |  |

| 48   | CSP      | Input  | High-side input current sense (VIN).                                                                                                                   |  |

# 3. Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. Stresses beyond those listed under "Absolute Maximum Ratings" might cause permanent damage to the P9242-R. Functional operation of the P9242-R at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions for extended periods could affect long-term reliability.

#### Table 2. Absolute Maximum Ratings

| Pins <sup>[a]</sup>                                                                                                                                                  | Rating <sup>[b]</sup> | Units |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|

| EN, VIN, SW_S, VBRG_IN, SW_BRG1, SW_BRG2, CSP, CSN, BST_BRG1, BST_BRG2, GH_BRG1, GH_BRG2                                                                             | -0.3 to 28            | V     |

| PREG, LDO33, VIN_LDO, LED1, LED2, VDDIO, SCL, SDA, ILIM/FOD, LED/Q-Fact, VCOIL, TS, BUZR, OVP_CTL, Q_DRV1, Q_DRV2, GL_BRG1, GL_BRG2, VDEM1, IDEMI, ISNS_OUT, DRV_VIN | -0.3 to 6             | V     |

| LDO18                                                                                                                                                                | -0.3 to 2             | V     |

[a] Absolute maximum ratings are not provided for reserved pins (RSV). These pins are not used in the application.

[b] All voltages are referred to ground unless otherwise noted. All GND pins and the exposed pad (EP) connected together.

### Table 3. Package Thermal Information

| Symbol          | Symbol Description                                                              |             | Units |

|-----------------|---------------------------------------------------------------------------------|-------------|-------|

| θ」Α             | θ <sub>JA</sub> Thermal Resistance Junction to Ambient <sup>[a], [b], [c]</sup> |             | °C/W  |

| θJC             | Thermal Resistance Junction to Case [b], [c]                                    | 18.8        | °C/W  |

| θ <sub>JB</sub> | Thermal Resistance Junction to Board <sup>[b], [c]</sup>                        | 1.36        | °C/W  |

| TJ              | Operating Junction Temperature <sup>[a], [b]</sup>                              | -40 to +125 | °C    |

| TA              | Ambient Operating Temperature <sup>[a], [b]</sup>                               | -40 to +85  | °C    |

| Tstg            | Storage Temperature                                                             | -55 to +150 | °C    |

| TLEAD           | Lead Temperature (soldering, 10s)                                               | +300        | °C    |

[a] The maximum power dissipation is P<sub>D(MAX)</sub> = (T<sub>J(MAX)</sub> - T<sub>A</sub>) / θ<sub>JA</sub> where T<sub>J(MAX)</sub> is 125°C. Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the device will enter thermal shutdown.

[b] This thermal rating was calculated on a JEDEC 51-standard 4-layer board with the dimensions 76.2 x 114.3 mm in still air conditions.

[c] Actual thermal resistance is affected by PCB size, solder joint quality, layer count, copper thickness, air flow, altitude, and other unlisted variables.

#### Table 4. ESD Information

| Test Model | Pins     | Ratings | Units |

|------------|----------|---------|-------|

| HBM        | All pins | ±2000   | V     |

| CDM        | All pins | ±500    | V     |

# 4. Electrical Characteristics

### Table 5. Electrical Characteristics

Note:  $V_{IN}$  = 5V,  $\overline{EN}$  = LOW,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at 25°C.

| Symbol                     | Description                                                   | Conditions/Notes                                                     | Min  | Typical | Мах  | Units |

|----------------------------|---------------------------------------------------------------|----------------------------------------------------------------------|------|---------|------|-------|

| Input Supplies             | and UVLO                                                      |                                                                      |      |         |      |       |

| V <sub>IN</sub>            | Input Operating Range <sup>[a]</sup>                          |                                                                      | 4.25 |         | 21   | V     |

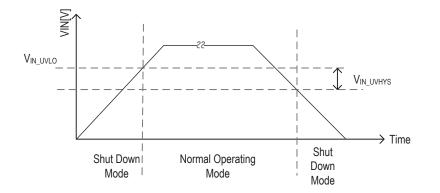

| VIN_UVLO                   | Under-Voltage Lockout                                         | V <sub>IN</sub> rising                                               |      | 4.0     |      | V     |

| VIN_UVHYS                  | Under-Voltage Hysteresis                                      | V <sub>IN</sub> falling                                              |      | 0.5     |      | V     |

| lin                        | Operating Mode Input Current                                  | Power transfer phase,<br>Vin = 12V                                   |      | 10      |      | mA    |

| I <sub>STD_BY</sub>        | Standby Mode Current                                          | Periodic ping                                                        |      | 1       |      | mA    |

| I <sub>SHD</sub>           | Shut Down Current                                             | $\overline{EN} = V_{IN} = 21V$                                       |      | 25      | 80   | μA    |

| Enable Pin Thr             | reshold (EN)                                                  |                                                                      |      |         |      | -     |

| V <sub>IH</sub>            | Input Threshold HIGH                                          |                                                                      | 2.5  |         |      | V     |

| VIL                        | Input Threshold LOW                                           |                                                                      |      |         | 0.5  | V     |

| I <sub>EN_LKG</sub>        | EN Pin Input Leakage Current                                  | V <sub>EN</sub> = 0V                                                 | -1   |         | 1    | μA    |

|                            |                                                               | V <sub>EN</sub> = 5V                                                 |      | 2.5     |      | μA    |

| Step-Down Reg              | gulator <sup>[b]</sup> with C <sub>OUT</sub> = 33µF; L = 4.7µ | ιH                                                                   |      |         |      |       |

| Vout                       | Step-Down Output Voltage                                      | Vin = 12V                                                            | 4.5  | 5       | 5.5  | V     |

| N-Channel MO               | SFET Drivers                                                  | + +                                                                  |      |         |      |       |

| tls_on_off                 | Low-Side Gate Driver Rise and Fall Times                      | C <sub>LOAD</sub> = 3nF; 10% to 90%,<br>90% to 10%                   |      | 50      | 150  | ns    |

| ths_on_off                 | High-Side Gate Driver Rise and<br>Fall Times                  | C <sub>LOAD</sub> = 3nF; 10% to 90%,<br>90% to 10%                   |      | 150     | 300  | ns    |

| Input Current S            | Sense                                                         | ·                                                                    |      |         |      | ·     |

| V <sub>SEN_OFST</sub>      | Amplifier Output Offset Voltage                               | Measured at the ISNS_OUT pin;<br>V <sub>CSP</sub> = V <sub>CSN</sub> |      | 0.6     |      | V     |

| ISENACC_TYP <sup>[C]</sup> | Measured Current Sense<br>Accuracy                            | V <sub>R_ISEN</sub> = 25mV, I = 1.25A                                |      | ±3.5    |      | %     |

| Analog to Digit            | tal Converter                                                 |                                                                      |      | - I I   |      | 1     |

| N                          | Resolution                                                    |                                                                      |      | 12      |      | Bit   |

| Channel                    | Number of Channels                                            |                                                                      |      | 10      |      |       |

| V <sub>IN,FS</sub>         | Full Scale Input Voltage                                      |                                                                      |      | 2.4     |      | V     |

| LDO18 <sup>[b]</sup>       |                                                               |                                                                      |      | - I     |      |       |

| VLDO18                     | 1.8V LDO Regulator                                            | Cout = 1µF, Vvin_ldo = 5.5V                                          | 1.71 | 1.8     | 1.89 | V     |

| Symbol               | Description                        | Conditions/Notes                           | Min       | Typical | Max       | Units |

|----------------------|------------------------------------|--------------------------------------------|-----------|---------|-----------|-------|

| LDO33 <sup>[b]</sup> | -                                  |                                            |           |         | <u> </u>  |       |

| V <sub>LDO33</sub>   | 3.3V LDO Regulator                 | $C_{OUT} = 1\mu F$ , $V_{VIN\_LDO} = 5.5V$ | 3.15      | 3.3     | 3.45      | V     |

| PREG                 | -                                  |                                            |           |         | <u> </u>  |       |

| V <sub>PREG</sub>    | 5V LDO Regulator                   |                                            |           | 5       |           | V     |

| Thermal Shut         | tdown                              |                                            |           |         |           |       |

| T <sub>SD</sub>      | Thermal Shutdown                   | Threshold rising                           |           | 140     |           | °C    |

|                      |                                    | Threshold falling                          |           | 120     |           | °C    |

| Analog Input         | Pins Input Current Leakage (TS, V  | COIL)                                      |           |         |           |       |

| I <sub>LKG</sub>     | Leakage Current                    |                                            | -1        |         | 1         | μA    |

| Open-Drain F         | Pins Output Logic Levels (LED1, LE | D2, SCL, SDA)                              | <b>!</b>  | •       |           |       |

| Vон                  | Output Logic HIGH                  |                                            | 4         |         |           | V     |

| Vol                  | Output Logic LOW                   | l = 8mA                                    |           |         | 0.5       | V     |

| Digital Input/       | Output Pins Logic Levels           |                                            |           |         |           |       |

| VIH                  | Input Voltage HIGH Level           |                                            | 0.7*VDDIO |         |           | V     |

| VIL                  | Input Voltage LOW Level            |                                            |           |         | 0.3*VDDIO | V     |

| Ilkg                 | Leakage Current                    |                                            |           |         | 1         | μA    |

| Vон                  | Output Logic HIGH                  | I = 8mA, VDDIO = 3.3V                      | 2.4       |         |           | V     |

| Vol                  | Output Logic LOW                   | I = 8mA, VDDIO = 3.3V                      |           |         | 0.5       | V     |

| I2C Interface        | (SCL, SDA)                         |                                            |           | 1       | 1         | I     |

| f <sub>SCL_SLV</sub> | Clock Frequency                    | As I2C slave                               |           |         | 400       | kHz   |

| CB                   | Capacitive Load                    | For each bus line                          |           |         | 100       | pF    |

| C <sub>BIN</sub>     | SCL, SDA Input Capacitance         |                                            |           | 5       |           | pF    |

| Ilkg                 | Input Leakage Current              | V = GND and 3.3V                           | -1        |         | 1         | μA    |

[a] The input voltage operating range is dependent upon the type of transmitter power stage (full-bridge, half-bridge) and transmitting coil inductance. WPC specifications should be consulted for appropriate input voltage ranges by end-product type.

[b] Do not externally load. For internal biasing only.

[c] A 20mΩ, 1% or better sense resistor and a 4.7Ω, 1% input filter resistor are required to meet the FOD specification.

# 5. Typical Performance Characteristics

V<sub>IN</sub> = 12.0V; EN = LOW. The following performance characteristics were taken using a P9221-R, 15W Wireless Power Receiver (RX) at  $T_A$  = +25°C unless otherwise noted.

### Figure 2. Efficiency vs. Output Load: Vout\_RX = 12V

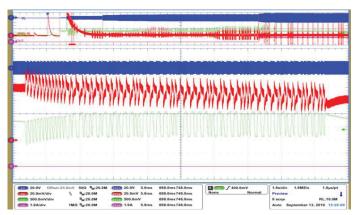

Figure 8. Over-Current Limit vs. VILIM

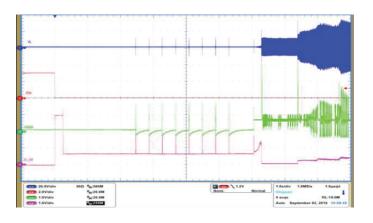

Figure 10. Enable Startup

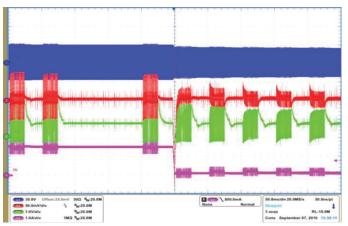

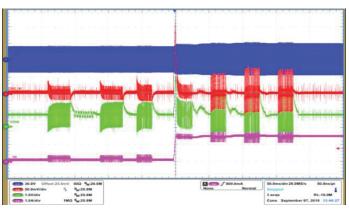

Figure 12. Communication Packet during R<sub>x</sub> Load Step from 1.3A to 0

### Figure 9. Voltage and Current Signal for Demodulation

Figure 11. Communication Packet during R<sub>x</sub> Load Step from 0 to 1.3A

# 6. Function Block Diagram

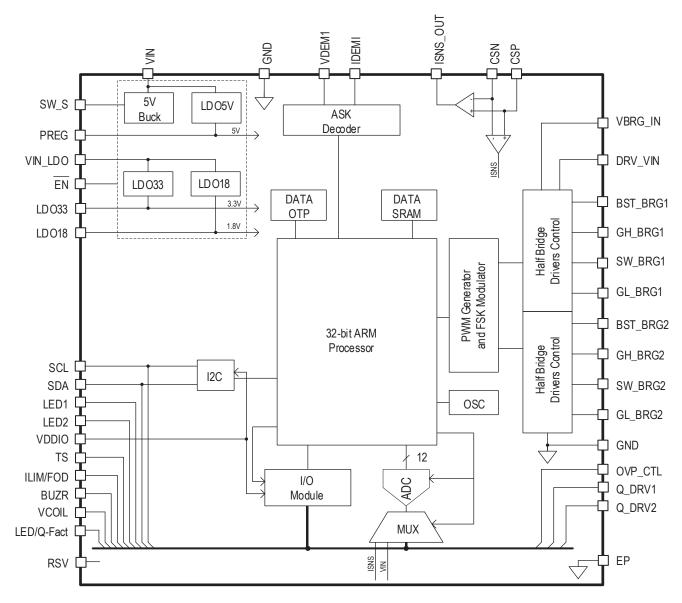

### Figure 13. Functional Block Diagram

# 7. Theory of Operation

A wireless power charging system has a base station with one or more transmitters that make power available via DC-to-AC inverter(s) and transmit the power over a strongly-coupled inductor pair to a receiver in a mobile device. The amount of power transferred to the mobile device is controlled by the wireless power receiver by sending communication packets to the transmitter to increase, decrease, or maintain the power level. The communication from receiver to transmitter is purely digital and consists of 1's and 0's that ride on top of the power link that exists between the transmitter (TX) and receiver (RX) coil. Communication from transmitter to receiver is achieved by frequency shift keying (FSK) modulation over the power signal frequency and amplitude shift keying (ASK) is used for the communication protocol from receiver to transmitter.

A feature of the wireless charging system is the fact that when it is not delivering power, the transmitter is in Standby Mode. The transmitter remains in Standby Mode and periodically pings until it detects the presence of a receiver. Once an Extended Power Profile Receiver is detected, such as the P9221-R or equivalent, the transmitter will provide with up to 15W of output power. If a Baseline Power Profile Receiver is present, the transmitter will deliver only up to 5W of output power.

The P9242-R contains features that ensure a high level of functionality and compliance with the WPC requirements, such as a power path that efficiently achieves power transfer, a simple and robust communication demodulation circuit, safety and protection circuits, configuration, and status indication circuits.

## 7.1 Foreign Object Detection

When metallic objects, such as coins, keys, and paperclips, are exposed to alternating magnetic fields, the eddy current flowing through the object will heat up. The amount of heat generated is a function of the amplitude and frequency of the magnetic field, as well as the characteristics of the object, such as resistivity, size, and shape. In any wireless power system, the heat generated by the eddy current manifests itself as a power loss reducing the overall system efficiency. If appropriate measures are not taken, the heating could lead to unsafe situations.

In the Extended Power Profile, there are two stages of foreign object detection (FOD). One is by measuring the system quality factor prior to entering the power-transfer phase, and the other is to measure the power loss difference between the received power and the transmitted power during the power-transfer phase. Prior to entering the power-transfer phase, the P9242-R detects a change in the coil's quality factor (the Q-factor) when a wireless power receiver or metal object has been placed on its surface. The transmitter measures the Q-factor and compares it with the reference Q-factor provided by the receiver. If the difference is higher than the reference Q-factor, the P9242-R will identify it as an FOD and shut down the system. See section 7.9 for details for enabling Q-factor detection.

The second stage of the foreign object detection is during the power transfer where the power loss difference between the received power and transmitted power is constantly measured and compared to the WPC-1.2-specified threshold. If the difference is higher than the threshold set by the WPC specification, the system will shut down to avoid over-heating.

See Table 6, Table 7, and Table 8 in section 7.2 for details for configuring the FOD threshold via external resistors.

## 7.2 Configuring Foreign Object Detection and Over-Current Limit – ILIM/FOD Pin

The over-current protection (OCP) is designed to protect the half-bridge and wireless receiver unit from becoming exposed to operating conditions that could potentially cause damage or unexpected behavior from the system. The input current is continuously monitored during the power transfer stage. If the input current goes above the OCP threshold of 2.5A (typical), the P9242-R will increase the switching frequency or reduce the duty cycle in order to keep the input current below the OCP value.

External resistors can be used to select a different OCP threshold (ILIM). The same resistors are used to set the FOD threshold (refer to section 7.1 for FOD details). See Table 6, Table 7, and Table 8 for the resistor values. See the typical application schematic in Figure 25 for the location of the resistors.

Note: The default current limit setting on the P9242-R-EVK is set to 2.5A. It is highly recommended that the current limit to be set at 2.5A for 15W applications.

| ILIM[mA] | R48[KΩ] | R40[KΩ] | Tuned FOD Threshold [%] |

|----------|---------|---------|-------------------------|

|          | 10      | 6.98    | -40                     |

|          | 10      | 7.68    | -30                     |

|          | 10      | 8.25    | -20                     |

|          | 10      | 9.09    | -10                     |

| 2500     | 10      | Open    | 0                       |

|          | 10      | 11      | 10                      |

|          | 10      | 12.1    | 20                      |

|          | 10      | 13.3    | 30                      |

|          | 10      | 14.3    | 40                      |

### Table 6. External Resistor Values for Setting Current Limiting (ILIM) to 2.5A and FOD Threshold

| Table 7. | External Resistor Values for Setting Current Limiting (ILIM) to 2.0A and FOD Threshold |

|----------|----------------------------------------------------------------------------------------|

|----------|----------------------------------------------------------------------------------------|

| ILIM [mA] | R48 [KΩ] | R40 [KΩ] | Tuned FOD Threshold [%] |

|-----------|----------|----------|-------------------------|

|           | 10       | 2.55     | -40                     |

|           | 10       | 2.94     | -30                     |

|           | 10       | 3.32     | -20                     |

|           | 10       | 3.74     | -10                     |

| 2000      | 10       | 4.12     | 0                       |

|           | 10       | 4.64     | 10                      |

|           | 10       | 5.11     | 20                      |

|           | 10       | 5.76     | 30                      |

|           | 10       | 6.34     | 40                      |

### Table 8. External Resistor Values for Setting Current Limiting (ILIM) to 1.5A and FOD Threshold

| ILIM [mA] | R48 [KΩ] | R40 [KΩ] | Tuned FOD Threshold [%] |

|-----------|----------|----------|-------------------------|

|           | Open     | 10       | -40                     |

|           | 10       | 0.232    | -30                     |

|           | 10       | 0.487    | -20                     |

|           | 10       | 0.732    | -10                     |

| 1500      | 10       | 1        | 0                       |

|           | 10       | 1.27     | 10                      |

|           | 10       | 1.58     | 20                      |

|           | 10       |          | 30                      |

|           | 10       | 2.21     | 40                      |

## 7.3 Enable Pin – EN

The P9242-R can be disabled by applying a logic HIGH to the  $\overline{EN}$  pin. When the voltage on the  $\overline{EN}$  pin is pulled high, operation is suspended and the P9242-R is placed in the low-current Shut Down Mode. If pulled low, the P9242-R is active.

## 7.4 Buzzer – BUZR Pin

An optional AC-type ceramic buzzer can be connected between the BUZR pin to GND through a current limiting resistor. A short 4kHz "chirp" sound will indicate when the object is detected. Do not connect this pin if the buzzer function is not desired.

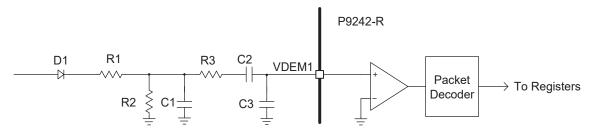

### 7.5 Voltage Demodulation – VDEM1 Pin

In order to increase the communication reliability in any load condition, the P9242-R has integrated two demodulation schemes, one based on coil current information and the other based on coil voltage modulation. The voltage mode envelope detector is implemented using a discrete solution as depicted on Figure 14. This simple implementation achieves the envelope detector function low-pass filter as well as the DC filter function.

### Figure 14. Voltage Mode Envelope Detector

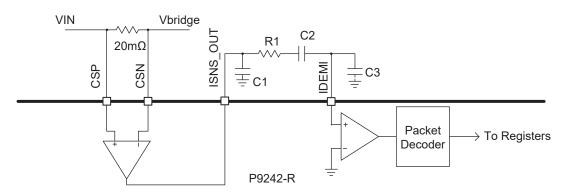

### 7.6 Current Demodulation – IDEMI

The current-mode detector takes the modulation information from the current sense resistor, which carries the coil current modulation information in addition to the averaged input current. There is an additional discrete low-pass filter and DC filter between the ISNS\_OUT and IDEMI pins. The packet decoder block is shared between the voltage-mode and current-mode detectors. The packet decoder selects either voltage-mode or current-mode signals depending upon which produces the best demodulated signal.

#### Figure 15. Current Mode Envelope Detector

## 7.7 Thermal Protection

The P9242-R integrates thermal shutdown circuitry to prevent damage resulting from excessive thermal stress that may be encountered under fault conditions. This circuitry will shut down or reset the P9242-R if the die temperature exceeds a threshold to prevent damage resulting from excessive thermal stress that might be encountered under fault conditions. An internal temperature protection block is enabled in the P9242-R that monitors the temperature inside the chip. If the die temperature exceeds 140°C, the chip shuts down and resumes when the internal temperature drops below 120°C.

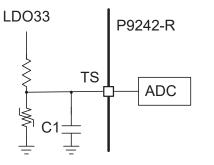

## 7.8 External Temperature Sensing – TS

The P9242-R has a temperature sensor input, TS, which can be used to monitor an external temperature by using a thermistor. The built-in comparator's reference voltage was chosen to be 0.6V in the P9242-R, and it is used for monitoring the voltage level on the TS pin.

### Figure 16. NTC Thermistor Connection to TS Pin

To disable the thermistor, the TS pin should be connected to the LDO33 pin. Do not leave the TS pin floating.

### 7.9 Q-Factor and LED Pattern Selection – LED/Q-Fact Pin

The P9242-R uses two LEDs to indicate the power transfer status, faults, and operating modes depending on the voltage level at the LED/Q-Fact pin. In addition, this pin enables or disables the Q-factor used for FOD (see section 7.1). The LEDs are connected to the LED1 and LED2 pins as shown in the typical application schematic in Figure 25. The LED pattern can be selected and the Q-factor can be enabled or disabled by the voltage on the LED/Q-Fact pin as determined by the resistor divider R43 and R44 as shown in Figure 25.

| Q-Factor  |          | LED/Q-Fact  | R43  | R44    |               |         | Sta       | tus      |           |

|-----------|----------|-------------|------|--------|---------------|---------|-----------|----------|-----------|

| Detection | Option   | Pin Voltage | [kΩ] | [kΩ]   | LED1/LED2 Pin | Standby | Transfer  | Complete | Fault     |

|           | 1        | Pull-Down   | Open | 10     | LED2          | Off     | On        | Off      | Off       |

|           | 1        |             | Open | 10     | LED1          | Off     | Off       | Off      | Blink 4Hz |

|           | 2 0.225V | 0.225V      | 10   | 0.732  | LED2          | On      | On        | Off      | Off       |

|           | 2        | 0.2250      | 10   | 0.752  | LED1          | On      | Off       | Off      | Blink 4Hz |

|           | 3        | 0.375V      | 10   | 1.27   | LED2          | Off     | Blink 1Hz | On       | Blink 4Hz |

|           |          | 0.3757      | 10   | 1.27   | LED1          | Off     | Off       | Off      | Off       |

| Enabled   | 4        | 0.525V      | 10   | 1.87   | LED2          | Off     | On        | Off      | Blink 4Hz |

| Liidbieu  |          | 0.323 V     | 10   | 1.07   | LED1          | Off     | Off       | Off      | Off       |

|           | 5        | 0.675V      | 10   | 2.55   | LED2          | On      | Blink 1Hz | On       | Off       |

|           | 5        | 0.0757      | 10   | 2.00   | LED1          | On      | Off       | Off      | Blink 4Hz |

|           | 6        | 0.825V      | 10   | 3.32   | LED2          | Off     | Off       | On       | Off       |

|           | 0        | 0.0257      | 10   | 5.52   | LED1          | Off     | On        | Off      | Blink 4Hz |

|           | 7        | Pull-Up     | 10   | Open   | LED2          | Off     | Blink 1Hz | On       | Off       |

|           | 1        | Full-Op     | 10   | Open   | LED1          | Off     | Off       | Off      | Blink 4Hz |

|           | 1        | 1.125       | 10   | 5.11 - | LED2          | Off     | On        | Off      | Off       |

|           | 1        | 1.125       | 10   | 5.11   | LED1          | Off     | Off       | Off      | Blink 4Hz |

|           | 2        | 1.275       | 10   | 6.34   | LED2          | On      | On        | Off      | Off       |

|           | 2        | 1.275       | 10   | 0.34   | LED1          | On      | Off       | Off      | Blink 4Hz |

|           | 3        | 1.425       | 10   | 7.68   | LED2          | Off     | Blink 1Hz | On       | Blink 4Hz |

|           | 5        | 1.425       | 10   | 7.00   | LED1          | Off     | Off       | Off      | Off       |

| Disabled  | 4        | 1.575       | 10   | 9.09   | LED2          | Off     | On        | Off      | Blink 4Hz |

| Disableu  | 4        | 1.575       | 10   | 9.09   | LED1          | Off     | Off       | Off      | Off       |

|           | 5        | 1.725       | 10   | 11     | LED2          | On      | Blink 1Hz | On       | Off       |

|           | 5        | 1.725       | 10   | 11     | LED1          | On      | Off       | Off      | Blink 4Hz |

|           | 6        | 1.875       | 10   | 13     | LED2          | Off     | Off       | On       | Off       |

|           | 0        | 1.070       | IU   | 10     | LED1          | Off     | On        | Off      | Blink 4Hz |

|           | 7        | 2.025       | 10   | 15.8   | LED2          | Off     | Blink 1Hz | On       | Off       |

|           | 1        | 2.020       | ĨŬ   | 13.0   | LED1          | Off     | Off       | Off      | Blink 4Hz |

Table 9. Resistors for Setting the LED Pattern and Enabling/Disabling the Q-factor Detection for FOD

### 7.10 Input Voltage Requirement

The P9242-R can support an input voltage ranging from 4.5V to 21V. However, since the transmitter is compliant with WPC's MP-A2 coil configuration, the input voltage is restricted to 10V to 14V with a nominal voltage of 12V.

## 7.11 Integrated Step-Down Regulator

The input capacitors (C14 and C15 in Figure 25) must be connected as close as possible between the VIN pin and GND pin. Similarly, the output capacitor (C4 and C5 in Figure 25) must be placed close to the inductor and GND. The output voltage is sensed by the VIN\_LDO pin; therefore, the connection from the step-down output (VCC\_5V; see Figure 25) to the VIN\_LDO pin should be made as wide and short as possible to minimize output voltage errors. The step-down regulator is the input voltage to the LDO18 and LDO33 linear regulators and is not recommended for powering an external load.

## 7.12 Integrated Linear Regulators – PREG, LDO33, and LDO18

The P9242 has three low-dropout (LDO) regulators used to bias the internal circuitry. The 5V pre-regulator (PREG) provides bias for the entire internal power management. The PREG requires a 1µF ceramic bypass capacitor connected from the PREG pin to GND. This capacitor must be placed very close to the PREG pin. The voltage regulator must not be externally loaded.

The LDO33 and LDO18 are used to bias the internal digital circuit. The regulator's input voltage is supplied through the VIN\_LDO pin. Both regulators require a 1µF ceramic capacitor from the pin to GND. The voltage regulators must not be externally loaded.

## 7.13 Under-Voltage Lock-Out (UVLO) Protection

The P9242-R has 4V (typical, rising) under-voltage lockout circuit on the VIN pin. To guarantee proper functionality, the voltage on the VIN pin must rise above the UVLO threshold. If the input voltage stays below the UVLO threshold, the P9242-R is in Shut Down Mode.

### Figure 17. UVLO Threshold Definition

## 7.14 LC Resonant Circuit

The LC resonant circuit comprises the series primary resonant coil ( $L_P$ ) and series capacitance ( $C_P$ ). The transmitter coil assembly is vendor specific, and it must comply with the WPC recommendation. The WPC recommendations include the self-inductance value, DC resistance (DCR), Q-factor, size, and number of turns.

The P9242-R is designed for an MP-A2 coil configuration using half-bridge and full-bridge inverter topologies to drive the primary coil (L<sub>P</sub>) and a series capacitance (C<sub>P</sub>). Within the operating frequency range from 110kHz to 145kHz, the assembly of the primary coil and shielding has a self-inductance of L<sub>P</sub> = 10.0µH ±10%, and the value of the series capacitance on the P9242-R-EVK is C<sub>P</sub> = 215nF ±5%. Near resonance, the voltage developed across the C<sub>P</sub> series capacitance could reach 70V peak. High-voltage (100V) COG-type ceramic capacitors are highly recommended for their AC and DC characteristics and temperature stability. The recommended parts are listed on the bill of materials (BOM) in Table 22.

# 8. Wireless Communication Interface

## 8.1 Modulation/Communication

The WPC-1.2 extended power profile specification uses two-way communication for power transfer: receiver-to-transmitter and transmitter-to receiver.

Receiver-to-transmitter communication is accomplished by modulating the load seen by the receiver's coil; the communication is purely digital and symbols 1's and 0's carried on the power signal. Modulation is done with amplitude-shift keying (ASK) modulation using with a bit-rate of 2Kbps. To the transmitter, this appears as an impedance change, which results in measurable variations of the transmitter's coil. The power transmitter demodulates this variation of the coil current or voltage to receive the packets.

Transmitter-to-receiver communication is accomplished by frequency-shift keying (FSK) modulation over the power signal frequency. The power transmitter P9242-R has the means to modulate FSK data from the power signal frequency and use it in order to establish the handshaking protocol with the power receiver.

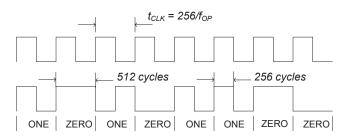

The P9242-R implements FSK communication when used in conjunction with WPC-compliant receivers, such as the P9221-R. The FSK communication protocol allows the transmitter to send data to the receiver using the power transfer link in the form of modulating the power transfer signal. This modulation appears in the form of a change in the base operating frequency ( $f_{OP}$ ) to the modulated operating frequency ( $f_{MOD}$ ) in periods of 256 consecutive cycles. Equation 1 should be used to compute the modulated frequency based on any given operating frequency.

Communication packets are transmitted from transmitter to receiver with less than 1% positive frequency deviation following any receiver-totransmitter communication packet. The frequency deviation is calculated using Equation 1.

$$f_{MOD} = \frac{60000}{\frac{60000}{f_{OP}} - 3}$$

[KHz]

Where  $f_{MOD}$  is the change in frequency in the power signal frequency;  $f_{OP}$  is the base operating frequency of power transfer; and 60,000kHz is the frequency of the internal oscillator responsible for counting the period of the power transfer signal.

The FSK byte-encoding scheme and packet structure complies with the WPC specification revision 1.2. The FSK communication uses a bi-phase encoding scheme to modulate data bits into the power transfer signal. The start bit will consist of 512 consecutive  $f_{MOD}$  cycles (or logic '0'). A logic '1' value will be sent by sending 256 consecutive  $f_{OP}$  cycles followed by 256  $f_{MOD}$  cycles or vice versa, and a logic '0' is sent by sending 512 consecutive  $f_{OP}$  cycles.

### Figure 18. Example of Differential Bi-phase Encoding for FSK

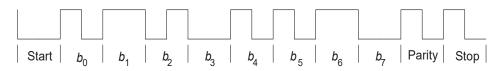

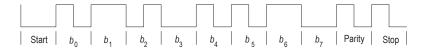

Each byte will comply with the start, data, parity, and stop asynchronous serial format structure shown in Figure 19:

### Figure 19. Example of Asynchronous Serial Byte Format for FSK

### 8.2 Bit Decoding Scheme for ASK

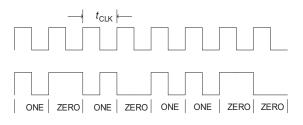

As required by the WPC, the P9242-R uses a differential bi-phase coding scheme to demodulate data bits onto the power signal. A clock frequency of 2kHz is used for this purpose. A logic ONE bit is coded using two narrow transitions, whereas a logic ZERO bit is encoded using one wider transition as shown below:

#### Figure 20. Bit Decoding Scheme

### 8.3 Byte Decoding for ASK

Each byte in the communication packet comprises 11 bits in an asynchronous serial format, as shown in Figure 21.

#### Figure 21. Byte Decoding Scheme

Each byte has a start bit, 8 data bits, a parity bit, and a single stop bit.

### 8.4 Packet Structure

The P9242-R communicates with the base station via communication packets. Each communication packet has the following structure:

#### Figure 22. Communication Packet Structure

| Preamble Header | Message | Checksum |

|-----------------|---------|----------|

|-----------------|---------|----------|

# 9. WPC Mode Characteristics

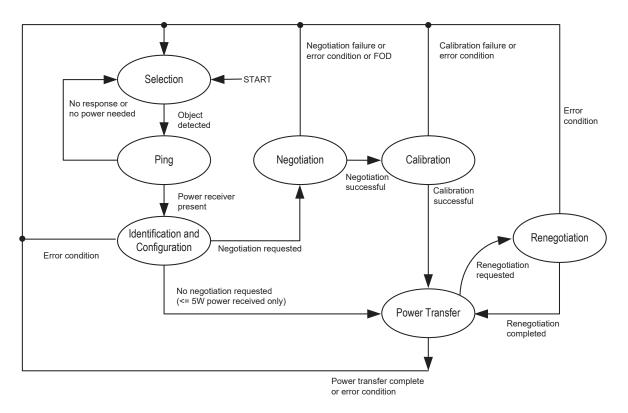

The WPC-1.2 extended power profile wireless power specification has a negotiation phase, calibration phase, and renegotiation phase, as shown in Figure 23.

## 9.1 Selection Phase

In the selection phase, the power transmitter determines if it will proceed to the ping phase after detecting the placement of an object. In this phase, the power transmitter typically monitors the interface surface for the placement and removal of objects using a small measurement signal. This measurement signal should not wake up a power receiver that is positioned on the interface surface.

## 9.2 Ping Phase (Digital Ping)

In the ping phase, the power transmitter will transmit power and will detect the response from a possible power receiver. This response ensures the power transmitter that it is dealing with a power receiver rather than some unknown object. When a power receiver is placed on a WPC "Qi" charging pad, it responds to the application of a power signal by rectifying this power signal. When the internal bias voltage is greater than a specific threshold level, then receiver is initiated enabling the WPC communication protocol.

If the power transmitter correctly receives a signal strength packet, the power transmitter proceeds to the identification and configuration phase of the power transfer, maintaining the power signal output.

### 9.3 Identification and Configuration Phase

The identification and configuration phase is the part of the protocol that the power transmitter executes in order to identify the power receiver and establish a default power transfer contract. This protocol extends the digital ping in order to enable the power receiver to communicate the relevant information.

In this phase, the power transmitter identifies itself and receives information for a default power transfer contract as follows:

- It receives the configuration packet.

- If the *Neg* bit in the received configuration packet is set to ZERO, the power transmitter should proceed to the power transfer phase without sending a response for baseline power profile.

- If the Neg bit in the received configuration packet is set to ONE, subsequently the power transmitter should proceed to the negotiation

phase for the extended power profile.

### 9.4 Negotiation Phase

In the negotiation phase, the power receiver negotiates with the power transmitter to fine-tune the power transfer contract. The power receiver sends negotiation requests to the power transmitter, which the power transmitter can grant or deny. In addition, to improve its initial assessment of whether foreign objects are present, the power transmitter can compare the quality factor reported by the power receiver with its own measurement. If the power transmitter detects a foreign object, it should return the selection phase.

### 9.5 Calibration Phase

In the calibration phase, the power receiver provides information that the power transmitter can use to improve its ability to detect foreign objects during power transfer.

### 9.6 Power Transfer Phase

In this phase, the P9242-R controls the power transfer by means of the following control data packets:

- Control Error Packets

- Received Power Packet (RPP, FOD-related)

- End Power Transfer (EPT) Packet

Once the "identification and configuration" phase is completed, the transmitter initiates the power transfer mode. The receiver's control circuit sends error packets to the transmitter to adjust the rectifier voltage to the level required to maximize the efficiency of the linear regulator and to send to the transmitter the actual received power packet for foreign object detection (FOD) to guarantee safe, efficient power transfer.

In the event of an EPT issued by the application, when the receiver sends EPT packets, the transmitter terminates the power transfer.

# **10. Functional Registers**

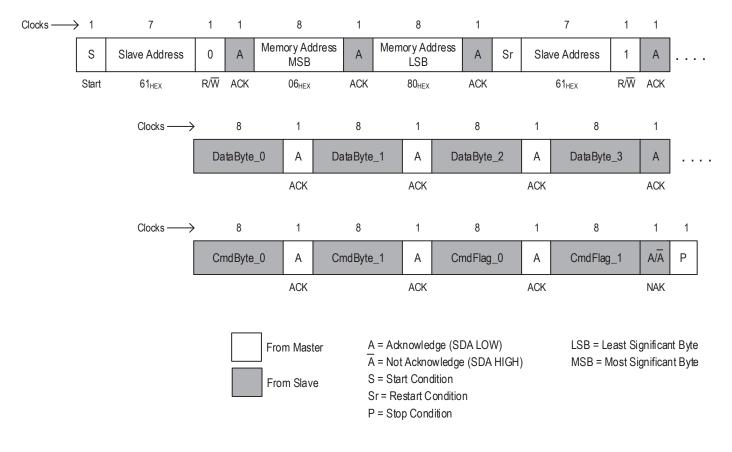

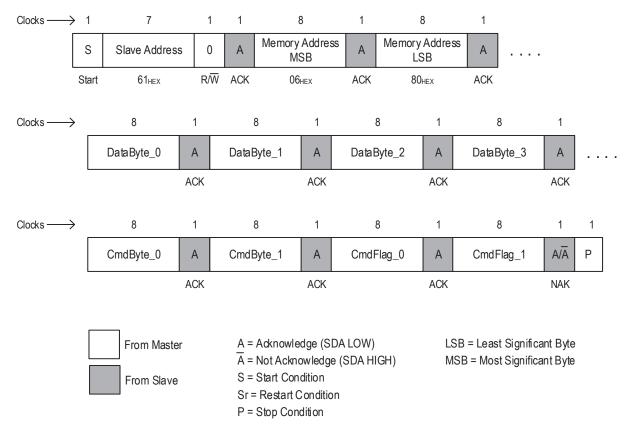

The P9242-R registers can be read and written to via the P9242-R's I2C interface on the SCL and SDA pins. Section 10.1 defines the protocol for reading and writing via this interface. Section 10.2 gives the details for the register definitions.

## 10.1 I2C Interface

### Figure 24. I2C Access Read Protocol and Write Protocol

### **Read Protocol**

### Write Protocol

## **10.2 Register Addresses and Definitions**

The tables in this section provide a comprehensive list of address locations, field names, available operations (R or RW), default values, and functional descriptions of all internally accessible registers contained within the P9242-R. The default I<sup>2</sup> C slave address is  $61_{HEX}$ . The address of each register has a two-byte structure. For example, the address of the device ID high byte is  $01_{HEX}$  and  $05_{HEX}$ .

#### Table 10. Device ID Register

| Address and Bit           | Register Field Name | R/W | Default           | Function and Description |

|---------------------------|---------------------|-----|-------------------|--------------------------|

| 0104 <sub>HEX</sub> [7:0] | Device_ID_L         | R   | $42_{\text{HEX}}$ | Device ID low byte       |

| 0105 <sub>HEX</sub> [7:0] | Device_ID_H         | R   | 92 <sub>HEX</sub> | Device ID high byte      |

#### Table 11. Firmware Major Revision

| Address and Bit           | Register Field Name | R/W | Default | Function and Description          |

|---------------------------|---------------------|-----|---------|-----------------------------------|

| 010C <sub>HEX</sub> [7:0] | FW_Major_Rev_L      | R   | 06нех   | Major firmware revision low byte  |

| 010D <sub>HEX</sub> [7:0] | FW_Major_Rev_H      | R   | 00нех   | Major firmware revision high byte |

#### Table 12. Firmware Minor Revision

| Address and Bit           | Register Field Name | R/W | Default           | Function and Description          |

|---------------------------|---------------------|-----|-------------------|-----------------------------------|

| 010E <sub>HEX</sub> [7:0] | FW_Minor_Rev_L      | R   | 16 <sub>HEX</sub> | Minor firmware revision low byte  |

| 010F <sub>HEX</sub> [7:0] | FW_Minor_Rev_H      | R   | 00нех             | Minor firmware revision high byte |

### Table 13. State Register

| Address and Bits    | Register Field Name | R/W | Default | Function and Description                                                                                                                                                                                                                   |

|---------------------|---------------------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06E0 <sub>HEX</sub> | System State        | R   | 00нех   | ODEC =Startup1DEC =Idle2DEC =Analog Ping Phase4DEC =Digital Ping Phase5DEC =WPC Identification7DEC =WPC Configuration8DEC =Power Transfer Initialization9DEC =Power Transfer State11 DEC =Remove Power12DEC =Restart13DEC =WPC Negotiation |

### Table 14. Status Register

| Address and Bits    | Register Field Name | R/W | Default | Function and Description                                                                                                                                                                                                                                   |

|---------------------|---------------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06E1 <sub>HEX</sub> | System Status       | R   | 00нех   | $0_{DEC}$ =System Normal $1_{DEC}$ =FOD Alarm $2_{DEC}$ =EPT Charge Complete $4_{DEC}$ =EPT No Response $5_{DEC}$ =EPT Internal Fault $6_{DEC}$ =Over-Temperature Alarm $7_{DEC}$ =Over-Current $9_{DEC}$ =EPT Other Rx Fault $10_{DEC}$ =Negotiation Fail |

### Table 15. Read Register – Input Current

| Address and Bits          | Register Field Name | R/W | Default | Function and Description           |

|---------------------------|---------------------|-----|---------|------------------------------------|

| 06E2 <sub>HEX</sub> [7:0] | Coil_current [7:0]  | R   | -       | 8 LSB of coil current value in mA. |

| 06E3 <sub>HEX</sub> [7:0] | Coil_current [15:8] | R   | -       | 8 MSB of coil current value in mA. |

### Table 16. Read Register – Input Voltage

| Address and Bits          | Register Field Name | R/W | Default | Function and Description           |

|---------------------------|---------------------|-----|---------|------------------------------------|

| 06E4 <sub>HEX</sub> [7:0] | Coil_voltage [7:0]  | R   | -       | 8 LSB of coil voltage value in mV. |

| 06E5 <sub>HEX</sub> [7:0] | Coil_voltage [15:8] | R   | -       | 8 MSB of coil voltage value in mV. |

#### Table 17. Read Register - Remote Temperature Sensing Voltage

Sensing Voltage =  $\frac{Thermistor ADC Value[15:0]}{4095} * 2.4V$

| Address and Bits          | Register Field Name         | R/W | Default | Function and Description       |

|---------------------------|-----------------------------|-----|---------|--------------------------------|

| 06E8 <sub>HEX</sub> [7:0] | Thermistor ADC Value [7:0]  | R   | -       | 8 LSB of thermistor ADC value. |

| 06E9 <sub>HEX</sub> [7:0] | Thermistor ADC Value [15:8] | R   | -       | 8 MSB of thermistor ADC value. |

### Table 18. Read Register – Operating Frequency

$f_{OP} = \frac{60 \text{MHz}}{FRE\_CNT[15:0]}$

| Address and Bits          | Register Field Name | R/W | Default | Function and Description            |

|---------------------------|---------------------|-----|---------|-------------------------------------|

| 06EA <sub>HEX</sub> [7:0] | FRE_CNT [7:0]       | R   | -       | 8 LSB of operating frequency count. |

| 06EB <sub>HEX</sub> [7:0] | FRQ_CNT [15:8]      | R   | -       | 8 MSB of operating frequency count. |

### Table 19. Read Register – Operating Duty Cycle

$DUTY CYCLE = \frac{DUTY\_CNT * 50\%}{255}$

| Address and Bits          | Register Field Name | R/W | Default | Function and Description       |

|---------------------------|---------------------|-----|---------|--------------------------------|

| 06EC <sub>HEX</sub> [7:0] | DUTY_CNT [7:0]      | R   | -       | 8 LSB of operating duty count. |

| 06ED <sub>HEX</sub> [7:0] | DUTY_CNT [15:8]     | R   | -       | 8 MSB of operating duty count. |

### Table 20. Read Register – Full/Half Bridge Status

| Address and Bits          | Register Field Name           | R/W | Default | Function and Description |

|---------------------------|-------------------------------|-----|---------|--------------------------|

| 06EE <sub>HEX</sub> [7:0] | Full/half bridge status [7:0] | R   | -       | 1 = Half bridge.         |

|                           |                               |     |         | 0 = Full bridge.         |

# **11. Application Information**

### **11.1 Power Dissipation and Thermal Requirements**

The P9242-R is offered in a 48-VFQFN package that has a maximum power dissipation capability of about 1.47W. The maximum power dissipation of the package is determined by the number of thermal vias between the package and the printed circuit board (PCB). The maximum power dissipation of the package is defined by the die's specified maximum operating junction temperature,  $T_{J(MAX)}$  of 125°C. The junction temperature rises when the heat generated by the device's power dissipation flow is impeded by the package-to-PCB thermal resistance.

The VFQFN package offers a typical thermal resistance, junction to ambient ( $\theta_{JA}$ ), of 27.2°C/W when the PCB layout design is optimized as described in the *P9242-R Layout Guide* document. The techniques noted in the PCB layout section must be followed when designing the printed circuit board layout. Attention to the placement of the P9242-R and bridge FET packages in proximity to other heat-generating devices in a given application design should also be considered. The ambient temperature around the power IC will also have an effect on the thermal limits of an application. The main factors influencing  $\theta_{JA}$  (in the order of decreasing influence) are PCB characteristics, die/package attached thermal pad size (VFQFN) and thermal vias, and the final system hardware construction. Board designers should keep in mind that the package thermal metric  $\theta_{JA}$  is impacted by the characteristics of the PCB. Changing the design or configuration of the PCB changes the overall thermal resistivity and the board's heat-sinking efficiency.

Three basic approaches for enhancing thermal performance are listed below:

- Improving the power dissipation capability of the PCB design.

- Improving the thermal coupling of the component to the PCB.

- Introducing airflow into the system.

First, the maximum power dissipation for a given situation should be calculated using Equation 2:

$$P_{D(MAX)} = \frac{\left(T_{J(MAX)} - T_{A}\right)}{\theta_{JA}}$$

Equation

Where

$P_{D(MAX)}$  = Maximum power dissipation

$\theta_{JA}$  = Package thermal resistance (°C/W)

$T_{J(MAX)}$  = Maximum device junction temperature (°C)

$T_A$  = Ambient temperature (°C)

The maximum recommended operating junction temperature ( $T_{J(MAX)}$ ) for the P9242-R is 125°C. The thermal resistance of the 48-pin VFQFN package (NDG48) is optimally  $\theta_{JA}$ =27.2°C/W. Operation is specified to a maximum steady-state ambient temperature ( $T_A$ ) of 85°C. Therefore, the maximum recommended power dissipation is given by the following equation:

$P_{D(Max)} = (125^{\circ}\text{C} - 85^{\circ}\text{C}) / 27.2^{\circ}\text{C/W} \approx 1.47 \text{ Watt}$

All the previously mentioned thermal resistances are the values found when the P9242-R is mounted on a standard board of the dimensions and characteristics specified by the JEDEC 51 standard.

## **11.2 Recommended Coils**

Table 21. Recommended Coil Manufactures

| Output Power | Vendor Part number |                     | Inductance at 100kHz | DCR at 20°C |

|--------------|--------------------|---------------------|----------------------|-------------|

| 15W          | SUNLORD            | SWA53N53H30C11B     | 10µH                 | 50mΩ        |

| 15W          | TDK                | WT525225-12F2-MA2-G | 10.6µH               | 40mΩ        |

2

## **11.3 Typical Application Schematic**

The typical application schematic provides a basic guideline to understanding and building a functional medium-power wireless power transmitter type MP-A2 as described in the WPC specifications. Other components, not shown on the typical application schematic, might be needed in order to comply with other requirements, such as EMC or thermal specifications.

## **11.4 Bill of Materials (BOM)**

#### Table 22. P9242-R MM Evaluation Kit V2.3 Bill of Materials

| ltem | Reference                                                                                                                                                                                                                            | Quantity | Value            | Description                                    | Part Number         | PCB<br>Footprint      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|------------------------------------------------|---------------------|-----------------------|

| 1    | C1, C2, C3, C4, C13,<br>C15, C21, C26, C29, C30,<br>C33, C34                                                                                                                                                                         | 12       | 0.1µF            | CAP CER 0.1µF 25V 10% X7R 0402                 | C1005X7R1E104K050BB | 0402                  |

| 2    | C5, C14, C31, C37, C38,<br>C40, C41                                                                                                                                                                                                  | 7        | 10µF             | CAP CER 10µF 25V 20% X5R 0603                  | C1608X5R1E106M080AC | 0603                  |

| 3    | C6, C12, C16, C27                                                                                                                                                                                                                    | 4        | 1µF              | CAP CER 1µF 25V 20% X5R 0402                   | C1005X5R1E105M050BC | 0402                  |

| 4    | C7, C9                                                                                                                                                                                                                               | 2        | 56pF             | CAP CER 56PF 50V NP0 0402                      | CL05C560JB5NNNC     | 0402                  |

| 5    | C8                                                                                                                                                                                                                                   | 1        | 6.8nF            | CAP CER 6800PF 25V X7R 0402                    | GRM155R71E682KA01D  | 0402                  |

| 6    | C10, C11                                                                                                                                                                                                                             | 2        | 22nF             | 0.022µF 50V Ceramic Capacitor X7R 0603         | GCM188R71H223KA37D  | 0603                  |

| 7    | C17                                                                                                                                                                                                                                  | 1        | 680pF            | CAP CER 680PF 50V X7R 0402                     | CL05B681KB5NNNC     | 0402                  |

| 8    | C18                                                                                                                                                                                                                                  | 1        | 1nF              | CAP CER 1000pF ±10% 50V X7R 0402               | GRM155R71H102KA01D  | 0402                  |

| 9    | C19, C35, C39                                                                                                                                                                                                                        | 3        | 5.6nF            | 5600pF 100V Ceramic Capacitor C0G, NP0<br>0603 | C1608C0G2A562J080AC | 0603                  |