# CMOS 12-Bit Monolithic Multiplying CMOS D/A Converter

PMI's PM-7541A is a 12-bit resolution, current output, 4-quadrant multiplying digital-to-analog converter. Manufactured with advanced oxide-isolated, silicon-gate, monolithic CMOS technology, the PM-7541A features circuitry designed to protect data inputs against damage from electrostatic discharges.

Laser-trimmed thin-film resistors provide true 12-bit linearity with excellent absolute accuracy. The PM-7541A's low power dissipation, along with NMOS temperature compensating switches, insures high performance across the full temperature range.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer (OCM).

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# CMOS 12-Bit Monolithic Multiplying CMOS D/A Converter

PM-7541A

#### **FEATURES**

- 7541 with Improved Accuracy and Ruggedness

- ±1/2 LSB Max Nonlinearity Over Full Temp. Range (12-Bit Linearity)

- ±1 LSB Max Gain Error No User Adjustment Required

- Less Than 0.03 LSB Max Zero Scale Error (5nA)

- ▶ Low Gain Tempco ......5ppm/°C Max

- All Data Input Pins Designed with ESD Protective Circuitry

- Full Four-Quadrant Multiplication

- Low Power Consumption

- Low Feedthrough Error and Digital Charge Injection

- Superior Power Supply Rejection

From +5V to +15V ......001%% Max

- Direct Replacement for AD7541 and AD7541A

- Both DIP Packages Suitable for Auto-Insertion, Surface Mount Packaging Available

- Available in Die Form

#### **APPLICATIONS**

- Digital/Synchro Conversion

- Programmable Amplifiers

- Ratiometric A/D Conversion

- Function Generators

- Digitally-Controlled Attenuators

- Digitally-Controlled Power Supplies

- Digitally-Controlled Filters

#### **GENERAL DESCRIPTION**

PMI's PM-7541A is a 12-bit resolution, current output, 4quadrant multiplying digital-to-analog converter. Manufactured with advanced oxide-isolated, silicon-gate, monolithic CMOS technology, the PM-7541A features circuitry designed to protect data inputs against damage from electrostatic discharges.

Laser-trimmed thin-film resistors provide true 12-bit linearity with excellent absolute accuracy. The PM-7541A's low power dissipation, along with NMOS temperature compensating switches, insures high performance across the full temperature range.

The PM-7541A is a superior pin-compatible replacement for the industry standard 7541 and the AD7541A Available in standard

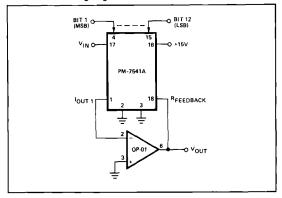

#### **FUNCTIONAL DIAGRAM**

plastic and CerDIP packages, the PM-7541A is compatible with automatic insertion equipment. The improved performance of the PM-7541A permits upgrading existing designs with greater ruggedness and accuracy. Tighter linearity and gain error specifications may permit reduced system parts count by eliminating trimming circuitry.

# ORDERING INFORMATION †

|               | PACKAGE                |                                       |                                                         |                                           |

|---------------|------------------------|---------------------------------------|---------------------------------------------------------|-------------------------------------------|

| GAIN<br>ERROR | NON-<br>LIN-<br>EARITY | MILITARY* TEMPERATURE -55°C to +125°C | EXTENDED<br>INDUSTRIAL<br>TEMPERATURE<br>-40°C to +85°C | COMMERCIAL<br>TEMPERATURE<br>0°C to +70°C |

| ±1 LSB        | ±1/2LSB                | PM7541AAX                             | PM7541AEX                                               | PM7541AGP                                 |

| ±2 LSB        | ±1/2 LSB               | PM7541ABX                             | PM7541AFX                                               | _                                         |

| ±2 LSB        | ±1/2 LSB               | PM7541ABRC/883                        | PM7541AFP                                               | -                                         |

| ±2LSB         | ±1/2 LSB               | _                                     | PM7541AFPC                                              | _                                         |

| ±2 LSB        | ±1/2 LSB               | _                                     | PM7541AFS                                               | -                                         |

- For devices processed in total compliance to MIL-STD-883, add/883 after part number. Consult factory for 883 data sheet.

- Burn-in is available on commercial and industrial temperature range parts in CerDIP, plastic DIP, and TO-can packages.

#### **CROSS REFERENCE**

| ADI       | TEMPERATURE RANGE                                                          |

|-----------|----------------------------------------------------------------------------|

| AD7541ATD |                                                                            |

| AD7541ASD | MIL                                                                        |

| AD7541ABQ |                                                                            |

| AD7541AAQ | IND                                                                        |

| AD7541AKN |                                                                            |

| AD7541AKP | COM                                                                        |

| AD7541AJN |                                                                            |

|           | AD7541ATD<br>AD7541ASD<br>AD7541ABO<br>AD7541AAQ<br>AD7541AKN<br>AD7541AKP |

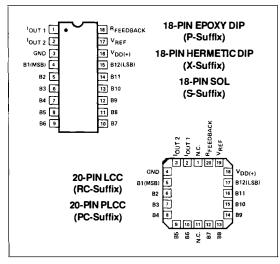

## **PIN CONNECTIONS**

### **ABSOLUTE MAXIMUM RATINGS**

|                                                                                                        | timom tiat intos                                           |                          |                                        |  |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------|----------------------------------------|--|

| $(T_A = +25^{\circ}C, unless)$                                                                         | s otherwise noted)                                         |                          |                                        |  |

| V <sub>DD</sub> (to GND)                                                                               |                                                            |                          | ±17V                                   |  |

| V <sub>BEE</sub> (to GND)                                                                              |                                                            |                          | ±25V                                   |  |

| Vara (to GND)                                                                                          | ***************************************                    |                          | ±25V                                   |  |

| Digital Input Voltag                                                                                   | e Range                                                    |                          | V <sub>n</sub> to GND                  |  |

| Operating Tempera                                                                                      |                                                            |                          | DD                                     |  |

|                                                                                                        | Versions                                                   | -55                      | °C to ±125°C                           |  |

|                                                                                                        | S Versions                                                 |                          |                                        |  |

|                                                                                                        |                                                            |                          |                                        |  |

|                                                                                                        |                                                            |                          |                                        |  |

|                                                                                                        | IIIA                                                       |                          | . 15000                                |  |

|                                                                                                        | ure                                                        |                          |                                        |  |

| Storage Temperatu                                                                                      | ıre                                                        | –65°                     | °C to +150°C                           |  |

| Storage Temperatu                                                                                      |                                                            | –65°                     | °C to +150°C                           |  |

| Storage Temperatu                                                                                      | ıre                                                        | –65°                     | °C to +150°C                           |  |

| Storage Temperature                                                                                    | (Soldering, 60 sec)                                        | –65°                     | °C to +150°C<br>300°C                  |  |

| Storage Temperature Lead Temperature PACKAGE TYPE                                                      | (Soldering, 60 sec)                                        | -65°                     | °C to +150°C<br>300°C<br>UNITS         |  |

| Storage Temperature Lead Temperature PACKAGE TYPE  18-Pin Hermetic DIP (X                              | (Soldering, 60 sec)<br>e <sub>jA</sub> (Note 1)            | -65°<br>Θ <sub>JC</sub>  | °C to +150°C<br>300°C<br>UNITS         |  |

| Storage Temperature Lead Temperature PACKAGE TYPE  18-Pin Hermetic DIP (X  18-Pin Plastic DIP (P)      | (Soldering, 60 sec)  (P <sub>JA</sub> (Note 1)  79  70     | Θ <sub>jc</sub> 11 30    | °C to +150°C<br>300°C<br>UNITS<br>•C/W |  |

| Storage Temperature  PACKAGE TYPE  18-Pin Hermetic DIP (X  18-Pin Plastic DIP (P)  20-Contact LCC (RC) | (Soldering, 60 sec)  (P <sub>JA</sub> (Note 1)  79  70  88 | Θ <sub>jc</sub> 11 30 33 | *C to +150°C 300°C UNITS               |  |

#### NOTE:

- Θ<sub>|A</sub> is specified for worst case mounting conditions, i.e., Θ<sub>|A</sub> is specified for device in socket for CerDIP, P-DIP, and LCC packages: Θ<sub>|A</sub> is specified for device soldered to printed circuit board for SOL and PLCC packages.

- CAUTION:

- Do not apply voltages higher than V<sub>DD</sub> or less than GND potential on any terminal except V<sub>REF</sub> (Pin 17) and R<sub>FB</sub> (Pin 18).

The digital control inputs are zener protected; however, permanent damage

- The digital control inputs are zener protected; however, permanent damage may occur on unprotected units from high-energy electrostatic fields. Keep units in conductive foam at all times until ready to use.

- 3. Use proper antistatic handling procedures.

- Absolute Maximum Ratings apply to both packaged devices and DICE. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device.

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$  = +15V,  $V_{REF}$  = +10V,  $V_{OUT,1}$  =  $V_{OUT,2}$  = 0V;  $T_A$  = -55°C to +125°C apply for PM-7541AAX/BX/ARC/BRC;  $T_A$  = -40°C to +85°C apply for PM-7541AEX/FX/FP/FPC/FS; and  $T_A$  = 0°C to +70°C apply for PM-7541AGP, unless otherwise noted.

| PARAMETER                                                      | SYMBOL            | CONDITIONS                                                                                                                  | MIN         | TYP                   | MAX              | UNITS  |

|----------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------|------------------|--------|

| STATIC ACCURACY                                                |                   |                                                                                                                             |             |                       |                  |        |

| Resolution                                                     | N                 |                                                                                                                             | 12          | _                     | _                | LSB    |

| Nonlinearity<br>(Note 1)                                       | INL               |                                                                                                                             | _           | -                     | ±1/2             | LSB    |

| Differential Nonlinearity (Note 2)                             | DNL               | PM-7541AA/E/G<br>PM-7541AB/F                                                                                                |             |                       | ±1/2<br>±1       | LSB    |

| Gain Error<br>(Note 3)                                         | G <sub>FSE</sub>  | T <sub>A</sub> = +25°C<br>PM-7541AA/E/G<br>PM-7541AB/F<br>T <sub>A</sub> = Full Temp. Range<br>PM-7541AA/E/G<br>PM-7541AB/F | -<br>-<br>- | -<br>-<br>-<br>-      | †<br>2<br>2<br>3 | LSB    |

| Gain Tempco<br>(\(\Delta\Gain\subset\Delta\Temp.\)<br>(Note 6) | TC <sub>GFS</sub> |                                                                                                                             | _           | ±2                    | ±5               | ppm/°C |

| Power Supply Rejection Ratio (ΔGain/ΔV <sub>DO</sub> )         | PSRR              | $\Delta V_{DD} = \pm 5\%$ $T_A = +25^{\circ}C$ $T_A = Full Temp. Range$                                                     |             | -<br>-                | ±0.001<br>±0.002 | %/%    |

| Output Leakage Current<br>(Notes 4, 5)                         | ILKG              | $T_A = +25^{\circ}\text{C}$<br>PM-7541AA/B/E/F/G<br>$T_A = \text{Full Temp. Range}$<br>PM-7541AA/B<br>PM-7541AE/F/G         | -<br>-<br>- | -<br>-<br>-           | 5<br>100<br>10   | nA     |

| Zero Scale Error<br>(Notes 12, 13)                             | l <sub>ZSE</sub>  | $T_A = +25^{\circ}$ C<br>PM-7541AA/B/E/G<br>$T_A =$ Full Temp. Range<br>PM-7541AA/B<br>PM-7541AE/F/G                        | -<br>-<br>- | 0.002<br>0.05<br>0.01 | -                | LSB    |

| REFERENCE INPUTS                                               |                   |                                                                                                                             |             |                       |                  |        |

| Input Resistance<br>(Note 9)                                   | R <sub>REF</sub>  |                                                                                                                             | 7           | 11                    | 15               | kΩ     |

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$  = +15V,  $V_{REF}$  = +10V,  $V_{OUT~1}$  =  $V_{OUT~2}$  = 0V;  $T_A$  = -55°C to +125°C apply for PM-7541AAX/BX/ARC/BRC;  $T_A$  = -40°C to +85°C apply for PM-7541AEX/FX/FP/FPC/FS; and  $T_A$  = 0°C to +70°C apply for PM-7541AGP, unless otherwise noted. Continued

| PARAMETER                                                                | SYMBOL             | CONDITIONS                                                                                       | MIN | TYP      | MAX        | UNITS             |

|--------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------|-----|----------|------------|-------------------|

| POWER SUPPLY                                                             |                    |                                                                                                  |     |          |            |                   |

| V <sub>DD</sub> Range                                                    | V <sub>DD</sub>    | Accuracy is not guaranteed over this range                                                       | +5  | 15       | +17        | V                 |

|                                                                          |                    | Digital Inputs = V <sub>IH</sub> or V <sub>IL</sub>                                              | _   |          | 2          | mA                |

| Supply Current                                                           | IDD                | Digital Inputs = 0V or V <sub>DD</sub> T <sub>A</sub> = +25°C  T <sub>A</sub> = Full Temp. Range |     | _        | 100<br>100 | μА                |

| DIGITAL INPUTS                                                           |                    |                                                                                                  |     |          |            |                   |

| Digital Input High                                                       | V <sub>IH</sub>    |                                                                                                  | 2.4 | _        | _          | V                 |

| Digital Input Low                                                        | V <sub>IL</sub>    |                                                                                                  | _   |          | 0.8        | V                 |

| Input Leakage Current<br>(Note 10)                                       | I <sub>IL</sub>    | V <sub>IN</sub> = 0 to +15V                                                                      | _   | _        | ±1         | μА                |

| Input Capacitance<br>(Note 6)                                            | C <sub>IN</sub>    | V <sub>IN</sub> = 0V                                                                             | -   | _        | 8          | pF                |

| DYNAMIC PERFORMANCE                                                      |                    |                                                                                                  |     |          |            |                   |

| Propagation Delay<br>(Notes 6, 7)                                        | t <sub>PD</sub>    | From Digital Input Change<br>to 90% of Final Analog Output<br>T <sub>A</sub> = +25°C             | _   | 100      | 150        | ns                |

| Output Current Settling Time<br>(Notes 6, 7, 8)                          | t <sub>S</sub>     | To $\pm 1/2$ LSB ( $\pm 0.01\%$ of Full Scale Range)<br>T <sub>A</sub> = $+25$ °C                | _   | 0.6      | 1          | μs                |

| Feedthrough Error<br>(V <sub>REF</sub> to I <sub>OUT</sub> )<br>(Note 6) | FT                 | $V_{REF} = 20V_{p^*p}$ @ f = 10kHz<br>All Digital Inputs Low<br>$T_A = -25^{\circ}$ C            | _   | 2        | 5          | mV <sub>p−p</sub> |

| Digital to Analog Glitch Energy<br>(Notes 6, 11)                         | Q                  | T <sub>A</sub> = -25°C                                                                           | _   | 700      | 1000       | nVs               |

| ANALOG OUTPUTS                                                           |                    |                                                                                                  |     |          |            |                   |

| Output Capacitance                                                       | C <sub>OUT 1</sub> | Digital Inputs = V <sub>IH</sub>                                                                 | _   | 85<br>30 | 120<br>50  | pF                |

| (Note 6)                                                                 | C <sub>OUT 1</sub> | Digital Inputs = V <sub>IL</sub>                                                                 | _   | 30<br>85 | 50<br>120  | μ.                |

# NOTES:

- 1.  $\pm 1/2$  LSB =  $\pm 0.012\%$  of Full Scale.

- 2. All grades are monotonic to 12-bits over temperature.

- 3. Using internal feedback resistor.

- 4. Applies to  $I_{OUT,1}$ ; digital inputs =  $V_{IL}$ .

- 5. Specification also applies for I<sub>OUT 2</sub> with all digital inputs = V<sub>IH</sub>.

- 6. Guaranteed by design and not tested.

- 7.  $I_{OUT}$  Load =  ${}^{\circ}00\Omega$ ,  $C_{EXT}$  = 13pF, digital inputs = 0V to  $V_{DD}$  or  $V_{DD}$  to 0V.

- 8. Extrapolated to 1/2 LSB:  $t_{\rm S}$  = Propagation Delay ( $t_{\rm PD}$ ) + 9 $\tau$ , where  $\tau$  = measured first time constant of the final RC decay.

- 9. Absolute temperature coefficient is approximately +50 ppm/°C.

- 10. Digital inputs are CMOS gates; I<sub>IN</sub> is typically 1nA at +25°C.

- 11. V<sub>REF</sub> = 0V, all digital inputs = 0V to V<sub>DD</sub> or V<sub>DD</sub> to 0V.

- 12.  $V_{REF} = +10V$ , all digital inputs = 0V. 13. Calculated from:  $I_{ZSE}$ (in LSBs) =  $\frac{R_{REF}(4096)I_{LKG}}{V}$

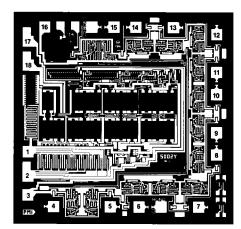

## **DICE CHARACTERISTICS**

DIE SIZE  $0.102 \times 0.100$  inch, 10,200 sq. mils  $(2.59 \times 2.54$  mm, 6.58 sq. mm)

- 1. CURRENT OUTPUT 1

- 2. CURRENT OUTPUT 2

- 3. GROUND

- 4. DIGITAL INPUT (BIT 1) (MOST SIGNIFICANT BIT)

- 5. DIGITAL INPUT (BIT 2)

- 6. DIGITAL INPUT (BIT 3)

- 7. DIGITAL INPUT (BIT 4)

- 8. DIGITAL INPUT (BIT 5)

- 9. DIGITAL INPUT (BIT 6)

- 10. DIGITAL INPUT (BIT 7)

- 11. DIGITAL INPUT (BIT 8)

- 12. DIGITAL INPUT (BIT 9)

- 13. DIGITAL INPUT (BIT 10)

- 14. DIGITAL INPUT (BIT 11)

- 15. DIGITAL INPUT (BIT 12) (LEAST SIGNIFICANT BIT)

- 16. POSITIVE POWER SUPPLY

- 17. REFERENCE INPUT VOLTAGE

- 18. INTERNAL FEEDBACK RESISTOR

# **WAFER TEST LIMITS** at $V_{DD} = +15V$ , $V_{REF} = +10V$ , AGND = DGND = 0V, $V_{OUT~1} = V_{OUT~2} = 0V$ , $T_A = +25^{\circ}C$ .

| PARAMETER                                                | SYMBOL           | CONDITIONS                                                                 | PM-7541AG<br>LIMIT | UNITS            |  |

|----------------------------------------------------------|------------------|----------------------------------------------------------------------------|--------------------|------------------|--|

| STATIC ACCURACY                                          | 31,3302          |                                                                            |                    | UNITS            |  |

| Resolution                                               | N                |                                                                            | 12                 | Bits MIN         |  |

| Nonlinearity                                             | INL              |                                                                            | ±1/2               | LSB MAX          |  |

| Differential Nonlinearity                                | DNL              |                                                                            | ±1                 | LSB MAX          |  |

| Gain Error<br>(Note 1)                                   | G <sub>FSE</sub> |                                                                            | ±1                 | LSB MAX          |  |

| Power Supply Rejection                                   | PSRR             | $\Delta V_{DD} = \pm 5\%$                                                  | ±0.001             | %/% MAX          |  |

| Output Leakage Current (I <sub>OUT 1</sub> )<br>(Note 2) | I <sub>LKG</sub> | Digital Inputs = V <sub>IL</sub>                                           | ±5                 | nA MAX           |  |

| REFERENCE INPUT                                          |                  |                                                                            |                    |                  |  |

| Input Resistance                                         | R <sub>REF</sub> |                                                                            | 7/15               | kΩ MIN/MAX       |  |

| DIGITAL INPUTS                                           |                  |                                                                            |                    |                  |  |

| Digital Input High                                       | V <sub>IH</sub>  |                                                                            | 2.4                | V MIN            |  |

| Digital Input Low                                        | VIL              |                                                                            | 0.8                | V MAX            |  |

| Input Leakage Current                                    | I <sub>IL</sub>  | V <sub>IN</sub> = 0 to 15V                                                 | ±1                 | μΑ MAX           |  |

| POWER SUPPLY                                             |                  |                                                                            |                    |                  |  |

| Supply Current                                           | I <sub>DD</sub>  | Digital Inputs = $V_{IH}$ or $V_{IL}$<br>Digital Inputs = $0V$ or $V_{DD}$ | 2<br>100           | mA MAX<br>µA MAX |  |

# NOTES:

- 1. Using internal feedback resistor.

- 2. Specification also applies for  $I_{OUT\ 2}$  but all Digital Inputs =  $V_{IH}$ .

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

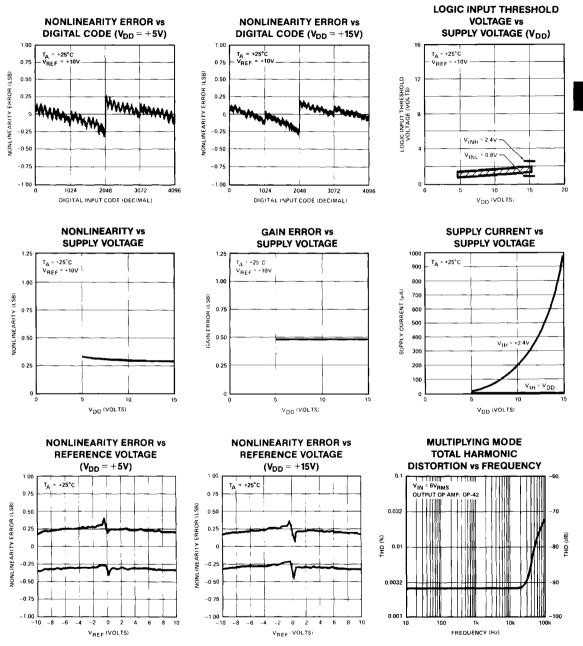

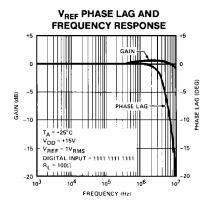

# TYPICAL PERFORMANCE CHARACTERISTICS

### TYPICAL PERFORMANCE CHARACTERISTICS

#### SPECIFICATION DEFINITIONS

#### RESOLUTION

The resolution of a DAC is the number of states (2<sup>n</sup>) that the full-scale range (FSR) is divided (or resolved) into, where "n" is equal to the number of bits.

#### SETTLING TIME

Time required for the analog output of the DAC to settle to within 1/2 LSB of its final value for a given digital input stimulus; i.e., zero to full scale.

#### **GAIN**

Ratio of the DAC's external operational amplifier output voltage to the  $V_{\text{REF}}$  input voltage when all digital inputs are HIGH.

#### **FEEDTHROUGH ERROR**

Error caused by capacitive coupling from  $V_{\mbox{\scriptsize REF}}$  to output with all switches OFF.

#### **OUTPUT CAPACITANCE**

Capacitance from I<sub>OUT 1</sub> or I<sub>OUT 2</sub> terminals to ground.

#### **OUTPUT LEAKAGE CURRENT**

Current which appears on  $\rm I_{OUT~1}$  terminal with all digital inputs LOW, or on  $\rm I_{OUT~2}$  terminal when all inputs are HIGH.

## **CIRCUIT DESCRIPTION**

#### **GENERAL CIRCUIT INFORMATION**

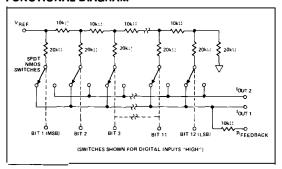

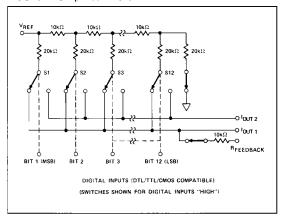

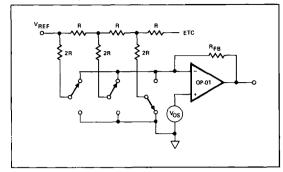

The PM-7541A is a 12-bit multiplying D/A converter consisting of a highly-stable, silicon-chrome, thin film, R-2R resistor ladder network and twelve pairs of NMOS current steering switches on a monolithic chip. Most applications require the addition of a voltage or current reference and an output operational amplifier.

A simplified circuit of the PM-7541A is shown in Figure 1. The R-2R inverted ladder binarily divides the input currents that are switched between I<sub>OUT 1</sub> and I<sub>OUT 2</sub> bus lines. This switching allows a constant current to be maintained in each ladder leg independent of the input code.

The design includes a matching switch in series with the feedback (R<sub>FB</sub>) and terminating resistors. These switches (Figure 1) provide improved gain and linearity performance over the operating temperature range.

FIGURE 1: Simplified DAC Circuit

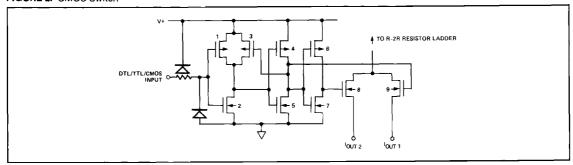

One of the twelve CMOS switches is shown in Figure 2. The digital input stage, devices 1, 2, and 3, drives the two inverters, devices 4, 5, 6, and 7; these inverters in turn drive the two output current steering switches, devices 8 and 9. Devices 1, 2, and 3 are designed such that the digital control inputs are DTL, TTL, and CMOS compatible over the full military temperature range.

The twelve output current-steering switches are in series with the R-2R resistor ladder, and therefore, can introduce bit errors. It is essential then, that the switch "ON" resistance be binarily scaled so that the voltage drop across each switch remains constant. If, for example, switch 1 of Figure 1 were designed with an "ON" resistance of 10 ohms, switch 2 for 20 ohms, etc., then with a 10 volt reference input, the current through switch 1 is 0.5mA, switch 2 is 0.25mA, etc., a constant 5mV drop will then be maintained across each switch.

FIGURE 2: CMOS Switch

To further insure accuracy across the full temperature range, permanently "ON" MOS switches are included in series with the feedback resistor and the R-2R ladder's terminating resistor. These series switches are equivalently scaled to two times switch 1 (MSB) and to switch 12 (LSB) respectively to maintain constant relative voltage drops with varying temperature. During any testing of the resistor ladder or R<sub>FEEDBACK</sub> (such as incoming inspection), V<sub>DD</sub> must be present to turn "ON" these series switches.

#### **ESD PROTECTION**

In the design of the PM-7541A's data inputs, ESD resistance has been incorporated through careful layout and the inclusion of input protection circuitry.

Figure 2 shows the input protection diodes. High voltage static charges applied to the digital inputs are shunted to the supply and ground rails through forward biased diodes. These protection diodes clamp the inputs well below dangerous levels during static discharge conditions.

#### **EQUIVALENT CIRCUIT ANALYSIS**

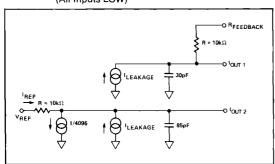

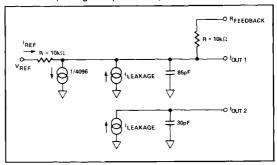

Figures 3 and 4 show the equivalent circuits for all digital inputs LOW and HIGH respectively. The reference current is switched to  $l_{\rm OUT~2}$  when all inputs are LOW and  $l_{\rm OUT~1}$  when inputs are HIGH. The  $l_{\rm LEAKAGE}$  current source is the combination of surface and junction leakages to the substrate; the 1/4096 current source represents the constant 1-bit current drain through the ladder terminating resistor. The output capacitance is dependent upon the digital input code, and is therefore varied between the low and high values.

FIGURE 3: PM-7541A Equivalent Circuit

(All Inputs LOW)

FIGURE 4: PM-7541A Equivalent Circuit (All Digital Inputs HIGH)

## **DYNAMIC PERFORMANCE**

# **OUTPUT IMPEDANCE**

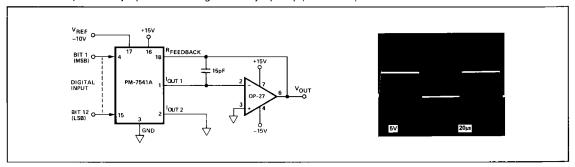

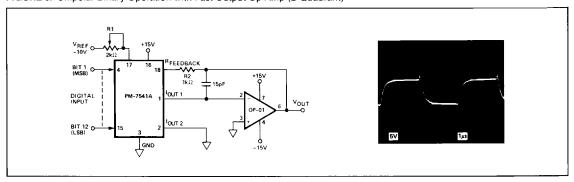

The output resistance, as in the case of the output capacitance, varies with the digital input code. This resistance, looking back into the  $l_{OUT-1}$  terminal, may be between  $10k\Omega$  (the feedback resistor alone when all digital inputs are low) and  $7.5k\Omega$  (the Redback resistor in parallel with approximately  $30k\Omega$  of the R-2R ladder network resistance when any single bit logic is high). Static accuracy and dynamic performance will be affected by these variations. The gain and phase stability of the output amplifier, board layout, and power supply decoupling will all affect the dynamic performance of the PM-7541A. The use of a compensation capacitor may be required when highspeed operational amplifiers are used. It may be connected across the amplifiers feedback resistor to provide the necessary phase compensation to critically damp the output.

The considerations when using high-speed amplifiers are:

- 1. Phase compensation (See Figures 5 and 6).

- Power supply decoupling at the device socket and use of proper grounding techniques.

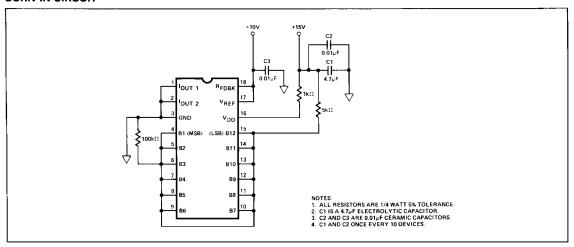

FIGURE 5: Unipolar Binary Operation with High Accuracy Op Amp (2-Quadrant)

FIGURE 6: Unipolar Binary Operation with Fast Output Op Amp (2-Quadrant)

# **BURN-IN CIRCUIT**

## APPLICATIONS INFORMATION

#### **APPLICATION TIPS**

Linearity depends upon the potential of  $I_{OUT\,1}$  and  $I_{OUT\,2}$  (pins 1 and 2) being exactly equal to GND (pin 3). In most applications, the DAC is connected to an external op amp with its noninverting input tied to ground, see Figures 5 and 6. The amplifier selected should have a low input bias current and low drift over temperature. The amplifier's input offset voltage should be nulled to less than  $\pm 200\mu V$  (less than 10% of 1 LSB).

The operational amplifier's noninverting input should have a minimum resistance connection to ground; the usual bias current compensation resistor should not be used. This resistor can cause a variable offset voltage appearing as a varying output error. All grounded pins should tie to a common ground point, avoiding ground loops. The V<sub>DD</sub> power supply should have a low noise level with no transients greater than +17V.

Unused digital inputs must always be grounded or taken to  $V_{DD}$ ; this will prevent noise from triggering the high impedance digital input resulting in output errors. It is also recommended that the used digital inputs be taken to ground or  $V_{DD}$  via a high value (1M $\Omega$ ) resistor; this will prevent the accumulation of static charge if the PC card is disconnected from the system.

Peak supply current flows as the digital inputs pass through the transition voltage. The supply current decreases as the input voltage approaches the supply rails (V<sub>DD</sub> or DGND), i.e., rapidly slewing logic signals that settle very near the supply rails will minimize supply current.

#### **OUTPUT AMPLIFIER CONSIDERATIONS**

For low speed or static applications, AC specifications of the amplifier are not very critical. In high-speed applications, slew rate, settling time, open-loop gain, and gain/phase margin specifications of the amplifier should be selected for the desired performance. It has already been noted that an offset can be caused by including the usual bias current compensation resistor in the amplifier's noninverting input-terminal. This resistor should not be used. Instead, the amplifier should have a bias current which is low over the temperature range of interest.

The static accuracy is affected by the variation in the DAC's output resistance. This variation is best illustrated by using the circuit of Figure 7 and the equation:

Error Voltage =

$$V_{OS} \left( 1 + \frac{R_{FB}}{R_{O}} \right)$$

where  $R_{O}$  is a function of the digital code, and:  $R_{O}\cong 10k\Omega \text{ for more than 4-bits of logic 1}$

$R_0 \approx 30 k\Omega$  for any single bit logic 1

# FIGURE 7: Simplified Circuit

Therefore, the offset gain varies as follows:

At code 0011 1111 1111:

$$V_{ERROR\,1} = V_{OS} \left( \ 1 + \frac{10 k \Omega}{10 k \Omega} \right) = 2 \ V_{OS}$$

The error difference is 2/3 VOS-

Since one LSB has a weight (for  $V_{REF} = +10V$ ) of 2.5mV for the PM-7541A DAC, it is clearly important that  $V_{OS}$  be minimized, either using the amplifier's nulling pins, an external nulling network, or by selection of an amplifier with inherently low  $V_{OS}$ . Amplifiers with sufficiently low  $V_{OS}$  include PMI's OP-77, OP-07, and OP-27.

#### **APPLICATIONS**

Figures 5, 6, and 8 show simple unipolar and bipolar circuits with their associated waveforms using the PM-7541A and two types of PMI output amplifiers. A small feedback capacitor should be used across the amplifier to help prevent overshoot and ringing when using high-speed op amps. Resistor R1 is used to trim for full scale. Low tempco (approximately 50ppm/°C) resistors or trimpots should be selected when gain adjustments are required.

## **UNIPOLAR BINARY OPERATION (2-QUADRANT)**

The circuits of Figures 5 and 6 can be used either as a fixed reference D/A converter, or as an attenuator with an AC input voltage. In the fixed reference mode, the DAC provides an analog output voltage in the range of zero to plus or minus  $V_{REF}$ , depending on  $V_{REF}$  polarity. The reference input voltage can range between  $-20\,V$  to  $+20\,V$ ; this is due to the ability of  $V_{REF}$  to exceed  $V_{DD}$ , the limiting factor being the op amp's voltage range. Table 1 shows the code relationship for the circuit of Figures 5 and 6.  $R_1$  can be omitted with a resulting maximum gain error of 0.02% of full scale.

TABLE 1: Unipolar Binary Code Table

| DIG<br>MSB | ITAL INPUT<br>LSB | NOMINAL ANALOG OUTPUT (V <sub>OUT</sub> as shown in Figures 5 and 6) |

|------------|-------------------|----------------------------------------------------------------------|

| 1111       | 1111 1111         | $-V_{REF} \left( \frac{4095}{4096} \right)$                          |

| 1000       | 0000 0001         | $-V_{REF}\left(\frac{2049}{4096}\right)$                             |

| 1000       | 0000 0000         | $-V_{REF}\left(\frac{2048}{4096}\right) = -\frac{V_{REF}}{2}$        |

| 0111       | 1111 1111         | $-V_{REF}\left(\frac{2047}{4096}\right)$                             |

| 0000       | 0000 0001         | $-V_{REF}\left(\frac{1}{4096}\right)$                                |

| 0000       | 0000 0000         | $-V_{REF}\left(\frac{0}{4096}\right) = 0$                            |

#### NOTES:

- 1. Nominal full scale for the circuits of Figures 5 and 6 is given by  $FS = -V_{REF} \left( \frac{4095}{4096} \right).$

- 2. Nominal LSB magnitude for the circuits of Figures 5 and 6 is given by  $LSB = V_{REF} \left( \frac{1}{4096} \right) \text{ or } V_{REF} \left( 2^{-n} \right).$

#### **BIPOLAR BINARY OPERATION (4-QUADRANT)**

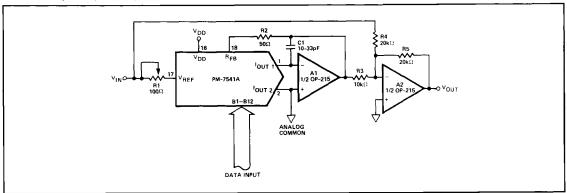

Figure 8 shows a simple bipolar output circuit using the PM-7541A and a PMI OP-215 dual op amp. The circuit uses offset binary coding and a fixed DC voltage for  $V_{REF}$ . Digitally-controlled attenuation of an AC signal occurs when the signal is used as the signal source at  $V_{REF}$ . Negative output full-scale is adjusted by setting the digital inputs to all zeros and adjusting the value of the  $V_{IN}$  voltage or  $R_{5}$ . The zero-scale output voltage is adjusted while the digital inputs are set to 1000 0000 0000 by adjusting  $R_{1}$  for a zero output voltage (less than 10% of 1 LSB). Resistors  $R_{3}$ ,  $R_{4}$ , and  $R_{5}$  must be selected for matching and tracking in order to keep offset and full scale errors to a minimum. Resistors  $R_{1}$  and  $R_{2}$  temperature coefficients must be taken into account if they are used.  $C_{1}$  phase compensation capacitor may not be needed and should be selected empirically. The digital input code versus analog output voltage is shown in Table 2.

TABLE 2: Bipolar (Offset Binary) Code Table

| DIG<br>MSB | ITAL IN | PUT<br>LSB | NOMINAL ANALOG OUTPUT (V <sub>OUT</sub> as shown in Figure 8) |

|------------|---------|------------|---------------------------------------------------------------|

| 1111       | 1111    | 1111       | $+V_{REF}\left(\frac{2047}{2048}\right)$                      |

| 1000       | 0000    | 0001       | $+V_{REF}\left(\frac{1}{2048}\right)$                         |

| 1000       | 0000    | 0000       | 0                                                             |

| 1111       | 1111    | 1111       | $-V_{REF}\left(\frac{1}{2048}\right)$                         |

| 0000       | 0000    | 0001       | $-V_{REF}\left(\frac{2047}{2048}\right)$                      |

| 0000       | 0000    | 0000       | $-V_{REF} \left( \frac{2048}{2048} \right)$                   |

#### NOTES

- 1. Nominal full scale for the circuit of Figure 8 is given by  $FS = V_{REF} \left( \frac{2047}{2048} \right).$

- 2. Nominal LSB magnitude for the circuit of Figure 8 is given by LSB =  $V_{REF} \left( \frac{1}{2048} \right)$ .

FIGURE 8: Bipolar Operation (4-Quadrant Multiplication)

#### ANALOG/DIGITAL DIVISION

The transfer function for the PM-7541A connected in the multiplying mode as shown in Figures 5 and 6 is:

$$V_O = -V_{IN} \left( \frac{A_1}{2^1} + \frac{A_2}{2^2} + \frac{A_3}{2^3} + \dots \frac{A_{12}}{2^{12}} \right)$$

where  $A_x$  assumes a value of 1 for an "ON" bit and 0 for an "OFF" bit. The transfer function is modified when the DAC is connected in the feedback of an operational amplifier as shown in Figure 9. It now is:

$$V_{O} = \left( \frac{-V_{IN}}{\frac{A_{1}}{2^{1}} + \frac{A_{2}}{2^{2}} + \frac{A_{3}}{2^{3}} + \dots + \frac{A_{12}}{2^{12}}} \right)$$

The above transfer function is the division of an analog voltage ( $V_{REF}$ ) by a digital word. The amplifier goes to the rails with all bits "OFF" since division by zero is infinity. With all bits "ON," the gain is 1 ( $\pm$ 1 LSB). The gain becomes 4096 with the LSB, bit 12, "ON."

FIGURE 9: Analog/Digital Divider