## 7261FI-2.x – G.723.1 Full Duplex Codec

D/7261\_FI-2.x/4 June 2016 DATASHEET Advance Information

#### **Features**

- Half-duplex operation

- Full-duplex operation

- Codec support:

- G.723.1 codec (5.3kbps / 6.3kbps rates) with Annex A

- PCM (linear, μ-law, A-law),

- Transcoding support:

- PCM to G.723.1 and reverse

- O PCM μ/A/linear to PCM μ/A/linear transcoder

- No external DSP or codecs required: simply upload Function Image™ (FI)

- Transcoder routing:

- Choice of input sources C-BUS transfer to host, external PCM device/codec, analogue audio input

- Choice of output sources C-BUS transfer to host, external PCM device/codec, analogue audio output

- C-BUS host serial interface

- SPI-like with register addressing

- Read/Write 128-word FIFOs and data buffers to streamline transfers and relax host service latency

- Auxiliary functions

- o Three GPIOs

- Analogue input/output gain adjustment

- Analogue input multiplexer

- o Analogue output multiplexer

- Master/Slave PCM serial interface

- For external audio CODEC

- Low power 3.3V operation with powersave functions

- Small 64-pin VQFN or LQFP package

## **Applications**

- Half duplex digital radio systems

- Full duplex digital radio systems

- Personal area network voice links

- Privacy-type digital voice communications

- Wireless PBX

- VoIP applications

- Digital Software Defined Radio (SDR)

This document contains:

Datasheet

User

Manual

## 1 Brief Description

The CMX7261 Multi-transcoder IC is a device supporting multiple speech codecs in a single chip. When loaded with Fl-2.x the CMX7261 is capable of encoding analogue voice into PCM (linear,  $\mu$ -law or A-law) or G.723.1 data formats at either 5.3kbps or 6.3kbps. It is capable of decoding PCM or G.723.1 (both rates) back to analogue voice. It can also transcode data between PCM formats and G.723.1.

Input and output signals may be passed through the C-BUS interface, the PCM port or the on-chip converters (ADC/DAC).

The device utilises CML's proprietary FirmASIC<sup>®</sup> component technology. On-chip sub-systems are configured by a Function Image<sup>™</sup> data file that is uploaded during device initialisation and defines the device's function and feature set. The Function Image<sup>™</sup> can be loaded automatically from a host  $\mu$ C over the C-BUS serial interface or from an external memory device. The device's functions and features can be enhanced by subsequent Function Image<sup>™</sup> releases, facilitating in-the-field upgrades.

The CMX7261 operates from a 3.3V supply and includes selectable powersaving modes. It is available in a 64-VQFN (Q1) or a 64-LQFP (L9) package.

Note that text shown in pale grey indicates features that will be supported in future versions of the device. This Data Sheet is the first part of a two-part document.

## **CONTENTS**

| <u>Section</u> |                                                       | <u>Page</u> |

|----------------|-------------------------------------------------------|-------------|

| 1              | Brief Description                                     | 2           |

| 2              | History                                               | 5           |

| 3              | Block Diagrams                                        |             |

| 3.1            | Half Duplex Transcoder                                | 6           |

| 3.2            | Full Duplex Transcoder                                | 6           |

| 4              | Pin and Signal List                                   |             |

| 4.1            | Signal Definitions                                    | 11          |

| 5              | PCB Layout Guidelines and Power Supply Decoupling     | 12          |

| 6              | External Components                                   | 13          |

| 6.1            | Xtal Interface                                        |             |

| 6.2            | C-BUS Interface                                       |             |

| 6.3            | PCM and Serial Port Interface                         |             |

| 6.4            | Audio Output                                          |             |

| 6.4.1          | Audio Output Routing                                  |             |

| 6.4.2          | Audio Output Reconstruction Filter                    | 16          |

| 6.5            | Audio Input                                           | 18          |

| 6.5.1          | Audio Input Routing                                   | 18          |

| 6.5.2          | Differential Audio Input                              | 18          |

| 6.5.3          | Single-Ended Audio Input Interface                    |             |

| 6.6            | GPIO Pins                                             | 20          |

| 7              | General Description                                   | 21          |

| 7.1            | CMX7261 Features                                      | 21          |

| 7.2            | Signal Interfaces                                     | 21          |

| 8              | Detailed Descriptions                                 | 23          |

| 8.1            | Xtal Frequency                                        | 23          |

| 8.2            | Host Interface                                        | 23          |

| 8.2.1          | C-BUS Operation                                       | 23          |

| 8.3            | Function Image™ Loading                               | 26          |

| 8.3.1          | FI Loading from Host Controller                       | 26          |

| 8.3.2          | FI Loading from Serial Memory                         | 28          |

| 8.4            | Coding Formats                                        | 29          |

| 8.4.1          | G.711 29                                              |             |

| 8.4.2          | G.723.1                                               | 29          |

| 8.5            | Transcoding Description                               | 30          |

| 8.5.1          | Input and Output Frame Sizes                          | 30          |

| 8.5.2          | Data Transfer Using C-BUS Interface                   | 32          |

| 8.5.3          | Data Formats – Packed and Unpacked                    | 37          |

| 8.6            | Device Control                                        | 39          |

| 8.6.1          | Normal Operation Overview                             | 39          |

| 8.6.2          | Transcoder Operation                                  | 40          |

| 8.6.3          | Device Configuration (Using the Programming Register) | 45          |

| 8.6.4          | Device Configuration (Using dedicated registers)      |             |

| 8.6.5          | Interrupt Operation                                   |             |

| 8.6.6          | PCM Port                                              |             |

| 8.7            | Signal Level Optimisation                             |             |

| 8.7.1          | Audio Output Path Levels                              | 46          |

|                |                                                       |             |

| 8.7.2         | Audio Input Path Levels                                                   | 46          |

|---------------|---------------------------------------------------------------------------|-------------|

| 8.8           | C-BUS Register Summary                                                    | 47          |

| 9             | Performance Specification                                                 | 48          |

| 9.1           | Electrical Performance                                                    | 48          |

| 9.1.1         | Absolute Maximum Ratings                                                  | 48          |

| 9.1.2         | Operating Limits                                                          | 49          |

| 9.1.3         | Operating Characteristics                                                 | 50          |

| 9.1.4         | CMX7261: 7261 FI-2.x Parametric Performance                               | 54          |

| 9.1.5         | C-BUS Timing                                                              |             |

| 9.2           | PCM Port Timing                                                           |             |

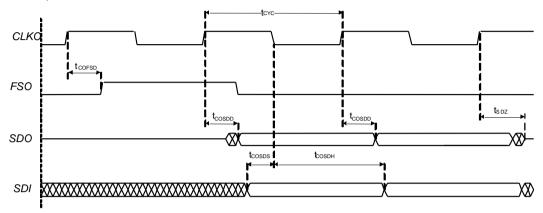

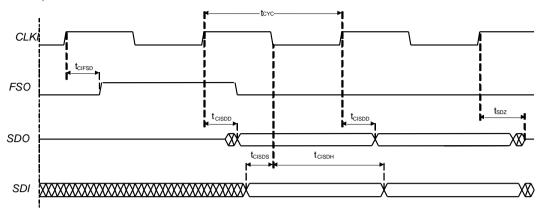

| 9.2.1         | PCM Internal Clock                                                        |             |

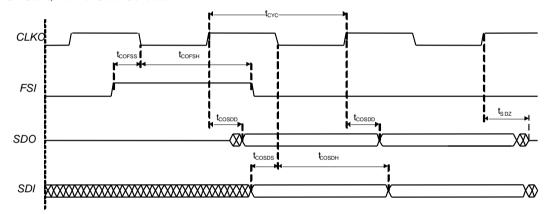

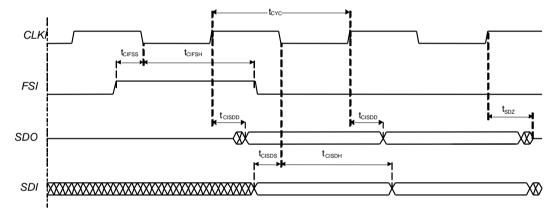

| 9.2.2         | PCM External Clock                                                        |             |

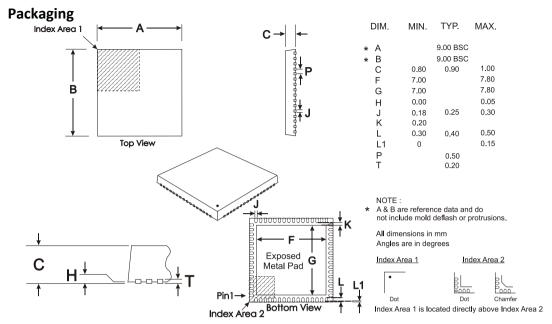

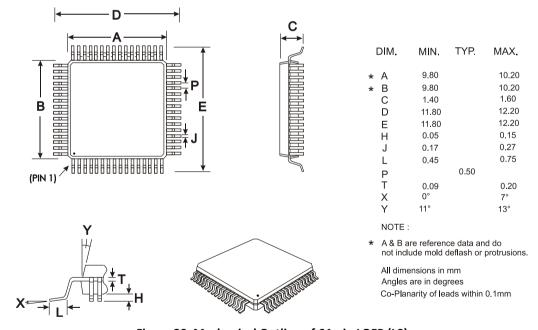

| 9.3           | Packaging                                                                 | 58          |

| <u>Table</u>  |                                                                           | <u>Page</u> |

|               | Input and Output Ports – Full Duplex Mapping                              |             |

|               | Definition of Power Supply and Reference Voltages                         |             |

| Table 3       | BOOTEN Pin States                                                         | 26          |

| Table 4       | Encoding of FIFO Format Registers (\$4A, \$4E) for G.723.1 Operation      | 31          |

| Table 5       | G723.1 Typical Process Times                                              | 31          |

| Table 6       | C-BUS Registers                                                           | 47          |

| <u>Figure</u> |                                                                           | <u>Page</u> |

| Figure 1      | L Block Diagram                                                           | 6           |

| Figure 2      | 2 Full Duplex Block Diagram                                               | 7           |

| •             | . CMX7261 Power Supply and De-coupling                                    |             |

| _             | 1 Recommended External Components – Xtal Interface                        |             |

| _             | 5 Recommended External Components – C-BUS Interface                       |             |

| _             | 5 Interfacing the CMX7261 to an External Codec (master) and Serial Memory |             |

| _             |                                                                           |             |

| _             | 7 Interfacing the CMX7261 to an External Codec (slave) and Serial Memory  |             |

| _             | 3 Analogue Audio Output Routing                                           |             |

| Figure 9      | Recommended External Components – ANAOUT/MONOUT Reconstruction Filter     | 17          |

| Figure 1      | 10 Recommended External Components – Speaker2 Output                      | 17          |

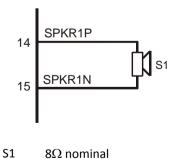

| Figure 1      | 11 Recommended External Components – Speaker1 Output                      | 17          |

| Figure 1      | 12 Analogue Audio Input Routing                                           | 18          |

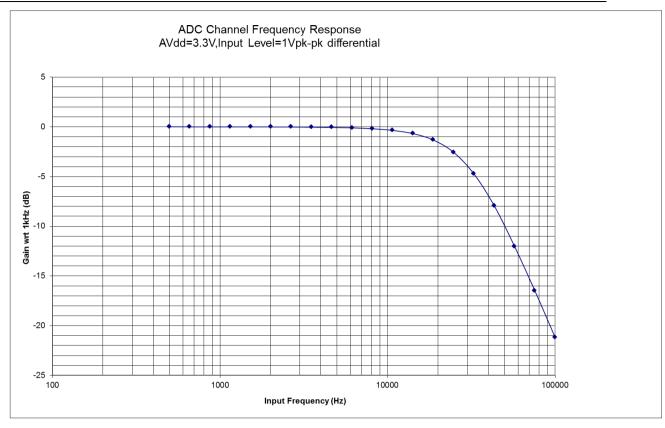

| Figure 1      | 13 ADC Channel Frequency Response                                         | 19          |

| _             |                                                                           |             |

|               | L5 CMX7261 Inputs and Outputs                                             |             |

| _             | 16 Basic C-BUS Transactions                                               |             |

| •             | 17 C-BUS Data-Streaming Operation                                         |             |

|               |                                                                           |             |

| _             | 18 FI Loading from Host                                                   |             |

| _             | 19 FI Loading from Serial Memory                                          |             |

|               | 20 Audio Input and Audio Output FIFOs                                     |             |

| Figure 2      | 21 Input Data Transfer into the CMX7261                                   | 36          |

| Figure 2      | 22 Output Data Transfer from the CMX7261                                  | 37          |

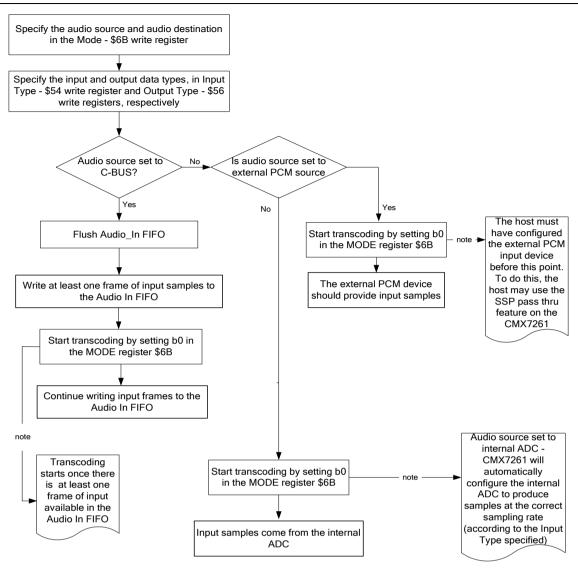

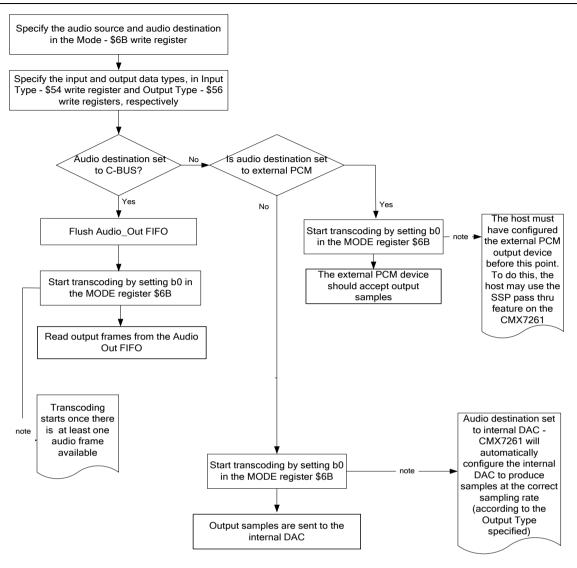

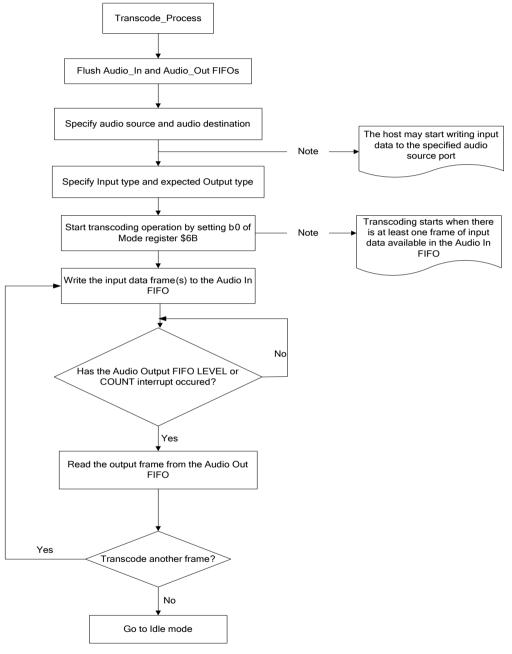

| Figure 2      | 23 Transcoder Operation Flowchart                                         | 40          |

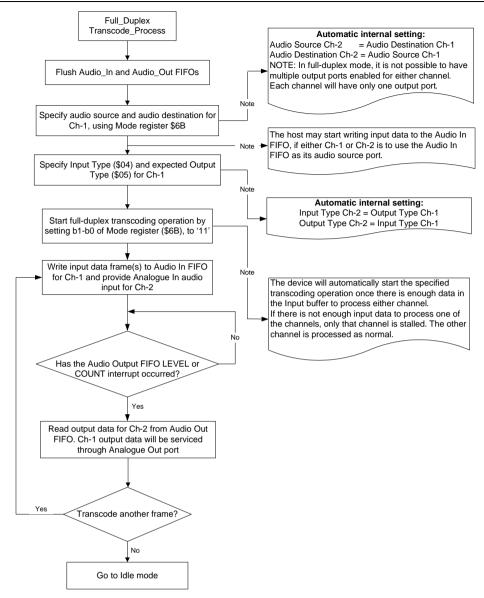

| Figure 2      | 24 Full duplex Transcoder Operation Flowchart                             | 43          |

| _             | 25 C-BUS Timing                                                           |             |

| _             | 26 PCM Internal Clock Timings                                             |             |

| J             |                                                                           |             |

| Figure 27 | PCM External Clock Timings             | 57 |

|-----------|----------------------------------------|----|

| •         | Mechanical Outline of 64-pin VQFN (Q1) |    |

| Figure 29 | Mechanical Outline of 64-pin LQFP (L9) | 58 |

## 2 History

| Version | Changes                                                                  | Date     |

|---------|--------------------------------------------------------------------------|----------|

| 4       | • Section 8.5.1: Added new Table 5 – G723.1 typical Process Times        | 07/06/16 |

|         | Section 9.1.3: Processing delays added to performance characteristics    |          |

|         | • Section 10.1.33: 'New frame Format' and 'New Frame Data' bits added to |          |

|         | IRQ Status register \$7E                                                 |          |

| 3       | Full public release, minor typographical corrections                     | 14/03/16 |

| 2       | First public release                                                     | 01/03/16 |

| 1       | Advance Draft for first alpha release                                    | 21/12/15 |

Information in this data sheet should not be relied upon for final product design. It is recommended that you check for the latest product datasheet version from the CML website: [www.cmlmicro.com].

## 3 Block Diagrams

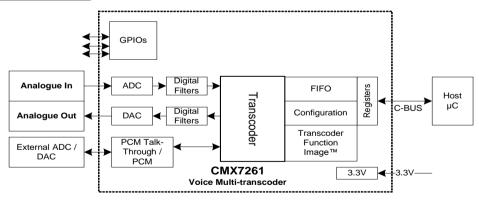

## 3.1 Half Duplex Transcoder

Figure 1 Block Diagram

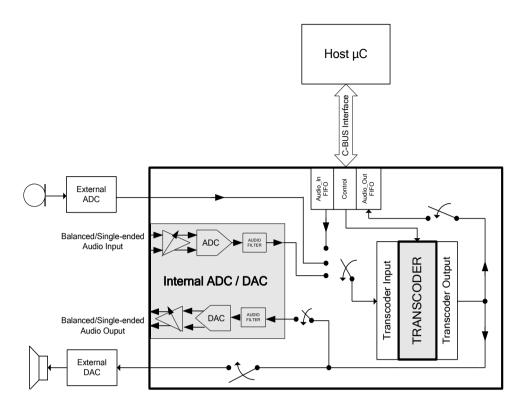

Figure 1 presents a detailed view of the CMX7261, as used in half duplex mode. In Figure 1, the Decoder and the Encoder together form a 'Transcoder Block'. The CMX7261 contains two such 'Transcoder Blocks' (Figure 1 shows only one of them). In full duplex mode both Transcoder Blocks are used, whereas in half duplex mode only one Transcoder Block is used.

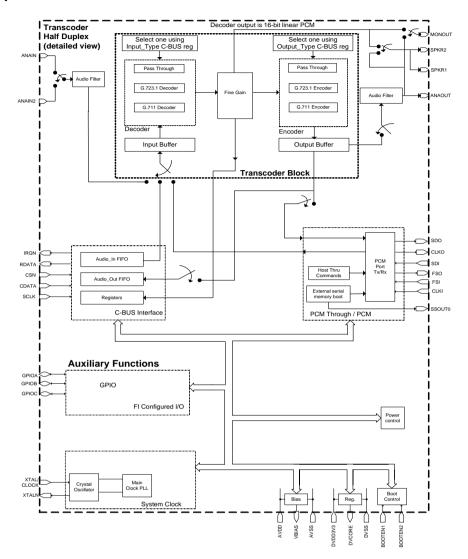

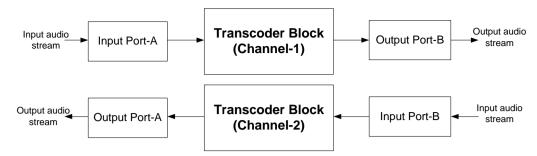

## 3.2 Full Duplex Transcoder

Figure 2 depicts a block level overview of full duplex transcoding operation. Full duplex operation means that a type of transcoding may be specified on one channel, and the opposite transcoding will then be implemented on a second audio stream. For example, if channel-1 is set to transcode from linear PCM to G.723.1, channel-2 will transcode from G.723.1 to linear PCM.

Figure 2 Full Duplex Block Diagram

In full duplex operation, the input and output ports may be specified on one channel and the opposite input and output ports will be used for the second channel.

Table 1 shows the mapping between Input Ports and Output Ports.

Table 1 Input and Output Ports - Full Duplex Mapping

| Input Port-A / B         | ← maps to → | Output Port-A / B          |

|--------------------------|-------------|----------------------------|

| Analogue In              |             | Analogue Out               |

| Audio In FIFO (C-BUS In) |             | Audio Out FIFO (C-BUS Out) |

| PCM Port In              |             | PCM Port Out               |

For example, if channel-1 input port is set to Analogue In and its output port set to Audio Out FIFO, then channel-2 input port will be Audio In FIFO and its output port will be Analogue Out.

## 4 Pin and Signal List

| 64-pin<br>Q1/L9 | Pir      | 1     | Signal Description                                                                                                                                                                                                             |  |

|-----------------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No.         | Name     | Type  |                                                                                                                                                                                                                                |  |

| 1               | CLKI     | IP    | PCM: Serial Clock In.                                                                                                                                                                                                          |  |

| 2               | BOOTEN1  | IP+PD | The combined state of BOOTEN1 and BOOTEN2, upon RESET, determine the Function Image™ load interface.                                                                                                                           |  |

| 3               | BOOTEN2  | IP+PD | The combined state of BOOTEN1 and BOOTEN2, upon RESET, determine the Function Image™ load interface.                                                                                                                           |  |

| 4               | DVSS     | PWR   | Negative supply rail (ground) for the digital on-chip circuits.                                                                                                                                                                |  |

| 5               | DVDD3V3  | PWR   | 3.3V positive supply rail for the digital on-chip circuits. This pin should be decoupled to DVSS by capacitors mounted close to the supply pins.                                                                               |  |

| 6               | GPIOA    | BI    | General Purpose I/O.                                                                                                                                                                                                           |  |

| 7               | RESETN   | IP    | Logic input used to reset the device (active low).                                                                                                                                                                             |  |

| 8               | GPIOB    | ВІ    | General Purpose I/O.                                                                                                                                                                                                           |  |

| 9               | GPIOC    | ВІ    | General Purpose I/O.                                                                                                                                                                                                           |  |

| 10              | DVSS     | PWR   | Negative supply rail (ground) for the digital on-chip circuits.                                                                                                                                                                |  |

| 11              | SPKR2    | ОР    | Single ended output for speaker.                                                                                                                                                                                               |  |

| 12              | AVDD     | PWR   | Positive 3.3V supply rail for the analogue on-chip circuit. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to AVSS by capacitors mounted close to the device pins.     |  |

| 13              | SPKR1VSS | PWR   | Negative supply rail (ground) for the on-chip speaker driver circuit.                                                                                                                                                          |  |

| 14              | SKPR1P   | ОР    | Low impedance differential driver to the external speaker; 'P' is                                                                                                                                                              |  |

| 15              | SPKR1N   | ОР    | positive, 'N' is negative. Together these are referred to as the SPKR1 output.                                                                                                                                                 |  |

| 16              | SPKR1VDD | PWR   | Positive supply rail for the on-chip speaker driver circuit. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to SPKR1VSS by capacitors mounted close to the device pin. |  |

| 17              | ANAOUTP  | ОР    | Differential outputs for main audio; 'P' is positive, 'N' is                                                                                                                                                                   |  |

| 18              | ANAOUTN  | ОР    | negative. Together these are referred to as ANAOUT.                                                                                                                                                                            |  |

| 19              | MONOUTP  | ОР    | Differential outputs for monitor audio; 'P' is positive, 'N' is                                                                                                                                                                |  |

| 20              | MONOUTN  | ОР    | negative. Together these are referred to as MONOUT.                                                                                                                                                                            |  |

| 21              | AVSS     | PWR   | Negative supply rail (ground) for the analogue on-chip circuits                                                                                                                                                                |  |

| 22              | DACREF   |       | DAC reference voltage, connect to AVSS.                                                                                                                                                                                        |  |

| 23              | ANAIN2P  | IP    | Input (IP) and feedback (FB) connections to single ended audio input 2. Gain and filtering circuitry can be constructed around these pins. Together these are referred to as ANAIN2.                                           |  |

| 64-pin<br>Q1/L9 | Pi       | n    | Signal Description                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-----------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin No.         | Name     | Туре |                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 24              | ANAIN2FB | OP   |                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 25              | NC       | NC   |                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 26              | NC       | NC   |                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 27              | VBIAS    | ОР   | Internally generated bias voltage of approximately AVDD/2. If VBIAS is power saved this pin will present a high impedance to AVDD. This pin must be decoupled to AVSS by a capacitor mounted close to the device pins; no other connections should be made.                                                                                                                                       |  |  |  |

| 28              | ANAINP   | IP   | Differential inputs for main audio; 'P' is positive, 'N' is negative.                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 29              | ANAINN   | IP   | Together these are referred to as the ANAIN.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 30              | ADCREF   |      | ADC reference voltage; connect to AVSS.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 31              | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 32              | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 33              | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 34              | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 35              | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 36              | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 37              | AVDD     | PWR  | Positive 3.3V supply rail for the analogue on-chip circuit. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to AVSS by capacitors mounted close to the device pins.                                                                                                                                                                        |  |  |  |

| 38              | AVSS     | PWR  | Negative supply rail (ground) for the analogue on-chip circuits.                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 39              | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 40              | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 41              | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 42              | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 43              | DVSS     | PWR  | Negative supply rail (ground) for the digital on-chip circuits.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 44              | DVCORE1  | PWR  | Digital core supply, nominally 1.8V. By default this will be supplied by an on-chip regulator, although an option is available to use an external regulator. This pin should be decoupled to DVSS by capacitors mounted close to the device pins and connected with a power supply track to DVCORE2. For details see programming register P1.19 in section 11.1.2 Program Block 1 – Clock Control |  |  |  |

| 45              | DVDD3V3  | PWR  | 3.3V positive supply rail for the digital on-chip circuits. This pin should be decoupled to DVSS by capacitors mounted close to the supply pins.                                                                                                                                                                                                                                                  |  |  |  |

| 46              | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 47              | DVSS     | PWR  | Negative supply rail (ground) for the digital on-chip circuits.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 64-pin<br>Q1/L9      | Pin        |       | Signal Description                                                                                                                                                                                                                                                                                                                                                                              |  |

|----------------------|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No.              | Name       | Туре  |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 48                   | DVSS       | PWR   | Negative supply rail (ground) for the digital on-chip circuits.                                                                                                                                                                                                                                                                                                                                 |  |

| 49                   | XTALN      | ОР    | Output of the on-chip xtal oscillator inverter.                                                                                                                                                                                                                                                                                                                                                 |  |

| 50                   | XTAL/CLOCK | IP    | Input to the oscillator inverter from the xtal circuit or external clock source.                                                                                                                                                                                                                                                                                                                |  |

| 51                   | NC         | NC    | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 52                   | NC         | NC    | Do not connect.                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 53                   | SCLK       | IP    | C-BUS serial clock input from the μC.                                                                                                                                                                                                                                                                                                                                                           |  |

| 54                   | RDATA      | TS OP | 3-state C-BUS serial data output to the $\mu$ C. This output is high impedance when not sending data to the $\mu$ C.                                                                                                                                                                                                                                                                            |  |

| 55                   | CDATA      | IP    | C-BUS serial data input from the μC.                                                                                                                                                                                                                                                                                                                                                            |  |

| 56                   | CSN        | IP    | C-BUS chip select input from the μC.                                                                                                                                                                                                                                                                                                                                                            |  |

| 57                   | IRQN       | OP    | 'wire-Orable' output for connection to the Interrupt Request input of the $\mu$ C. This output is pulled down to DVSS when active and is high impedance when inactive. An external pull-up resistor is required.                                                                                                                                                                                |  |

| 58                   | DVCORE2    | PWR   | Digital core supply, nominally 1.8V. Normally this will be supplied by the on-chip regulator, although an option is available to use an external regulator. This pin should be decoupled to DVSS by capacitors mounted close to the devic pins and connected with a power supply track to DVCORE1. If details see programming register P1.19 in section 11.1.2 Program Block 1 – Clock Control. |  |

| 59                   | SDO        | ОР    | While booting FI: SPI: Master Out Slave In (MOSI). While running FI: PCM: Serial Data Out.                                                                                                                                                                                                                                                                                                      |  |

| 60                   | FSO        | ОР    | PCM: Frame Sync Out.                                                                                                                                                                                                                                                                                                                                                                            |  |

| 61                   | SDI        | IP    | While booting FI: SPI: Master In Slave Out (MISO). While running FI: PCM: Serial Data In.                                                                                                                                                                                                                                                                                                       |  |

| 62                   | SSOUT0     | ОР    | SPI: Slave Select Out 0.                                                                                                                                                                                                                                                                                                                                                                        |  |

| 63                   | CLKO       | ОР    | While booting FI: SPI: Serial Clock (SCLK). While running FI: PCM: Serial Clock Out.                                                                                                                                                                                                                                                                                                            |  |

| 64                   | FSI        | BI    | PCM: Frame Sync In.                                                                                                                                                                                                                                                                                                                                                                             |  |

| Exposed<br>Metal Pad | SUBSTRATE  | ~     | On this device, the central metal pad (which is exposed on the Q1 package only) may be electrically unconnected or, alternatively, may be connected to Analogue ground (AV <sub>SS</sub> ). No other electrical connection is permitted.                                                                                                                                                        |  |

Notes: IP = Input (+ PU/PD = internal pull-up / pull-down resistor)

OP = Output

BI = Bidirectional

TS OP = 3-state Output

PWR = Power Connection

NC = No Connection - should NOT be connected to any signal

## 4.1 Signal Definitions

## Table 2 Definition of Power Supply and Reference Voltages

| Signal Name         | Pins                | Usage                                                            |  |  |  |

|---------------------|---------------------|------------------------------------------------------------------|--|--|--|

| $AV_{DD}$           | AVDD                | Power supply for analogue circuits                               |  |  |  |

| DV <sub>SS</sub>    | DVSS                | OVSS Ground for all digital circuits                             |  |  |  |

| $V_{BIAS}$          | VBIAS               | Internal analogue reference level, derived from AV <sub>DD</sub> |  |  |  |

| DV <sub>DD3v3</sub> | DVDD3V3             | 3.3V positive supply rail for the digital on-chip circuits       |  |  |  |

| DV <sub>CORE</sub>  | DVCORE1,<br>DVCORE2 | Power for digital core voltage of approximately 1.8V             |  |  |  |

| AV <sub>SS</sub>    | AVSS                | Ground for all analogue circuits                                 |  |  |  |

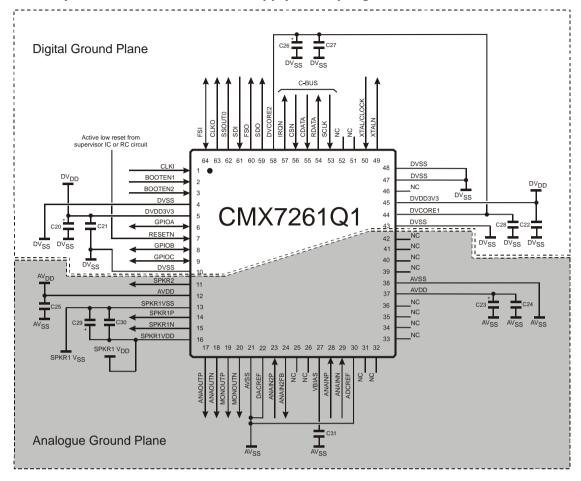

## PCB Layout Guidelines and Power Supply Decoupling

| C20 | 10μF | C26 | 22μF  |

|-----|------|-----|-------|

| C21 | 10nF | C27 | 10nF  |

| C22 | 10nF | C28 | 10nF  |

| C23 | 10μF | C29 | 10μF  |

| C24 | 10nF | C30 | 10nF  |

| C25 | 10nF | C31 | 100nF |

Figure 3 CMX7261 Power Supply and De-coupling

#### Notes:

5

To achieve good noise performance, VDD and VBIAS decoupling and protection of the receive path from extraneous in-band signals are very important. It is recommended that the printed circuit board is laid out with a ground plane in the CMX7261 area to provide a low impedance connection between the VSS pins and the VDD and VBIAS decoupling capacitors.

## 6 External Components

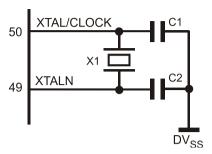

#### 6.1 Xtal Interface

- X1 For frequency range see section 9.1.2 Operating Limits

- C1 22pF Typical

- C2 22pF Typical

Figure 4 Recommended External Components - Xtal Interface

#### Notes:

- The clock circuit can operate with either a xtal or external clock generator. If using an external clock generator it should be connected to the XTAL/CLOCK pin and the xtal and other components are not required. For external clock generator frequency range see section 9.1.2 Operating Limits. When using an external clock generator the XTAL oscillator circuit may be disabled to save power, see 11.1.2 Program Block 1 Clock Control for details.

- The tracks between the xtal and the device pins should be as short as possible to achieve maximum stability and best start up performance. It is also important to achieve a low impedance connection between the xtal capacitors and the ground plane.

- The DVSS to the xtal oscillator capacitors C1 and C2 should be of low impedance and preferably be part of the DVSS ground plane to ensure reliable start up. For correct values of capacitors, C1 and C2 refer to the documentation of the xtal used.

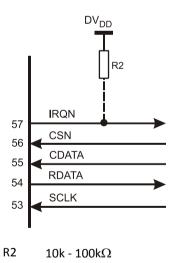

## 6.2 C-BUS Interface

Figure 5 Recommended External Components - C-BUS Interface

Note: If the IRQN line is connected to other compatible pull-down devices only one pull-up resistor is required on the IRQN node.

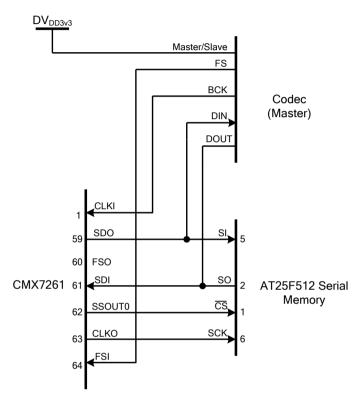

## 6.3 PCM and Serial Port Interface

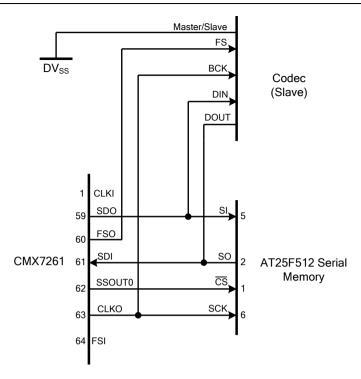

The CMX7261 can be connected to an external codec using its PCM port. The CMX7261 can also load its FI from an external serial memory. Pins 59, 61 and 63 act as serial port pins whilst booting the FI and as PCM pins whilst the FI is in operation. For more information refer to section 4 Pin and Signal List.

Booting from an external serial memory or connecting with an external codec are both optional.

The schematic in Figure 6 shows the connections required when using an external codec with the CMX7261 as a slave device. The schematic also shows the connections required for interfacing to an external serial memory for FI booting.

Figure 6 Interfacing the CMX7261 to an External Codec (master) and Serial Memory

The schematic in Figure 7 shows the connections required when using an external codec as a slave device to the CMX7261. The schematic also shows the connections required for interfacing to an external serial memory for FI booting.

Hardware design must ensure that, when booting from external serial memory, no device other than the external serial memory drives the serial port interface pins.

Figure 7 Interfacing the CMX7261 to an External Codec (slave) and Serial Memory

## 6.4 Audio Output

## 6.4.1 Audio Output Routing

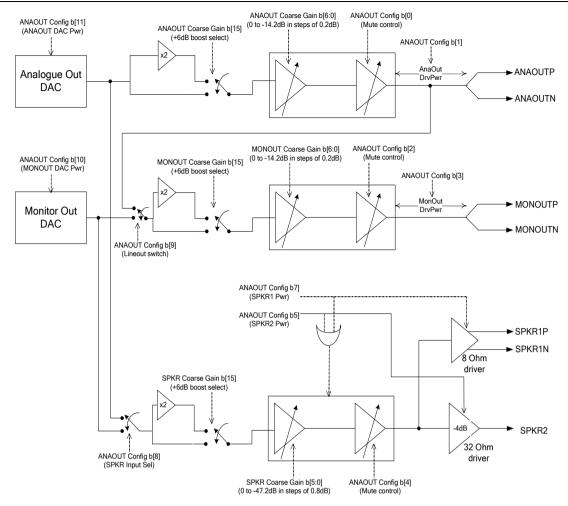

The CMX7261 has four possible analogue outputs: two differential outputs – ANAOUT and MONOUT, a low impedance differential output speaker driver – SPKR1 and a single ended output – SPKR2, that can drive a headset/earpiece.

The CMX7261's two DACs (Analogue Out DAC and Monitor Out DAC) can output analogue waveforms on any or all of the four outputs (ANAOUT, MONOUT, SPKR1 and SPKR2). Figure 8 Analogue Audio Output Routing, shows the analogue output signal routing and control.

Figure 8 Analogue Audio Output Routing

The registers that control the analogue audio output routing are:

- 10.1.27 ANAOUT Config \$B3 write

- 10.1.28 ANAOUT Coarse Gain \$B4 write

- 10.1.29 MONOUT Coarse Gain \$B5 write

- 10.1.30 SPKR Coarse Gain \$B6 write

NOTE: If lower operating current is desired, it is recommended that unused outputs be powered down using the ANAOUT Config - \$B3 write register.

#### 6.4.2 Audio Output Reconstruction Filter

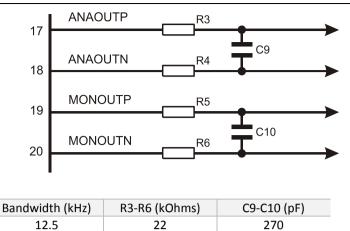

The CMX7261 ANAOUT and MONOUT outputs provide internal reconstruction filtering. To complete the reconstruction filter, the external RC network shown in Figure 9 should be used for each of the differential outputs.

The SPKR1 and SPKR2 outputs do not need any external reconstruction filter.

Figure 9 Recommended External Components - ANAOUT/MONOUT Reconstruction Filter

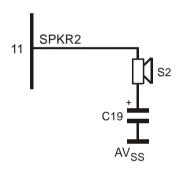

The CMX7261 SPKR2 output provides a single ended audio output that can be used to drive an earpiece or headphone, as shown in Figure 10.

S2  $32\Omega$  nominal C19  $100\mu F$

Figure 10 Recommended External Components - Speaker2 Output

The CMX7261 SPKR1 output can be used to drive a speaker as shown in Figure 11.

Figure 11 Recommended External Components - Speaker1 Output

Care should be taken to avoid shorting any of the speaker outputs to one another or to VSS or VDD. An external RC filter may be added across SPKR1P and SPKR1N pins if clock noise needs further reduction.

## 6.5 Audio Input

## 6.5.1 Audio Input Routing

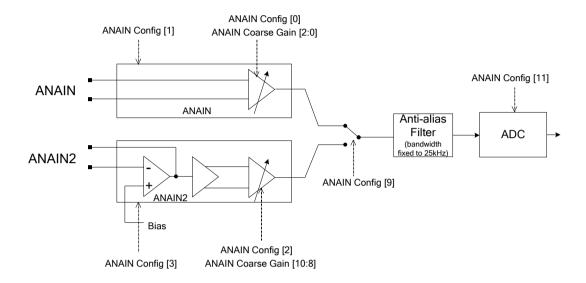

The CMX7261 has two possible analogue inputs: a differential input – ANAIN and a single ended input – ANAIN2.

The CMX7261's ADC can sample any one of the two analogue inputs. Figure 12 shows the analogue input signal routing and control.

Figure 12 Analogue Audio Input Routing

The registers that control the analogue audio input routing are:

- 10.1.25 ANAIN Config \$B0 write

- 10.1.26 ANAIN Coarse Gain \$B1 write

NOTE: If lower operating current is desired, it is recommended that unused inputs be powered down using the ANAIN Config - \$B0 write register.

#### 6.5.2 Differential Audio Input

The device has a 25kHz anti-alias low-pass filter in the analogue audio input path which should be sufficient for most applications; however, if additional filtering is required it can be done at the input to the device. The frequency response (including the anti-alias filter) is shown in Figure 13.

Figure 13 ADC Channel Frequency Response

The input impedance of the ANAIN pins varies with the input gain setting, see section 9.1.3 Operating Characteristics.

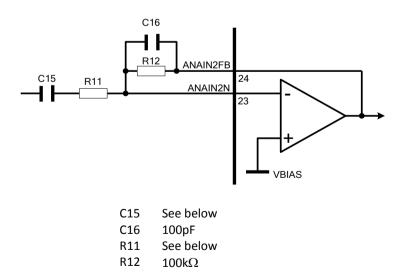

## 6.5.3 Single-Ended Audio Input Interface

A single ended input can be connected to the CMX7261 using the ANAIN2 pins. Gain and filtering circuitry can be constructed around these pins, as shown in Figure 14.

Figure 14 Recommended External Components - Single-Ended Audio Input Interface

R11 should be selected to provide the required DC gain (assuming C15 is not present) as follows:

$$|GAIN_{ANAIN2}| = 100k\Omega/R11$$

The gain should be such that the resultant output at the pins is within the input signal range.

C15 should be selected to maintain the lower frequency roll-off of the ANAIN2 input as follows:

$$C15 \geq 0.1 \mu F \quad X \quad |GAIN_{ANAIN2}|$$

The high frequency cut off

$$=\left(\frac{1}{2\pi .R12.C16}\right)$$

The low frequency cut off

$$=\left(\frac{1}{2\pi .R11.C15}\right)$$

## 6.6 GPIO Pins

All GPIO pins are configured as inputs with an internal bus-hold circuit, after the Function Image<sup> $\mathbf{M}$ </sup> has been loaded. This avoids the need for users to add external termination (pullup/pulldown) resistors onto these inputs. The bus-hold is equivalent to a  $75k\Omega$  resistor either pulling up to logic 1 or pulling down to logic 0. As the input is pulled to the opposite logic state by the user, the bus-hold resistor will change, so that it also pulls to the new logic state. The internal bus-hold can be disabled or re-enabled using programming register P1.20 in Program Block 1 – Clock Control.

## 7 General Description

#### 7.1 CMX7261 Features

The CMX7261 is a multi-transcoder chip that performs encoding and decoding of various vocoder standard formats. When loaded with FI-2 the CMX7261 will encode and decode linear PCM, G.711 (A-law and  $\mu$ -law) and G.723.1, as well as transcoding between these standards. The CMX7261 can be operated either as a half duplex or as a full duplex transcoder. Full duplex operation means that a type of transcoding may be specified on one channel and the opposite transcoding will then be implemented on a second audio stream.

A flexible power control facility allows the device to be placed in its optimum powersave mode when not actively processing signals.

The device includes a crystal clock generator, with phase locked loop to enable operation from a range of reference xtal frequencies.

Block diagrams of the device are shown in Figure 1.

#### **Encoder Functions:**

- Analogue voice to PCM encoding ( $\mu$ -law or A-law according to G.711 standard).

- Analogue voice to G.723.1 encoding.

#### **Decoder Functions:**

- PCM decoding to analogue voice.

- G.723.1 decoding to analogue voice.

#### Transcoder Functions (Half-Duplex):

- PCM μ / A / linear to G.723.1 transcoding.

- PCM  $\mu$  / A / linear to PCM  $\mu$  / A / linear transcoding.

#### **Transcoder Functions (Full-Duplex):**

- Two separate audio streams (channel-1, channel-2) are processed simultaneously.

- Channel-1 may process audio using a Decoder, Encoder or Transcoder function.

- Channel-2 will process audio in the reverse manner to channel-1. For example, if channel-1 is configured to transcode from linear PCM to G.723.1, channel-2 will transcode from G.723.1 to linear PCM.

#### Interface:

- Optimised C-BUS (4-wire, high speed synchronous serial command/data bus) interface to host for control and data transfer, including streaming C-BUS for efficient data transfer.

- Input data can come through the analogue audio input or, C-BUS or from an external PCM device connected to CMX7261's PCM port.

- Output data can be sent to the analogue audio output or, C-BUS or, to an external PCM device connected to CMX7261's PCM port.

- Open drain IRQ to host.

- Three GPIO pins.

- Serial memory or C-BUS (host) boot mode.

#### 7.2 Signal Interfaces

In half duplex mode the transcoder output can be sent to one, any two, or all of the three possible output ports – C-BUS (for transfer to host controller), PCM (for transfer to external DAC) or analogue audio output. In full duplex mode a single output must be selected. The input to the transcoder must come from one of the three input ports – C-BUS (input data from the host controller), PCM (from the external ADC) or analogue audio input.

Figure 15 CMX7261 Inputs and Outputs

## 8 Detailed Descriptions

## 8.1 Xtal Frequency

The CMX7261 is designed to work with a xtal or an external frequency oscillator within the ranges specified in section 9.1.3. Programming registers P1.0-P1.6 in Program Block 1 – Clock Control (see User Manual) must be loaded with the correct values to ensure that the device will work to specification with the user selected clock frequency. A table of configuration values can be found in Table 8 for a range of Xtal or external oscillator frequencies.

#### 8.2 Host Interface

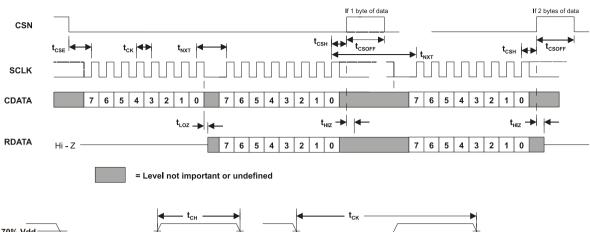

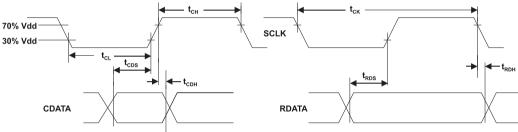

A serial data interface (C-BUS) is used for command, status and data transfers between the CMX7261 and the host  $\mu$ C; this interface is compatible with Microwire<sup>TM</sup>, SPI<sup>TM</sup> and other similar interfaces. Interrupt signals notify the host  $\mu$ C when a change in status has occurred; the  $\mu$ C should read the Status register across the C-BUS and respond accordingly. Interrupts only occur if the appropriate mask bit has been set, see Interrupt Operation.

#### 8.2.1 C-BUS Operation

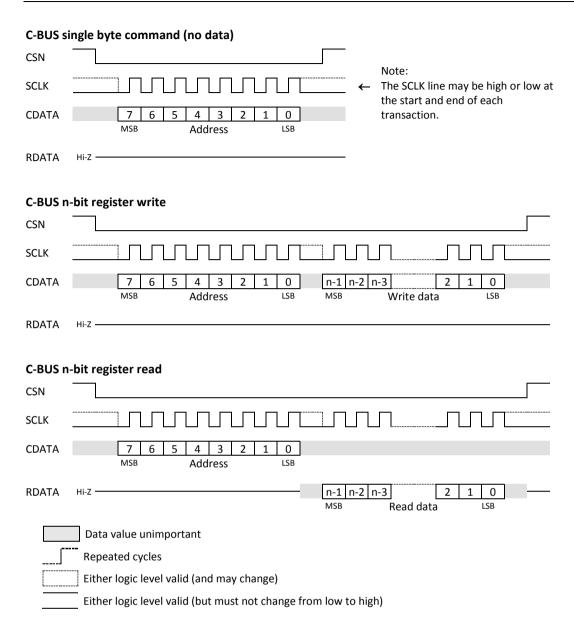

This block provides for the transfer of data and control or status information between the CMX7261 internal registers and the host  $\mu$ C over the C-BUS serial bus. Single register transactions consist of a single Register Address byte sent from the  $\mu$ C, which may be followed by a data word sent from the  $\mu$ C to be written into one of the CMX7261's Write Only Registers, or a data word read out from one of the CMX7261's Read Only Registers. Streaming C-BUS transactions consist of a single Register Address byte followed by many data bytes being written to or read from the CMX7261. All C-BUS data words are a multiple of 8 bits wide, the width depending on the source or destination register. Note that certain C-BUS transactions require only an address byte to be sent from the  $\mu$ C, no data transfer being required. The operation of the C-BUS is illustrated in Figure 16.

Data sent from the  $\mu$ C on the CDATA (command data) line is clocked into the CMX7261 on the rising edge of the SCLK input. Data sent from the CMX7261 to the  $\mu$ C on the RDATA (reply data) line is valid when SCLK is high. The CSN line must be held low during a data transfer and kept high between transfers. The C-BUS interface is compatible with most common  $\mu$ C serial interfaces and may also be easily implemented with general purpose  $\mu$ C I/O pins controlled by a simple software routine. Section 9.1.5 (C-BUS Timing) gives detailed C-BUS timing requirements.

Note that, due to internal timing constraints, there may be a delay of up to  $60\mu$ s between the end of a C-BUS write operation and the device reading the data from its internal register.

Figure 16 Basic C-BUS Transactions

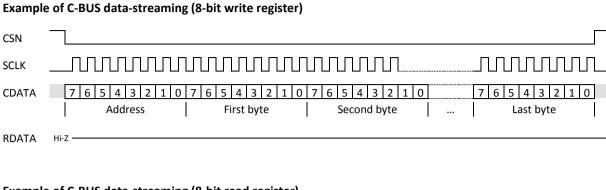

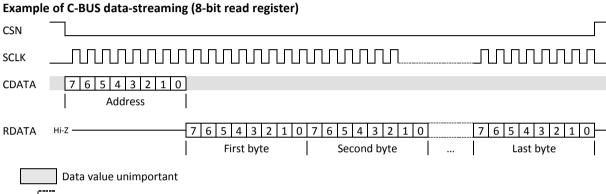

To increase the data bandwidth between the  $\mu$ C and CMX7261, certain of the C-BUS read and write registers are capable of data-streaming operation. This allows a single address byte to be followed by the transfer of multiple read or write data words, all within the same C-BUS transaction. This can significantly increase the transfer rate of large data blocks, as shown in Figure 17.

Figure 17 C-BUS Data-Streaming Operation

#### Notes:

- 1. For Command byte transfers only the first 8 bits are transferred (\$01 = Reset)

- 2. For single byte data transfers only the first 8 bits of the data are transferred

- 3. The CDATA and RDATA lines are never active at the same time. The Address byte determines the data direction for each C-BUS transfer.

- 4. The SCLK can be high or low at the start and end of each C-BUS transaction

- 5. The gaps shown between each byte on the CDATA and RDATA lines in the above diagram are optional; the host may insert gaps or concatenate the data as required.

## 8.3 Function Image™ Loading

The Function Image™ (FI), which defines the operational capabilities of the device, may be obtained from the CML Technical Portal, following registration. This is in the form of a 'C' header file, which can be included into the host controller software or programmed into an external serial memory. The Function ImageTM size can never exceed 128kbytes, although a typical FI will be considerably less than this. Note that the BOOTEN1, 2 pins are only read at power-on, when the RESETN pin goes high, or following a C-BUS General Reset, and must remain stable throughout the FI loading process. Once the FI load has completed, the BOOTEN1, 2 pins are ignored by the CMX7261 until the next power-up or Reset.

The BOOTEN 1, 2 pins are both fitted with internal low current pull-up devices.

For serial memory load operation, BOOTEN2 should be pulled low by connecting it to DVss either directly or via a 47k resistor (seeTable 3).

Whilst booting, the boot loader will return the checksum of each block loaded in the C-BUS Audio Out FIFO. The checksums can be verified against the published values to ensure that the FI has loaded correctly. Once the FI has been loaded, the CMX7261 performs these actions:

- (1) The product identification code is reported in the C-BUS Audio Out FIFO

- (2) The FI version code is reported in C-BUS Audio Out FIFO.

|                    | BOOTEN2 | BOOTEN1 |

|--------------------|---------|---------|

| C-BUS host load    | 1       | 1       |

| Reserved           | 1       | 0       |

| Serial Memory load | 0       | 1       |

| Reserved           | 0       | 0       |

**Table 3 BOOTEN Pin States**

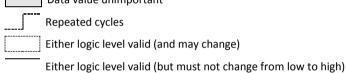

#### 8.3.1 FI Loading from Host Controller

The FI can be included into the host controller software build and downloaded into the CMX7261 at power-up over the C-BUS interface, using the Audio In FIFO. For Function Image™ load, the FIFO accepts raw 16-bit Function Image™ data (using the Audio In FIFO data word - \$49 write register), there is no need for distinction between control and data fields. The BOOTEN 1, 2 pins must be set to the C-BUS load configuration, the CMX7261 powered or Reset, and then data can then be sent directly over the C-BUS to the CMX7261.

If the host detects a brownout, the BOOTEN 1, 2 pins should be set to re-load the FI. A General Reset should then be issued or the RESETN pin used to reset the CMX7261 and the appropriate FI load procedure followed.

Streaming C-BUS may be used to load the Audio In FIFO Data8 - \$48 write register with the Function Image™, and the Audio In FIFO Level - \$4B read register used to ensure that the FIFO is not allowed to overflow during the load process.

The download time is limited by the clock frequency of the C-BUS; with a 5MHz SCLK it should take less than 250ms to complete even when loading the largest possible Function Image $^{\text{TM}}$ .

Figure 18 FI Loading from Host

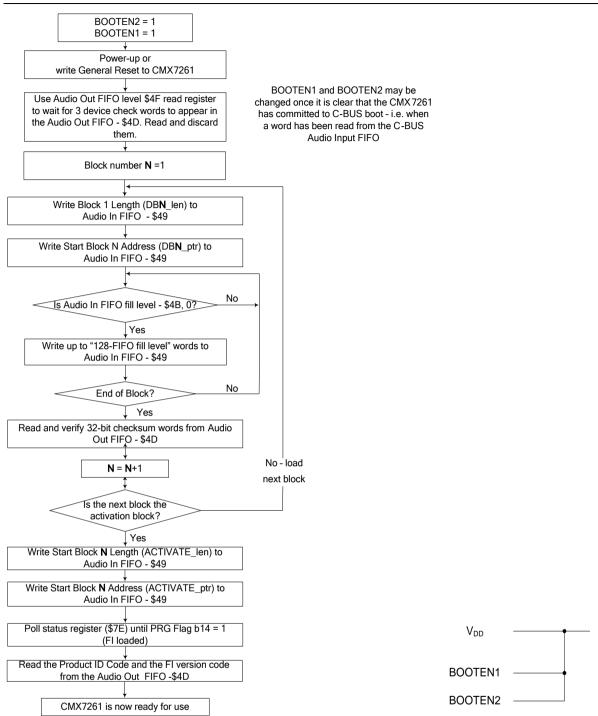

#### 8.3.2 FI Loading from Serial Memory

The FI must be converted into a format for the serial memory programmer (normally Intel Hex) and loaded into the serial memory by either the host or an external programmer. The serial memory should contain the same data stream as written to the Audio In FIFO shown in Figure 18. The most significant byte of each 16-bit word should be stored first in serial memory.

The serial memory should be interfaced to the CMX7261 using SSOUT0 as the chip select and PCM port pins, which act as an SPI port whilst booting (refer section 4 Pin and Signal List). Section 6.3 PCM and Serial Port Interface, shows the connections required for interfacing the AT25F512 Serial Flash memory with CMX7261.

The CMX7261 needs to have the BOOTEN pins set to serial memory load, and then on power-on, following the RESETN pin becoming high, or following a C-BUS General Reset, the CMX7261 will automatically load the data from the serial memory without intervention from the host controller.

Figure 19 FI Loading from Serial Memory

The CMX7261 has been designed to function with the AT25F512 Serial Flash memory, however other manufacturers' parts may also be suitable. The time taken to load the FI should be less than 500ms even when loading the largest possible Function Image™.

## 8.4 Coding Formats

This section provides a brief description about the various coding standards handled by the CMX7261 when loaded with FI-2.x. The motivation behind all the voice coding standards described here is to compress analogue voice in order to reduce the bandwidth required to transmit it.

#### 8.4.1 G.711

The G.711 standard is an ITU recommendation for audio companding. The standard specifies coding of linear PCM speech at 8 ksamples/s into logarithmic PCM speech at 8 ksamples/s – a coded data rate of 64 kbits/second.

The general principle behind companding is that for large sample values the exact value of the sample is not that important, so the signal can be quantised without loss of quality. However, when the sample value is small excessive quantisation would lead to poor quality speech. The result is that as the sample amplitude increases less resolution is required and, compared to linear PCM, compression is possible.

There are two variants: μ-law and A-law.

- μ-law is used primarily in North America codes 14-bit linear PCM to 8-bit logarithmic PCM

- A-law is used in the rest of the world codes 13-bit linear PCM to 8-bit logarithmic PCM

A single input sample maps onto a single companded sample, with no memory or algorithmic delay. The algorithm is lossy – if linear PCM speech is A-law or  $\mu$ -law encoded and then decoded back into linear PCM the resulting audio will not be identical sample by sample but should sound similar.

In addition to companding, the G.711 standard specifies that A-law encoded samples should have even bits inverted. This is to provide many 0/1 transitions to assist signal reception when the data is transmitted using a modem. Inverting the even bits is equivalent to XORing the data with 0x55.

The G.711 standard specifies that μ-law encoded samples should be inverted, equivalent to XORing with 0xFF.

## 8.4.2 G.723.1<sup>1</sup>

G.723.1 is an ITU recommendation for coding speech samples at 8 ksamples/s with a 30ms frame size. This translates to 240 PCM samples per G.723.1 frame.

The vocoder produces a compressed bit stream at either 5.3 kbits/s or 6.3 kbits/s depending on the selected mode of operation. In addition, G.723.1 Annex A defines a discontinuous transmission (DTX) capability.

With the DTX enabled a Voice Activity Detection (VAD) decision will detect the end of speech and will instead start encoding the background noise with a greatly reduced bandwidth requirement. Instead of a full size voice frame a much shorter Silence Insertion Descriptor (SID) frame is transmitted and then no further frames are transmitted until a change in the input signal triggers a new SID frame or until voice is detected again. At the decoder a received SID frame will result in generation of comfort noise to fill the period of non-transmitted frames.

© **2016** CML Microsystems Plc Page 29 D/7261\_FI-2.x/4

<sup>&</sup>lt;sup>1</sup> CML acknowledges that the device contains an implementation of the G.723.1 standard, rights to which are held by third parties who may claim and/or be entitled to compensation in connection with their implementation. It is the users' responsibility to obtain any licence that may be required directly from holders of such rights if using G.723.1 functionality. Licence details are available from Sipro Lab Telecom (<a href="www.sipro.com">www.sipro.com</a>). User hereby waives any right to seek damages or other compensation by way of suit or other action against CML Microsystems Plc in connection with any such standards.

## 8.5 Transcoding Description

Internally the CMX7261 decodes the input audio data to linear PCM before encoding into a desired output format. Once the transcoder is configured, the following steps happen inside the CMX7261:

- 1. A frame of input audio is first passed through the 'Decoder' block (refer Figure 1 Block Diagram) where it is decoded from the input format configured in the Input Type \$54 write register, to linear PCM.

- 2. The output of the 'Decoder' is held internally in linear PCM format and this is then passed through the 'Encoder' block (refer Figure 1 Block Diagram) where it is encoded to the output format configured in the Output Type \$56 write register. In the case of G.723.1 encoding mode the currently configured rate and VAD option is read from the G.723.1 Vocoder Options \$5E write register.

- 3. Optionally the linear PCM output from the Decoder can be monitored using the MONOUT pins. This facility is provided for debug purposes and can be switched off, to conserve power.

The steps above describe transcoding of a single audio channel. Full duplex mode provides two such audio channels with the limitation that one channel provides the reverse transcoding of the other.

#### 8.5.1 Input and Output Frame Sizes

The input and output frame sizes differ between various transcoding formats, as explained in this section.

#### G.723.1

G.723.1 operates with various sizes of encoded frames, depending on configuration and VAD operation.

A transmitted 30ms G.723.1 frame can correspond to either

```

24 bytes = 6.3 kbits/s rate, voice)

20 bytes = 5.3 kbits/s rate, voice)

4 bytes = Annex A: Silence Insertion Descriptor (SID) or

0 bytes = Annex A: Silence (no transmission)

```

These can occur in any order, although silence frames are typically preceded by a SID frame. Voice frames may change rate at any time and so it is important that the correct length is given for each frame.

At the decoder the length of the frame being passed is signalled using the Audio In FIFO Format - \$4A – write register, which must be written prior to writing the frame data into the FIFO. This is set in the Type field, according to the values listed in Table 4.

If a frame error was detected in the underlying transport this should be signalled to the decoder by also setting the CRC flag in the format byte. This will indicate to the decoder that it should attempt Lost Packet Recovery (LPR) for this frame. Once a following frame is received error free this bit must be cleared to zero before it is transferred.

The data for the frame is then written to the Audio In FIFO Data8 - \$48 write (Supports streaming C-BUS) register. This may be performed as a streaming CBUS write if required. Care should be taken not to overflow the FIFO so the available space may be checked prior to writing the data.

When DTX (Annex A) is enabled at the remote end there will be periods where no frames are received. During these periods a no-transmission (silence) frame must still be inserted by writing a single 1-byte frame to the Audio In FIFO Data8 - \$48 write (Supports streaming C-BUS) register, in order to indicate the position relative to other frames. The value written is important. Because silence frames often occur in a block this may be performed as follows.

1. Write type (\$03) to the Audio In FIFO Format - \$4A – write register on the first silence frame in a block.

2. Write one byte of data (\$03) to Audio In FIFO Data8 - \$48 write (Supports streaming C-BUS)register. This must be written for the first silence frame and each one thereafter.

In all cases the length of data written to the FIFO must match the type field which was set in the format byte.

| 7 | 6 | 5 | 4   | 3 | 2 | 1    | 0 |

|---|---|---|-----|---|---|------|---|

| 0 | 0 | 0 | CRC | 0 | 0 | Type |   |

| Type[1:0]       | Packet Type         | Tx / Rx<br>Length | FIFO Length |

|-----------------|---------------------|-------------------|-------------|

| 00 <sub>b</sub> | 6.3 kbits/s Voice   | 24 bytes          | 24 bytes    |

| 01 <sub>b</sub> | 5.3 kbits/s Voice   | 20 bytes          | 20 bytes    |

| 10 <sub>b</sub> | SID                 | 4 bytes           | 4 bytes     |

| 11 <sub>b</sub> | Silence (no packet) | 0 bytes           | 1 byte      |

| CRC | (decoder only)               |

|-----|------------------------------|

| 0   | Frame was received correctly |

| 1   | Frame had CRC errors         |

Table 4 Encoding of FIFO Format Registers (\$4A, \$4E) for G.723.1 Operation

For encoder operation the output FIFO operates as the reverse of the decoder. Upon detection of a new packet being produced the host must read the Audio Out FIFO Format - \$4E read register to determine the type, and therefore the length, of the next frame in the buffer. This is encoded using the same format as Table 4. The host must then read the correct number of bytes from the Audio Out FIFO Data8 - \$4C read (Supports streaming C-BUS) register before transmitting the frame. In the case of a single byte of type \$03 (silence) the FIFO must be read once but no data should be transmitted. The CRC flag is not used in encoder mode.

Typical processing delays are shown in Table 5:

**Encoder: ADC FIFO** 5ms **Buffer Input Samples** 30ms Algorithm Look-ahead 7.5ms **Encode Processing** 24.5ms Total: 67ms Decoder: **Decode Processing** 4.5ms **DAC FIFO** 5ms Total: 9.5ms **Encode/Decode Total:** 76.5ms

**Table 5 G723.1 Typical Process Times**

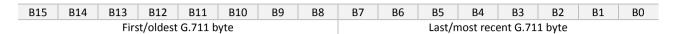

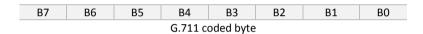

#### G.711

- When decoding G.711  $\mu$ /A-law coded audio each 8-bit input byte will be decoded into a linear PCM sample representing 0.125ms of audio (at 8kHz sampling rate).

- When encoding into G.711  $\mu$ /A-law coded audio each input (at 8kHz sampling rate) will be encoded into an 8-bit sample.

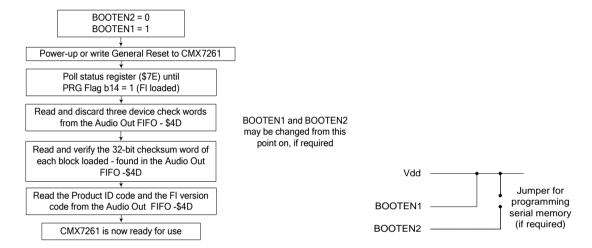

#### 8.5.2 Data Transfer Using C-BUS Interface

Audio data can be transferred to and from the host via C-BUS Audio In and Audio Out FIFOs, each of which provide efficient streaming C-BUS access. The FIFO fill level can be determined by reading the Audio In and Audio Out FIFO levels and controlled using the FIFO Control - \$50 write register. Interrupts may be provided on FIFO fill thresholds being reached, or on every 'N' new samples being read from or written to the respective FIFOs.

Each FIFO word is 16-bits long and can be accessed as one 16-bit word or as two bytes – LSByte and MSByte. Word wide FIFO writes involve writing 16-bit words to the Audio In FIFO data word register using either a single write or a streaming C-BUS. The word written is transferred to the Audio In FIFO and its fill level is updated.

Byte wide FIFO writes involve writing to the Audio In FIFO data byte register using either a single write or a streaming C-BUS. The contents of the Audio In FIFO data byte register are transferred to the Audio In FIFO (with undefined data in the MSByte) and its fill level is updated.

Likewise a word read from the Audio Out FIFO data word read register will return the oldest Audio Out FIFO data word and Audio Out FIFO fill level is updated. Reading the Audio Output data byte register will read the oldest Audio Out FIFO data word, discard the MSByte and return the LSByte. Audio Out FIFO fill level is also updated. In summary:

| Operation                | Effect                                                                    |

|--------------------------|---------------------------------------------------------------------------|

| Audio In FIFO Data word  | Data word is added to Audio In FIFO. Audio In FIFO fill level is updated. |

| Wr                       |                                                                           |

| Audio In FIFO Data byte  | Audio In FIFO Data byte written is added to Audio In FIFO and its fill    |

| Wr                       | level is updated. The MSByte is a "don't care" byte.                      |

| Audio Out FIFO Data word | Oldest Audio Out FIFO data word is removed from FIFO and returned;        |

| Rd                       | Audio Out FIFO fill level is updated.                                     |

| Audio Out FIFO Data byte | Oldest Audio Out FIFO data word is removed from FIFO, its MSByte is       |

| Rd                       | discarded and its LSByte is returned. Audio Out FIFO fill level is        |

|                          | updated.                                                                  |

Figure 20 shows the C-BUS interface to the Audio In and Audio Out FIFOs.

Figure 20 Audio Input and Audio Output FIFOs

The type of input data selected using the Input Type - \$54 write register will determine whether the Audio In FIFO write 16 or 8 bit registers should be used for C-BUS audio input. The type of output data selected using the Output Type - \$56 write register will determine whether the Audio Out FIFO read 16 or 8 bit registers should be used for C-BUS audio output.

The registers that affect FIFO operation are:

- Audio In FIFO Data8 \$48 write

- Audio In FIFO Data16 word \$49 write (Supports streaming C-BUS)

- Audio Out FIFO Data8 \$4C read

- Audio Out FIFO Data16 \$4D read (Supports streaming C-BUS)Audio In FIFO Level \$4B read

- Audio Out FIFO Level \$4F read

- Audio In FIFO Format \$4A write

- Audio Out FIFO Format \$4E read

- FIFO Control \$50 write.

- G.723.1 Vocoder Options \$5E write

The remainder of this section explains data transfer to and from the host using the C-BUS interface.

#### When the input data source is C-BUS:

- 1. The host must ensure that the Audio In FIFO does not contain audio from previous encoding/decoding operations (see FIFO Control \$50 write register).

- 2. The Audio Source field in the Mode \$6B write register must be set to indicate that audio input is through the C-BUS interface.

- 3. The host writes at least a frame of data to the Audio In FIFO (see Audio In FIFO Data8 \$48 write registers). The frame size varies between different vocoders. The following table gives the frame size for various vocoders that exist in the CMX7261.