## Precision Monolithics Inc.

## **FEATURES**

| • | Low Offset Voltage                | 150μV Max  |

|---|-----------------------------------|------------|

|   | Low Offset Voltage Drift          |            |

|   | Five Times PM108A Output Current  |            |

|   | Low Offset Current                |            |

|   | Low Bias Current                  |            |

|   | Low Power Consumption             |            |

| • | High Common-Mode Input Range .    | ±13.5V Min |

|   | MIL-STD-883 Class B Processing Av |            |

|   |                                   |            |

- Silicon-Nitride Passivation

- 125° C Temperature-Tested Dice

- Available in Die Form

## ORDERING INFORMATION <sup>†</sup>

| T - 25°C                                             | PACI            | KAGE             | OBERATING                         |

|------------------------------------------------------|-----------------|------------------|-----------------------------------|

| T <sub>A</sub> = 25°C<br>V <sub>OS</sub> MAX<br>(mV) | CERDIP<br>8-PIN | PLASTIC<br>8-PIN | OPERATING<br>TEMPERATURE<br>RANGE |

| 0.15                                                 | OP08AZ          | _                | MIL                               |

| 0.15                                                 | _               | OP08EP           | COM                               |

| 1.0                                                  | OP08GZ          | _                | СОМ                               |

Burn-in is available on commercial and industrial temperature range parts in CerDIP and plastic DIP packages. For ordering information, see 1990/91 Data Book, Section 2.

## **GENERAL DESCRIPTION**

The PMI OP-08 is an improved version of the popular LM108A low-power op amp. Excellent performance is achieved by applying PMI's ion-implanted super-beta process and on-chip-zener-zap trimming. The OP-08 has a three-times lower offset voltage and a two-times lower offset voltage drift. Worst-case input offset voltage over  $-55^{\circ}$  C to  $+125^{\circ}$  C for the OP-08 is only  $350\mu$ V. In addition, the OP-08 has five times the output current capability of the 108A. For an op amp with identical specifications plus internal frequency compensation, see the OP-12 data sheet.

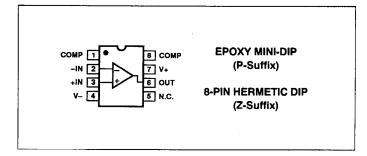

## **PIN CONNECTIONS**

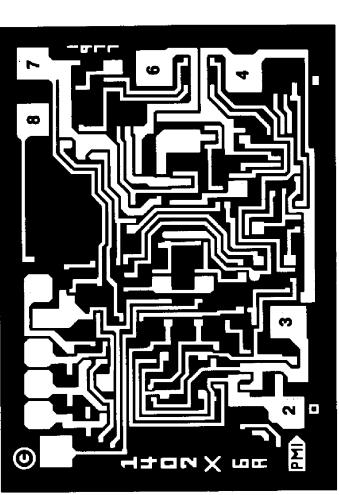

## SIMPLIFIED SCHEMATIC

| <b>ABSOLUTE MAXIMUM RATINGS (Note</b>       | e 4)           |

|---------------------------------------------|----------------|

| Supply Voltage                              | •              |

| OP-08A, OP-08E (All DICE Except GR)         | ±20V           |

| OP-08G (GR DICE Only)                       | ±18V           |

| Differential Input Current (Note 1)         | ±10mA          |

| Input Voltage (Note 2)                      |                |

| Output Short-Circuit Duration               | Indefinite     |

| Operating Temperature Range                 |                |

| OP-08A                                      | 55°C to +125°C |

| OP-08E, OP-08G                              | 0°C to +70°C   |

| Storage Temperature Range (Z)               | 65°C to +150°C |

| Storage Temperature Range (P)               | 65°C to +125°C |

| Lead Temperature (Soldering, 60 sec)        | 300°C          |

| DICE Junction Temperature (T <sub>i</sub> ) | 65°C to +150°C |

|                                             |                |

| PACKAGE TYPE           | ⊖ <sub>JA</sub> (Note 3) | elc | UNITS |

|------------------------|--------------------------|-----|-------|

| 8-Pin Hermetic DIP (Z) | 162                      | 26  | °C/W  |

| 8-Pin Plastic DIP (P)  | 110                      | 50  | °C/W  |

### NOTES:

- The inputs are shunted with back-to-back diodes for overvoltage protection.

Therefore, excessive current will flow if a differential input voltage in excess of 1V is applied between the inputs without some limiting resistance.

- For supply voltages less than ±15V, the absolute maximum input voltage is equal to the supply voltage.

- Θ<sub>jA</sub> is specified for worst case mounting conditions, i.e., Θ<sub>jA</sub> is specified for device in socket for CerDIP and P-DIP packages.

- Absolute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

**ELECTRICAL CHARACTERISTICS** at  $T_A = +25$ °C,  $V_S = \pm 20$ V for A and E Grades,  $V_S = \pm 15$ V for G Grade, unless otherwise noted. Compensation capacitor = 30pF.

|                                         |                   |                                                                                                                                    | (           | <b>A80-9C</b>        | /E             | OP-08G      |                      |               |                   |

|-----------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|----------------|-------------|----------------------|---------------|-------------------|

| PARAMETER                               | SYMBOL            | CONDITIONS                                                                                                                         | MIN         | TYP                  | MAX            | MIN         | TYP                  | MAX           | UNITS             |

| Input Offset Voltage                    | v <sub>os</sub>   |                                                                                                                                    | _           | 0.07                 | 0.15           | _           | 0.25                 | 1.0           | m∨                |

| Input Offset Current                    | Ios               |                                                                                                                                    | _           | 0.05                 | 0.20           | _           | 0.08                 | 0.50          | nA                |

| Input Bias Current                      | I <sub>B</sub>    |                                                                                                                                    | _           | 0.80                 | 2.0            | _           | 1.0                  | 5.0           | nA                |

| Input Noise Voltage                     | e <sub>np-p</sub> | 0.1Hz to 10Hz                                                                                                                      |             | 0.9                  |                |             | 0.9                  | _             | μV <sub>p-p</sub> |

| Input Noise<br>Voitage Density          | e <sub>n</sub>    | $f_O = 10Hz$ $f_O = 100Hz$ $f_O = 1000Hz$                                                                                          | _<br>_<br>_ | 22<br>21<br>20       |                | _           | 22<br>21<br>20       | _<br>_<br>_   | nV/√Hz            |

| Input Noise Current                     | i <sub>np-p</sub> | 0.1Hz to 10Hz                                                                                                                      | _           | 3                    |                | _           | 3                    |               | рА <sub>р-р</sub> |

| Input Noise<br>Current Density          | in                | $f_{O} = 10Hz$ $f_{O} = 100Hz$ $f_{O} = 1000Hz$                                                                                    |             | 0.15<br>0.14<br>0.13 |                | _<br>_<br>_ | 0.15<br>0.14<br>0.13 | <u>-</u><br>- | p <b>A</b> /√Hz   |

| Input Resistance —<br>Differential Mode | R <sub>IN</sub>   | (Note 1)                                                                                                                           | 26          | 70                   | _              | 10          | 50                   | _             | МΩ                |

| Input Voltage Range                     | IVR               | V <sub>S</sub> = ±15V                                                                                                              | ± 13.5      | ± 14.0               | _              | ± 13.5      | ± 14.0               | _             | V                 |

| Common-Mode<br>Rejection Ratio          | CMRR              | $V_{CM} = \pm 13.5V$                                                                                                               | 104         | 120                  | <u> </u>       | 84          | 116                  | -             | dB                |

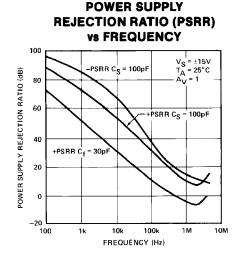

| Power Supply<br>Rejection Ratio         | PSRR              | $V_S = \pm 5V$ to $\pm 15V$                                                                                                        | _           | 1                    | 7              | · _         | 2                    | 63            | μV/V              |

| Large-Signal<br>Voltage Gain            | Avo               | $\begin{aligned} R_L &\geq 10k\Omega, \\ V_O &= \pm 10V \\ R_L &\geq 2k\Omega, \\ V_O &= \pm 10V, \\ V_S &= \pm 15V \end{aligned}$ | 80<br>50    | 300<br>150           | _              | 40          | 250<br>100           | -             | V/mV              |

| Output Voltage Swing                    | Vo                | $R_L \ge 10k\Omega$ ,<br>$V_S = \pm 15V$<br>$R_L \ge 2k\Omega$ ,<br>$V_S = \pm 15V$                                                | ±13<br>±10  | ±14<br>±12           | -              | ±13<br>±10  | ±14<br>±12           | -<br>-        | ٧                 |

| Slew Rate                               | SR                | $H_L \ge 2k\Omega$                                                                                                                 | _           | 0.12                 | _              |             | 0.12                 | _             | V/μs              |

| Closed-Loop<br>Bandwidth                | BW                | A <sub>VCL</sub> = +1                                                                                                              | _           | 0.8                  | _              | _           | 0.8                  | _             | MHz               |

| Open-Loop Output<br>Resistance          | Ro                | $\mathbf{v_O} = \mathbf{v}, \ \mathbf{I_O} = \mathbf{v}$                                                                           |             | 200                  |                | _           | 200                  | _             | Ω                 |

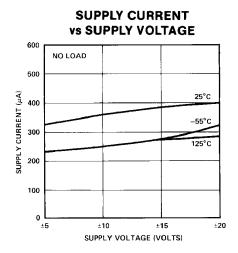

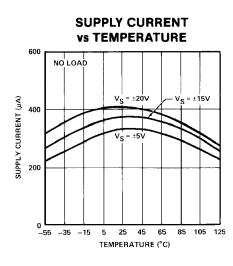

| Power Consumption                       | P <sub>d</sub>    | $V_S = \pm 15V$<br>$V_S = \pm 5V$                                                                                                  |             | 9                    | <b>18</b><br>6 |             | 12<br>4              | 24<br>8       | mW                |

### NOTE:

1. Guaranteed by input bias current.

# **ELECTRICAL CHARACTERISTICS** $V_S = \pm 20V$ for A Grade, $-55^{\circ}C \le T_A \le +125^{\circ}C$ , unless otherwise noted.

|                                          |                   |                                                                               |            | OP-08A     |              |       |

|------------------------------------------|-------------------|-------------------------------------------------------------------------------|------------|------------|--------------|-------|

| PARAMETER                                | SYMBOL            | CONDITIONS                                                                    | MIN        | TYP        | MAX          | UNITS |

| Input Offset Voltage                     | V <sub>os</sub>   |                                                                               | -          | 0.12       | 0.35         | mV    |

| Average Input<br>Offset Voltage<br>Drift | TCV <sub>os</sub> |                                                                               | _          | 0.50       | 2.5          | μV/°C |

| Input Offset Current                     | los               |                                                                               |            | 0.12       | 0.40         | nA    |

| Average Input<br>Offset Current<br>Drift | TCI <sub>os</sub> |                                                                               | _          | 0.50       | 2.5          | pA/°C |

| Input Bias Current                       | I <sub>B</sub>    |                                                                               | _          | 1.2        | 3.0          | nA    |

| Input Voltage Range                      | IVR               | V <sub>S</sub> = ±15V                                                         | ±13.5      | ±14.0      | _            | V     |

| Common-Mode<br>Rejection Ratio           | CMRR              | V <sub>CM</sub> = ±13.5                                                       | 100        | 110        | -            | dB    |

| Power Supply<br>Rejection Ratio          | PSRR              | V <sub>S</sub> = ±5V to ±15V                                                  | _          | 4          | 10           | μV/V  |

| Large-Signal<br>Voltage Gain             | A <sub>VO</sub>   | $R_L \ge 5k\Omega$ ,<br>$V_O = \pm 10V$ , $V_S = \pm 15V$                     | 40         | 120        | -            | V/mV  |

| Output Voltage Swing                     | v <sub>o</sub>    | $R_L \ge 10k\Omega$ , $V_S = \pm 15V$<br>$R_L \ge 5k\Omega$ , $V_S = \pm 15V$ | ±13<br>±10 | ±14<br>±12 | <del>-</del> | v     |

| Power Consumption                        | P <sub>d</sub>    | V <sub>S</sub> = ±15V                                                         | _          | 9          | 18           | mW    |

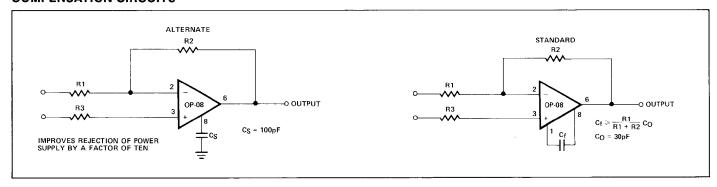

# **COMPENSATION CIRCUITS**

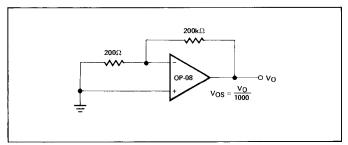

## **OFFSET VOLTAGE TEST CIRCUIT**

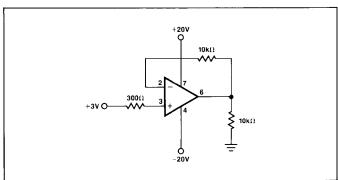

## **BURN-IN CIRCUIT**

**ELECTRICAL CHARACTERISTICS** at  $V_S = \pm 15V$  for G Grade and  $V_S = \pm 20V$  for E Grade,  $0^{\circ}C \le T_A \le +70^{\circ}C$ , unless otherwise noted.

|                                          |                   |                                                                                                    |              | OP-08E     |              |            | OP-08G     |          |        |

|------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------|--------------|------------|--------------|------------|------------|----------|--------|

| PARAMETER                                | SYMBOL            | CONDITIONS                                                                                         | MIN          | TYP        | MAX          | MIN        | TYP        | MAX      | UNITS  |

| Input Offset Voltage                     | Vos               |                                                                                                    | _            | 0.10       | 0.26         |            | 0.32       | 1.4      | mV     |

| Average Input<br>Offset Voltage<br>Drift | TCV <sub>OS</sub> | (Note 1)                                                                                           | _            | 0.50       | 2.5          | -          | 1.5        | 10       | μV/° C |

| Input Offset Current                     | Ios               |                                                                                                    | _            | 0.08       | 0.30         | _          | 0.12       | 6.5      | nA     |

| Average Input Offset Current Drift       | TCI <sub>OS</sub> | (Note 1)                                                                                           | _            | 0.50       | 2.5          | _          | 2.0        | 50       | pA/°C  |

| Input Bias Current                       | I <sub>B</sub>    |                                                                                                    | <del>-</del> | 1.0        | 2.6          | _          | 1.4        | 6.5      | nA     |

| Input Voltage Range                      | IVR               | V <sub>S</sub> = ±15V                                                                              | ±13.5        | ±14.0      | _            | ± 13.5     | ±14.0      | _        | V      |

| Common-Mode<br>Rejection Ratio           | CMRR              | $V_{CM} = \pm 13.5V$                                                                               | 100          | 116        | _            | 80         | 112        | _        | dB     |

| Power Supply<br>Rejection Ratio          | PSRR              | $V_S = \pm 5V$ to $\pm 15V$                                                                        |              | 2          | 10           | _          | 3          | 100      | μV/V   |

| Large-Signal<br>Voltage Gain             | A <sub>VO</sub>   | $R_{L} \ge 2k\Omega,$ $V_{O} = \pm 10V$ $R_{L} \ge 10k\Omega,$ $V_{O} = \pm 10V$ $V_{S} = \pm 15V$ | 25<br>60     | 100        | <del>-</del> | _<br>25    | 80<br>150  | <b>-</b> | V/mV   |

| Output Voltage<br>Swing                  | Vo                | $R_L \ge 10k\Omega$ ,<br>$V_S = \pm 15V$<br>$R_L \ge 2k\Omega$ ,<br>$V_S = \pm 15V$                | ±13          | ±14<br>±12 | <b>–</b>     | ±13<br>±10 | ±14<br>±12 | -        | V      |

| Power Consumption                        | P <sub>d</sub>    | V <sub>S</sub> = ±15V                                                                              | _            | 9          | 18           |            | 15         | 24       | mW     |

## NOTE:

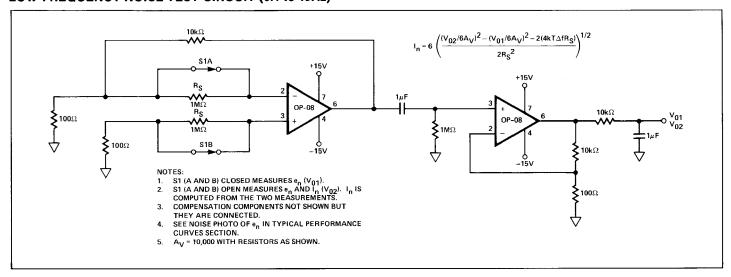

# LOW-FREQUENCY NOISE TEST CIRCUIT (0.1 to 10Hz)

<sup>1.</sup> Sample tested.

## DICE CHARACTERISTICS (125°C TESTED DICE AVAILABLE)

DIE SIZE  $0.059 \times 0.043$  inch, 2537 sq. mils (1.50  $\times$  1.09 mm, 1.64 sq. mm)

- 1. COMPENSATION

- 2. INVERTING INPUT

- 3. NONINVERTING INPUT

- 4. V-

- 6. OUTPUT

- 7. V+

- 8. COMPENSATION

For additional DICE ordering information, refer to 1990/91 Data Book, Section 2.

**WAFER TEST LIMITS** at  $V_S=\pm 20V$  and  $T_A=25^{\circ}$  C for OP-08N and OP-08G devices;  $V_S=\pm 20V$  and  $T_A=125^{\circ}$  C for OP-08NT and OP-08GT devices;  $V_S=\pm 15V$  and  $T_A=25^{\circ}$  C for OP-08GR devices, unless otherwise noted.

| PARAMETER                                         | SYMBOL          | CONDITIONS                                                                                                                                | OP-08NT<br>LIMIT | OP-08N<br>LIMIT | OP-08GT           | OP-08G<br>LIMIT   | OP-08GR<br>LIMIT | UNITS    |

|---------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-------------------|-------------------|------------------|----------|

| Input Offset Voltage                              | V <sub>OS</sub> |                                                                                                                                           | 0.35             | 0.15            | 0.6               | 0.3               | 1.0              | mV MAX   |

| Input Offset Current                              | los             |                                                                                                                                           | 0.4              | 0.2             | 0.4               | 0.2               | 0.5              | nA MAX   |

| Input Bias Current                                | I <sub>B</sub>  |                                                                                                                                           | 3                | 2               | 4                 | 2                 | 5                | nA MAX   |

| Input Voltage Range                               | IVR             | $V_S = \pm 15V$                                                                                                                           | ± 13.5           | ± 13.5          | ± 13.5            | ± 13.5            | ± 13.5           | V MIN    |

| Common-Mode<br>Rejection Ratio                    | CMRR            | $V_{CM} = \pm 13V$<br>$V_{S} = \pm 15V$                                                                                                   | 100              | 104             | 100               | 104               | 84               | dB MIN   |

| Power Supply<br>Rejection Ratio                   | PSRR            | $V_{S} = \pm 5V \text{ to } \pm 15V$                                                                                                      | 10               | 7               | 10                | 7                 | 63               | μV/V MAX |

| Output Voltage<br>Swing                           | V <sub>O</sub>  | $\begin{split} V_S &= \pm 15 V \\ R_L &\geq 10 k \Omega \\ R_L &\geq 2 k \Omega \\ R_L &\geq 5 k \Omega \end{split}$                      | ±13<br>—<br>±10  | ±13<br>±10<br>— | ± 13<br>—<br>± 10 | ± 13<br>± 10<br>— | ± 13<br>± 10     | V MIN    |

| Large-Signal<br>Voltage Gain<br>$(V_0 = \pm 10V)$ | A <sub>VO</sub> | $\begin{aligned} R_L &\geq 10 k \Omega \\ R_L &\geq 2 k \Omega, \ V_S = \pm 15 V \\ R_L &\geq 5 k \Omega, \ V_S = \pm 15 V \end{aligned}$ | -<br><br>40      | 80<br>50<br>—   | _<br>_<br>40      | 80<br>50<br>—     | 40<br>_<br>_     | V/mV MIN |

| Input Resistance                                  | R <sub>IN</sub> | (Note 2)                                                                                                                                  | _                | 25              |                   | 25                | 10               | ΜΩ ΜΙΝ   |

| Supply Current                                    | I <sub>SY</sub> | $I_{OUT} = 0, V_S = \pm 15V$<br>$V_{OUT} = 0$                                                                                             | 0.6              | 0.6             | 0.6               | 0.6               | 0.8              | mA MAX   |

## NOTES:

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

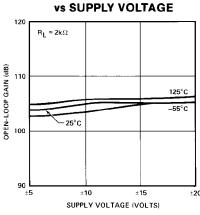

# TYPICAL ELECTRICAL CHARACTERISTICS at $V_S = \pm 15V$ , unless otherwise noted.

| PARAMETER                             | SYMBOL CONDITIONS | OP-08NT<br>TYPICAL | OP-08N<br>TYPICAL | OP-08GT<br>TYPICAL | OP-08G<br>TYPICAL | OP-08GR<br>TYPICAL | UNITS  |

|---------------------------------------|-------------------|--------------------|-------------------|--------------------|-------------------|--------------------|--------|

| Average Input Offset<br>Voltage Drift | TCV <sub>OS</sub> | 0.5                | 0.5               | 1.0                | 1.0               | 1.5                | μV/° C |

| Average Input Offset<br>Current Drift | TCI <sub>OS</sub> | 0.5                | 0.5               | 0.5                | 0.5               | 1.0                | pA/°C  |

For 25°C characteristics of NT & GT devices, see N & G characteristics, respectively.

<sup>2.</sup> Guaranteed by input bias current.

## **TYPICAL PERFORMANCE CHARACTERISTICS**

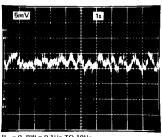

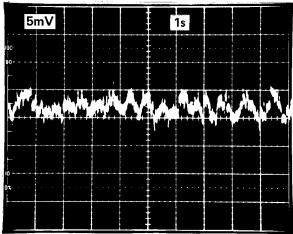

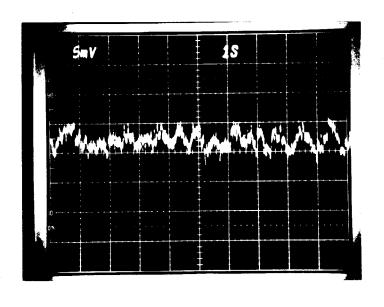

## **LOW FREQUENCY NOISE**

$R_S$  = 0, BW = 0.1Hz TO 10Hz 5mV/DIV AT READOUT 0.5 $\mu$ V/DIV REFERRED TO INPUT

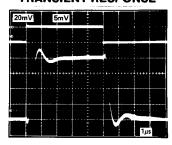

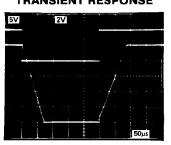

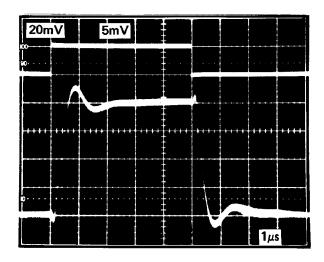

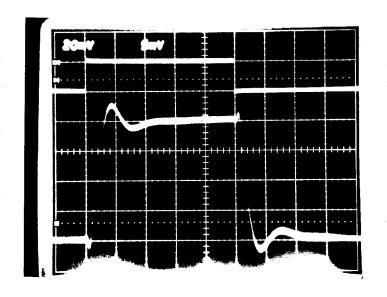

SMALL-SIGNAL TRANSIENT RESPONSE

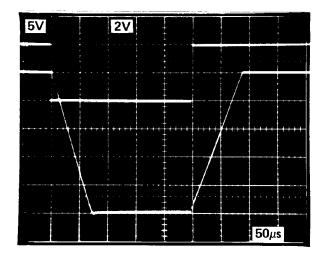

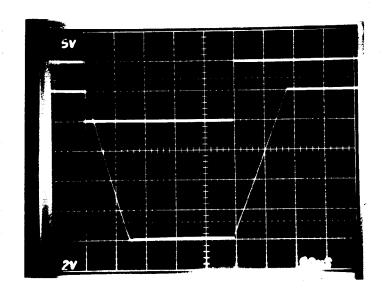

# LARGE-SIGNAL TRANSIENT RESPONSE

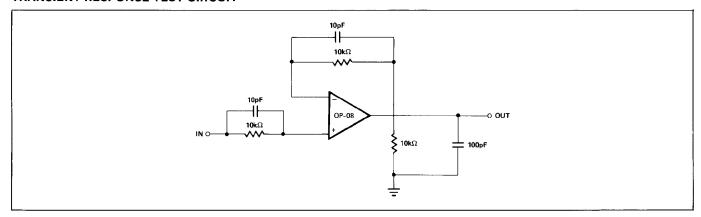

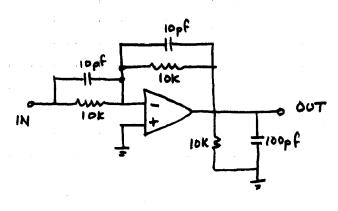

### TRANSIENT RESPONSE TEST CIRCUIT

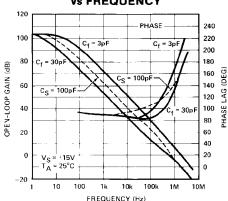

OPEN-LOOP GAIN AND PHASE vs FREQUENCY

OPEN-LOOP GAIN

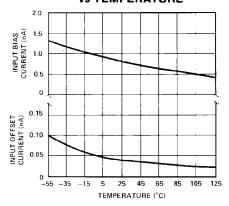

INPUT BIAS CURRENT

AND INPUT OFFSET CURRENT

vs TEMPERATURE

## TYPICAL PERFORMANCE CHARACTERISTICS

## **APPLICATIONS INFORMATION**

The OP-08 series has very low input offset and bias currents; the user is cautioned that printed circuit board leakage currents can produce significant errors, especially at high board temperatures. Careful attention to board layout and cleaning procedure is needed to take full advantage of the OP-08 performance. Board leakage is minimized by encircling the input pins with a guard ring maintained at the same potential as the inputs. This guard ring should be driven by a low impedance source, such as an amplifier's output or ground.

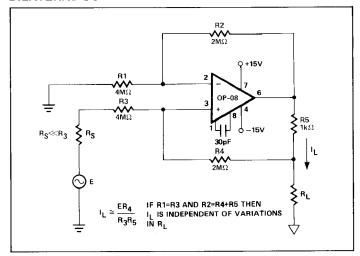

### TYPICAL APPLICATION

### **BILATERAL CURRENT SOURCE**

R<sub>S</sub> = 0, BW = 0.1Hz TO 10Hz 5mV/DIV AT READOUT 0.5µV/DIV REFERRED TO INPUT

op08, 12

LARGE SIGNAL RESP.

OP 08 , 12

TRANSIENT RESP

OP 08, 12

LOW FREQ NOISE

Rs = 0, BW = 0. 1 Hz to 10Hz

SMV/dry AT OUTPUT

· 5 NV REFERRED TO INPUT

04-08

1. COMPENSATION

DIE SIZE 0.058 × 0.042 inch

2. INVERTING INPUT

3. NON-INVERTING INPUT

4. V6. OUTPUT

7. V+

8. COMPENSATION

06.08