# **ICs for Communications**

Audio Ringing Codec Filter Basic Function ARCOFI®-BA, PSB 2161 Version 1.1

http://www.sienens.de

| PSB 2161 – Data Sheet  Application Note Layout and Wiring Recommendations  ARCOFI® Telephone Board SIPB 5132-SP – Board Description  ARCOFI® Coefficients Software SIPO 2163 – User's Manual  Application Note Analog Line Interface with the ARCOFI®-BA  Application Note Using the ARCOFI®-BA with a SLIC |                                                          |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---|

| Application Note Layout and Wiring Recommendations  ARCOFI® Telephone Board SIPB 5132-SP – Board Description  ARCOFI® Coefficients Software SIPO 2163 – User's Manual  Application Note Analog Line Interface with the ARCOFI®-BA  Application Note Using the ARCOFI®-BA with a SLIC                        | Contents                                                 |   |

| ARCOFI® Telephone Board SIPB 5132-SP – Board Description  ARCOFI® Coefficients Software SIPO 2163 – User's Manual  Application Note Analog Line Interface with the ARCOFI®-BA  Application Note Using the ARCOFI®-BA with a SLIC                                                                            | PSB 2161 Data Sheet                                      | : |

| ARCOFI® Coefficients Software SIPO 2163 – User's Manual  Application Note Analog Line Interface with the ARCOFI®-BA  Application Note Using the ARCOFI®-BA with a SLIC  Microelectronics Training Center Information on Literature                                                                          |                                                          |   |

| Application Note Analog Line Interface with the ARCOFI®-BA  Application Note Using the ARCOFI®-BA with a SLIC  Microelectronics Training Center Information on Literature                                                                                                                                   | ARCOFI® Telephone Board SIPB 5132-SP – Board Description |   |

| Analog Line Interface with the ARCOFI®-BA  Application Note  Using the ARCOFI®-BA with a SLIC  Microelectronics Training Center Information on Literature                                                                                                                                                   | ARCOFI® Coefficients Software SIPO 2163 – User's Manual  |   |

| Using the ARCOFI®-BA with a SLIC  Microelectronics Training Center Information on Literature                                                                                                                                                                                                                |                                                          |   |

| Information on Literature                                                                                                                                                                                                                                                                                   |                                                          |   |

|                                                                                                                                                                                                                                                                                                             |                                                          |   |

Edition 11 97

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München.

81541 Munchen.

© Siemens AG 1997. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change

design reserved.

For questions on technology, delivery and prices please contact the Semicon-

ductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list). Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group. Siemens AG is an approved CECC

#### Packing

manufacturer.

known to you. We can also help you -get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport. For packing material that is returned to us unsorted or which we are not obliged to accept we shall have to invoice you for any costs incurred.

Please use the recycling operators

Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life-support devices or systems are intended (a) to be implanted in the human body, or (b) support and/or maintain and sustain human life. If they fail, it is reasonably to assume that the health of the user may be endangered.

# ICs for Communications

Audio Ringing Codec Filter Basic Function ARCOFI®-BA

**PSB 2161 Version 1.1**

User's Manual 11.97

| PSB 2161 Revision History: Current Version: 1997-11-01 Previous Version: Preliminary Data Sheet 08.95 |                                 | Current Version: 1997-11-01                                     |  |

|-------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------|--|

|                                                                                                       |                                 | Preliminary Data Sheet 08.95                                    |  |

| Page<br>(in previous<br>Version)                                                                      | Page<br>(in current<br>Version) | Subjects (major changes since last revision)                    |  |

| 86, 87                                                                                                | 91, 92                          | The bypass mode of MIC, HOC, LSC is reserved for internal tests |  |

# Contents

| Table of       | i Contents                                 | age  |

|----------------|--------------------------------------------|------|

| 1              | Overview                                   | -    |

| 1.1            | Comparison between PSB 2161 and PSB 2160   |      |

| 1.2            | Table of Symbols                           |      |

| 1.3            | Features                                   |      |

| 1.4            | Pin Configurations                         | _    |

| 1.5            | Pin Definitions and Functions              |      |

| 1.6            | Logic Symbol                               |      |

| 1.7            | Functional Block Diagram                   |      |

| 1.8            | System Integration                         |      |

| 1.8.1          | ISDN-Voice Terminal                        |      |

| 1.8.2          | Digital PABX Voice Terminal                |      |

| 1.8.3          | Terminal Adapter for Analog Telephones     |      |

| 1.8.4          | Voice/Data Terminal (PC-Card)              |      |

| 1.8.5          | Multifunctional ISDN Terminal              |      |

| 1.8.6          | IOM®-2 Line Card Application               |      |

| 1.8.7          | Group 3 Fax/Modem Adapter                  |      |

| 2              | Functional Description                     |      |

| 2.1            | Analog Front End (AFE) Description         |      |

| 2.1.1<br>2.1.1 | Description of the Analog I/O              |      |

| 2.1.2          | AFE Attenuation Plan                       |      |

| 2.1.3          | Interface to Acoustic Transducers          |      |

| 2.2            | ARCOFI® Signal Processor (ASP) Description | . 42 |

| 2.2.1          | Transmit Signal Processing                 |      |

| 2.2.2          | Receive Signal Processing                  |      |

| 2.2.3          | Programmable Coefficients                  |      |

| 2.2.4          | Tone Generation                            |      |

| 2.2.4.1        | Tone Generation Architecture               |      |

| 2.2.4.2        | Control Generator                          | 49   |

| 2.2.4.3        | Tone Generator                             |      |

| 2.2.4.4        | Tone Filter                                |      |

| 2.2.4.5        | Tone Level Adjustment                      |      |

| 2.2.4.6        | DTMF Generator (transmit)                  |      |

| 2.3            | ARCOFI® Digital Interface (ADI)            | . 56 |

| 2.3.1          | PCI-Interface                              |      |

| 2.3.2          | IOM®-2 Frame Structure and Timing Modes    |      |

| 2.3.3          | Serial Control Interface                   |      |

| 2.3.4          | Serial Data Interface                      |      |

| 2.4            | Tool Functions                             |      |

| Table of                                                                                         | f Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                     |

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

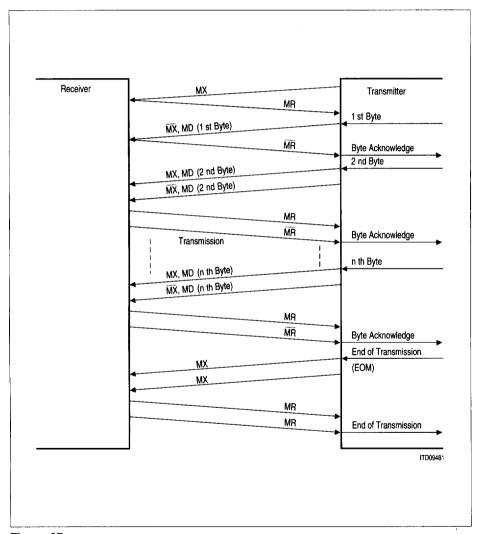

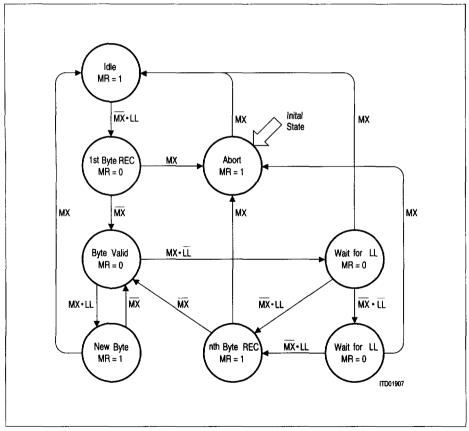

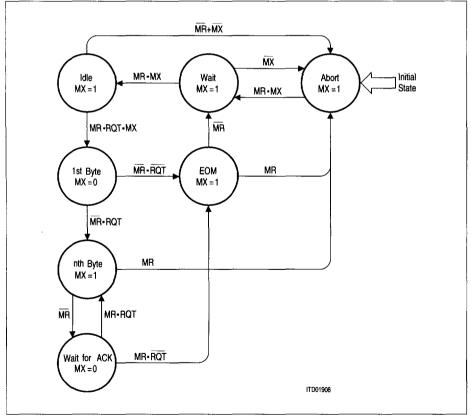

| 3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.2.1<br>3.4.2.2<br>3.4.2.3<br>3.4.3<br>3.5      | Operational Description Reset Initialization ARCOFI® Operating Modes IOM®-2 Interface Protocol B- and IC-Channels (IOM®-2 TE Mode) Monitor Channel MON Channel Data Structure MON Transfer Protocol Implementation of the MON-Channel Protocol Command/Indication Channel 1 (TE Mode) ARCOFI® Voice/Data Manipulation (VDM)                                                                                                                                                                                                                                                                       | 64<br>65<br>69<br>71<br>71<br>71<br>73                   |

| 4<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13 | Detailed Register Description Command Register (CMDR) General Configuration Register (GCR) Data Format and Interface Configuration Register (DFICR) Programmable Filter Configuration Register (PFCR) Tone Generator Configuration Register (TGCR) Tone Generator Switch Register (TGSR) AFE Transmit Configuration Register (ATCR) AFE Receive Configuration Register (ARCR) Test Function Configuration Register (TFCR) SDI Configuration Register (SDICR); SDI mode only Time Slot Configuration Register (TSCR); SDI mode only Extended Configuration Register (XCR) Test Mode Register (TMR) | 84<br>86<br>87<br>88<br>90<br>91<br>92<br>93<br>94<br>95 |

| 5                                                                                                | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 98                                                       |

| 6                                                                                                | Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 108                                                    |

| 7<br>7.1<br>7.2<br>7.3<br>7.3.1<br>7.3.2<br>7.3.3                                                | Application Note – Layout and Wiring Recommendations Introduction Layout Considerations Connecting the Analog Front End Outputs for Earpiece and Loudspeaker Differential Microphone Inputs The Single Ended Input MI3                                                                                                                                                                                                                                                                                                                                                                            | . 115<br>. 116<br>. 117<br>. 117<br>. 118                |

| Table o | f Contents                                               | Page  |

|---------|----------------------------------------------------------|-------|

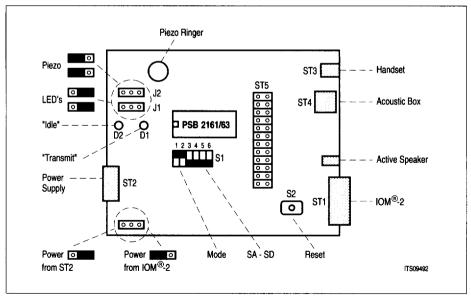

| 8       | ARCOFi® Telephone Board SIPB 5132-SP ~ Board Description | . 129 |

| 8.1     | Introduction                                             |       |

| 8.2     | Hardware Configuration                                   |       |

| 8.2.1   | Floor Plan and DIP Switches                              |       |

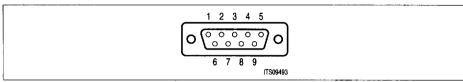

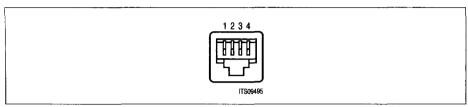

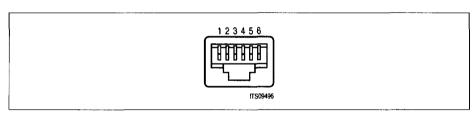

| 8.2.2   | Connectors                                               |       |

| 8.3     | Hardware Environment                                     |       |

| 8.4     | Trackfiles                                               | . 136 |

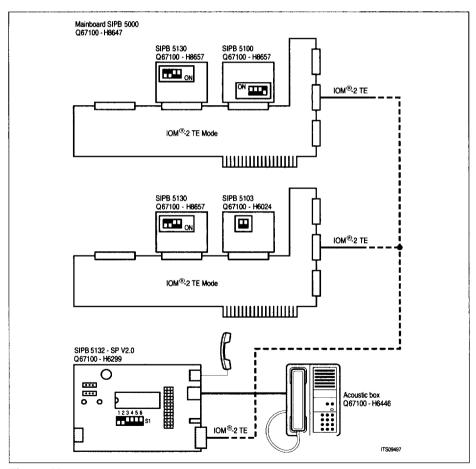

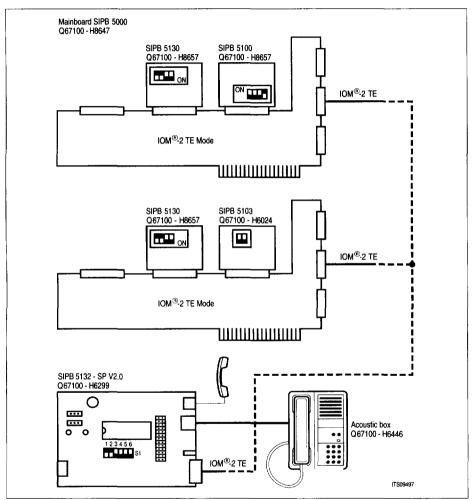

| 8.4.1   | Trackfile for IOM®-2 TE Mode                             | . 136 |

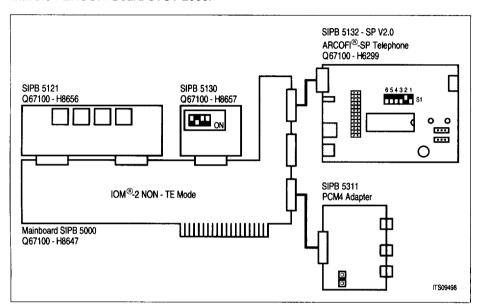

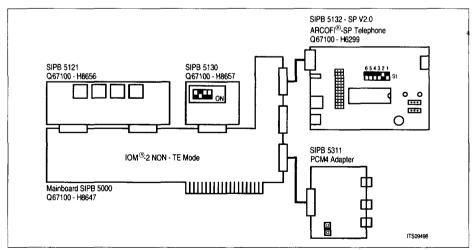

| 8.4.2   | Trackfiles for IOM®-2 NON-TE Mode                        | . 139 |

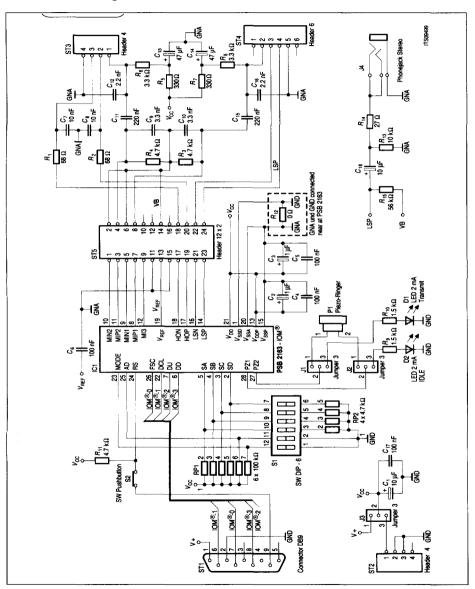

| 8.5     | Circuit Diagram                                          |       |

| 9       | ARCOFI® Coefficients Software SIPO 2163 – User's Manual  | . 155 |

| 9.1     | Introduction                                             | . 155 |

| 9.1.1   | The ARCOFI®-SP PSB 2163                                  | . 155 |

| 9.1.2   | The ARCOFI®-BA PSB 2161                                  | . 155 |

| 9.1.3   | The ARCOS-SP PLUS Software                               | . 156 |

| 9.1.4   | System Requirements                                      |       |

| 9.1.5   | Installation and Activation of ARCOS-SP PLUS             |       |

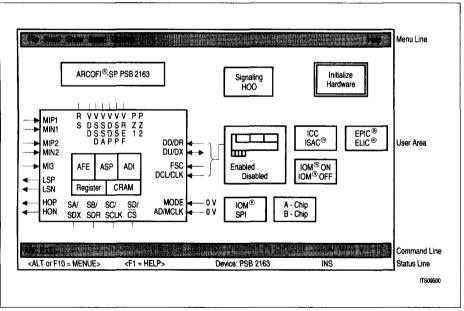

| 9.2     | Using ARCOS-SP PLUS                                      | . 159 |

| 9.2.1   | Introduction                                             |       |

| 9.2.2   | The Menu Line                                            | . 160 |

| 9.2.2.1 | Using the Menu Line                                      | . 160 |

| 9.2.2.2 | Pull-Down Menu "File"                                    |       |

| 9.2.2.3 |                                                          | . 162 |

| 9.2.2.4 | Pull-Down Menu "Show"                                    | . 162 |

| 9.2.2.5 | Pull-Down Menu "Board"                                   | . 162 |

| 9.2.2.6 | Pull-down Menu "Options"                                 |       |

| 9.2.3   | The User Area                                            |       |

| 9.2.4   | The Command Line                                         | . 166 |

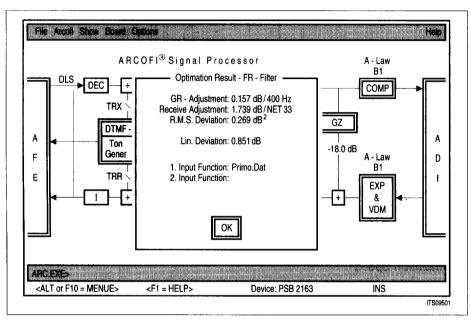

| 9.3     | Generating the Correction Filter Coefficients            | . 170 |

| 9.3.1   | Filter Implementation and Theory of Calculation          | . 170 |

| 9.3.2   | Calculation of Coefficients                              | . 171 |

| 9.3.3   | Reading the FX and FR Filters                            | . 176 |

| 9.3.4   | Examples for the Usage of the FX/FR Filters              | . 176 |

| 9.3.5   | Adapting the FX Filters to a Target Frequency Response   | . 176 |

| 9.3.5.1 | Using the "Execute" Feature to Calculate Coefficients    | . 178 |

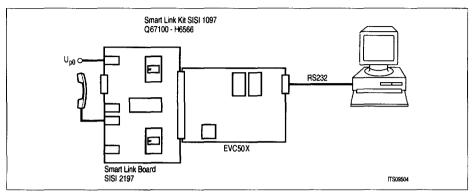

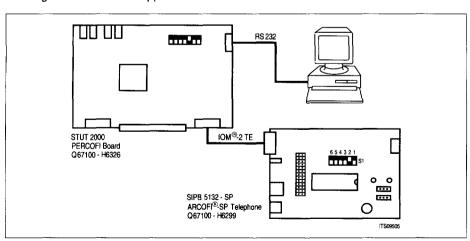

| 9.4     | Hardware Setup for Use with ARCOS-SP PLUS                | . 180 |

| 9.4.1   | Introduction                                             | . 180 |

| 9.4.2   | Using the SIPB 5000 System                               | . 180 |

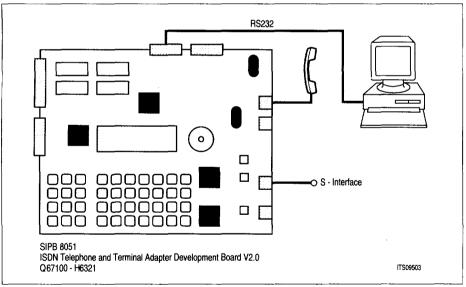

| 9.4.3   | Other Hardware Tools                                     | . 183 |

| 9.5     | Error Messages and Troubleshooting                       | . 187 |

| 9.5.1   | Hardware related Problems                                |       |

| 9.5.2   | Other Problems                                           | . 189 |

| Table o | f Contents                                                   | Page  |

|---------|--------------------------------------------------------------|-------|

| 10      | Application Note - Analog Line Interface with the ARCOFI®-BA | . 197 |

| 10.1    | Introduction                                                 |       |

| 10.2    | Realization                                                  | . 198 |

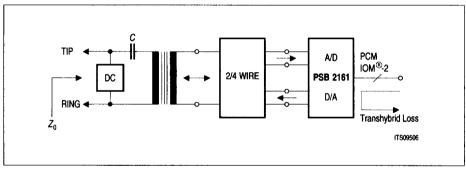

| 10.2.1  | General Architecture                                         | . 198 |

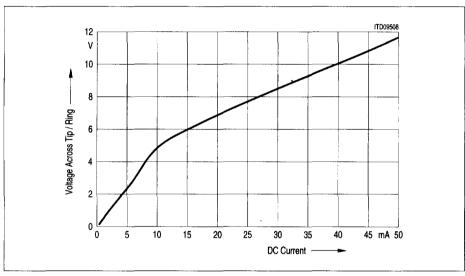

| 10.2.2  | DC Characteristic                                            | . 200 |

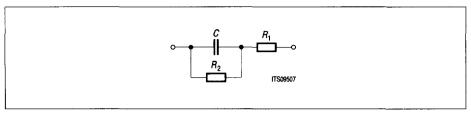

| 10.2.3  | Impedance Matching                                           | . 201 |

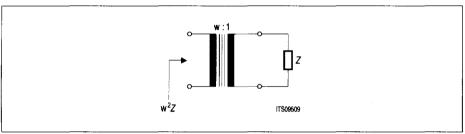

| 10.2.4  | 2-wire / 4-wire Conversion                                   | . 202 |

| 10.2.5  | Transhybrid Balance                                          | . 204 |

| 10.2.6  | Hook-Switch and Pulse Dialling                               | . 205 |

| 10.2.7  | Ring Detection                                               | . 206 |

| 10.3    | Circuit Diagram                                              | . 207 |

| 10.3.1  | Component Values                                             | . 207 |

| 10.3.2  | Circuit Diagram 1                                            | . 210 |

| 10.3.3  | Circuit Diagram 2                                            | . 211 |

| 10.4    | Measurement Results                                          | . 212 |

| 10.5    | Line Interface for use on a Linecard                         | . 213 |

| 10.6    | Appendix                                                     | . 215 |

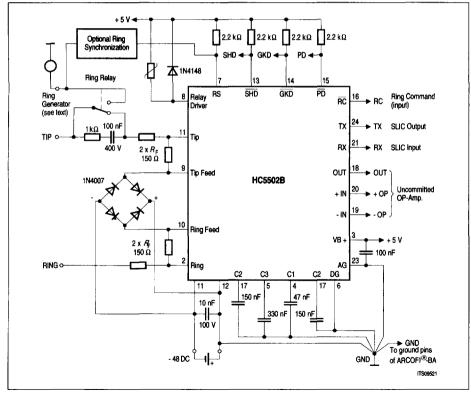

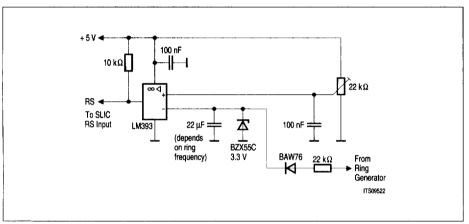

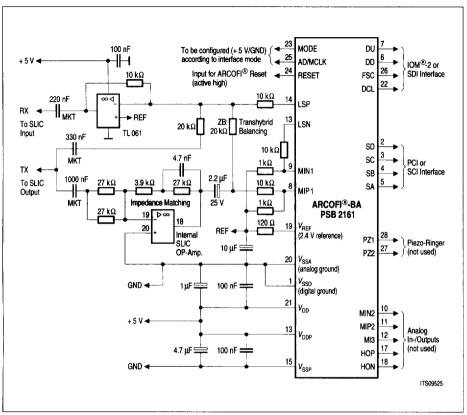

| 11      | Application Note – Using the ARCOFI®-BA with a SLIC          | . 223 |

| 11.1    | Introduction                                                 | . 223 |

| 11.2    | The Harris SLIC HC5502B                                      | . 224 |

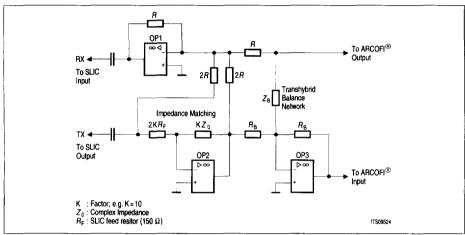

| 11.3    | Resistive Impedance Matching                                 | . 227 |

| 11.4    | Complex Impedance Matching                                   | . 228 |

| 11.5    | Measurement Results                                          | . 231 |

| 12      | Microelectronics Training Center                             | . 235 |

IOM®, IOM®-1, IOM®-2, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4 C, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, EPIC®-1, EPIC®-S, ELIC®, ITAC®, ISAC®-S, ISAC®-S TE, ISAC®-P and ISAC®-P TE are registered trademarks of Siemens AG.

# PSB 2161 - Data Sheet

#### 1 Overvíew

The PSB 2161 ARCOFI-BA provides the design engineer with a cost-optimized Audio, Ringing, Codec, Filter processor solution for simple digital terminals. It offers the minimum functions necessary to develop a low-cost telephone with the high flexibility by the DSP technics.

Remark: For more sophisticated digital terminals (e.g. comfort telephones offering speakerphone, voice/data terminals) we recommend the use of the Siemens ARCOFI-SP PSB 2163.

The typical applications of the ARCOFI-BA are:

- · low-cost digital telephone

- · low-cost facsimile terminal

- · low-cost answering machine

Note: Throughout this whole document "ARCOFI" refers to ARCOFI-BA PSB 2161.

The ARCOFI performs all encoding, decoding and filtering functions according to the ITU-T and ETSI (NET33) norms.

Full featured applications are possible without any external elements. All the necessary hardware and software is implemented.

Two transducer correction filters (one for each direction) can be programmed for an optimum adaptation to different transducer frequency characteristics.

The ARCOFI provides a universal tone generator for automatic generation of multitone sequences which can be used for tone alerting, call progress tones or other audible feedback tones.

A DTMF generator for the transmit direction is also available. This flexible tone generator concept fulfills a wide range of applications.

The interfacing to a handset mouth and earpiece is facilitated by a flexible analog front end. A loudspeaker output has also been integrated on the chip as well as a secondary input for a handsfree microphone. All analog inputs and outputs are gain programmable through software.

At the digital side an ISDN-Oriented Modular (IOM-2) interface for terminal (TE) and non-terminal (NON-TE) applications or a Serial Control/Data Interface (SCI & SDI) is realized to connect layer-1/2 devices to the ARCOFI.

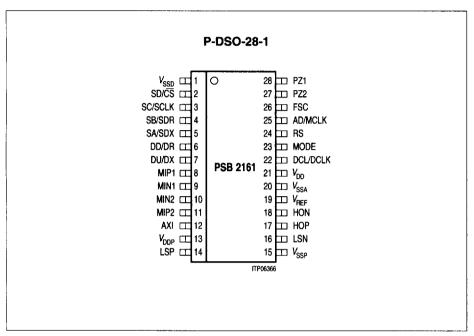

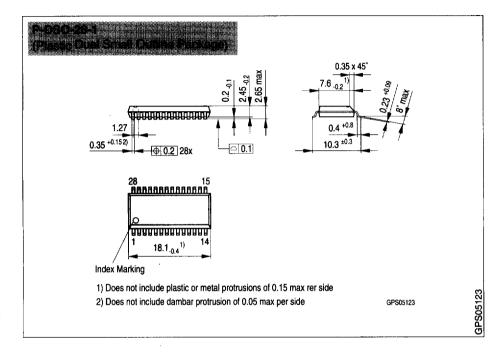

The ARCOFI is a BICMOS-device, available in a P-DSO-28-1 package. It operates from a single + 5 V supply and features a power-down state with very low power consumption.

## 1.1 Comparison between PSB 2161 and PSB 2160

Table of main differences:

| PSB 2161                                                                                                                                                                                                                       | PSB 2160                                                                                                                                                           | Comment |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 0.8 μ BICMOS technology                                                                                                                                                                                                        | 2 μ CMOS technology                                                                                                                                                |         |

| P-DSO-28-1                                                                                                                                                                                                                     | P-DIP-24 and P-LCC-28                                                                                                                                              |         |

| Single + 5 V supply Reduced power consumption in power down and operating modes                                                                                                                                                | ±5 V supply                                                                                                                                                        |         |

| IOM-2 NON-TE Interface; Serial<br>Control/Data Interface<br>Flexible configuration concept<br>Buffered Dual Port Coefficient-RAM<br>(reprogramming of the Coefficient-RAM<br>in operating modes without acoustical<br>effects) | SLD Interface                                                                                                                                                      |         |

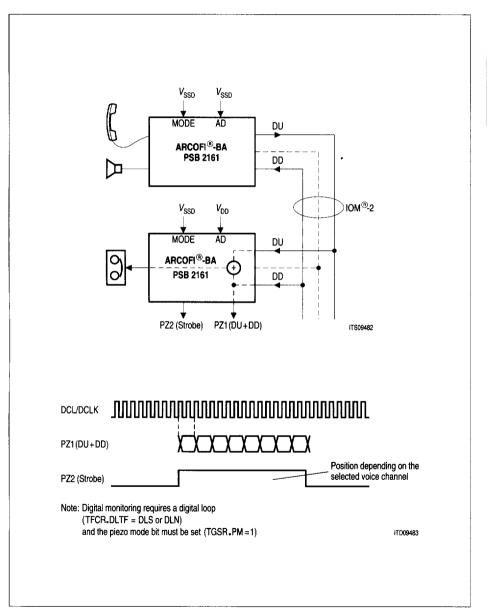

| Separate digital output for a piezo ringer                                                                                                                                                                                     | Multiplexed digital output for a piezo ringer                                                                                                                      |         |

| Fully programmable, high performance AFE in BICMOS technology                                                                                                                                                                  | Partial programmable Analog<br>Front End (AFE)                                                                                                                     | i       |

| Ringing directly via loudspeaker<br>(simultaneously signalling over the<br>loudspeaker and voice over the<br>earpiece is possible)                                                                                             | Ringing via loudspeaker only<br>over the common receiver path<br>(simultaneously signaling over<br>the loudspeaker and voice over<br>the earpiece is not possible) |         |

| Sidetone gain stage with higher resolution (two byte coefficient)                                                                                                                                                              | Sidetone gain stage with low resolution (one byte coefficient)                                                                                                     |         |

| Extended tone generation unit for receive and transmit direction                                                                                                                                                               | Simple tone generation unit for the receive direction and a DTMF generator for the transmit direction                                                              |         |

| Digital high pass in receive direction<br>Monitoring mode for digital and analog<br>voice recording<br>Additional test loops                                                                                                   |                                                                                                                                                                    |         |

| ETSI (NET33) & ITU-T G.712                                                                                                                                                                                                     | ITU-T G.712                                                                                                                                                        |         |

Note: Many slightly improvements realized in the PSB 2161 are not documented in this table.

**PSB 2161**

# **SIEMENS**

Overview

# 1.2 Table of Symbols

AD Address of the ARCOFI (IOM-2 mode)

A/D Analog to Digital converter ADI ARCOFI Digital Interface

AFE Analog Front End

AHO Handset Output Amplifier

AIMX Analog Input Multiplexer control bits (ATCR)

ALC Analog Loop via Converter (TFCR)

ALF Analog Loop via Front End (TFCR)

ALI Analog Loop via Interface (TFCR)

ALN Analog Loop via Noise Shaper (TFCR)

ALS Loudspeaker Amplifier

ALTF Analog Loop & Test Function bits (TFCR)

ALZ Analog Loop via Z-side tone gain stage

AMI Microphone Amplifier

ARCOFI Audio Ringing Codec Filter

ASP ARCOFI Signal Processor

AXI Auxiliary Input

BM Beat Mode bit (TGCR)

BT Beat Tone bit (TGCR)

CAM Chip Address Mode bit (IOM-2 two chip mode; GCR)

CCITT International Telegraph and Telephone Consultative Committee

CG Control Generator bit (TGCR)

CMDR Command Register

COP Coefficient Operation (CMDR)

CR Configuration Register

CRAM Coefficient RAM

CS Chip Select active low (serial control interface)

D/A Digital to Analog converter

DCE Double Clock Enable at DCLK pin (SDICR)

DCL IOM-2 interface clock

DCLK Data Clock pin (serial data interface)

DD IOM-2 Data Downstream pin

DEC Decimation filter

DHON Disable pin HON (XCR)

DHOP Disable pin HOP (XCR)

DHPR Disable High Pass Receive bit (PFCR)

DHPX Disable High Pass Transmit bit (PFCR)

DLN Digital Loop via Noise Shaper (TFCR)

DLP Digital Loop via PCM-register (TFCR)

Overview

#### Table of Symbols (cont'd)

DLS Digital Loop via Signal processor (TFCR)

DLSN Disable pin LSN (XCR) DLSP Disable pin LSP (XCR)

DI TF Digital Loop and Test Function bits (TFCR) DR Data Receive pin (serial data interface)

Data RAM DRAM

DSP Digital Signal Processor Dual Tone bit (TGCR) DT

DTMF Dual Tone Multi Frequency bit (TGSR)

DU IOM-2 Data Upstream pin

DΧ Data Transmit pin (serial data interface)

FΡ Earpiece

EPP0 Enable Push-Pull at pin DU/DX (SDICR) FPP1 Enable Push-Pull at pin SA/SDX (SDICR)

Enable Tone Filter bit (TGCR) **ETF**

European Telecommunications Standards Institute **ETSI**

FVX Enable Voice Transmit bit (GCR) **EVREF** Enable VREF buffer bit (ATCR) **FWDF** Electrical Wave Digital Filter

FR Frequency correction Receive bit (PFCR)

**FSC** IOM-2 and SDI-Frame Synchronization pin (8 kHz)

FX Frequency correction Transmit bit (PFCR)

GR Receive Gain bit (PFCR): Receive gain stage GX Transmit Gain bit (PFCR); Transmit gain stage GZ Z-side tone Gain bit (PFCR); Z-side tone Gain stage

HO Handset Output

Handset Output Control bits (ARCR) HOC HON Handset earpiece Output - pin HOP Handset earpiece Output + pin

**HPR** High-pass filter receive **HPX** High-pass filter transmit

**IDENT** Identification Code

IDR Initialize Data RAM (TFCR)

INT Interpolation filter IOM

ISDN-Oriented Modular

ISDN Integrated Services Digital Network

ITU-T International Telecommunication Union -Telephone

**PSB 2161**

# SIEMENS

Overview

#### Table of Symbols (cont'd)

LAW A-Law/μ-Law bit (GCR)

LIN Linear data mode (VDM; DFICR)

LS Loudspeaker

LSC Loudspeaker Control bits (ARCR)

LSN Loudspeaker output – pin LSP Loudspeaker output + pin

MCLK Master Clock pin (synchronized system clock)

MCLKR Master Clock Rate (SDICR)

MIC Microphone Control bits (ATCR)

MIN1/2 Microphone inputs – pins MIP1/2 Microphone inputs + pins

NOP No Operation (CMDR)

NOT No Test mode (TFCR)

PABX Private Automatic Branch Exchange

PCI Peripheral Control Interface PCM Pulse Code Modulation

PM Piezo Mode; output to digital pins PZ1/PZ2 (TGSR)

POR Power-On Reset

PU Power-Up bit (GCR)

RCM Reverse Channel Mode (CMDR)

RS Reset pin

R/W Read/Write operation bit (CMDR)

RX Receive path

SA-SD PCI I/O pins; I/O control bits (SDICR)

SCI Serial Control Interface

SCLK Serial Clock pin (serial control interface)

SDI Serial Data Interface

SDR Serial Data Receive pin (serial control interface)

SDX Serial Data Transmit pin (serial control interface)

SLOT IOM-2 Slot select for TE mode (GCR)

SM Stop Mode bit (TGCR)

SOP Status Operation (CMDR)

SQTR Square/Trapezoid mode bit (TGCR)

S/T Square/Trapezoid Generator

SIEMENS PSB 2161

Overview

#### Table of Symbols (cont'd)

TE Terminal Equipment

TG Tone Generator bit (TGCR)

TR Three party conferencing (VDM; DFICR)

TRL Tone Ringing via Loudspeaker (TGSR)

TRR Tone Ringing Receive bit (TGSR)

TRX Tone Ringing Transmit bit (TGSR)

TS Time-Slot Selection in SDI-mode (TSCR)

TX Transmit path

$V_{\rm DD}$  Voltage supply (+ 5 V)

$V_{\text{DDP}}$  Analog Voltage supply for Power amplifiers (+ 5 V)

VDM Voice Data Manipulation bits (DFICR)

$V_{\mathsf{REF}}$  Reference Voltage output pin

$V_{\rm SSA}$  Analog ground (0 V)  $V_{\rm SSD}$  Digital ground (0 V)

$V_{\rm SSP}$  Analog ground for Power amplifiers (0 V)

WDF Wave Digital Filter

XOP Extended Operation (CMDR)

#### Audio Ringing Codec Filter Basic Function ARCOFI-BA

**PSB 2161**

**BICMOS** Version 1.1

#### 1.3 **Features**

- Applications in digital terminal equipment featuring voice functions

- Digital signal processing performs all CODEC **functions**

- Fully compatible to the ITU-T G. 712 and ETSI (NET33) specification

- PCM A-Law/μ-Law (G. 711 ITU-T) and 16-bit linear data

- Flexible configuration of all internal functions

- Data Interface (SDI)

- single-ended auxiliary input

- Two differential outputs for a handset earpiece (200 Ω) and a loudspeaker (50 Ω)

- 100 mW sine wave and 200 mW square wave loudspeaker driver capability

- Separate digital output for a piezo ringer

- Flexible Peripheral Control Interface (PCI) in IOM-2 TE mode

- Flexible test and maintenance loopbacks in the analog front end and the digital signal processor

- Independent gain programmable amplifiers for all analog inputs and outputs

- Buffered Dual Port Coefficient-RAM (reprogramming of the Coefficient-RAM in operating modes without acoustical effects)

- · Two transducer correction filters

- Side tone gain adjustment

- Flexible DTMF, tone and ringing generator

- Single 5 V power supply

- Low power consumption: standby < 1 mW, operating consumption is dependent on</li> the selected operating mode

- Advanced 0.8

µ BICMOS technology

**Type**

**Ordering Code**

**Package**

# 1.4 Pin Configurations

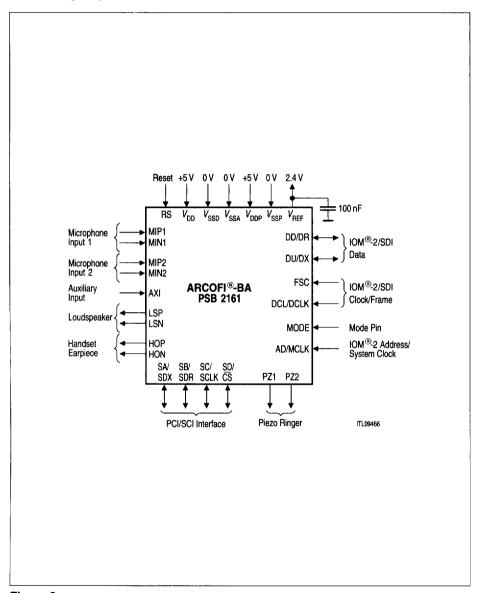

Figure 1

**PSB 2161**

# **SIEMENS**

Overview

# 1.5 Pin Definitions and Functions

| Pin No.  | Symbol        | Input (I)<br>Output (O)<br>Open Drain (OD) | Function                                                                                                                                                        |

|----------|---------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21       | $V_{DD}$      | _                                          | Power supply (5 V ± 5 %)                                                                                                                                        |

| 13       | $V_{DDP}$     | _                                          | Power supply (5 V ± 5 %)                                                                                                                                        |

| 1        | $V_{SSD}$     | _                                          | Digital Ground (0 V)                                                                                                                                            |

| 20       | $V_{SSA}$     | _                                          | Analog Ground (0 V)                                                                                                                                             |

| 15       | $V_{\sf SSP}$ | _                                          | Analog Ground (0 V)                                                                                                                                             |

| 23       | MODE          | 1                                          | Mode Selection: IOM-2 or serial control/data interface                                                                                                          |

| 25       | AD<br>MCLK    | 1                                          | IOM® Address: Chip address in IOM-2 two chip mode Master Clock: Synchronous system clock when serial control/data interface is selected                         |

| 24       | RS            | I                                          | Reset: A high signal on this pin forces the ARCOFI into reset state                                                                                             |

| 26       | FSC           | I                                          | Frame Sync:<br>8-kHz frame synchronization signal (IOM-2 and<br>SDI mode)                                                                                       |

| 22       | DCLK          | 1                                          | DCL-System Clock: 1.536 MHz supplied by the application system clock when IOM-2 mode is selected DCLK Data Clock: Data clock of the serial data interface (SDI) |

| 6        | DD            | I/(OD) 1)                                  | Data Downstream: Receive data from layer-1 IOM-2 controlling device Data Receive: Receive data of the serial data interface (SDI)                               |

| 28<br>27 | PZ1<br>PZ2    | 0                                          | Digital Piezo Ringer Output: When selected the tone ringer is routed to this output (PZ1 & PZ2 are in opposite phases)                                          |

<sup>1)</sup> See DD/DU-voice channel swapping (XOP\_D)

Overview

# Pin Definitions and Functions (cont'd)

| Pin No. | Symbol       | Input (I)<br>Output (O)<br>Open Drain (OD) | Function                                                                                                                                                     |

|---------|--------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | DU           | OD/I 1)                                    | Data Upstream:<br>Transmit data to the layer-1 IOM-2 controlling<br>device                                                                                   |

|         | DX           | OD/O <sup>2)</sup>                         | Data Transmit: Transmit data of the serial data interface (SDI)                                                                                              |

| 2       | SD           | 10                                         | Programmable I/O PCI Pin SD: This port pin is only available in IOM-2 TE mode                                                                                |

|         | CS           | 1                                          | Chip Select: A low level indicates a microprocessor access to the serial control interface (SCI)                                                             |

| 3       | SC           | 10                                         | Programmable I/O PCI Pin SC: This port pin is only available in IOM-2 TE mode                                                                                |

|         | SCLK         |                                            | Serial Clock: Clock signal of the serial control interface (SCI)                                                                                             |

| 4       | SB<br>SDR    | IO<br>I                                    | Programmable I/O PCI Pin SB: This port pin is only available in IOM-2 TE mode Serial Data Receive: Receive data line of the serial control interface (SCI)   |

| 5       | SA<br>SDX    | OD/O 3)                                    | Programmable I/O PCI Pin SA: This port pin is only available in IOM-2 TE mode Serial Data Transmit: Transmit data line of the serial control interface (SCI) |

| 19      | $V_{REF}$    | 0                                          | 2.4 V Output: Output for biasing analog single-ended inputs                                                                                                  |

| 8       | MIP1<br>MIN1 | 1                                          | Microphone Input 1: This highly symmetrical differential input has been designed for commonly used telephone microphones                                     |

See DD/DU voice channel swapping (XOP\_D)

Programmable via bit SDICR.EPP0

Programmable via bit SDICR.EPP1

Overview

# Pin Definitions and Functions (cont'd)

| Pin No.  | Symbol       | Input (I)<br>Output (O)<br>Open Drain (OD) | Function                                                                                                                                                                                        |

|----------|--------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11<br>10 | MIP2<br>MIN2 | 1                                          | Microphone Input 2: This highly symmetrical differential input has been designed for commonly used telephone microphones                                                                        |

| 12       | AXI          | 1                                          | Auxiliary Input:<br>Single-ended auxiliary input                                                                                                                                                |

| 14<br>16 | LSP<br>LSN   | 0                                          | Loudspeaker Output: LSP, LSN are differential output pins which can drive a 50 $\Omega$ loudspeaker directly; a piezo transducer can also be used for ringing signal instead of the loudspeaker |

| 17<br>18 | HOP<br>HON   | 0                                          | Handset Earpiece Output: HOP, HON are differential output pins which can drive handset earpiece transducers directly                                                                            |

Overview

# 1.6 Logic Symbol

Figure 2 Logic Symbol of the ARCOFI®

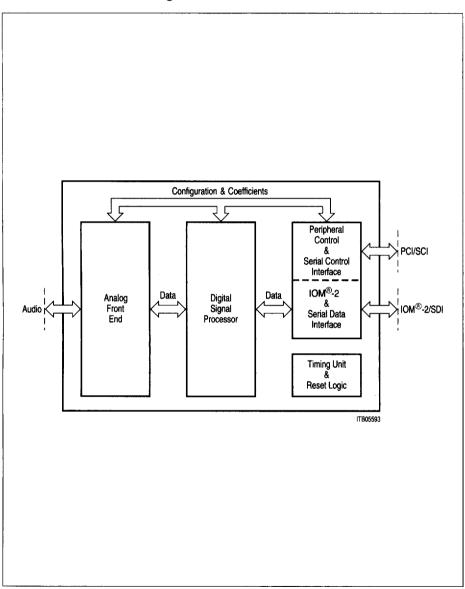

# 1.7 Functional Block Diagram

Figure 3

Block Diagram of the ARCOFI®

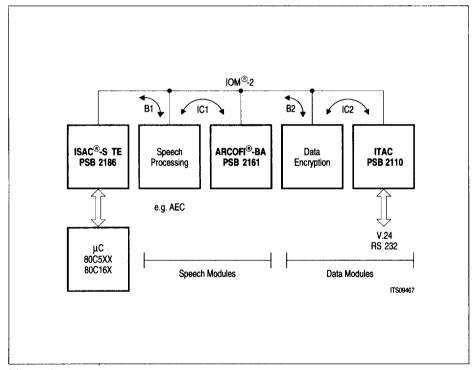

#### 1.8 System Integration

The complete family of ICs for digital terminals offered by Siemens simplifies the development of these devices and gives a cost-effective solution to the design engineer. The architecture of these terminals is based on a modular interface especially conceived for ISDN and named IOM-2.

**Figure 4** shows an example of an integrated multifunctional ISDN terminal using the ISAC-S TE. The ISAC-S TE (ISAC-S: ISDN S-Access controller PSB 2186) provides the S-interface and separates the B and D channels.

A voice processor is connected to the programmable digital signal processing codec filter (ARCOFI-BA) via IC1 and a data encryption module to a data device via IC2. B1 is used for voice communication and B2 for data communication.

Typical terminal applications are described in the next sections.

Figure 4

Example of ISDN Voice/Data Terminal

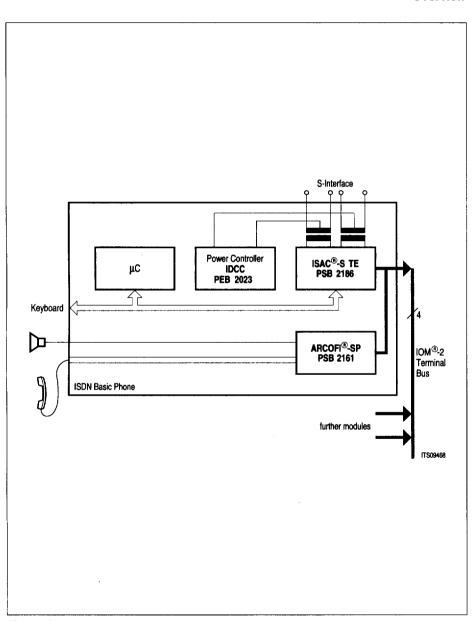

#### 1.8.1 ISDN-Voice Terminal

Figure 5 shows a typical solution for a voice terminal for S interface.

The ARCOFI offers the functions of CODEC and filtering. It also carries out the functions of tone ringing, DTMF, and A/D and D/A conversions. The ARCOFI permits the direct connection of a handset and a loudspeaker.

The ARCOFI can be programmed and read out by the  $\mu$ C via the IOM-2 interface and the ISAC-S TE. The same  $\mu$ C supervises the keyboard functions and the function hook-ON/OFF.

The S-interface functions such as activation/deactivation, clock recovery, clock resynchronization as well as the layer-2 functions like LAPD protocol handling are executed by the ISDN Subscriber Access Controller.

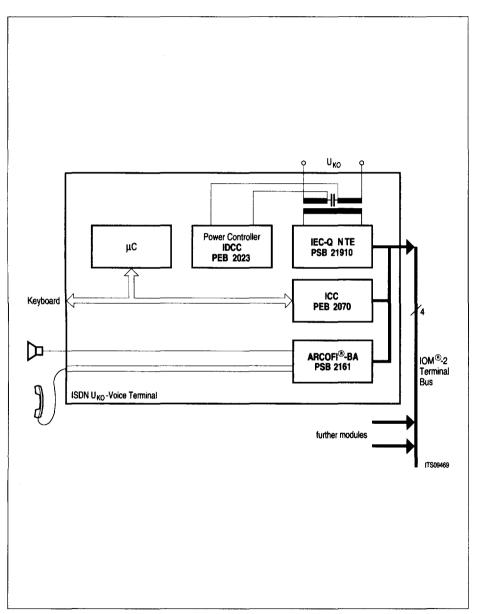

A U-interface telephone can easily be derived from the voice terminal shown on **figure 5** by replacing the ISAC-S with the ISDN Communication Controller ICC PEB 2070 and the ISDN-Echo Cancellation Unit IEC-Q NTE (PSB 21910).

Figure 6 shows such a typical solution for a voice terminal with U-interface.

In both cases the whole terminal is power supplied by the ISDN DC Converter Circuit IDCC PEB 2023.

Overview

Figure 5

Basic ISDN S-Voice Terminal

#### Overview

Figure 6

Basic ISDN U-Voice Terminal

#### 1.8.2 Digital PABX Voice Terminal

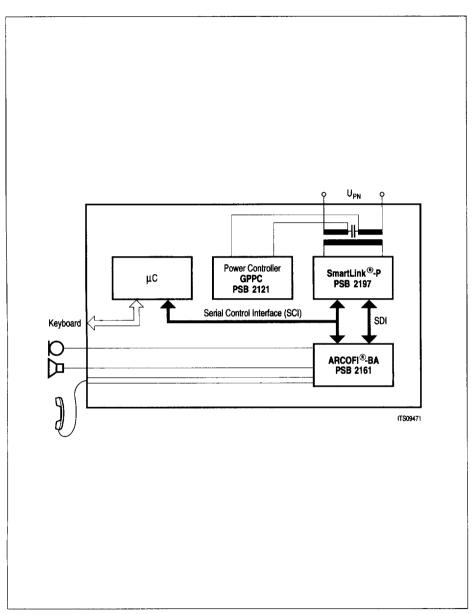

The Serial Control Interface allows the ARCOFI to be programmed directly from a serial port of a microcontroller.

The voice data may be transmitted via the IOM-2 interface or on a PCM interface provided from other transceiver devices. If the Serial Data Interface (SDI) is selected the PCM data rate can vary from 64 kbit/s up to 4096 kbit/s.

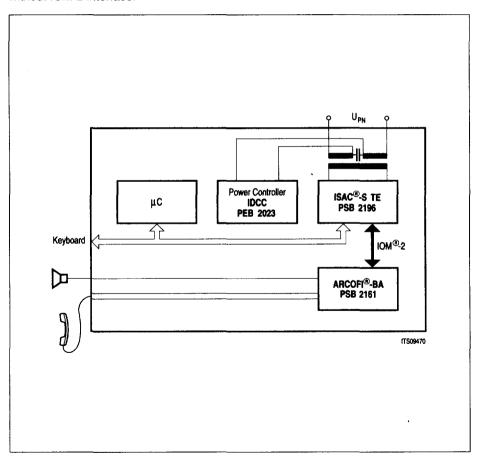

Figure 7 shows a PABX voice terminal using the ISAC-P TE PSB 2196 together with a microcontroller. Figure 8 shows a PABX-voice terminal using a transceiver device without IOM-2 interface.

Figure 7

UPN PABX Voice Terminal

Figure 8

PABX Voice Terminal in NON-IOM®-2 Architecture

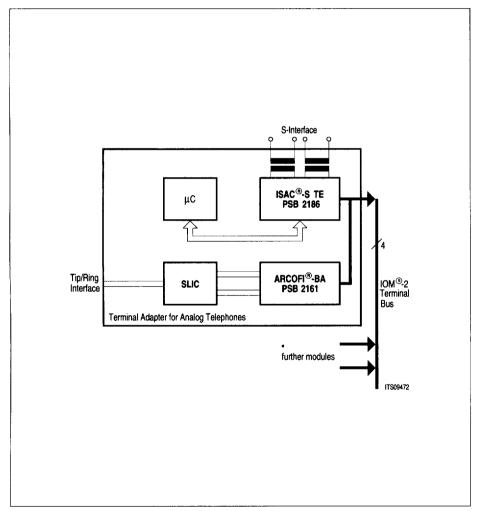

#### 1.8.3 Terminal Adapter for Analog Telephones

Figure 9 shows how to implement a terminal adapter (tip/ring) connecting analog telephones to the ISDN world. A SLIC can be connected to the ARCOFI.

The tip and ring information is transmitted transparently through the ARCOFI via the C/I-channel of the IOM channel 1 through the ISAC-S TE to the  $\mu$ C.

Figure 9

Terminal Adapter Tip/Ring for Analog Telephones

#### 1.8.4 Voice/Data Terminal (PC-Card)

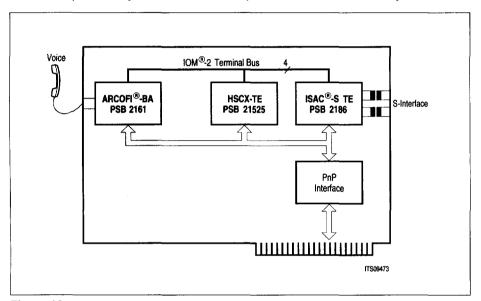

**Figure 10** shows a voice/data terminal developed on a PC-card. The HSCX-TE (PSB 21525) offers a low cost data interface (e.g. X.25) from the host to the ISDN world via the IOM-2 interface.

The card is powered by the PC, and thus no power controller is necessary.

Figure 10 PC-Card as an ISDN Voice/Data Terminal

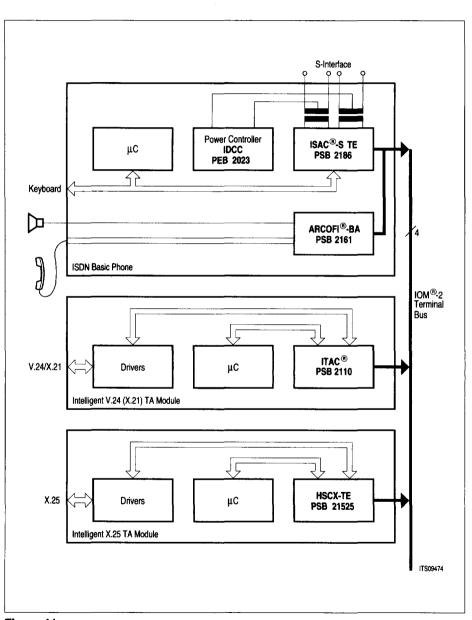

#### 1.8.5 Multifunctional ISDN Terminal

**Figure 11** gives an example of a multifunctional terminal. The HSCX-TE PSB 21525 (High-Level Serial Communications Controller Extended for Terminal Applications) simplifies the realization of an intelligent X.25 terminal adapter module whereas the ITAC PSB 2110 offers X.21, V.24, V.110 or V.120 interfaces for non ISDN terminals.

The  $\mu$ C connected to the ISAC-S TE PSB 2186 is the system master. The two other  $\mu$ Cs are the slaves. When a slave  $\mu$ C wants access to the  $\mu$ C bus, it informs the master via the C/l-channel of IOM-2 channel 1.

#### Overview

Figure 11 Multifunctional ISDN Terminal

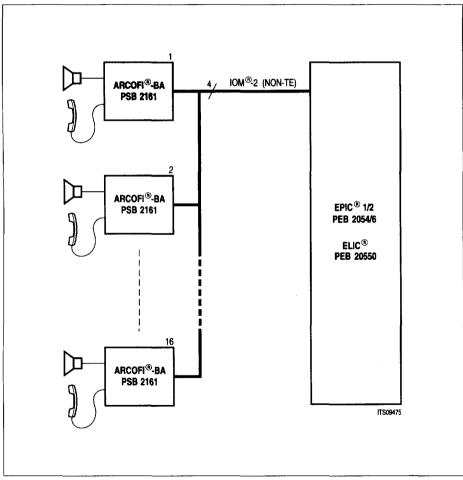

## 1.8.6 IOM®-2 Line Card Application

Some applications require the ARCOFI to connect directly to the IOM-2 interface of a line card. The IOM channel is selected via pin-strapping. The ARCOFI is programmed via the MONITOR channel of the selected IOM channel. Up to two ARCOFIs can be distinguished via AD input on the same IOM channel.

This configuration allows control of up to 16 ARCOFIs at one IOM-2 interface of a line card controller.

Figure 12

ARCOFI® Line Card Application

Overview

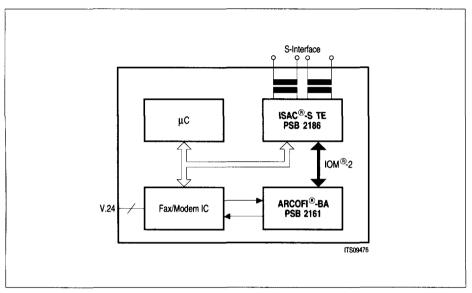

## 1.8.7 Group 3 Fax/Modem Adapter

The ARCOFI can be connected to a standard fax or modem chip set designed for analog networks. The ARCOFI converts the analog signal to PCM data which are transmitted over the digital network.

Figure 13 Group 3 Fax/Modem Adapter

## 2 Functional Description

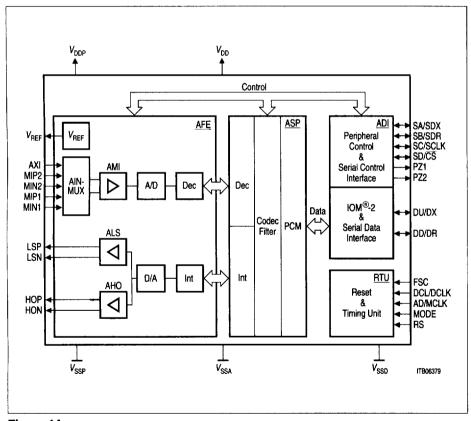

The ARCOFI bridges the gap between the audio world of microphones, earphones, loudspeakers and the PCM digital world by providing a full PCM Codec with all the necessary transmit and receive filters. A block diagram of the ARCOFI is shown in figure 14.

The ARCOFI can be subdivided in three main blocks:

- The ARCOFI Analog Front End (AFE)

- The ARCOFI Signal Processor (ASP)

- The ARCOFI Digital Interface (ADI)

A detailed description can be found in the following chapters.

Figure 14

Architecture of the ARCOFI®

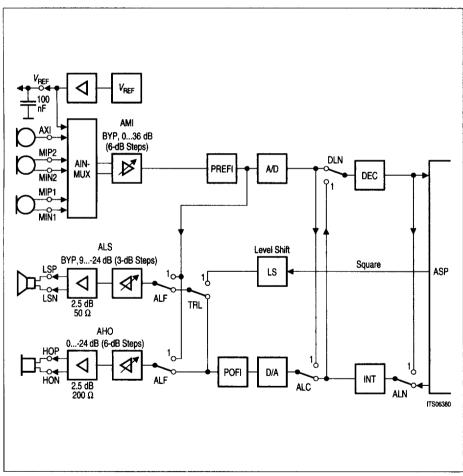

### 2.1 Analog Front End (AFE) Description

The Analog Front End section of the ARCOFI is the interface between the analog transducers and the digital signal processor. In the transmit direction, the AFE function is to amplify the transducer input signals (microphones) and to convert them into digital signals. In the AFE receive section, the incoming digital signal is converted to an analog signal which is output to an earpiece and/or a loudspeaker.

A block diagram of the AFE is shown in figure 15.

Figure 15 Signal Flow Graph of the AFE

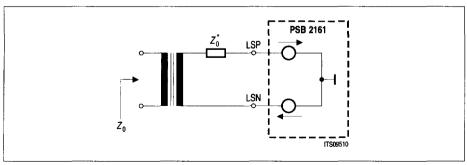

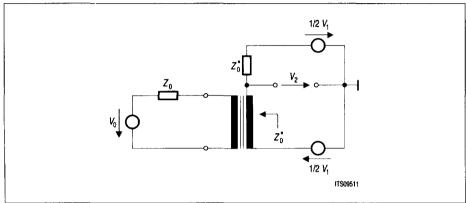

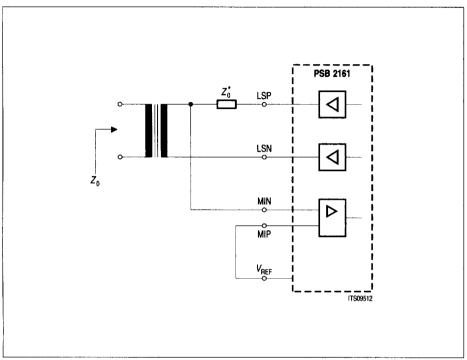

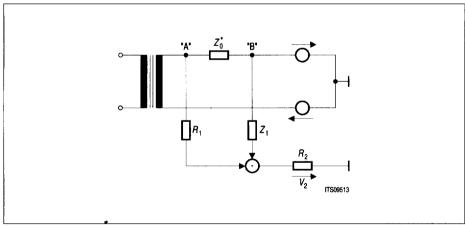

## 2.1.1 Description of the Analog I/O

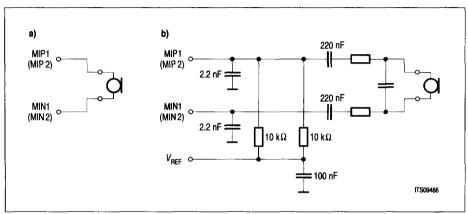

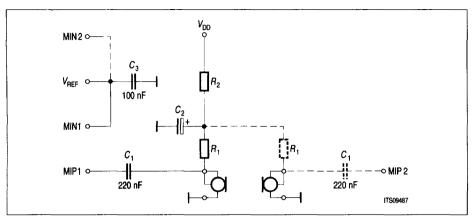

Two differential inputs (MIP1/MIN1 and MIP2/MIN2) and one single-ended input (AXI) are connected to the amplifier AMI via an analog input multiplexer. The programmable amplifier AMI provides a coarse gain adjustment range. Fine gain adjustment is performed in the digital domain via the programmable gain adjustment stage GX (see signal processor section). This allows a perfect level adaptation to various types of microphone transducers without loss in the signal to noise performance.

Fully differential output HOP/HON connects the amplifier AHO to a handset earpiece. Differential output LSP/LSN is provided for use with a 50  $\Omega$  loudspeaker. Up to 100 mW (sine wave) of power can be delivered to the loudspeaker via the amplifier ALS. The programmable amplifiers AHO and ALS provide a coarse gain adjustment range. Fine gain adjustment is performed in the digital domain via the programmable adjustment stage GR.

Two implemented AFE configuration registers (ATCR, ARCR) provide a high flexibility to accommodate an extensive set of user procedures and terminal attributes.

#### 2.1.2 AFE Attenuation Plan

#### Transmit Direction

| Parameter                          | Limit '     | Values   | Unit | Reference |

|------------------------------------|-------------|----------|------|-----------|

| Transmit                           | 0dBm0       | max.     | 1    |           |

| MIP1/MIN1                          | 2.65E-02    | 3.81E-02 | Vp   | ٧         |

| MIP2/MIN2                          | 1.87E-02    | 2.70E-02 | Vrms | V         |

| Microphone input level at max gain | <b>– 36</b> | - 32.86  | dBm0 | 1.18 V    |

| AMI = 36 dB                        | - 32.33     | - 29.19  | dBm  | 0.775 V   |

| MIP1/MIN1                          | 1.67E-00    | 2.40E-00 | Vp   | ٧         |

| MIP2/MIN2                          | 1.18E-00    | 1.70E-00 | Vrms | V         |

| Microphone input level at min gain | 0           | 3.14     | dBm0 | 1.18 V    |

| AMI = 0 dB                         | 3.67        | 6.81     | dBm  | 0.775 V   |

| AXI                                | 1.06E-01    | 1.51E-01 | Vp   | ٧         |

| Input level at max gain            | 7.46E-02    | 1.07E-01 | Vrms | V         |

| AMI = 24 dB                        | - 24        | - 20.86  | dBm0 | 1.18 V    |

|                                    | - 20.37     | - 17.19  | dBm  | 0.775 V   |

| AXI                                | 8.36E-01    | 1.20E-00 | Vp   | V         |

| Input level at min gain            | 5.91E-01    | 8.49E-01 | Vrms | V         |

| AMI = 0 dB                         | - 6         | - 2.86   | dBm0 | 1.18 V    |

|                                    | - 2.33      | 0.81     | dBm  | 0.775 V   |

## **Functional Description**

## **Receive Direction**

| Parameter                | Limit '  | Values   | Unit | Reference |

|--------------------------|----------|----------|------|-----------|

| Receive                  | 0dBm0    | max.     | 1    |           |

| LSP/LSN                  | 2.23E-00 | 3.20E-00 | Vp   | V         |

| Output level symmetrical | 1.58E-00 | 2.26E-00 | Vrms | V         |

| in a 50-Ω load           | 2.5      | 5.64     | dBm0 | 1.18 V    |

| ALS = 2.5 dB             | 6.17     | 9.31     | dBm  | 0.775 V   |

| LSP/LSN                  | 1.41E-01 | 2.02E-01 | Vp   | V         |

| Output level symmetrical | 9.95E-02 | 1.43E-01 | Vrms | V         |

| in a $50-\Omega$ load    | - 21.5   | - 18.36  | dBm0 | 1.18 V    |

| ALS = - 21.5 dB          | - 17.83  | - 14.69  | dBm  | 0.775 V   |

| HOP/HON                  | 2.23E-00 | 3.20E-00 | Vp   | V         |

| Output level symmetrical | 1.58E-00 | 2.26E-00 | Vrms | V         |

| in a 200-Ω load          | 2.5      | 5.64     | dBm0 | 1.18 V    |

| AHO = 2.5 dB             | 6.17     | 9.31     | dBm  | 0.775 V   |

| HOP/HON                  | 1.41E-01 | 2.02E-01 | Vp   | V         |

| Output level symmetrical | 9.95E-02 | 1.43E-01 | Vrms | V         |

| in a 200-Ω load          | - 21.5   | - 18.36  | dBm0 | 1.18 V    |

| ALS = -21.5 dB           | - 17.83  | - 14.69  | dBm  | 0.775 V   |

## **Functional Description**

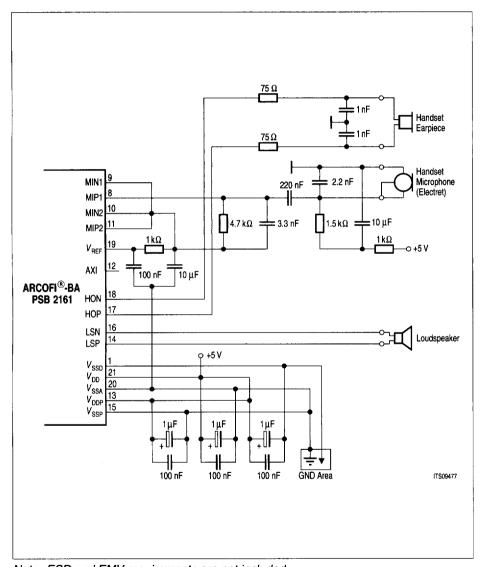

### 2.1.3 Interface to Acoustic Transducers

Note: ESD and EMV requirements are not included.

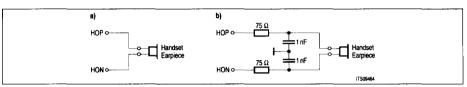

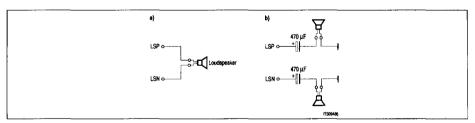

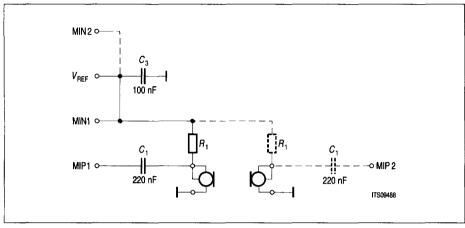

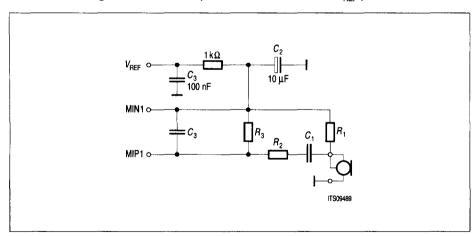

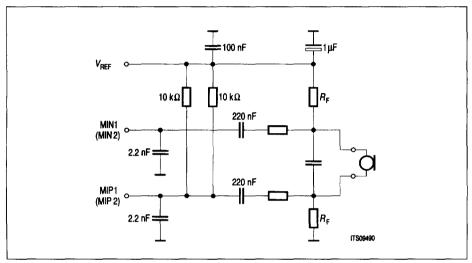

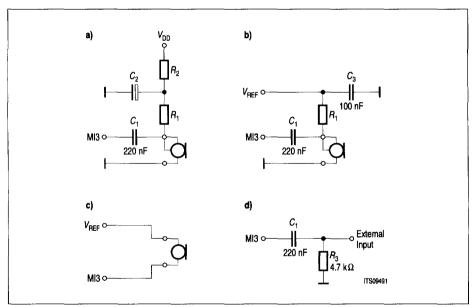

Figure 16

Example to Connect the AFE to Acoustic Transducers

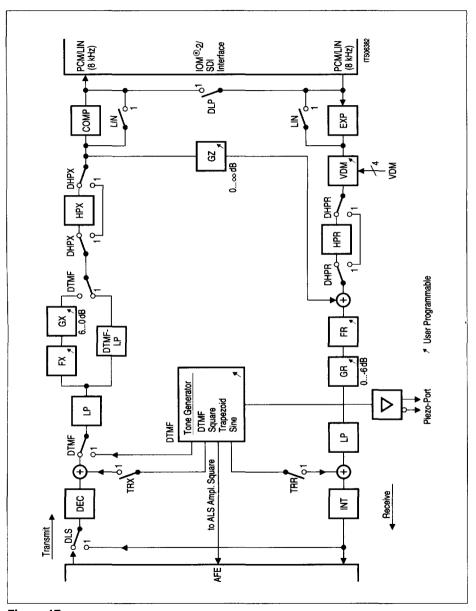

### 2.2 ARCOFI® Signal Processor (ASP) Description

The ARCOFI signal processor (ASP) has been conceived to perform all ITU-T and ETSI (NET33) recommended filtering in transmit and receive paths and is therefore fully compatible to the ITU-T G.712 and ETSI (NET33) specifications. The data processed by the ASP is provided in the transmit direction by an oversampling A/D-converter situated in the analog front end (AFE). Once processed, the speech signal is converted into an 8-bit A-law or  $\mu$ -law PCM format or remains as a 16-bit linear word (2s complement) if the compander is bypassed. The bypassing of the companding depends on the bit setting in the configuration register DFICR (VDM-bits).

In the receive direction, the incoming PCM stream is expanded into a linear format (if the linear mode is selected, the expansion logic is bypassed) and subsequently processed until it is passed to the oversampling D/A-converter.

Additionally to these standard codec functions, the ARCOFI provides a universal tone generation unit.

## **Functional Description**

Figure 17 Processor Signal Flow Graph

#### 2.2.1 Transmit Signal Processing

In the transmit direction a series of decimation filters reduces the sampling rate down to the 8-kHz PCM-rate. These filters attenuate the out-of-band noise by limiting the transmit signal to the voice band.

The decimation stages end with a EWDF low-pass filter which band limits the voice signal to the ITU-T G.712 and ETSI (NET33) recommendations. The ARCOFI meets or exceeds all the ITU-T and ETSI (NET33) recommendations on attenuation distortion and group delay distortion.

If the tone generation unit is connected to the transmit direction (TGSR.DTMF = 1), a special 2-kHz DTMF low-pass filter is placed in the transmit path. This filter guarantees an attenuation of all unwanted frequency components, if DTMF signals are transmitted. Additionally, it is possible to add a programmable tone signal to the transmit voice signal (TGSR.TRX = 1).

The GX-gain adjustment stage is digitally programmable allowing the gain to be programmed from + 6 to 0 dB in steps of  $\leq$  0.25 dB ( $-\infty$  dB and others are also possible). Two bytes are necessary to set GX to the desired value. On reset, the GX-gain stage is bypassed.

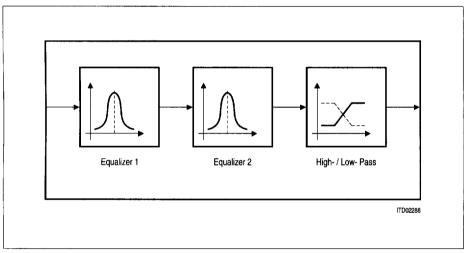

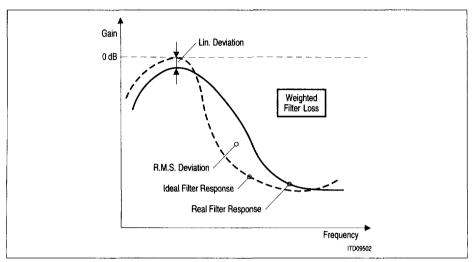

The transmit path contains a programmable high performance frequency response correction filter FX allowing an optimum adaptation to different types of microphones (dynamic, piezoelectric or electret). Twelve bytes are necessary to set FX to the desired frequency correction function. On reset, the FX-frequency correction filter is bypassed. **Figure 18** shows the architecture of the FX/FR-filter.

A high-pass filter (HPX) is also provided to remove power line frequencies.

The voice signal, after being linearly processed, can be output as an 8-bit PCM-word according to the ITU-T G.711 A-law or the North-American  $\mu$ -law format. If desired the companding stage can be bypassed, a 16-bit linear word (2s complement) is then output to the IOM-2 or SDI interface.

## 2.2.2 Receive Signal Processing

In the receive path the incoming PCM-signal is expanded into a linear code according to the selected A-law or  $\mu$ -law. If the linear mode is chosen, the PCM-expander circuit is bypassed and a 16-bit linear word (2s complement) has to be provided to the processor.

The block VDM offers several possibilities of voice/data manipulation for special applications.

A programmable sidetone gain stage GZ adds a sidetone signal to the incoming voice signal. The sidetone gain can be programmed from – 54 to 0 dB within a  $\pm$  1 dB tolerance range ( $-\infty$  dB and others are also possible). Respectively two bytes are coded in the CRAM to set GZ to the desired value. On reset, the GZ-gain stage is disabled ( $-\infty$  dB).

A high-pass filter (HPR) is also provided to remove disturbances from 0 to 50/60 Hz due to the telecommunication network.

The FR-frequency correction response filter is similar to the FX-filter allowing an optimum adaptation to different types of loudspeakers or earpieces. Twelve bytes are necessary to set FR to the desired frequency correction function. On reset, the FR-frequency correction filter is bypassed.

The GR-gain adjustment stage is digitally programmable from -6 to 0 dB in steps  $\leq 0.25$  dB ( $-\infty$  dB and others are also possible). Respectively two bytes are coded in the CRAM to set GR to the desired value. On reset, the GR-gain stage is bypassed.

A low-pass EWDF-filter limits the signal bandwidth in the receive direction according to ITU-T and ETSI (NET33) recommendations.

A series of low-pass interpolation filters increases the sampling frequency up to the desired value. The last interpolator feeds the D/A-converter.

Figure 18

Architecture of the FX- and FR-Correction Filter

### 2.2.3 Programmable Coefficients

This section gives a short overview of important programmable coefficients. For more detailed information and about special applications, a special coefficient software package is available (ARCOS-SP PLUS SIPO 2163).

Description of the programmable level adjustment parameters:

| Parameter | No. of CRAM<br>Bytes | Range       | Comment                                                          |

|-----------|----------------------|-------------|------------------------------------------------------------------|

| GX        | 2                    | F           | Transmit gain adjustment Transmission characteristics guaranteed |

| GR        | 2                    |             | Receive gain adjustment Transmission characteristics guaranteed  |

| GZ        | 2                    | 0 to - ∞ dB | Sidetone gain adjustment                                         |

Coefficients for GX, GR and GZ:

| Gain [dB] | MSB             | LSB             | Gain [dB]    | MSB             | LSB             | Gain [dB]       | MSB             | LSB             |

|-----------|-----------------|-----------------|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 12.0      | 10 <sub>H</sub> | 01 <sub>H</sub> | 0            | A0 <sub>H</sub> | 01 <sub>H</sub> | - 12.0          | A9 <sub>H</sub> | 01 <sub>H</sub> |

| 11.0      | 10H             | 31 <sub>H</sub> | - 0.5        | B3 <sub>H</sub> | 42 <sub>H</sub> | - 13.0          | 9CH             | 51 <sub>H</sub> |

| 10.0      | 10H             | 13 <sub>H</sub> | - 1.0        | A3 <sub>H</sub> | 2B <sub>H</sub> | - 14.0          | 99 <sub>H</sub> | 13 <sub>H</sub> |

| 9.0       | 01H             | 4B <sub>H</sub> | - 1.5        | A2H             | 32 <sub>H</sub> | <b>– 15.0</b>   | 8C <sub>H</sub> | 1B <sub>H</sub> |

| 8.0       | 20 <sub>H</sub> | 94 <sub>H</sub> | - 2.0        | BBH             | 4A <sub>H</sub> | <b>– 16.0</b>   | 82 <sub>H</sub> | 7BH             |

| 7.0       | 30 <sub>H</sub> | 94 <sub>H</sub> | <b>– 2.5</b> | BBH             | 13 <sub>H</sub> | <b> </b> - 17.0 | 84 <sub>H</sub> | 4B <sub>H</sub> |

| 6.0       | 13 <sub>H</sub> | 51 <sub>H</sub> | - 3.0        | BAH             | 29 <sub>H</sub> | <b>–</b> 18.0   | 89 <sub>H</sub> | 6A <sub>H</sub> |

| 5.5       | B0 <sub>H</sub> | 39H             | - 3.5        | BAH             | 5B <sub>H</sub> | <b>– 19.0</b>   | 8B <sub>H</sub> | 0CH             |

| 5.0       | A0 <sub>H</sub> | 49 <sub>H</sub> | - 4.0        | A2H             | 01 <sub>H</sub> | - 20.0          | 84 <sub>H</sub> | 1C <sub>H</sub> |

| 4.5       | 23 <sub>H</sub> | 01 <sub>H</sub> | - 4.5        | AAH             | 1B <sub>H</sub> | - 21.0          | 8C <sub>H</sub> | 1C <sub>H</sub> |

| 4.0       | 22 <sub>H</sub> | B4 <sub>H</sub> | <b>–</b> 5.0 | 9B <sub>H</sub> | 3A <sub>H</sub> | - 22.0          | 82 <sub>H</sub> | 7C <sub>H</sub> |

| 3.5       | 23 <sub>H</sub> | 12 <sub>H</sub> | - 5.5        | AAH             | 33 <sub>H</sub> | - 23.0          | 84 <sub>H</sub> | 4C <sub>H</sub> |

| 3.0       | 32 <sub>H</sub> | A4 <sub>H</sub> | - 6.0        | AAH             | 22 <sub>H</sub> | - 24.0          | 89 <sub>H</sub> | 6B <sub>H</sub> |

| 2.5       | B1 <sub>H</sub> | BCH             | <b>-</b> 7.0 | B9H             | 2CH             | - 25.0          | 8B <sub>H</sub> | 0D <sub>H</sub> |

| 2.0       | B1 <sub>H</sub> | 03H             | - 8.0        | 9A <sub>H</sub> | BCH             | - 26.0          | 84 <sub>H</sub> | 1DH             |

| 1.5       | 33 <sub>H</sub> | 39 <sub>H</sub> | <b>–</b> 9.0 | 9B <sub>H</sub> | 13 <sub>H</sub> | - ∞             | 88 <sub>H</sub> | 01 <sub>H</sub> |

| 1.0       | B2 <sub>H</sub> | 5A <sub>H</sub> | - 10.0       | 9B <sub>H</sub> | 32 <sub>H</sub> |                 |                 | ''              |

| 0.5       | взн             | 49 <sub>H</sub> | - 11.0       | 93 <sub>H</sub> | 02 <sub>H</sub> |                 |                 |                 |

#### 2.2.4 Tone Generation

#### 2.2.4.1 Tone Generation Architecture

The ASP contains a universal tone generator which can be used for tone alerting, call progress tones, DTMF signals or other audible feedback tones.

For the receive channel, a universal switching to each signal path (earpiece, loudspeaker and piezo ringer) is implemented. In the earpiece and loudspeaker direction, an addition of the programmed tone sequence (sine-wave, trapezoid, square-wave and DTMF) with the incoming voice signal is possible.

For the transmit direction, a supplementary DTMF generator is implemented. If the DTMF generator is active (TGSR.DTMF = 1), only a part of the tone generator (TG) is available for the receive direction (one or two tone sequences). In addition, a universal switching to the transmit path is also possible (TGSR.TRX).

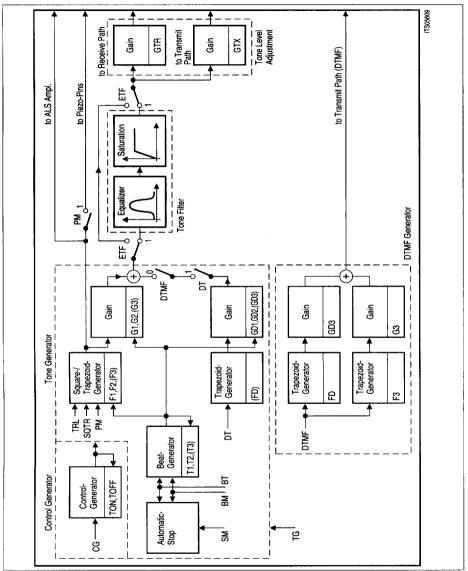

All the tone generation configurations are programmable in the registers TGCR and TGSR (see description in **chapter 4**). A signal flow graph of the ARCOFI tone generation unit is shown in **figure 20**.

The tone generation can be subdivided into five main blocks:

- Control Generator (CG)

- Tone Generator (TG)

- Tone Filter (TF)

- Tone Level Adjustment (TLA)

- DTMF Generator (DTG)

A detailed description of the five main tone generation blocks follows in the next subsections.

## **Functional Description**

Note: Adjustments in brackets are only available if the DTMF generator is switched off (TGCR.DTMF = 0).

Figure 19

Signal Flow Graph of the Tone Generation Unit

#### 2.2.4.2 Control Generator

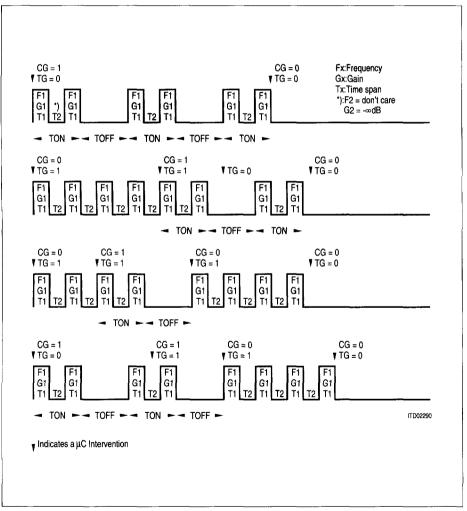

In conjunction with the control generator it is possible to generate very complex signal sequences without reprogramming the necessary parameters (e.g. pulsed three tone calls). Four typical applications for the control generator programming are shown in figure 20.

Figure 20

Typical Control Generator Application

Function table of CG/TG-bit setting in TGCR:

| TON/TOFF | CG | TG | Generator Output                                  |

|----------|----|----|---------------------------------------------------|

| X        | 0  | 0  | No tone                                           |

| X        | 0  | 1  | Ringing sequence F1, F2, F3 without break         |

| TOFF     | 1  | X  | Break between two ringing sequences of F1, F2, F3 |

| TON      | 1  | x  | Ringing sequence until next break                 |

Description of the programmable parameters:

| Parameter | # of CRAM<br>Bytes | Range           | Comment                                       |

|-----------|--------------------|-----------------|-----------------------------------------------|

| TON       | 2                  | 20 ms to 16 min | Period while the tone generator is turned on  |

| TOFF      | 2                  | 20 ms to 16 min | Period while the tone generator is turned off |

#### 2.2.4.3 Tone Generator

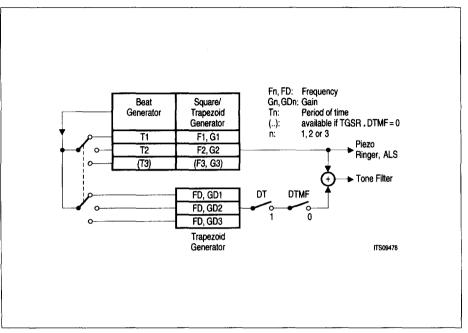

The tone generator contains a beat generator, a square/trapezoid generator, a second trapezoid generator and an automatic stop for two and three tone ringing signals. With the automatic stop function (SM-bit setting in TGCR) the multitone generation can be stopped after a sequence is completed. This avoids unpleasant sounds when stopping the tone generator.

If the control generator is activated (TGCR.CG = 1) the bit setting of TG is insignificant. Otherwise (TGCR.CG = 0) the TG-bit setting controls the activities of the tone generator.

A functional diagram of the tone generator is shown in figure 21.

Figure 21 Functional Diagram of the Tone Generator

Distinctive alerting signals, allowing for example the use of different multitone ringing patterns, are all programmable using the beat tone generator in conjunction with the square/trapezoid generator. In the case of two or three tone ringing signals, the square/trapezoid generator controls the output frequency pitch whilst the beat generator controls the repetition rate. Either square or trapezoid shaped tones can be generated depending on the TGCR.SQTR bit setting. If the piezo mode (PM or TRL in TGSR) is chosen, only a square-wave is available (fixed amplitude of  $V_{\rm DD}$ ). In this case the SQTR-bit in TGCR has no effect.

A secondary trapezoid generator is also built into the ARCOFI. Depending on the DT-bit setting in the TGCR, the output signal of this generator is added to the output signal of the Square/Trapezoid (S/T) generator. In conjunction with the S/T generator, a wide variety of different dual tone signals can be programmed.

If the beat generator (TGCR.BT = 1) is enabled, the automatic stop function (SM-bit setting in TGCR) can be activated. This prevents an uncontrolled turn-off of the tone generator. Only when the generation of the frequency F2 or F3 (depending on the BM-bit setting in TGCR) has been completed, the tone generator will switch off.

## **Functional Description**

## Beat generator programming:

| ВТ | ВМ | DT | Generator Output                                                     |

|----|----|----|----------------------------------------------------------------------|

| 0  | 0  | 0  | Continuous signal F1, G1                                             |

| 0  | 0  | 1  | Continuous signal F1, G1 + FD, GD1                                   |

| 0  | 1  | 0  | Continuous signal F2, G2                                             |

| 0  | 1  | 1  | Continuous signal F2, G2 + FD, GD2                                   |

| 1  | 0  | 0  | Alternating signal F1, G1, T1; F2, G2, T2                            |

| 1  | 0  | 1  | Alternating signal F1, G1, T1; F2, G2, T2 + FD, GD1, T1; FD, GD2, T2 |

| 1  | 1  | 0  | Alternating signal F1, G1, T1; F2, G2, T2; F3, G3, T3                |

| 1  | 1  | 1  | Alternating signal F1, G1, T1; F2, G2, T2; F3, G3, T3 +              |

|    |    |    | FD, GD1, T1; FD, GD2, T2; FD, GD3, T3                                |

## Description of the programmable parameters:

| Parameter | No. of CRAM<br>Bytes | Range             | Comment                                        |

|-----------|----------------------|-------------------|------------------------------------------------|

| Fn        | 2/2/2                | 50 Hz to 4 kHz    | Trapezoid shaped tone                          |

|           |                      | 16 kHz/m; (m ≥ 3) | Square-wave signal                             |

| Gn        | 1/1/1                | 0 dB to - 48 dB   | Gain adjustment for square/trapezoid generator |

| Tn        | 2/2/2                | 10 ms to 8 s      | Period of time for two or three tone sequences |

| FD        | 2                    | 50 Hz to 4 kHz    | Trapezoid shaped tone                          |

| GDn       | 1/1/1                | 0 dB to - 48 dB   | Gain adjustment for trapezoid generator        |

#### n is either 1, 2 or 3

Note: 0 dB gain setting of G1, G2 or G3 and GD1, GD2 or GD3 corresponds to the maximum PCM level (A-Law: + 3.14 dBm0)

#### 2.2.4.4 Tone Filter

The tone filter contains a programmable equalizer and a saturation amplifier (see figure 19). If no filter function is necessary, a bypass mode can be used (TGCR.ETF = 0). A brief description of the tone filter follows below.

The equalizer is realized as a band-pass filter. The filter parameters (center frequency, bandwidth, and attenuation of the stopband) are programmable.

A generated square-wave or trapezoid signal can be converted by the equalizer into a sine-wave signal. A maximum attenuation of the first harmonic frequency of 50 dB is possible.

The two main purposes of the programmable saturation amplification are:

- Level balancing of the filtered signal (avoidance of overload effects).

- Amplification up to + 12 dB followed by a saturation (3.14 dBm0) of the incoming signal. This saturation amplification converts a sine-wave signal into a square-wave or a trapezoid signal where their edges are eliminated. This method produces pleasant ringing tones.

Description of the programmable parameters:

| Parameter | No. of CRAM<br>Bytes | Range           | Comment                                                                                      |

|-----------|----------------------|-----------------|----------------------------------------------------------------------------------------------|

| A1        | 1                    | 200 Hz to 4 kHz | Center frequency                                                                             |

| A2        | 1                    | 0 to - 1        | Determines with A1 and K the bandwidth. The closer A2 comes to -1, the smaller the bandwith. |

| K         | 1                    | 0 to 54 dB      | Attenuation of the stopband                                                                  |

| GE        | 1                    | + 12 to - 12 dB | Saturation amplification                                                                     |

### 2.2.4.5 Tone Level Adjustment

The two level adjustment stages GTR and GTX determines the output levels of the tone generation (see figure 19).

Description of the programmable parameters:

| Parameter | No. of<br>CRAM<br>Bytes | Range                            | Comment                                                                    |

|-----------|-------------------------|----------------------------------|----------------------------------------------------------------------------|

| GTX       | 1                       | 0 dB to - 50 dB<br>(also - ∞ dB) | Level adjustment for the output which is connected to the transmit channel |

| GTR       | 1                       | 0 dB to - 50 dB<br>(also - ∞ dB) | Level adjustment for the output which is connected to the receive channel  |

#### 2.2.4.6 DTMF Generator (transmit)

The DTMF generator contains two independent trapezoid generators which can be programmed in a wide frequency and gain range. If the DTMF generator is active (TGSR.DTMF = 1), the output signal is automatically switched to the transmit direction. In this case the attenuation of the unwanted frequency components is executed by a special DTMF low-pass filter to the following limits:

| Frequency Band | Min. Attenuation |

|----------------|------------------|

| 0 - 300 Hz     | 33 dB            |

| 300 - 3400 Hz  | 20 dB            |

| 3400 – 4000 Hz | 33 dB            |

The pre-emphasis of 2 dB between the high and the low DTMF frequency groups has to be set with the independent gain stages for the two trapezoid generators (G3 and GD3). All generated DTMF frequencies are guaranteed within a  $\pm 1$  % deviation.

## **Functional Description**

DTMF-frequency (F3, FD) programming:

| ITU-T Q.23 | ARCOFI® Nominal | Relative Deviation | Coefficients |     |  |

|------------|-----------------|--------------------|--------------|-----|--|

|            |                 | from ITU-T         | high         | low |  |

| Low Group  |                 |                    |              |     |  |

| 697        | 697.1           | + 143 ppm          | 4F           | 16  |  |

| 770        | 770.3           | + 390 ppm          | A6           | 18  |  |

| 852        | 852.2           | + 235 ppm          | 45           | 1B  |  |

| 941        | 941.4           | + 425 ppm          | 20           | 1E  |  |

| High Group |                 |                    |              |     |  |

| 1209       | 1209.5          | + 414 ppm          | B4           | 26  |  |

| 1336       | 1336.9          | + 674 ppm          | C8           | 2A  |  |

| 1477       | 1477.7          | + 474 ppm          | 49           | 2F  |  |

| 1633       | 1632.8          | – 122 ppm          | 40           | 34  |  |

Note: The deviations due to the inaccuracy of the incoming clock DCL/MCLK, when added to the nominal deviations tabulated above give the total absolute deviation from the ITU-T recommended frequencies.

Description of the programmable parameters:

| Parameter | No. of CRAM<br>Bytes | Range           | Comment                                   |

|-----------|----------------------|-----------------|-------------------------------------------|

| F3        | 2                    | 50 Hz to 4 kHz  | Trapezoid shaped tone 1                   |

| G3        | 1                    | 0 dB to - 48 dB | Gain adjustment for trapezoid generator 1 |

| FD        | 2                    | 50 Hz to 4 kHz  | Trapezoid shaped tone 2                   |

| GD3       | 1                    | 0 dB to - 48 dB | Gain adjustment for trapezoid generator 2 |

## 2.3 ARCOFI® Digital Interface (ADI)

The ADI-function consists of two interface blocks:

- The Peripheral Control Interface (PCI) or the Serial Control Interface (SCI)

- The IOM-2 interface (TE or NON-TE timing mode) or the Serial Data Interface (SDI)

Supplementary functions are accessed by strapping the pins MODE and AD according to the following table:

| Pin MODE | Pin AD | Mode         | Description                       |

|----------|--------|--------------|-----------------------------------|

| 0        | 0      | IOM-2 TE     | IOM-2 TE timing mode (AD = 0)     |

| 0        | 1      | IOM-2 TE     | IOM-2 TE timing mode (AD = 1)     |

| 0        | MCLK   | Test         |                                   |

| 1        | 0      | IOM-2 NON TE | IOM-2 NON-TE timing mode (AD = 0) |

| 1        | 1      | IOM-2 NON TE | IOM-2 NON-TE timing mode (AD = 1) |

| 1        | MCLK   | SDI          | Serial Data Interface             |

A detailed description is in the following chapter.

#### 2.3.1 PCI-interface

The Peripheral Control Interface (PCI) provides 4 programmable I/O pins to control the peripheral devices (for more detailed information see section 4, DFICR). These four interface pins are only available in the IOM-2 terminal mode (TE mode).

Otherwise three pins (SB, SC, SD) are used as slot select pins in the IOM-2 NON-TE mode or used as a Serial Control Interface (SCI).

| SA-SD       | Mode         |

|-------------|--------------|

| PCI         | IOM-2 TE     |

| Slot Select | IOM-2 NON TE |

| SCI         | Serial Mode  |

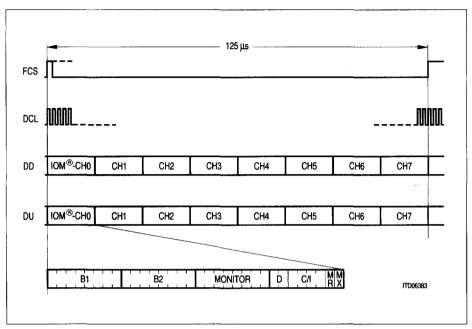

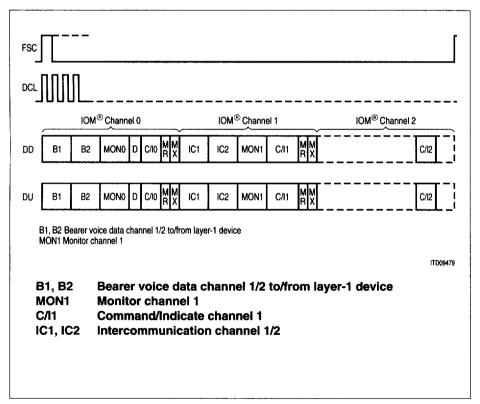

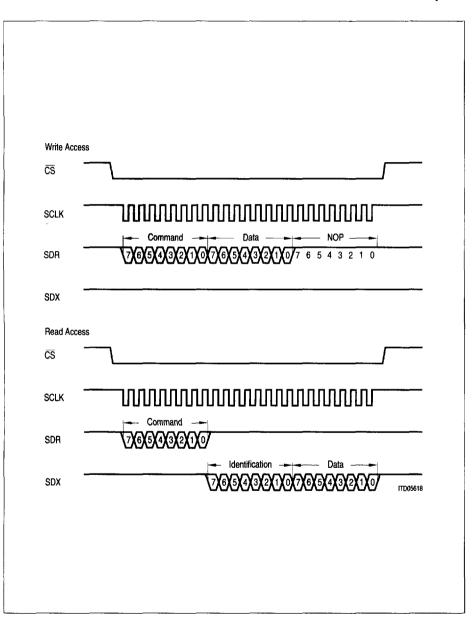

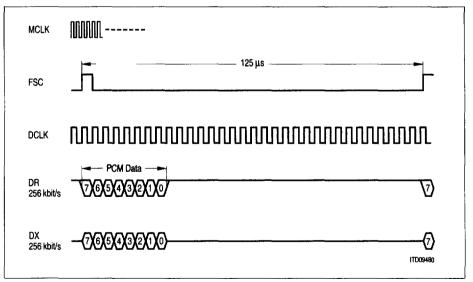

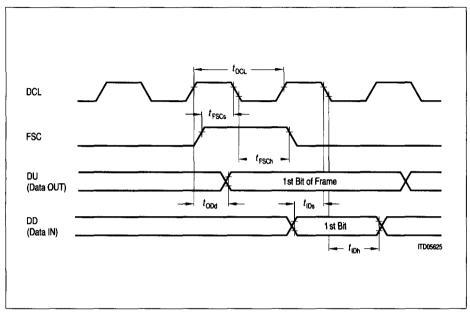

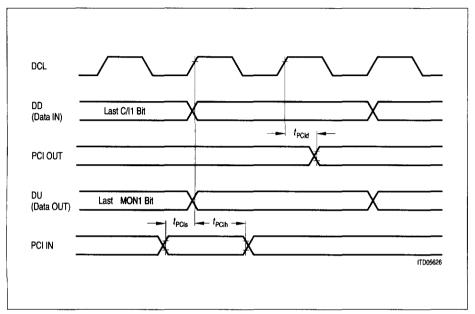

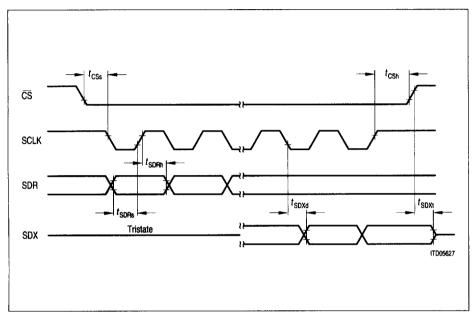

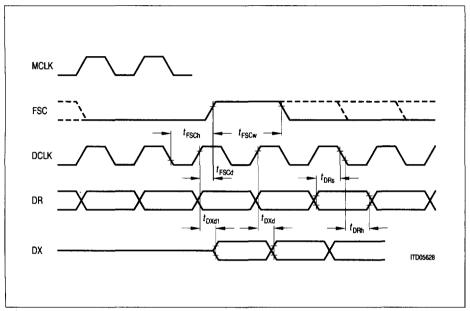

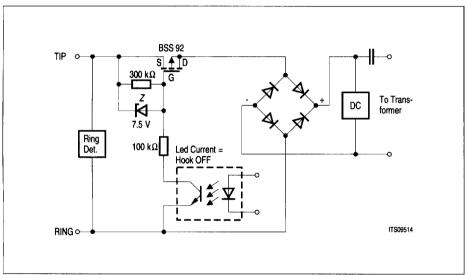

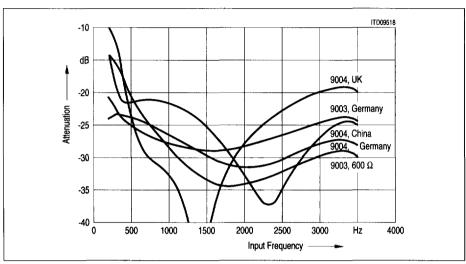

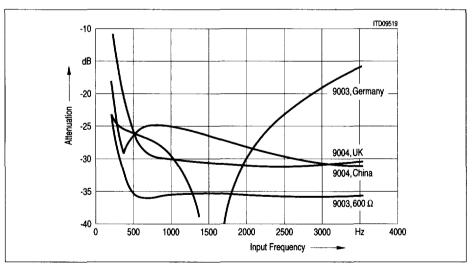

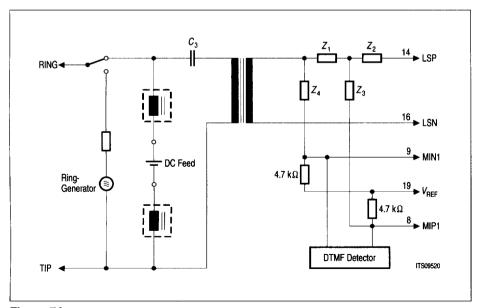

## 2.3.2 IOM®-2 Frame Structure and Timing Modes