# Am2502/3/4 Family

## Eight-Bit/Twelve-Bit Successive Approximation Řegisters

#### **Distinctive Characteristics**

- Contains all the storage and control for successive approximation A-to-D converters.

- Provision for register extension or truncation.

- Can be operated in START-STOP or continuous conversion mode.

- Can be used as serial-to-parallel converter or ring counters

- Electrically tested and optically inspected dice for the assemblers of hybrid products.

#### **FUNCTIONAL DESCRIPTION**

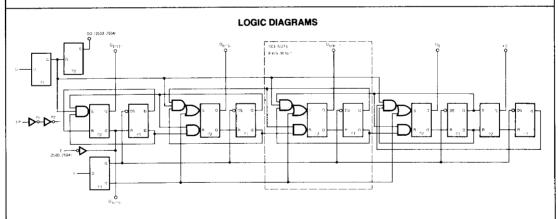

The Am2502, Am2503 and Am2504 are 8-bit and 12-bit TTL Successive Approximation Registers. The registers contain all the digital control and storage necessary for successive approximation analog-to-digital conversion. They can also be used in digital systems as the control and storage element in recursive digital routines.

The registers consist of a set of master latches that act as the control elements in the device and change state when the input clock is LOW, and a set of slave latches that hold the register data and change on the input clock LOW-to-HIGH transition. Externally the device acts as a special purpose serial-to-parallel converter that accepts Ata at the D input of the register and sends the data to the appropriate slave latch to appear at the register output and the DO output on the Am2502 and Am2504 when the clock goes from LOW-to-HIGH. There are no restrictions on the data input; it can change state at any time except during the set-up time just prior to the clock transition. At the same time that data enters the register bit the next less significant bit is set to a LOW ready for the next iteration.

The register is reset by holding the  $\overline{S}$  (Start) signal LOW during the clock LOW-to-HIGH transition. The register synchronously resets to the state  $O_7(11)$  LOW, (Note 2) and all the remaining register outputs HIGH. The  $\overline{CC}$  (Conversion Complete) signal is also set HIGH at this time. The  $\overline{S}$  signal should not be brought back HIGH until after the

clock LOW-to-HIGH transition in order to guarantee correct resetting. After the clock has gone HIGH resetting the register, the  $\overline{S}$  signal is removed. On the next clock LOW-to-HIGH transition the data on the D input is set into the  $\Omega_7(11)$  register bit and the  $\Omega_6(10)$  register bit is set to a LOW ready for the next clock cycle. On the next clock LOW-to-HIGH transition data enters the  $\Omega_6(10)$  register bit and  $\Omega_6(9)$  is set to a LOW. This operation is repeated for each register bit in turn until the register has been filled. When the data goes into  $\Omega_0$ , the  $\overline{CC}$  signal goes LOW, and the register is inhibited from forther change until reset by a Start signal.

In order to allow complementary conversion the complementary output of the most significant register bit is made available. An active LOW enable input,  $\overline{E}$ , on the Am2503 and Am2504 allows devices to be connected together to form a longer register by connecting the clock, D, and  $\overline{S}$  inputs together and connecting the  $\overline{CC}$  output of one device to the  $\overline{E}$  input of the next less significant device. When the Start signal resets the register, the  $\overline{E}$  signal goes HIGH, forcing the  $Q_7(111)$  bit HIGH and inhibiting the device from accepting data until the previous device is full and its  $\overline{CC}$  goes LOW. If only one device is used the  $\overline{E}$  input should be held at a LOW logic level (Ground). If all the bits are not required, the register may be truncated and conversion time saved by using a register output going LOW rather than the  $\overline{CC}$  signal to indicate the end of conversion.

Notes: 1. Cell logic is repeated for register stages.  $Q_5$  to  $Q_1$  Am2502/3,  $Q_9$  to  $Q_1$  Am2504.

2. Numbers in parentheses are for Am2504.

LIC-224

# Am2502/3/4 Family MAXIMUM RATINGS (Above which the useful life may be impaired)

| Storage Temperature                                 | −65 to +150°C                |

|-----------------------------------------------------|------------------------------|

| Supply Voltage to Ground Potential Continuous       | -0.5 to +7V                  |

| DC Voltage Applied to Outputs for High Output State | -0.5 to +V <sub>CC</sub> max |

| DC Input Voltage                                    | -0.5 to +5.5V                |

| Output Current, Into Outputs                        | 30mA                         |

| DC Input Current                                    | -30 to +5 0mA                |

### **ELECTRICAL CHARACTERISTICS** over operating temperature and voltage ranges

|                 |                                |                                                                                                          |             |                 | Aı  | m2502/3 | 3/4             | Am2  | 5L02/L0 | 3/L04 |      |

|-----------------|--------------------------------|----------------------------------------------------------------------------------------------------------|-------------|-----------------|-----|---------|-----------------|------|---------|-------|------|

| Parameters      | Description                    |                                                                                                          | Min         | Typ<br>(Note 1) | Max | Min     | Typ<br>(Note 1) | Max  | Units   |       |      |

| Voн             | Output HIGH Voltage            | V <sub>CC</sub> = MIN, I <sub>OH</sub> = -0.48mA<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> |             |                 | 2.4 | 3.6     |                 | 2.4  | 3.6     |       | ٧    |

| V <sub>OL</sub> | Output LOW Voltage<br>(Note 2) | V <sub>CC</sub> = MIN, i <sub>C</sub><br>V <sub>IN</sub> = V <sub>IH</sub> or V                          |             |                 | 0.2 | 0.4     | 0.15            | 0.3  |         | ٧     |      |

| V <sub>IH</sub> | Input HIGH Level               | Guaranteed in voltage for all                                                                            |             | 2.0             |     |         | 2.0             |      |         | ٧     |      |

| V <sub>IL</sub> | Input LOW Level                | Guaranteed in voltage for all                                                                            |             |                 |     | 0.8     |                 |      | 0.7     | ٧     |      |

|                 | , Unit Load                    | VCC = MAX, VIN = 0.4V                                                                                    |             | CP, D, S        |     | -1.0    | -1.6            |      | -0.25   | -0.4  | 4    |

| l(L             | input LOW Current              | ACC = MYY                                                                                                | /IN = 0.4V  | Ē               |     | 1.5     | -2.4            |      | -0.4    | -0.6  | ⊢ mA |

|                 | Unit Load                      | $V_{CC} = MAX, V_{IN} = 2.4V$ $V_{CC} = MAX, V_{IN} = 5.5V$                                              |             | CP, D           |     | 6.0     | 40              |      | 2.0     | 20    | μΑ   |

| hн              | Input HIGH Current             |                                                                                                          |             | E, S            |     | 12.0    | 80              |      | 4.0     | 40    |      |

|                 | Input HIGH Current             |                                                                                                          |             |                 |     |         | 1.0             |      |         | 1.0   | mA   |

| Isc             | Output Short Circuit Current   | V <sub>CC</sub> = MAX, \                                                                                 | OUT = 0.0V  |                 | -10 | -25     | -45             | -4.0 | -15     | -35   | mA   |

|                 |                                |                                                                                                          | Am25(L)02   | XM              |     | 65      | 85              |      | 25      | 33    | mA   |

|                 |                                |                                                                                                          |             | хс              |     | 65      | 95              |      | 25      | 35    |      |

|                 | Davies County Councet          | V <sub>CC</sub> = MAX                                                                                    | Am25(L)03   | ХМ              |     | 60      | 80              |      | 22      | 31    |      |

| lcc             | Power Supply Current           |                                                                                                          |             | xc              |     | 60      | 90              |      | 22      | 33    |      |

|                 |                                |                                                                                                          | Am25(L)04   | XM              |     | 90      | 110             |      | 30      | 42    |      |

|                 |                                |                                                                                                          | A11125(L)04 | xc              |     | 90      | 124             |      | 30      | 45    |      |

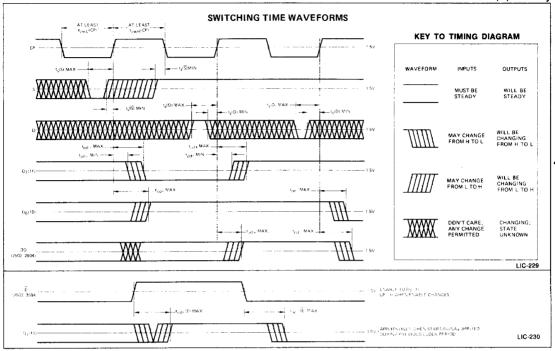

# SWITCHING CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_{CC} = +5.0V$ , $C_L = 15pF$

|                       |                                                              |                                       |     |         |     |     | ]   |       |     |

|-----------------------|--------------------------------------------------------------|---------------------------------------|-----|---------|-----|-----|-----|-------|-----|

|                       |                                                              |                                       | Aı  | m2502/3 | /4  | An  |     |       |     |

| arameters             | Description                                                  | Min                                   | Тур | Max     | Min | Тур | Max | Units |     |

|                       | Turn Off Delay CP to Output HIGH (excep                      | t Q <sub>11</sub> , Q <sub>11</sub> ) | 10  | 29      | 45  | 20  | 75  | 110   |     |

| t <sub>pd+</sub>      | Turn Off Delay CP to Q <sub>11</sub> or Q <sub>11</sub> HIGH | 10                                    | 35  | 50      | 30  | 100 | 140 | ns    |     |

| t <sub>pd</sub> -     | Turn On Delay CP to Output LOW                               | urn On Delay CP to Output LOW         |     |         |     | 20  | 75  | 100   | ns  |

| t <sub>s</sub> (D)    | Setup Time Data Input                                        | -10                                   | 4.0 | 10      | 15  | 8.0 | 20  | ns    |     |

| t <sub>s</sub> (S)    | Setup Time Start Input                                       | Setup Time Start Input                |     | 9.0     | 16  | 0   | 20  | 25    | ns  |

| t <sub>pd+</sub> (E)  | Turn Off Delay E to Q7(11) HIGH                              | Am2503/Am2504)                        |     | 15      | 23  |     | 50  | 75    |     |

| t <sub>pd</sub> _(E)  | Turn On Delay E to Q <sub>7</sub> (11) LOW                   | $C_P = H, \overline{S} = L$           |     | 20      | 30  |     | 60  | 75    | ns  |

| t <sub>pwL</sub> (CP) | Minimum LOW Clock Pulse Width                                |                                       | 28  | 46      |     | 100 | 150 | ns    |     |

| t <sub>pwH</sub> (CP) | Minimum HIGH Clock Pulse Width                               |                                       |     | 12      | 20  |     | 70  | 100   | ns  |

| f <sub>max</sub>      | Maximum Clock Frequency                                      |                                       | 15  | 25      |     | 3.5 | 5.0 |       | MHz |

3-12

Notes: 1. Typical Limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

2. V<sub>OL</sub> (MAX) = 0.4V with total device fanout of less than 50 TTL Unit Loads (80mA). Otherwise, V<sub>OL</sub> (MAX) = 0.45V.

#### **DEFINITION OF TERMS**

#### SUBSCRIPT TERMS:

H -HIGH, applying to a HIGH logic level or when used with  $V_{CC}$  to indicate high  $V_{CC}$  value.

#### 1 Input

L -LOW, applying to LOW logic level or when used with  $V_{CC}$  to indicate low  $V_{CC}$  value.

O Output

#### **FUNCTIONAL TERMS:**

$\label{eq:Fan-Out} \textbf{Fan-Out} \quad \text{The logic HIGH or LOW output drive capability in terms of Input Unit Loads}.$

**Input Unit Load** One  $T^2$  Ligate input load. In the HIGH state it is equal to  $I_{\rm IH}$  and in the LOW state it is equal to  $I_{\rm IL}$ .

CP The clock input of the register.

CC The conversion complete output. This output remains HIGH during a conversion and goes LOW when a conversion is complete.

D The serial data input of the register.

$\bar{E}$  The register enable. This input is used to expand the length of the register and when HIGH forces the  $\Omega_7(11)$  register output HIGH and inhibits conversion. When not used for expansion the enable is held at a LOW logic level (Ground).

Q7(11) The true output of the MSB of the register.

$\overline{Q}_7$ (11) The complement output of the MSB of the register.

$Q_i$  i = 7(11) to 0 The outputs of the register.

$\overline{S}$  The start input. If the start input is held LOW for at least a clock period the register will be resef to  $Q_7(11)$  LOW and all the remaining outputs HIGH. A start pulse that is LOW for a shorter period of time can be used if it meets the set-up time requirements of the  $\overline{S}$  input.

DO The serial data output. (The D input delayed one bit).

#### **OPERATIONAL TERMS:**

IIL Forward input load current.

$I_{\mathrm{OH}}$  Output HIGH current, forced out of output  $V_{\mathrm{OH}}$  test.

$I_{\mbox{\scriptsize OL}}$  Output LOW current, forced into the output in  $V_{\mbox{\scriptsize OL}}$  test.

I<sub>IH</sub> Reverse input load current.

Negative Current Current flowing out of the device.

Positive Current Current flowing into the device.

VIH Minimum logic HIGH input voltage.

VII Maximum logic LOW input voltage.

V<sub>OH</sub> Minimum logic HIGH output voltage with output HIGH current I<sub>OH</sub> flowing out of output.

${\bf V_{OL}}$  Maximum logic LOW output voltage with output LOW current  ${\bf I_{OL}}$  flowing into output.

SWITCHING TERMS: (Measured at the 1.5 V logic level).

$t_{pd-}$  The propagation delay from the clock signal LOW-HIGH transition to an output signal HIGH-LOW transition.

$t_{pd+}$  The propagation delay from the clock signal LOW-HIGH transition to an output signal LOW-HIGH transition.

$t_{pd-}(\bar{E})$  . The propagation delay from the Enable signal HIGH-LOW transition to the  $\Omega_7(11)$  output signal HIGH-LOW transition.

$t_{pd+}(\bar{E})$  The propagation delay from the Enable signal LOW-HIGH transition to  $\Omega_7(11)$  output signal LOW-HIGH transition.

$t_s(D)$  Set-up time required for the logic level to be present at the data input prior to the clock transition from LOW to HIGH in order for the register to respond. The data input should remain steady between  $t_s$  max. and  $t_s$  min. before the clock.

$t_s(\bar{s})$  Set-up time required for a LOW level to be present at the  $\bar{s}$  input prior to the clock transition from LOW to HIGH in order for the register to be reset, or time required for a HIGH level to be present on S before the HIGH to LOW clock transition to prevent resetting.

$\mathbf{t}_{pw}(\text{CP})$  The minimum clock pulse width (LOW or HIGH) required for proper register operation.

#### Am2502/3/4 Family

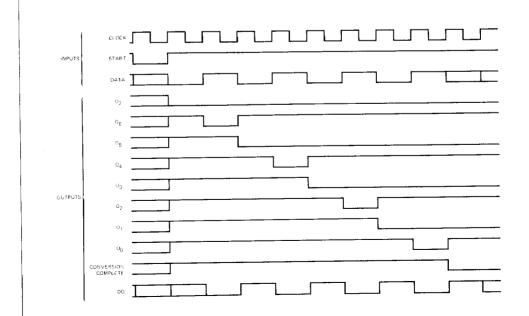

| Time           | in             | pu | ts |                |                |                |                | Out            | puts       |       |       |                |    |

|----------------|----------------|----|----|----------------|----------------|----------------|----------------|----------------|------------|-------|-------|----------------|----|

| t <sub>n</sub> | D              | s  | Ē  | D <sub>0</sub> | α,             | Ω <sub>6</sub> | 05             | 04             | $\sigma_3$ | $a_2$ | 0,    | o <sub>o</sub> | СC |

| 0              | ×              | L  | L  | X              | X              | X              | Х              | Х              | X          | Х     | Х     | Х              | Х  |

| 1              | $D_7$          | н  | L  | X              | L              | Н              | Н              | Н              | Н          | Н     | Н     | H              | Н  |

| 2              | D <sub>6</sub> | н  | L  | $D_7$          | 07             | L              | н              | н              | Н          | Н     | Н     | Н              | Н  |

| 3              | D <sub>5</sub> | н  | L  | D <sub>6</sub> | $D_7$          | $D_6$          | L              | Н              | н          | Н     | Н     | Н              | Н  |

| 4              | D <sub>4</sub> | н  | L  | _              | -              | D <sub>6</sub> | $D_5$          | L              | Н          | Н     | Н     | Н              | Н  |

| 5              | D <sub>3</sub> |    |    | DΔ             |                | _              | D <sub>5</sub> | $D_4$          | L          | Н     | н     | Н              | Н  |

| 6              | D <sub>2</sub> |    |    | -              |                | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | $D_3$      | L     | Н     | н              | Н  |

| 7              | D <sub>1</sub> |    | L  |                |                | D <sub>6</sub> |                |                |            | $D_2$ | L     | Н              | Н  |

| 8              | Do             | н  | L  | D <sub>1</sub> |                | D <sub>6</sub> |                |                | $D_3$      |       | $D_1$ | L              | Н  |

| 9              | x              | н  | L  | ο.             | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | $D_3$      | $D_2$ | $D_1$ | $D_0$          | L  |

| 10             | х              | Х  | L  |                |                | D <sub>6</sub> |                |                |            |       |       | D <sub>0</sub> | L  |

|                | X              | X  | Н  | X              | Н              | NC             | NC             | NC             | NC         | NC    | NC    | NC             | NÇ |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

NC = No Change

Note: Truth Table for Am2504 is extended to include 12 outputs.

#### USER NOTES FOR A/D CONVERSION

- 1. The register can be used with either current switches that require a low voltage level to turn the switch on, or current switches that require a high voltage level to turn the current switch on. If current switches are used which turn on with a low logic level the resulting digital output from the register is active LOW. That is, a logic "1" is represented as a low voltage level. If current switches are used that turn on with a high logic level then the digital output is active HIGH; a logic "1" is represented as a high voltage level.

- For a maximum digital error of ±½LSB the comparator must be biased. If current switches that require a high voltage level to turn on are used, the comparator should be biased ±½LSB and if the current switches require a high logic level to turn on then the comparator must be biased ±½LSB.

- The register, by suitable selection of resistor ladder network, can be used to perform either binary or BCD conversion. Additional data input gating should be used to eliminate the possibility of false BCD codes.

- 4. The register can be used to perform 2's complement conversion by offsetting the comparator ½ full range +½ LSB and using the complement of the MSB Q<sub>7</sub> (Q<sub>11</sub>) as the sign bit.

- If the register is truncated and operated in the continuous conversion mode a lock-up condition may occur on poweron. This situation can be overcome by making the START input the OR function of CC and the appropriate register output.

#### Am25(L)02/3 TIMING CHART

LIC-231

| Am2502/3 LOADING RULES (IN UNIT LOADS) Input Fanout |              |     |              |                |               |  |  |

|-----------------------------------------------------|--------------|-----|--------------|----------------|---------------|--|--|

| Input/Output                                        | Pin<br>No.'s |     | Load<br>HIGH | Output<br>HIGH | Output<br>LOW |  |  |

| Ē (2503)                                            | 1            | 1.5 | 2            |                | -             |  |  |

| DO (2502)                                           | 1            | _   |              | 12             | 6             |  |  |

| CC                                                  | 2            |     | _            | 12             | 6             |  |  |

| $Q_0$                                               | 3            | _   | _            | 12             | 6             |  |  |

| Q <sub>1</sub>                                      | 4            |     |              | 12             | 6             |  |  |

| 02                                                  | 5            |     | _            | 12             | 6             |  |  |

| 0 <sub>3</sub>                                      | 6            | _   | _            | 12             | 6             |  |  |

| D                                                   | 7            | 1   | 1            | -              | _             |  |  |

| GND                                                 | 8            |     | _            | _              | _             |  |  |

| СР                                                  | 9            | 1   | 1            |                | _             |  |  |

| Ī                                                   | 10           | 1   | 2            |                |               |  |  |

| Ο <sub>4</sub>                                      | 11           | _   | _            | 12             | 6             |  |  |

| Ω <sub>5</sub>                                      | 12           | _   |              | 12             | 6             |  |  |

| Q <sub>6</sub>                                      | 13           |     | _            | 12             | 6             |  |  |

| 07                                                  | 14           | _   | -            | 12             | 6             |  |  |

| 07                                                  | 15           | _   | _            | 12             | 6             |  |  |

| V <sub>CC</sub>                                     | 16           |     |              |                |               |  |  |

#### MSI INTERFACING RULES

| Input Un<br>HIGH | it Load          |

|------------------|------------------|

| s 1              | 1                |

| 1                | 1                |

| 1                | 1                |

| 1                | 1                |

| 2                | 2                |

| 1                | 1                |

| 12               | 1                |

|                  | Input Un<br>HIGH |

| Am2504 LOADING RULES (IN UNIT LOADS) Input Fanout |              |             |              |    |               |  |  |  |  |

|---------------------------------------------------|--------------|-------------|--------------|----|---------------|--|--|--|--|

| Input/Output                                      | Pin<br>No.'s | Unit<br>LOW | Load<br>HIGH |    | Output<br>LOW |  |  |  |  |

| Ē                                                 | 1            | 1.5         | 2            |    | _             |  |  |  |  |

| DO                                                | 2            | -           | _            | 12 | 6             |  |  |  |  |

| CC                                                | 3            |             |              | 12 | 6             |  |  |  |  |

| a <sub>0</sub>                                    | 4            | _           | _            | 12 | 6             |  |  |  |  |

| $\Omega_1$                                        | 5            | _           | _            | 12 | 6             |  |  |  |  |

| Q                                                 | 6            |             |              | 12 | 6             |  |  |  |  |

| $\alpha_3$                                        | 7            | -           |              | 12 | 6             |  |  |  |  |

| $Q_{\Delta}$                                      | 8            | _           | -            | 12 | 6             |  |  |  |  |

| Ω <sub>5</sub>                                    | 9            |             | _            | 12 | 6             |  |  |  |  |

| NC                                                | 10           |             |              |    | ***           |  |  |  |  |

| D                                                 | 11           | 1           | 1            | _  | _             |  |  |  |  |

| GND                                               | 12           | _           |              | _  | _             |  |  |  |  |

| СР                                                | 13           | 1           | 1            | _  |               |  |  |  |  |

| Ī                                                 | 14           | 1           | 2            |    | _             |  |  |  |  |

| NC                                                | 15           | _           |              |    | _             |  |  |  |  |

| ο <sub>6</sub>                                    | 16           | _           |              | 12 | 6             |  |  |  |  |

| $\Omega_7$                                        | 17           | -           | _            | 12 | 6             |  |  |  |  |

| Ω <sub>8</sub>                                    | 18           |             |              | 12 | 6             |  |  |  |  |

| Ω <sub>9</sub>                                    | 19           |             |              | 12 | 6             |  |  |  |  |

| Ω <sub>10</sub>                                   | 20           | _           |              | 12 | 6             |  |  |  |  |

| Ω <sub>11</sub>                                   | 21           |             |              | 12 | 6             |  |  |  |  |

| NC                                                | 22           |             |              |    |               |  |  |  |  |

| ō₁1                                               | 23           |             |              | 12 | 6             |  |  |  |  |

| V <sub>CC</sub>                                   | 24           |             |              |    | _             |  |  |  |  |

A Standard TTL Unit Load is defined as 40 $\mu$ A measured at 2.4V HIGH and -1.6mA measured at 0.4V LOW.

NC = No Connection

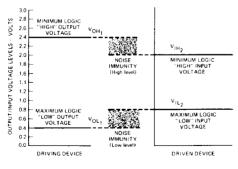

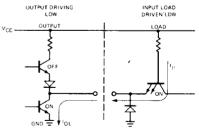

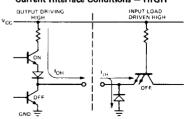

#### INPUT/OUTPUT INTERFACE CONDITIONS

#### Voltage Interface Conditions - LOW & HIGH

#### Current Interface Conditions — LOW

#### Current Interface Conditions - HIGH

LIC-232

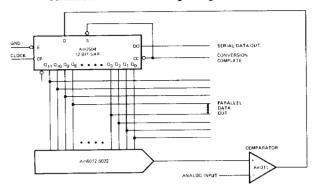

#### Am2502/3/4 APPLICATION Continuous Conversion Analog-to-Digital Converter

This shows how the Am2502/3/4 registers are used with a Digital-to-Analog converter and a comparator to form a very high-speed continuous conversion Analog-to-Digital converter. Conversion time is limited mainly by the speed of the D/A converter and comparator with typical conversion rates of 100,000 conversions per second.

LIC-233

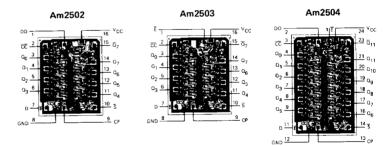

#### Metallization and Pad Layouts

DIE SIZE 0.087" X 0.105"

DIE SIZE 0.087" X 0.105"

DIE SIZE 0.087" X 0.135"

#### ORDERING INFORMATION\*

| Order<br>Number | Order<br>Number | Package<br>Type | Temperature<br>Range | Bits |

|-----------------|-----------------|-----------------|----------------------|------|

| Am2502DM        | Am25L02DM       | Hermetic DIP    | -55 to +125°C        | 8    |

| Am2503DM        | Am25L03DM       | Hermetic DIP    | -55 to +125°C        | 8    |

| Am2504DM        | Am25L04DM       | Hermetic DIP    | -55 to +125°C        | 12   |

| Am2502FM        | Am25L02FM       | Flat Package    | - 55 to +125°C       | 8    |

| Am2503FM        | Am25L03FM       | Flat Package    | -55 to +125°C        | 8    |

| Am2504FM        | AM25L04FM       | Flat Package    | -55 to +125°C        | 12   |

| Am2502XM        | Am25L02XM       | Dice            | -55 to +125°C        | 8    |

| Am2503XM        | Am25L03XM       | Dice            | -55 to +125°C        | 8    |

| Am2504XM        | Am25L04XM       | Dice            | -55 to +125°C        | 8    |

| Am2502DC        | Am25L02DC       | Hermetic DIP    | 0 to +70°C           | 8    |

| Am2503DC        | Am25L03DC       | Hermetic DIP    | 0 to +70°C           | 8    |

| Am2504DC        | Am25L04DC       | Hermetic DIP    | 0 to +70°C           | 12   |

| Am2502PC        | Am25L02PC       | Plastic         | 0 to +70°C           | 8    |

| Am2503PC        | Am25L03PC       | Plastic         | 0 to +70°C           | 8    |

| Am2504PC        | Am25L04PC       | Plastic         | 0 to +70°C           | 12   |

| Am2502XC        | Am25L02XC       | Dice            | 0 to +70°C           | 8    |

| Am2503XC        | Am25L03XC       | Dice            | 0 to +70°C           | 8    |

| Am2504XC        | Am25L04XC       | Dice            | 0 to +70°C           | 12   |

<sup>\*</sup>Also available with burn-in processing. To order add suffix B to part number.