# LF13508 8-Channel Analog Multiplexer LF13509 4-Channel Differential Analog Multiplexer

## **General Description**

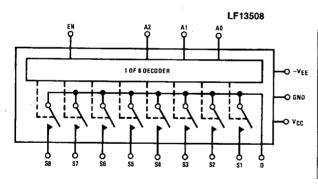

The LF13508 is an 8-channel analog multiplexer which connects the output to 1 of the 8 analog inputs depending on the state of a 3-bit binary address. An enable control allows disconnecting the output, thereby providing a package select function.

This device is fabricated with National's BI-FET technology which provides ion-implanted JFETs for the analog switch on the same chip as the bipolar decode and switch drive circuitry. This technology makes possible low constant "ON" resistance with analog input voltage variations. This device does not suffer from latch-up problems or static charge blow-out problems associated with similar CMOS parts. The digital inputs are designed to operate from both TTL and CMOS levels while always providing a definite break-before-make action.

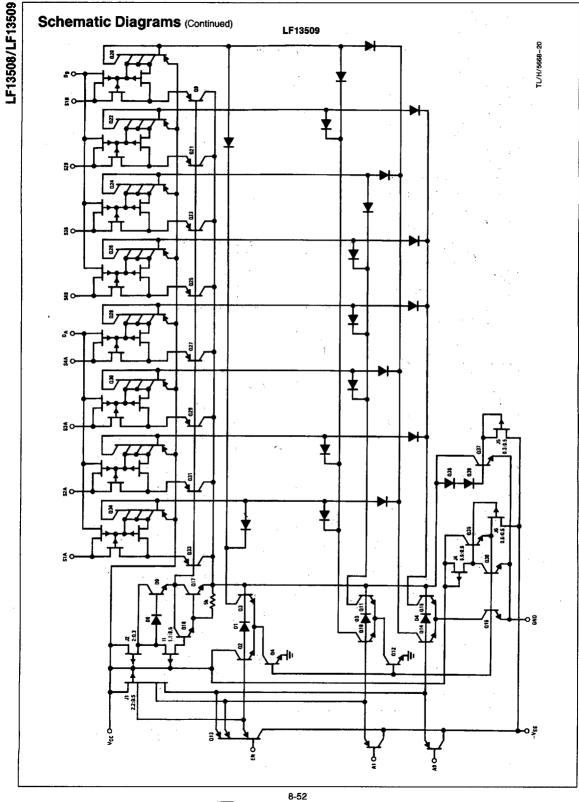

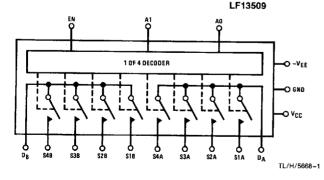

The LF13509 is a 4-channel differential analog multiplexer. A 2-bit binary address will connect a pair of independent

analog inputs to one of any 4 pairs of independent analog outputs. The device has all the features of the LF13508 series and should be used whenever differential analog inputs are required.

### **Features**

- JFET switches rather than CMOS

- No static discharge blow-out problem

- No SCR latch-up problems

- Analog signal range 11V, -15V

- Constant "ON" resistance for analog signals between -11V and 11V

- "ON" resistance 380 Ω typ

- Digital inputs compatible with TTL and CMOS

- Output enable control

- Break-before-make action: t<sub>OFF</sub>=0.2 μs; t<sub>ON</sub>=2 μs typ

- Lower leakage devices available

# **Functional Diagrams and Truth Tables**

| EN | A2 | A1  | <b>A</b> 0 | SWITCH<br>ON |

|----|----|-----|------------|--------------|

| Н  | L  | L   | L          | S1           |

| ·H | L  | L   | Н          | S2           |

| Н  | L  | Н   | L          | S3           |

| Н  | L  | Н   | Н          | S4           |

| Н  | Н  | L   | L          | <b>S</b> 5   |

| Н  | Н  | L   | Н ;        | S6           |

| Н  | Н  | Н ; | L          | <b>S</b> 7   |

| Н  | Н  | Н   | Н          | S8           |

| L  | Х  | Х   | Х          | NONE         |

| EN | <b>A</b> 1 | AO | SWITCH<br>PAIR ON |

|----|------------|----|-------------------|

| L  | х          | X  | None              |

| Н  | L          | L  | S1                |

| Н  | L          | Н  | S2                |

| Н  | H          | L  | S3                |

| Н  | Н          | Н  | S4                |

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Positive Supply — Negative Supply (V<sub>CC</sub>—V<sub>EE</sub>)

Positive Analog Input Voltage (Note 1)

Negative Analog Input Voltage (Note 1)

Negative Analog Input Voltage (Note 1)

Positive Digital Input Voltage

Vcc

Negative Digital Input Voltage

-5V

Negative Digital Input Voltage -5V

Analog Switch Current |Is|<10 mA

Power Dissipation (PD at 25°C)

(Notes 2 & 7)

Molded DIP (N) PD Cavity DIP (D) PD Small Outline (SO) PD 500 mW 900 mW 500 mW

Maximum Junction Temperature (T<sub>jMAX</sub>)

100°C

Operating Temperature Range 0°C≤T<sub>A</sub>≤ +70°C Storage Temperature Range −65°C to +150°C

Lead Temperature

36V

$V_{CC}$

D Package (Soldering, 10 seconds) N Package (Soldering, 10 seconds) 300°C 260°C

Surface Mount Package (SO) Vapor Phase (60 seconds) Infrared (15 seconds)

215°C 220°C

### **Electrical Characteristics (Note 3)**

| Symbol                | Parameter "ON" Resistance                     | Conditions                                                      |                       | LF13508<br>LF13509 |         |     | Units    |

|-----------------------|-----------------------------------------------|-----------------------------------------------------------------|-----------------------|--------------------|---------|-----|----------|

| <b>Oj</b>             |                                               | ·                                                               |                       |                    | Тур Мах | Max | <u> </u> |

| R <sub>ON</sub>       |                                               | V <sub>OUT</sub> = 0V, I <sub>S</sub> = 100 μA                  | T <sub>A</sub> = 25°C |                    | 380     | 650 | Ω        |

| ··OII                 |                                               |                                                                 |                       |                    | 500     | 850 | Ω        |

| ΔR <sub>ON</sub>      | ΔR <sub>ON</sub> with Analog Voltage<br>Swing | $-10V \le V_{OUT} \le +10V$ , $I_S = 100 \mu A$                 | T <sub>A</sub> =25°C  |                    | 0.01    | 1   | %        |

| R <sub>ON</sub> Match | RON Match Between Switches                    | V <sub>OUT</sub> =0V, I <sub>S</sub> =100 μA                    | T <sub>A</sub> = 25°C |                    | 20      | 150 | Ω        |

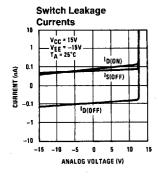

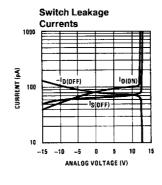

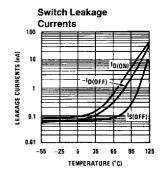

| Is(OFF)               | Source Current in "OFF"<br>Condition          | Switch "OFF", V <sub>S</sub> =11, V <sub>D</sub> =-11, (Note 4) | T <sub>A</sub> =25°C  |                    |         | 5   | nA       |

|                       |                                               |                                                                 |                       |                    | 0.09    | 50  | nA       |

| I <sub>D(OFF)</sub>   | Drain Current in "OFF"<br>Condition           | Switch "OFF", V <sub>S</sub> = 11, V <sub>D</sub> = -11,        | T <sub>A</sub> =25°C  |                    |         | 20  | nA       |

|                       |                                               | (Note 4)                                                        |                       |                    | 0.6     | 500 | nA       |

| I <sub>D</sub> (ON)   | Leakage Current in "ON"<br>Condition          | Switch "ON" V <sub>D</sub> =11V, (Note 4)                       | T <sub>A</sub> = 25°C |                    |         | 20  | nΑ       |

|                       |                                               |                                                                 |                       |                    | 1       | 500 | nA       |

| V <sub>INH</sub>      | Digital "1" Input Voltage                     |                                                                 |                       | 2.0                |         |     | ٧        |

| V <sub>INL</sub>      | Digital "0" Input Voltage                     |                                                                 |                       |                    |         | 0.7 | ٧        |

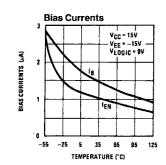

| INL                   | Digital "0" Input Current                     | V <sub>IN</sub> = 0.7V                                          | T <sub>A</sub> =25°C  |                    | 1.5     | 30  | μΑ       |

|                       |                                               |                                                                 |                       |                    |         | 40  | μА       |

| I <sub>INL(EN)</sub>  | Digital "0" Enable Current                    | V <sub>EN</sub> =0.7V                                           | T <sub>A</sub> =25°C  |                    | 1.2     | 30  | μΑ       |

|                       |                                               |                                                                 |                       |                    |         | 40  | μΑ       |

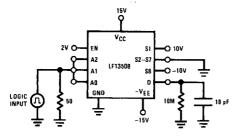

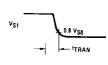

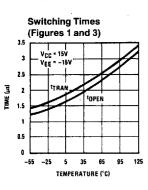

| t <sub>TRAN</sub>     | Switching Time of Multiplexer                 | (Figure 1), (Note 5)                                            | T <sub>A</sub> =25°C  |                    | 1.8     |     | μs       |

| topen                 | Break-Before-Make                             | (Figure 3)                                                      | T <sub>A</sub> =25°C  |                    | 1.6     |     | μs       |

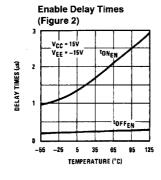

| ton(EN)               | Enable Delay "ON"                             | (Figure 2)                                                      | T <sub>A</sub> =25°C  |                    | 1.6     |     | μs       |

| t <sub>OFF(EN)</sub>  | Enable Delay "OFF"                            | (Figure 2)                                                      | T <sub>A</sub> =25°C  |                    | 0.2     |     | μs       |

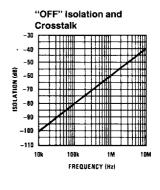

| I <sub>SO(OFF)</sub>  | "OFF" Isolation                               | (Note 6)                                                        | T <sub>A</sub> =25°C  |                    | -66     |     | dB       |

| CT                    | Crosstalk                                     | LF13509 Series, (Note 6)                                        | T <sub>A</sub> = 25°C |                    | -66     |     | dB       |

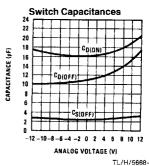

| C <sub>S(OFF)</sub>   | Source Capacitance ("OFF")                    | Switch "OFF", V <sub>OUT</sub> = 0V,<br>V <sub>S</sub> = 0V     | T <sub>A</sub> = 25°C |                    | 2.2     |     | pF       |

| C <sub>D(OFF)</sub>   | Drain Capacitance ("OFF")                     | Switch "OFF", V <sub>OUT</sub> = 0V,<br>V <sub>S</sub> = 0V     | T <sub>A</sub> =25°C  |                    | 11.4    |     | pF       |

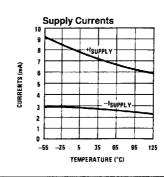

| Icc                   | Positive Supply Current                       | All Digital Inputs Grounded                                     | T <sub>A</sub> =25°C  |                    | 7.4     | 12  | mA       |

|                       |                                               |                                                                 |                       |                    | 7.9     | 15  | , mA     |

| IEE                   | Negative Supply Current                       | All Digital Inputs Grounded                                     | T <sub>A</sub> =25°C  |                    | 2.7     | 5   | mA       |

|                       |                                               |                                                                 |                       |                    | 2.8     | 6   | mA       |

#### Electrical Characteristics (Continued)

Note 1: If the analog input voltage exceeds this limit, the input current should be limited to less than 10 mA.

Note 2: The maximum power dissipation for these devices must be derated at elevated temperatures and is dictated by  $T_{jMAX}$ ,  $\theta_{jA}$ , and the ambient temperature,  $T_A$ . The maximum available power dissipation at any temperature is  $P_D = (T_{jMAX} - T_A)/\theta_{jA}$  or the 25°C  $P_{DMAX}$ , whichever is less.

Note 3: These specifications apply for V<sub>S</sub> = ±15V and over the absolute maximum operating temperature range (T<sub>L</sub>≤T<sub>A</sub>≤T<sub>H</sub>) unless otherwise noted.

Note 4: Conditions applied to leakage tests insure worse case leakages. Exceeding 11V on the analog input may cause an "OFF" channel to turn "ON".

Note 5: Lots are sample tested to this parameter. The measurement conditions of Figure 1 insure worse case transition time.

Note 6: "OFF" isolation is measured with all switches "OFF" and driving a source. Crosstalk is measured with a pair of switches "ON", driving channel A and measuring channel B. R<sub>L</sub> = 200, C<sub>L</sub> = 7 pF, V<sub>S</sub> = 3 Vrms, f = 500 kHz.

Note 7: Thermal Resistance  $\theta_{|A}$  (Junction to Ambient)

Molded DIP (N) Cavity DIP (D) 150°C/W 100°C/W

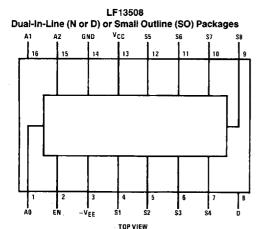

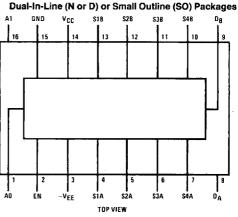

# Connection Diagrams

LF13509

TL/H/5668-2

Order Number LF13508D See NS Package Number D16C Order Number LF13508M See NS Package Number M16A Order Number LF13508N See NS Package Number N16A Order Number LF13509D See NS Package Number D16C Order Number LF13509M See NS Package Number M16A Order Number LF13509N See NS Package Number N16A

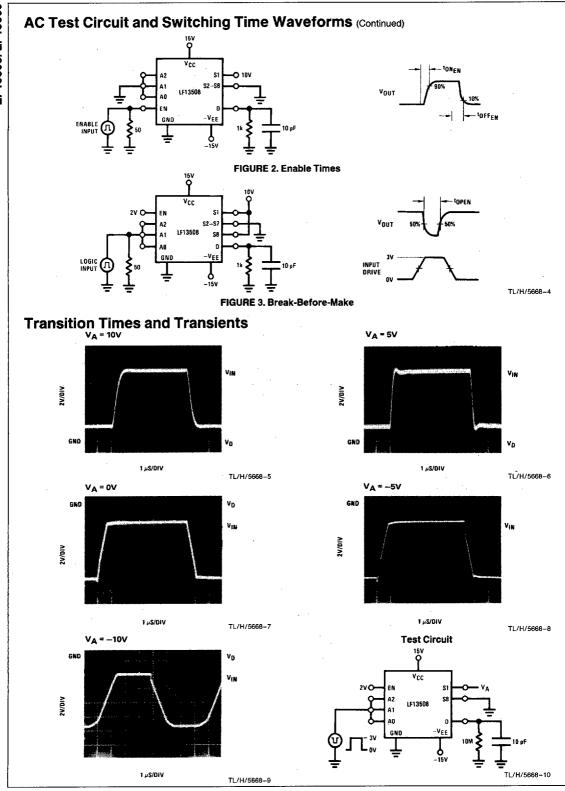

# **AC Test Circuits and Switching Time Waveforms**

FIGURE 1. Transition Time

TL/H/5668-3

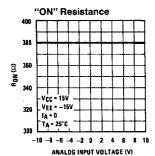

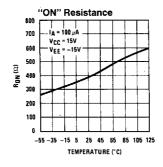

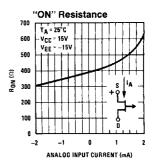

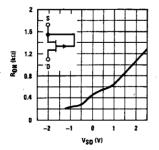

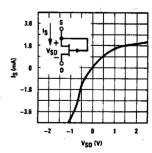

# **Typical Performance Characteristics**

TL/H/5668-11

# **Application Hints**

The LF11508 series is an 8-channel analog multiplexer which allows the connection of a single load to 1 of 8 different analog inputs. These multiplexers incorporate JFETs in a switch configuration which insures a constant "ON" resistance over the analog voltage range of the device. Four TTL compatible inputs are provided; a 3-bit binary decode to select a particular channel and an enable input used as a package select. The switches operate with a break-beforemake action preventing the temporary connection of 2 analog inputs during switching. Because these multiplexers are fabricated with the BI-FET process rather than CMOS, they do not require special handling.

The LF11509 series is a 4-channel differential multiplexer which allows two loads to be connected to 1 of 4 different pairs of analog inputs. The LF11509 series also has all the features of the LF11508.

#### **ANALOG VOLTAGE AND CURRENT**

The "ON" resistance,  $R_{ON}$ , of the analog switches is constant over a wide input range from positive ( $V_{CC}$ ) supply to negative ( $-V_{FE}$ ) supply.

The analog input should not exceed either positive or negative supply without limiting the current to less than 10 mA; otherwise the multiplexer may get damaged. For proper operation, however, the positive analog voltage should be kept equal to or less than  $V_{CC}-4V$  as this will increase the switch leakage in both "ON" and "OFF" state and it may also cause a false turn "ON" of a normally "OFF" switch. This limit applies over the full temperature range.

The maximum allowable switch "ON" voltage (the drop across the switch in the "ON" condition) is  $\pm 0.4V$  over temperature. If this number is to exceed the input current should be limited to 10 mA.

The "ON" resistance of the multiplexing switches varies slightly with analog current because they are JFETs running at 0V gate to source. The JFET characteristics shown in Figure 4 indicates how R<sub>ON</sub> tends to vary with current. A lower R<sub>ON</sub> is possible when the source voltage is negative with respect to the drain voltage because the JFET becomes enhanced. Caution should be used when operating in this mode as this may forward-bias an internal transistor and cause high currents to flow in the switches. Thus, the drain voltage should never be greater than 0.4V positive with respect to the source voltage without limiting the drain current to less than 10 mA.

#### FIGURE 4. JFET Characteristics

#### **LEAKAGE CURRENTS**

Leakage currents will remain within the specified value as long as the drain and source remain within the specified analog voltage range. As the switch terminals exceed the positive analog voltage range "ON" and "OFF" leakage currents increase. The "ON" leakage increases due to an internal clamp required by the switch structure. The "OFF" leakage increases because the gate to source reverse bias has been decreased to the point where the switch becomes active. Leakage currents vary slightly with analog voltage and will approximately double for every 10°C rise in temperature.

#### SWITCHING TIMES AND TRANSIENTS

These multiplexers operate with a break-before-make switch action. The turn off time is much faster than the turn on time to guarantee this feature over the full range of analog input voltage and temperature. Switching transients are introduced when a switch is turned "OFF". The amplitude of these transients may be reduced by increasing the load capacitance or decreasing the load resistance. The actual charge transfer in the transient may be reduced by operating on reduced power supplies. Examples of switching times and transients are shown in the typical characteristic curves. The enable function switching times are specified separately from switch-to-switch transition times and may be thought of as package-to-package transition times.

#### LOGIC INPUTS AND ENABLE INPUT

Switch selection in the LF11508 series is accomplished by using a 3-bit binary decode while the LF11509 series uses a 2-bit decode. These binary logic inputs are compatible with both TTL and CMOS logic voltage levels. The maximum positive voltage applied to these inputs may exceed  $V_{CC}$  but should not exceed  $-V_{EE} + 36V$ . The maximum negative voltage should not be less than 4V below ground as this will cause an internal device to zener and all the switches will turn "ON".

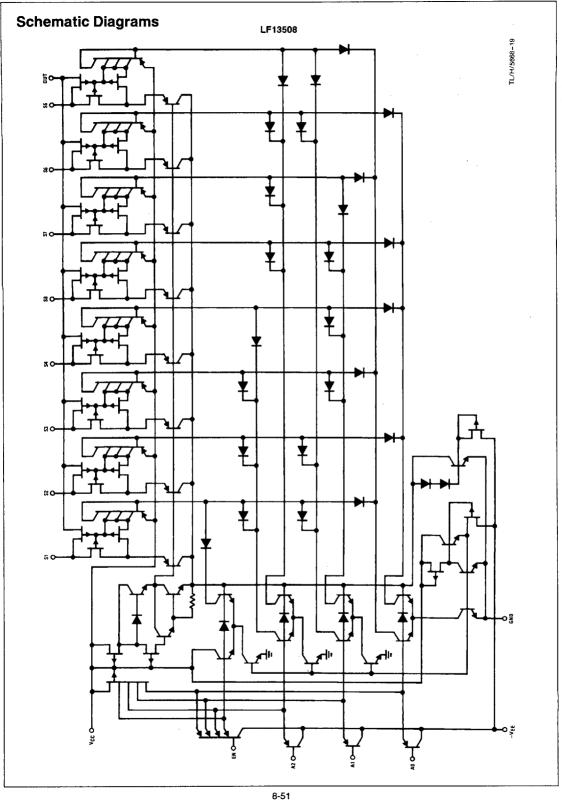

As shown in the schematic diagram, the logic low bias current will flow until the PNP input is raised above the 3 diode reference ( $\approx$  2.1V). Above this voltage the input device becomes reverse biased and the input current drops to the leakage of the reverse biased junction (<0.1  $\mu$ A).

TL/H/5668~12

# R

## **Typical Applications**

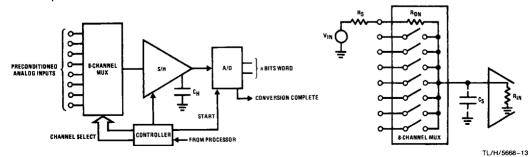

#### **DATA ACQUISITION SYSTEM**

#### A SIMPLIFIED SYSTEM DISCUSSION

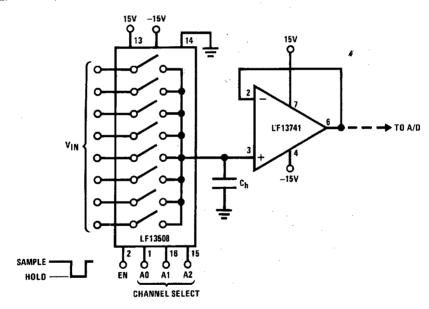

Analog multiplexers (MUX) are usually used for multi-channel Data Acquisition Units (DAU). Figure 5 shows a system in which 8 different analog inputs are sampled and converted into digital words for further processing. The sample and hold circuit is optional, depending on input speed requirements and on A/D converter speed.

Parameters characterizing the system are:

System Channels: The number of multiplexer channels.

**Accuracy:** The conversion accuracy of each individual sample with the system operating at the throughput rate.

Speed or Throughput Rate: Number of samples/second/ channel the system can handle.

For a discussion on system structure, addressing mode and processor interfacing, see application note AN-159.

#### A. ACCURACY CONSIDERATIONS

- 1. Multiplexer's Influence on System Accuracy (Figure 6).

- a. The error, (E), caused by the finite "ON" resistance, R<sub>ON</sub>, of the multiplexing switches is given by:

$$E(\%) = \frac{100}{1 + R_{IN}/(R_{ON} + R_S + \Delta R_{ON})} \text{ where}$$

$R_{IN}$  = following stage input impedance  $\Delta R_{ON}$  = "ON" resistance modulation which is negligible for JFET switches like the LF11508

Example: Let  $R_{ON}=450~\Omega,~\Delta R_{ON}=0,~R_S=0,~T_A=25^{\circ}C$  and allowable E = 0.01% which is equivalent to 1/2 LSB in a 12-bit system:

$$R_{IN} \bigg|_{min} = \frac{R_{ON}(100 - E)}{E} = 4.5 M\Omega$$

Note that if temperature effects are included, some gain (or full scale) drift will occur; but effects on linearity are small.

b. Multiplexer settling time (ts):

$t_{s(ON)}$ : is the time required for the MUX output to settle within a predetermined accuracy, as shown in Table I.

C<sub>S</sub> (Figure 6): MUX output capacitance + following stage input capacitance + any stray capacitance at this node.

#### TABLE I.

| ERROR % | BITS | t <sub>s</sub> (ON)<br>TO 1/2 LSB |

|---------|------|-----------------------------------|

| 0.2     | 8    | 6.2t                              |

| 0.05    | 10   | 7.6t                              |

| 0.01    | 12   | 9t                                |

| 0.0008  | 16   | 11.8t                             |

$$t = C_S (R_{ON} + R_S) \| R_{IN}$$

$t_{s(OFF)}$ : is the time it takes to discharge  $C_S$  within a tolerable error. The "OFF" settling time should be taken into account for bipolar inputs where its effects will appear as a worse case of doubling of the  $t_{s(ON)}$ .

2. Sample and Hold Influence on System Accuracy

The sample and hold, if used, also introduces errors into the system accuracy due to:

- · Offset voltage of sample and hold

- . Droop rate in the Hold mode

- T<sub>A</sub>: Aperture time or time delay between the time of a digital Hold command and the actual Hold occurance

- Taq: Acquisition time or time it takes to acquire an analog input and settle within a predetermined error band

- Hold step: Error created during the Sample to Hold mode caused by an undesirable charge injected into the Hold capacitor C<sub>h</sub>.

For more details on sample and hold errors, see the LF198/LF298/LF398 data sheet.

3. A/D Converter Influence on System Accuracy

The "accuracy" of the A/D converter is the best possible system accuracy. In most data acquisition systems, the A/D converter is the most expensive single component, so its error will often dominate system error. Care should be taken that MUX, S/H and input source errors do not exceed system error requirements when added to A/D errors. For instance, if an 8-bit accuracy system is desired and an 8-bit A/D converter is used, the accuracy of the MUX and S/H should be far better than 8 bits.

For details on A/D converter specifications, see AN-156.

FIGURE 6. 8-Channel MUX

FIGURE 5. Random-Addressed, Multiplexed DAU

### Typical Applications (Continued)

#### **B. SPEED CONSIDERATIONS**

In the system of Figure 5 with the S/H omitted, if n-bit accuracy is desired, the change of the analog input voltage should be less than  $\pm 1/2$  LSB over the A/D conversion time  $T_C$ . In other words, the analog input slew rate, (rate of change of input voltage), will cause a slew-induced error and its magnitude, with respect to the total system error, will depend on the particular application.

$$\left. \frac{\Delta V_{IN}}{\Delta t} \right|_{max} < \frac{\pm 1/2 \ LSB}{T_C} = \frac{V_{FS}}{2^n \times T_C}$$

where V<sub>FS</sub> is the full scale voltage of the A/D. Note that slew induced errors are not affected by the MUX switch time since we can let the unit settle before starting conversion.

Example: Let  $T_C = 40 \mu s$  (MM4357),  $V_{FS} = 10V$  and n = 8.

$$\frac{\Delta V_{IN}}{\Delta t}\Big|_{max} < \frac{1mV}{\mu s}$$

which is a very small number. A 10 Vp-p sine wave of a frequency greater than 32 Hz will have higher slew rate than this. The maximum throughput rate of the above 8-channel system would be calculated using both the A/D conversion time and the sum of MUX switch "ON" time and settling time, i.e.:

Th. R

$$\left| \frac{1}{8(T_C + T_{MUX})} = \frac{3k \text{ samples/sec/}}{\text{channel}} \right|$$

$$T_{MUX} = T_{ON} + T_{S(ON)}$$

Also notice that Nyquist sampling criteria would allow each channel to have a signal bandwidth of 1.5 kHz max, while the slew limit dictates a maximum frequency of 32 Hz. If the input signal has a peak-to-peak voltage less than 10V, the allowable maximum input frequency can be calculated by:

$$f_{MAX} = \frac{\text{(Slew Rate)max}}{\pi \text{ Vp-p}}$$

On the other hand, if the input voltage is not band-limited a low pass filter with an attenuation of 30 dB or better at 1.5 kHz, should be connected in front of the MUX.

Improving System Speed with a Sample and Hold The system speed can be improved by using the S/H shown in Figure 5. This allows a much greater rate of change of V<sub>IN</sub>.

$$\left. \frac{\Delta V_{IN}}{\Delta t} \right|_{max} < \frac{V_{FS}}{2^n \times T_A}$$

where  $T_A$  is the aperture time of the S/H. This represents an input slew rate improvement by a factor:  $T_C/T_A$ . Here again, the slew rate error is not affected by the acquisition time of the Sample and Hold since conversion will start after the S/H has settled. An important thing to notice is that the sample and hold errors will add to the total system error budget; therefore, the inequality of the  $\Delta V_{IN}/\Delta t$  expression should become more stringent.

Example:  $T_C = 40 \mu s$ ,  $T_A = 0.5 \mu s$ , n = 8:  $T_C/T_A = 80$ So the use of a S/H allows a speed improvement by nearly two orders of magnitude.

The maximum throughput rate can be calculated by:

Th. R

$$=\frac{1}{8(T_A + Taq + T_C)}$$

Notice that  $T_{MUX}$  does not affect the  $\Delta V_{IN}/\Delta t$  expression nor the throughput rate of the system since it may be switched and settled while the Sample and Hold is in the Hold mode. This is true, provided that:  $T_{MUX} < T_A + T_C$ .

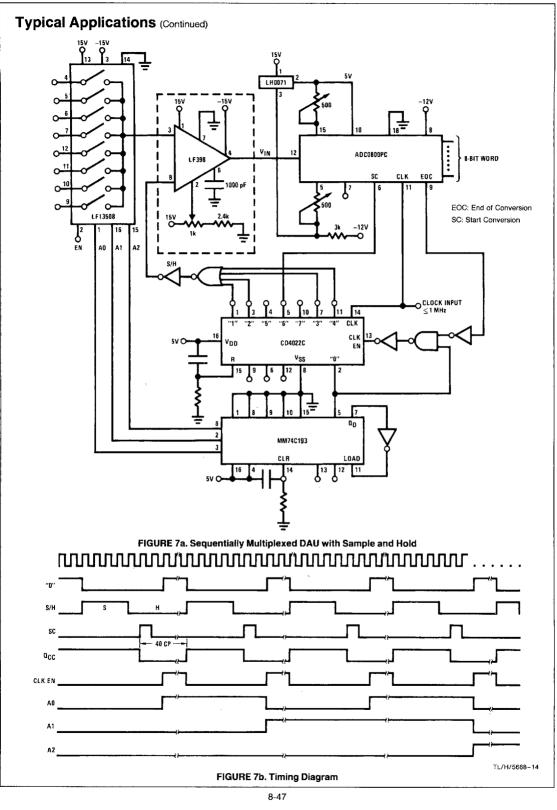

#### C. SYSTEM EXAMPLE (Figure 7)

The LF398 S/H with a 1000 pF hold capacitor, has an acquisition time of 4  $\mu s$  to 0.1% (1/4 LSB error for 8 bits) and an aperture time of less than 200  $\mu s$ . On the other hand, after the hold command, the output will settle to  $\pm 0.05$  mV in 1  $\mu s$ . This, together with the acquisition time, introduces approximately a  $\pm 1/4$  LSB error. Allowing another 1/4 LSB error for hold step and gain non-linearity, the maximum slew error ( $\Delta V_{IN}/\Delta t$ ) should not exceed 1/4 LSB or:

$$\frac{\Delta V_{IN}}{\Delta t} \leq \frac{1}{4} \times \frac{1}{256} \times \frac{1}{T_A} \approx 5 \text{mV}/\mu \text{s}$$

(which is the maximum slew rate of a 5 V peak sine wave. Also notice that, due to the above input slew restrictions, the analog delay caused by the finite BW of the S/H and the digital delay caused by the response time of the controller will be negligible. The maximum throughput rate of the system is:

Th. R

$$\Big|_{\text{max}} = \frac{1}{8(5 + 40)10^{-6}} = 2800 \text{ samples/sec/ch.}$$

If the system speed requirements are relaxed, but the A/D converter is still too slow, then an inexpensive S/H can be built by using just a capacitor and a low cost FET input op amp as shown in *Figure 8*.

### Typical Applications (Continued)

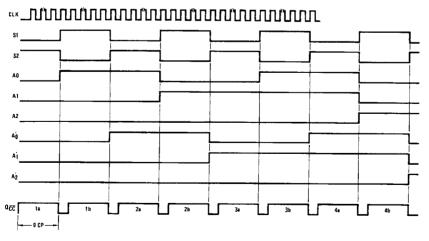

#### D. DOUBLING THE SYSTEM CHANNEL CAPABILITY

This is done in two different ways. First, we can use second level multiplexing with speed benefits, as shown in Figure 9. A fast 2-channel multiplexer, made by the dual analog switch AM182, accepts the outputs of each 8-channel MUX, LF13508, and then feeds them sequentially into an 8-bit successive approximation A/D converter. With this technique, the throughput rate of the system can again be made independent of the LF13508 speed. Looking at the timing diagram, when the A/D converter converts the analog value of an upper multiplexer channel, we switch channels in the lower multiplexer for the next conversion. This can be done provided that:

T<sub>MUX</sub>

$$\leq$$

T<sub>C</sub> + 1 CP

The LF356 connected as unity gain buffers are used because of the low input impedance of the A/D; they are connected between multiplexers for speed optimization. With a maximum clock frequency of 4.5 MHz:

Th. R =

$$\frac{10^6}{16 \times 2}$$

= 31,25k samples/sec/channel

and

$$\frac{\Delta V_{IN}}{\Delta t}\Big|_{max} < \frac{10}{256} \times \frac{1}{2\mu s} = 19.5 \text{ mV/}\mu s \text{ for } 10V_{FS}$$

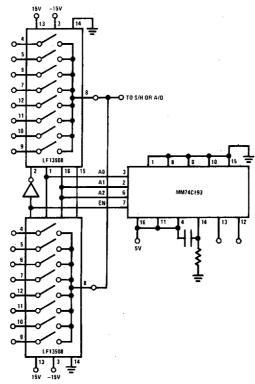

An alternate way to increase the system channel is shown in *Figure 10*, where the enable pins are used to disable one MUX while the other is sampling. With this method, many 8-channel multiplexers can be connected, but the parasitic capacitance at the common output node will keep increasing and will eventually degrade the settling time, t<sub>S(ON)</sub>. Also, the MUX speed will now affect the system throughput. If, for instance, this method was used instead of second level multiplexing, the system of *Figure 9* will lose half of its speed. If, however, speed is not the prime system requirement, the approach of *Figure 10* is more cost effective.

#### E. DIFFERENTIAL INPUT SYSTEMS

Systems operating in industrial environments may require an instrumentation amplifier to separate the desired analog signal from any common-mode signal present. The LF11509 was designed to provide 4 pairs of differential input signals to the input of an instrumentation amplifier for further process.

TL/H/5668-15

- The acquisition time, TA, of the Sample and Hold depends upon: RON, IDSS of switches, ZOUT of switches

- I<sub>DSS</sub> $\cong$  1.5 mA, Z<sub>OUT</sub>=40 k $\Omega$

- $\bullet$  V<sub>IN</sub>= 10V, C<sub>h</sub>=1000 pF, T<sub>A</sub>=20  $\mu s$  to 0.1%

- $\bullet$  Error created by charge injection during Hold mode:  $\Delta V_{\mbox{\footnotesize E}}\!\cong\!10$  pF (14.5V V  $_{\mbox{\footnotesize IN}}\mbox{)}/C_{\mbox{\footnotesize h}}$

FIGURE 8. Inexpensive Sample and Hold

TL/H/5668-16

FIGURE 9a. A Fast 16-Channel DAU with Second Level Multiplexing

FIGURE 9b. Timing Diagram

8-49

# Typical Applications (Continued)

FIGURE 10. A 16-Channel Multiplexer with Sequential Multiplexing

**■** 6501124 0094176 922 **■**