## Recent Additions CD54AC299/3A CD54ACT299/3A

# 8-Input Universal Shift/Storage Register with Common Parallel I/O pins

Asynchronous Reset

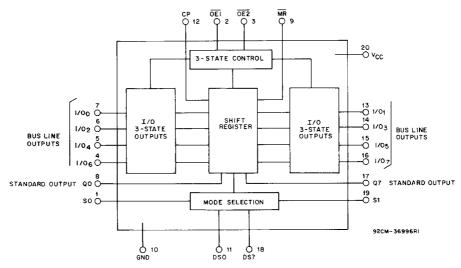

The RCA CD54AC299 and CD54ACT299 are 3-state, 8-input universal shift/storage registers with common parallel I/O pins. These devices utilize the new RCA ADVANCED CMOS LOGIC technology. These registers have four synchronous-operating modes controlled by the two select inputs as shown in the Mode Select (S0, S1) table. The Mode Select, the Serial Data (DS0, DS7), and the Parallel Data (I/O $_0$  - I/O $_7$ ) respond only to the LOW-TO-HIGH transition of the clock pulse (CP). S0, S1 and Data inputs must be present one setup time prior to the positive transition of the clock.

The Master Reset (MR) is an asynchronous active-LOW input. When MR is LOW, the register is cleared regardless of the status of all other inputs. The register can be expanded by cascading same units by tying the serial output (QO) to the serial data (DS7) input of the preceding register, and tying the serial output (Q7) to the serial data (DS0) input of the following register. Recirculating the (n x 8) bits is accomplished by tying the Q7 of the last stage to the

DS0 of the first stage.

The 3-state input/output (I/O) port has three modes of operation:

- Both Output Enable (OE1 and OE2) inputs are LOW and S0 or S1 or both are LOW, the data in the register is present at the eight outputs.

- When both S0 and S1 are HIGH, I/O terminals are in the high-impedance state but being input ports, ready for parallel data to be loaded into eight registers with one clock transition regardless of the status of OE1 and OE2.

- Either one of the two Output Enable inputs being HIGH will force I/O terminals to be in the off state. It is noted that each I/O terminal is a 3-state output and a CMOS buffer input.

The CD54AC299 and CD54ACT299 are supplied in 20-lead dual-in-line ceramic packages (F suffix).

Fig. 1 - Functional diagram.

## Package Specifications

(See Section 11, Fig. 13)

## Recent Additions CD54AC299/3A CD54ACT299/3A

## Static Electrical Characteristics (Limits with black dots (•) are tested 100%.)

| CHARACTERISTICS                       |                 |                        |                 | AMBIENT TEMPERATURE (TA) - °C |      |             |      | UNITS |

|---------------------------------------|-----------------|------------------------|-----------------|-------------------------------|------|-------------|------|-------|

|                                       | TEST CONDITIONS |                        | V <sub>cc</sub> | +25                           |      | -55 to +125 |      |       |

|                                       | V, (V)          | I <sub>o</sub><br>(mA) | (V)             | MIN.                          | MAX. | MIN.        | MAX. |       |

| Quiescent Supply<br>Current (MSI) Icc | V∞<br>or<br>GND | 0                      | 5.5             | _                             | 8•   | _           | 160• | μΑ    |

The complete static electrical test specification consists of the above by-type static tests combined with the standard static tests in the beginning of this section.

#### **ACT INPUT LOADING TABLE**

| INPUT            | UNIT LOAD* |  |  |

|------------------|------------|--|--|

| S1, S2, OE1, OE2 | 0.83       |  |  |

| SL, CP           | 0.67       |  |  |

| MR               | 1.33       |  |  |

\*Unit load is  $\Delta I_{CC}$  limit specified in Static Characteristics Chart, e.g., 2.4 mA max. @ 25° C.

### **Burn-In Test-Circuit Connections**

Identical to CD54HC/HCT299/3A, page 5-121.

### SWITCHING CHARACTERISTICS: AC Series; t,, t, = 3 ns, C, = 50 pF (Worst Case)

| CHARACTERISTICS                     | SYMBOL                                                                       | V <sub>cc</sub><br>(V) | -55 to         |                      |       |

|-------------------------------------|------------------------------------------------------------------------------|------------------------|----------------|----------------------|-------|

|                                     |                                                                              |                        | MIN.           | MAX.                 | UNITS |

| Propagation Delays:<br>CP to Q0, Q7 | t <sub>PLH</sub><br>t <sub>PHL</sub>                                         | 1.5<br>3.3*<br>5†      | 3.4<br>2.2     | 162<br>18.1<br>12.9• | ns    |

| CP to (I/O)n                        | t <sub>PLH</sub><br>t <sub>PHL</sub>                                         | 1.5<br>3.3<br>5        | <br>3.5<br>2.3 | 169<br>18.9<br>13.5• | ns    |

| MR to Q0, Q7                        | t <sub>PLH</sub><br>t <sub>PHL</sub>                                         | 1.5<br>3.3<br>5        | 2.9<br>1.9     | 140<br>15.7<br>11.2• | ns    |

| MR to (I/O)n                        | t <sub>PLH</sub>                                                             | 1.5<br>3.3<br>5        | <br>3.5<br>2.4 | 174<br>19.5<br>13.9  | ns    |

| Enable and Disable<br>Times         | t <sub>PZL</sub><br>t <sub>PZH</sub><br>t <sub>PLZ</sub><br>t <sub>PHZ</sub> | 1.5<br>3.3<br>5        | 3.8<br>2.6     | 186<br>22.4<br>14.9• | ns    |

| Power Dissipation Capacitance       | C <sub>PD</sub> §                                                            | - 1                    |                |                      | pF    |

| Input Capacitance                   | Cı                                                                           | _                      |                | 10                   | pF    |

| 3-State Output Capacitance          | Co                                                                           | _                      |                | 15                   | pF    |

\*3.3 V: min. is @ 3.6 V max. is @ 3 V

†5 V: min. is @ 5.5 V max. is @ 4.5 V  $\ensuremath{\S{C_{PD}}}$  is used to determine the dynamic power consumption per function.

$P_D = C_{PD} V_{CC}{}^2 \, f_i + \Sigma \; (C_L V_{CC}{}^2 \, f_o)$  where  $\, f_i = \text{input frequency} \,$

$f_0 = \text{output frequency}$

C<sub>L</sub> = output load capacitance

V<sub>cc</sub> = supply voltage

(Limits with black dots (•) are tested 100%.)

## Recent Additions CD54AC299/3A CD54ACT299/3A

#### SWITCHING CHARACTERISTICS: ACT Series; t,, t, = 3 ns, C<sub>L</sub> = 50 pF (Worst Case)

| CHARACTERISTICS                     |                                      | V <sub>cc</sub> (V) | -55 to       |       |       |

|-------------------------------------|--------------------------------------|---------------------|--------------|-------|-------|

|                                     | SYMBOL                               |                     | MIN.         | MAX.  | UNITS |

| Propagation Delays:<br>CP to Q0, Q7 | t <sub>PLH</sub><br>t <sub>PHL</sub> | 5†                  | 2.2          | 12.9• | ns    |

| CP to (I/O)n                        | t <sub>PLH</sub><br>t <sub>PHL</sub> | 5                   | 2.5          | 14.5● | ns    |

| MR to Q0, Q7                        | t <sub>PLH</sub><br>t <sub>PHL</sub> | 5                   | 2.1          | 12.2• | ns    |

| MR to (I/O)n                        | t <sub>PLH</sub><br>t <sub>PHL</sub> | 5                   | 3.2          | 18.6  | ns    |

| Enable Disable<br>Times             | tplz<br>tpHz<br>tpZL<br>tpZH         | 5                   | 2.6          | 14.9• | ns    |

| Power Dissipation Capacitance       | C <sub>PD</sub> §                    | _                   |              |       | pF    |

| Input Capacitance                   | Cı                                   | _                   | <del>-</del> | 10    | pF    |

| 3-State Output Capacitance          | C <sub>o</sub>                       |                     | _            | 15    | pF    |

†5 V: min. is @ 5.5 V max. is @ 4.5 V §C<sub>PD</sub> is used to determine the dynamic power consumption, per function.

For ACT,  $P_D = C_{PD}V_{CC}^2 f_i + \Sigma (C_LV_{CC}^2 f_o) + V_{CC} \Delta I_{CC}$  where  $f_i = \text{input frequency}$

f<sub>o</sub> = output frequency

C<sub>L</sub> = output load capacitance

V<sub>cc</sub> = supply voltage

(Limits with black dots (•) are tested 100%.)

## CD54AC323/3A CD54ACT323/3A

# 8-Input Universal Shift/Storage Register with Common Parallel I/O pins

Synchronous Reset

The RCA CD54AC323 and CD54ACT323 are 3-state, 8-input universal shift/storage registers with common parallel I/O pins. These devices utilize the new RCA ADVANCED CMOS LOGIC technology. These registers have four synchronous-operating modes controlled by the two select inputs as shown in the Mode Select (S0, S1) table. The Mode Select, the Serial Data (DS0, DS7), and the Parallel Data (I/O<sub>0</sub> - I/O<sub>7</sub>) respond only to the LOW-TO-HIGH transition of the clock pulse (CP). S0, S1 and Data inputs must be present one setup time prior to the positive transition of the clock.

The Master Reset  $(\overline{MR})$  clears the register in sync with the clock input. The register can be expanded by cascading same units by tying the serial output (QO) to the serial data (DS7) input of the preceding register, and tying the serial output (Q7) to the serial data (DS0) input of the following register. Recirculating the (n x 8) bits is accomplished by tying the Q7 of the last stage to the DS0 of the first stage.

The 3-state input/output (I/O) port has three modes of operation:

- Both Output Enable (OE1 and OE2) inputs are LOW and S0 or S1 or both are LOW, the data in the register is present at the eight outputs.

- When both S0 and S1 are HIGH, I/O terminals are in the high-impedance state but being input ports, ready for parallel data to be loaded into eight registers with one clock transition regardless of the status of OE1 and OE2.

- Either one of the two Output Enable inputs being HIGH

will force I/O terminals to be in the off state. It is noted

that each I/O terminal is a 3-state output and a CMOS

buffer input.

The CD54AC323 and CD54ACT323 are supplied in 20-lead dual-in-line ceramic packages (F suffix).