# **OctalFALC**<sup>TM</sup>

Octal E1/T1/J1 Framer and Line Interface Component for Long- and Short-Haul Applications

PEF 22558 E, Version 1.1

Wireline Communications

ABM®, ACE®, AOP®, ARCOFI®, ASM®, ASP®, DigiTape®, DuSLIC®, EPIC®, ELIC®, FALC®, GEMINAX®, IDEC®, INCA®, IOM®, IPAT®-2, ISAC®, ITAC®, IWE®, IWORX®, MUSAC®, MuSLIC®, OCTAT®, OptiPort®, POTSWIRE®, QUAT®, QuadFALC®, SCOUT®, SICAT®, SICOFI®, SIDEC®, SLICOFI®, SMINT®, SOCRATES®, VINETIC®, 10BaseV®, 10BaseVX® are registered trademarks of Infineon Technologies AG. 10BaseS™, EasyPort™, VDSLite™ are trademarks of Infineon Technologies AG. Microsoft® is a registered trademark of Microsoft Corporation, Linux® of Linus Torvalds, Visio® of Visio Corporation, and FrameMaker® of Adobe Systems Incorporated.

The information in this document is subject to change without notice.

#### Edition 2005-05-03

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany

© Infineon Technologies AG 2005.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# OctalFALC<sup>TM</sup>

**Revision History:** 2005-05-03 Rev. 2.0

Previous Version: Rev. 1.0

| Page | age Subjects (major changes since last revision) |  |  |  |

|------|--------------------------------------------------|--|--|--|

| 46   | Transmit Line Monitor                            |  |  |  |

|      |                                                  |  |  |  |

| Table o                                                   | f Contents                                                                                                                                                                                      | Page           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1                                                         | General                                                                                                                                                                                         | 8              |

| <b>2</b><br>2.1<br>2.2                                    | Compatibility                                                                                                                                                                                   | 8              |

| 3                                                         | Microcontroller Interface                                                                                                                                                                       | 12             |

| <b>4</b><br>4.1<br>4.2                                    | Serial Interfaces  SCI Interface  SPI Interface                                                                                                                                                 | 18             |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | Clock Modes Individual Receive Clock Selection Transmit Clock Switching TCLK Frequency RCLK Frequency DCO-R/DCO-X Characteristics PLL Reset and Configuring PLL Interrupt Status Bits           | 27 28 28 28 28 |

| 6<br>6.1<br>6.2<br>6.3<br>6.4                             | Framer Features                                                                                                                                                                                 | 33<br>33       |

| <b>7</b><br>7.1<br>7.2<br>7.3                             | CAS Features  Basic CAS Operation Mode  Bit Robbing Force One in Cleared Channels (T1/J1 only)  Bit Robbing Idle (T1/J1 only)                                                                   | 36             |

| 8                                                         | HDLC/BOM Controllers                                                                                                                                                                            | 37             |

| 9<br>9.1<br>9.2<br>9.3<br>9.4                             | System Interface System Multiplex Mode Clock Edge Selection Tristate Modes Redundancy Mode                                                                                                      | 39<br>41<br>41 |

| 10<br>10.1<br>10.2<br>10.3<br>10.3.1<br>10.3.2            | Line Interface Tunable Transmit Line Output Resistance Transmit Line Monitor Programmable Pulse Shaper and Line Build-Out QuadFALC® Compatible Programming Programming with TXP(16:1) Registers | 45<br>46<br>46 |

| Table of                                     | f Contents                                                                                                                                                                                                        | Page                         |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 10.4                                         | Receive Line Termination                                                                                                                                                                                          | . 49                         |

| 11                                           | Multi Function Port Features                                                                                                                                                                                      | . 51                         |

| 12<br>12.1<br>12.2<br>12.3<br>12.4<br>12.4.1 | Test and Maintenance  PRBS Test Signal  PPR Enhancement (T1/J1 only)  In-Band Loop Switching  Out-Band Loop Switching (T1/J1 only)  Bit Oriented Messages (BOM): Generation, Detection and Loop Switch (T1/J1) 58 | . 53<br>. 55<br>. 55<br>. 57 |

| 12.5<br>12.6<br>12.7                         | FEC Count Up Behaviour                                                                                                                                                                                            | . 60                         |

| 13                                           | Supported Standards                                                                                                                                                                                               | . 61                         |

| <b>14</b><br>14.1<br>14.2                    | Development Support                                                                                                                                                                                               | . 61                         |

| <b>15</b><br>15.1<br>15.2<br>15.3            | Register Functions Global Register Compatibility Handling Pseudo QuadFALC® Register GPC1 Additional Registers or Register Bits                                                                                    | . 61<br>. 63                 |

| 16                                           | External Signals                                                                                                                                                                                                  | . 72                         |

| 17                                           | Package                                                                                                                                                                                                           | . 83                         |

| <b>18</b><br>18.1<br>18.2<br>18.3            | Electrical Characteristics Absolute Maximum Ratings Operating Range DC Characteristics                                                                                                                            | . 85<br>. 86                 |

| List of Figu | ires Pa                                                                                | age |

|--------------|----------------------------------------------------------------------------------------|-----|

| Figure 1     | Logic Symbol                                                                           | . 9 |

| Figure 2     | Basic Operation Modes for Microcontroller interface                                    | 10  |

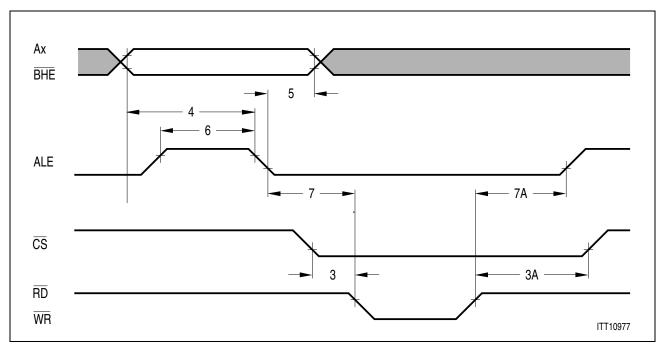

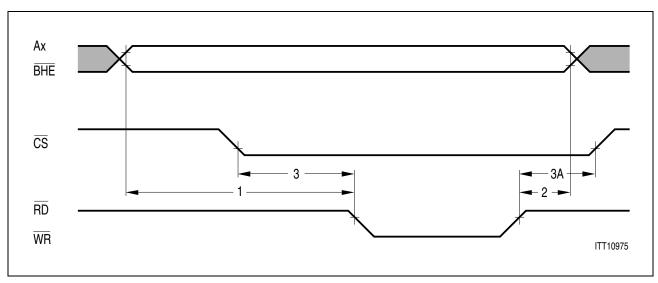

| Figure 3     | Intel Read Cycle Timing                                                                | 12  |

| Figure 4     | Intel Write Cycle Timing                                                               |     |

| Figure 5     | Intel Multiplexed Address Timing                                                       | 13  |

| Figure 6     | Intel Non Multiplexed Address Timing                                                   | 14  |

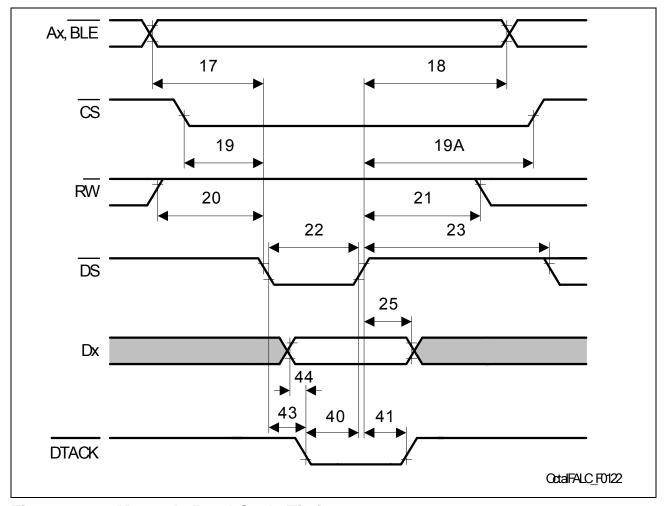

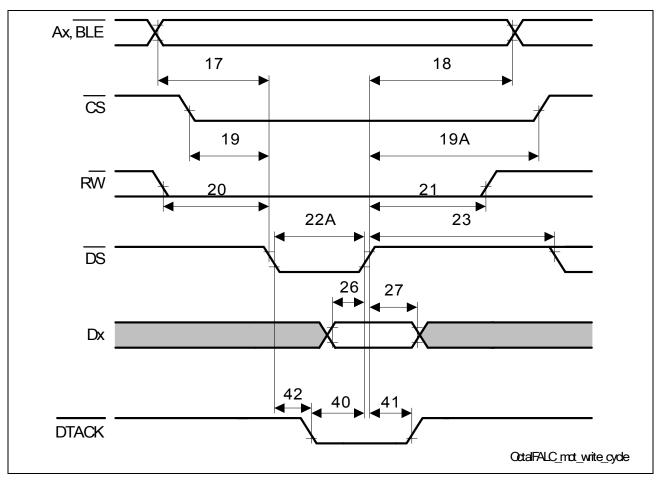

| Figure 7     | Motorola Read Cycle Timing                                                             | 15  |

| Figure 8     | Motorola Write Cycle Timing                                                            |     |

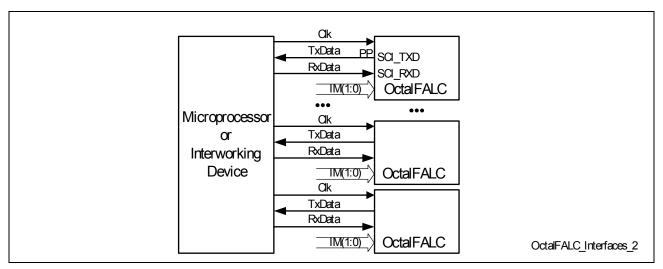

| Figure 9     | SCI interface Application with Point to Point Connections                              | 19  |

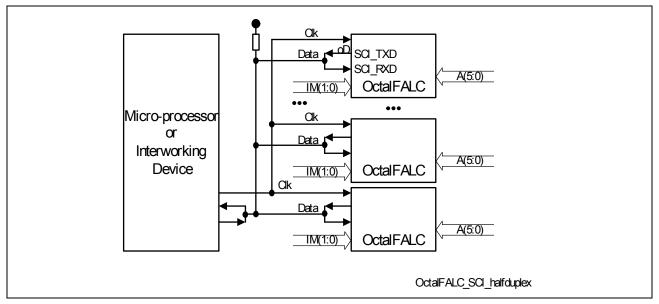

| Figure 10    | SCI interface Application with Multipoint to Multipoint Connection                     |     |

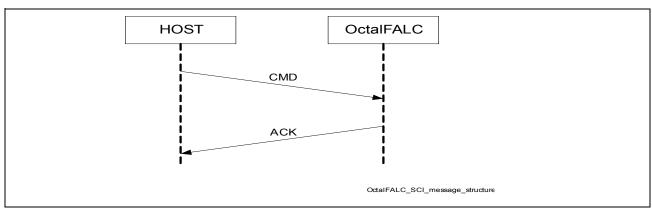

| Figure 11    | SCI Message Structure of OctalFALC <sup>TM</sup>                                       |     |

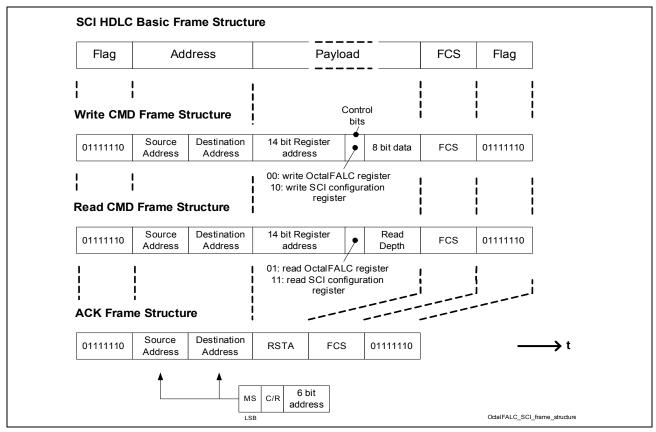

| Figure 12    | Frame Structure of OctalFALC <sup>TM</sup> SCI Messages                                | 21  |

| Figure 13    | Principle of Building of Addresses and RSTA Bytes in the SCI ACK                       |     |

|              | Message 22                                                                             |     |

| Figure 14    | SCI Interface Timing                                                                   |     |

| Figure 15    | SPI Read Operation                                                                     |     |

| Figure 16    | SPI Write Operation                                                                    |     |

| Figure 17    | SPI Interface Timing                                                                   |     |

| Figure 18    | Receive Clock Selection                                                                |     |

| Figure 19    | Principle of Setting Parameters of the DCO-X and DCO-R                                 |     |

| Figure 20    | Flexible Master Clock Unit                                                             |     |

| Figure 21    | AXRA Requirements                                                                      |     |

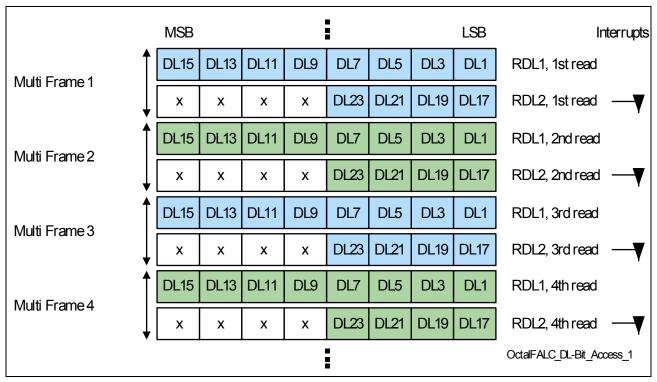

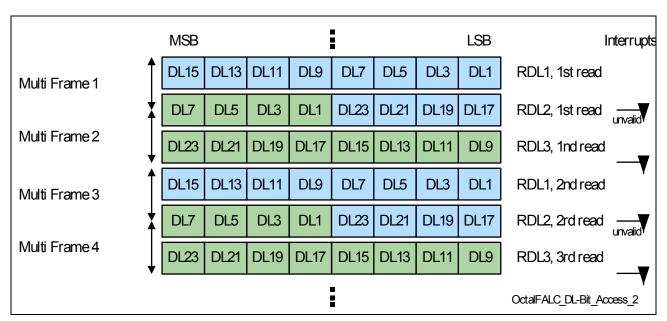

| Figure 22    | Standard DL-Bit Access in ESF Mode                                                     |     |

| Figure 23    | Optional DL-Bit Access in ESF Mode                                                     |     |

| Figure 24    | HDLC Controller Standard Configuration for all three HDLC Channels                     |     |

| Figure 25    | HDLC Controller Inverse Configuration for All Three HDLC Channels                      |     |

| Figure 26    | Principle of System Interface Multiplex Modes, shown for RDO                           |     |

| Figure 27    | Redundancy Application (shown for one channel and using RLM)                           |     |

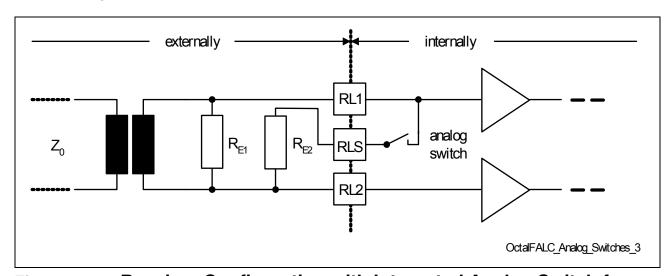

| Figure 28    | Long Haul Redundancy Application using the Analog Switch (shown formula) 44            | or  |

| Figure 29    | Transmit Impedances                                                                    | 45  |

| Figure 30    | Receiver Configuration with Integrated Analog Switch for Receive Impedance Matching 49 |     |

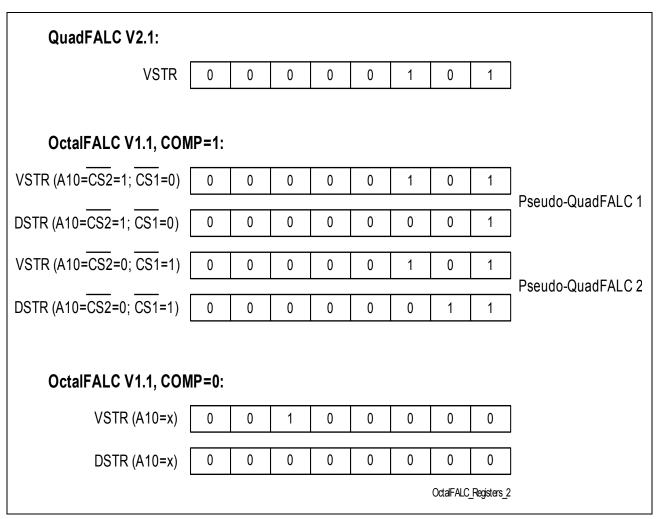

| Figure 31    | GIS Register Compatibility                                                             | 62  |

| Figure 32    | VSTR and DSTR Register Compatibility                                                   | 63  |

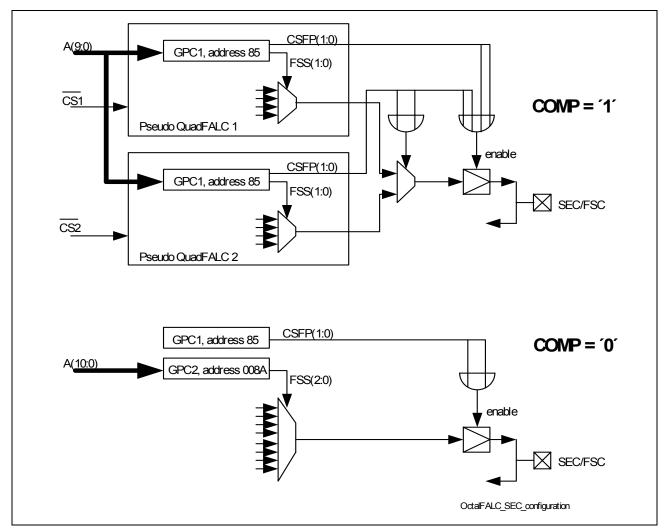

| Figure 33    | Principle of configuration of SEC/FSC Output                                           | 64  |

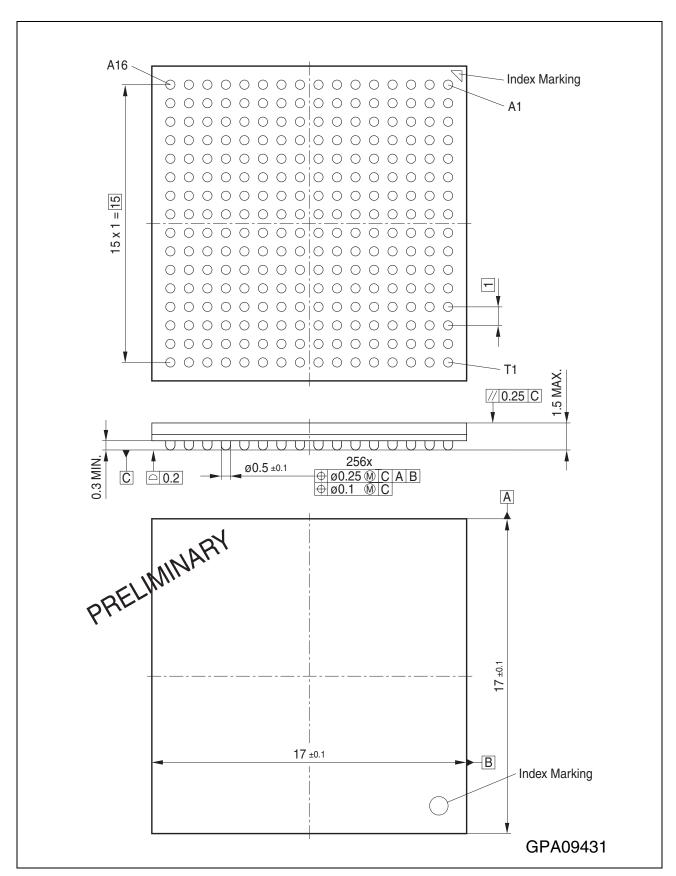

| Figure 34    | PG-LBGA-256-1 (Plastic Green Low Profile Ball Grid Array Package)                      | 84  |

|              |                                                                                        |     |

| List of Table                 | es Pag                                                                                              | ge |

|-------------------------------|-----------------------------------------------------------------------------------------------------|----|

| Table 1<br>Table 2<br>Table 3 | Overview Interface- and Basic Operation-Modes Intel Bus Interface Timing Parameter Values           | 14 |

| Table 4                       | Definition of Control Bits in Commands (CMD)                                                        |    |

| Table 5                       | SCI Configuration Register Content                                                                  |    |

| Table 6                       | SCI Timing Parameter Values                                                                         |    |

| Table 7                       | SPI Interface Timing Parameter Values                                                               |    |

| Table 8                       | Conditions for a PLL Reset                                                                          |    |

| Table 9                       | Receive FIFO User Depth (HDLC channel 1) and Bit Positions in Registe RBCL 38                       |    |

| Table 10                      | System Multiplex Modes                                                                              | 40 |

| Table 11                      | Tristate Configurations for the RDO, RSIG, SCLKR and RFM Pins 4                                     | 41 |

| Table 12                      | Redundancy Application Using RLM Mode                                                               | 42 |

| Table 13                      | Redundancy Application Using the Analog Switch, Switching with only one Board Signal 44             |    |

| Table 14                      | Serial Impedance Values                                                                             | 45 |

| Table 15                      | Recommended Pulse Shaper Programming for T1/J1 with registers XPM(2:0) (Compatible to QuadFALC®) 47 |    |

| Table 16                      | Recommended Pulse Shaper Programming for E1 with Registers XPM(2:0) (Compatible to QuadFALC®) 47    |    |

| Table 17                      | Recommended Pulse Shaper Programming for T1 with Registers TXP(16:1) 48                             |    |

| Table 18                      | Recommended Pulse Shaper Programming for E1 with Registers TXP(16:1) 48                             |    |

| Table 19                      | Receiver Configuration Examples                                                                     | 50 |

| Table 20                      | Multi Function Port Selection                                                                       | 51 |

| Table 21                      | Supported PRBS Polynomials (pattern)                                                                | 54 |

| Table 22                      | Bit/Timeslot Selection of PRBS Pattern                                                              | 55 |

| Table 23                      | Out-Band Loop (BOM) Messages                                                                        | 58 |

| Table 24                      | Out-band Loop Messages for Loop Switching (T1/J1)                                                   | 58 |

| Table 25                      | Overview of Additional Control Register Functions for E1 Mode                                       | 65 |

| Table 26                      | Overview of Additional Status Register Functions for E1 Mode                                        | 67 |

| Table 27                      | Overview of Additional Control Register Functions for T1/J1                                         | 68 |

| Table 28                      | Overview of Additional Status Register Functions for T1/J1s                                         | 70 |

| Table 29                      | I/O Signals                                                                                         | 72 |

| Table 30                      | Pinstrapping Overview                                                                               | 82 |

| Table 31                      | Absolute Maximum Ratings                                                                            | 85 |

| Table 32                      | Operating Range                                                                                     | 86 |

| Table 33                      | DC Characteristics                                                                                  | 87 |

General

#### **Abstract**

This document describes the differences of PEF 22558 E, OctalFALC<sup>TM</sup>, Version v1.1, relative to the QuadFALC<sup>®</sup>, Version 2.1. QuadFALC is a registered brand.

## 1 General

The number of receive and transmit channels has been increased from four to eight. All channels can be configured and used independently.

To enable a seamless transition from QuadFALC<sup>®</sup> designs to OctalFALC<sup>TM</sup> applications, a compatibility mode is provided. This mode allows software written for the QuadFALC<sup>®</sup> to be used with the OctalFALC<sup>TM</sup> without changes.

For new applications, a number of additional features and enhancements are provided.

# 2 Compatibility

# 2.1 Hardware Compatibility

The OctalFALC<sup>TM</sup> always requires two supply voltages, 1.8 V and 3.3 V. The 3.3 V-only mode usable with QuadFALC<sup>®</sup> (V1.3 and V2.1) is *not* supported.

To enable use of PG-LBGA-256-1 package the number of multifunction ports is reduced to three in receive and two in transmit direction per channel. Furthermore RCLK signals are provided on multifunction ports instead of separate pins.

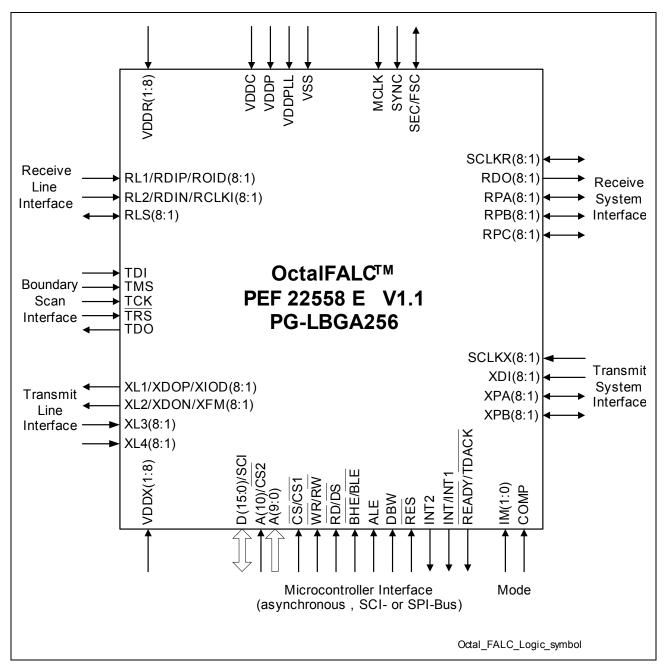

To ensure software compatibility unused registers (for example PC4) still exists but are not used. Figure 1 shows the Logical Symbol of the OctalFALC<sup>TM</sup>.

Compatibility

Figure 1 Logic Symbol

# 2.2 Software Compatibility

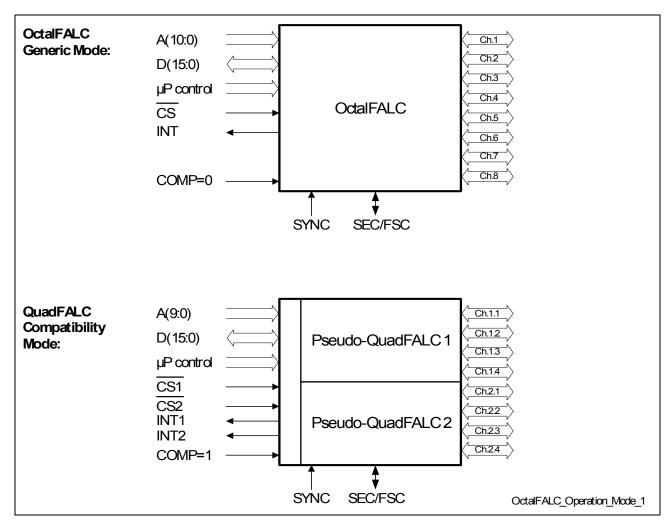

The OctalFALC<sup>TM</sup> can be used in two basic modes. The "QuadFALC<sup>®</sup> Compatibility Mode" allows to use the device like two separate QuadFALC<sup>®</sup>s while the "OctalFALC<sup>TM</sup> Generic Mode" handles the device as a single entity. The "Compatibility Mode" option allows an easy migration of designs from QuadFALC<sup>®</sup> to OctalFALC<sup>TM</sup> without the need for *software* changes. As for the QuadFALC<sup>®</sup> the register addresses are 10 bits wide.

In the "OctalFALC $^{\text{TM}}$  Generic Mode" the register addresses are 11 bit wide.

Compatibility

An overview is given in Table 1.

Additional features are available also in compatibility mode, but are disabled by default and must be activated by software.

If compatibility mode is selected, the version status register VSTR shows the same value as in QuadFALC® V2.1 while the JTAG boundary scan ID is always the OctalFALC<sup>TM</sup> number and not affected by the mode selection. In compatibility mode the behavior of the clocking system is the same as in the QuadFALC®. So the eigenfrequencies and attunation factors of all PLLs, especially of the DCO-R and DCO-X must be in the near of the QuadFALC® values with the equivalent register programing. Also the multi function pin RPC must have the function RCLK after reset (Register bits PC1.RPC(3:0)).

Note: In compatibility mode and if microcontroller mode is selected, A(10) - active high - is used as second chip select signal (CS2) - active low - for the second pseudo QuadFALC®, see Figure 2 and Table 1. The first pseudo QuadFALC® is selected by CS1. Activation of both chip selects simultaneous is not allowed.

Figure 2 Basic Operation Modes for Microcontroller interface

Compatibility

Table 1 Overview Interface- and Basic Operation-Modes

| Interface<br>Mode                          | IM(1:0) | COMP  | CS                                  | A(10)                                | A(9:0)                  | Basic<br>Operation<br>Modes |

|--------------------------------------------|---------|-------|-------------------------------------|--------------------------------------|-------------------------|-----------------------------|

| Intel or<br>Motorola<br>micro<br>processor | 0x      | 1     | CS1, for<br>pseudo<br>QuadFA<br>LC1 | CS2, for<br>pseudo<br>QuadFAL<br>C 2 | 10-bit parallel address | "Compatibility<br>Mode"     |

| mode                                       |         | 0     | CS                                  | 11-bit para                          | llel address            | "Generic                    |

| SPI                                        | 10      | Not   | CS                                  | Not valid; serial Mode"              |                         |                             |

| SCI                                        | 11      | valid |                                     | addresses<br>bit                     | are always 11           |                             |

In compatibility mode every global register exists one times in both of the pseudo QuadFALC®s: CIS, GPC(1:6), IPC, VSTR, GIS, GCM(1:8), GIMR, GIS2, GLC1, INBLDTR, DSTR and PRBSTS(1:4).

In compatibility mode (COMP = ´1´) the registers regarding the central clock PLL, GCM(1:8), exists one times in both of the pseudo QuadFALC®s, but the registers of the pseudo QuadFALC®2 are "dummys": Writing and reading is possible but their values are not taken for any configuration of the PLL and writing on register GCM5 or GCM6 causes NO reset of the PLL. Only the registers GCM(1:8) of the pseudo QuadFALC®1 are taken for configuration of the PLL and writing on register GCM5 or GCM6 causes a reset of the PLL as in QuadFALC® or FALC56v2.1

In compatibility mode (COMP = ´1´) the status registers regarding the central clock PLL, GIS2 and GIMR, exists one times in both of the pseudo QuadFALC®s: The status of the one PLL is "doubled" and can be masked individually in every of the both pseudo QuadFALC®s.

In generic mode (COMP = '0') the registers GIMR, GIS2 and GCM(1:8) exist only one times in the whole device.

If compatibility mode is selected, the version status register VSTR shows the same value as in QuadFALC® V2.1 while the JTAG boundary scan ID is always the OctalFALC<sup>TM</sup> number and not affected by the compatibility mode selection.

# 3 Microcontroller Interface

The microcontroller interface is selected if IM(1:0) is strapped to  $100_B$  (Intel mode) or  $100_B$  (Motorola mode).

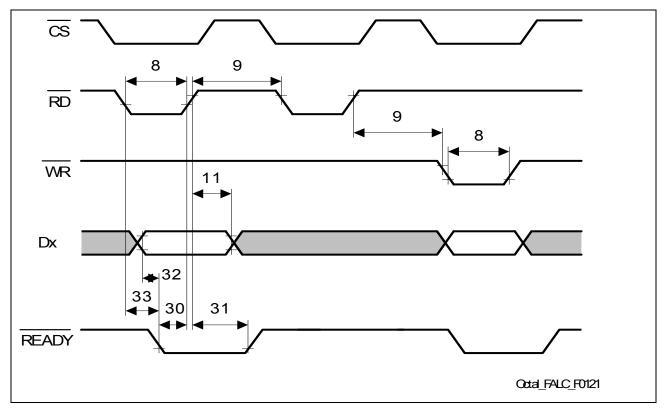

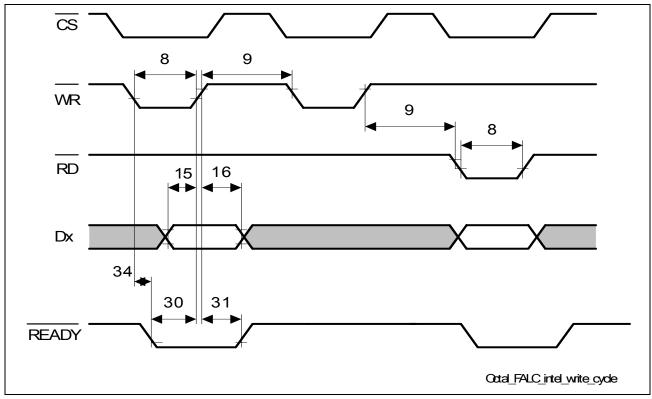

It is based on the existing QuadFALC® interface. An additional handshake signal (data acknowledge  $\overline{\text{DTACK}}$  for Motorola- and  $\overline{\text{READY}}$  for Intel-mode) is provided indicating successful read or write cycle. By using  $\overline{\text{DTACK}}$  or  $\overline{\text{READY}}$  respectively no counter is necessary in the microcontroller to finish the access.

The generation of READY is asynchronous:

In Intel mode read access  $\overline{READY}$  will be set to low by the OctalFALC<sup>TM</sup> after the data output is stable at the OctalFALC<sup>TM</sup>. After the rising edge of  $\overline{RD}$  (which is driven by the micro controller),  $\overline{READY}$  is low for a "hold time", before it will be set to high by the OctalFALC<sup>TM</sup>.

In the Intel mode write acces  $\overline{READY}$  will be set to low by the OctalFALC<sup>TM</sup> after the falling edge of  $\overline{WR}$  (which is driven by the micro controller). After  $\overline{WR}$  is high and data are written successfully into the registers of the OctalFALC<sup>TM</sup>,  $\overline{READY}$  will be set to high by the OctalFALC<sup>TM</sup>.

The general timing diagrams are shown in Figure 3 to Figure 7:

Figure 3 Intel Read Cycle Timing

Delta Sheet 12 Rev. 2.0, 2005-05-03

Figure 4 Intel Write Cycle Timing

Figure 5 Intel Multiplexed Address Timing

Delta Sheet 13 Rev. 2.0, 2005-05-03

Figure 6 Intel Non Multiplexed Address Timing

Table 2

Intel Bus Interface Timing Parameter Values

| No. | Parameter                               | Lir  | Limit Values |    |  |

|-----|-----------------------------------------|------|--------------|----|--|

|     |                                         | Min. | Max.         |    |  |

| 1   | Address, BHE setup time                 | 5    |              | ns |  |

| 2   | Address, BHE hold time                  | 0    |              | ns |  |

| 3   | CS setup time                           | 0    |              | ns |  |

| ЗА  | CS hold time                            | 0    |              | ns |  |

| 4   | Address, BHE stable before ALE inactive | 20   |              | ns |  |

| 5   | Address, BHE hold after ALE inactive    | 10   |              | ns |  |

| 6   | ALE pulse width                         | 30   |              | ns |  |

| 7   | ALE setup time before RD or WR          | 0    |              | ns |  |

| 7A  | ALE hold time after RD or WR            | 30   |              | ns |  |

| 8   | RD, WR pulse width                      | 80   |              | ns |  |

| 9   | RD, WR control interval                 | 70   |              | ns |  |

| 11  | Data hold after RD inactive             | 10   | 30           | ns |  |

| 15  | Data stable before WR inactive          | 30   |              | ns |  |

| 16  | Data hold after WR inactive             | 10   |              | ns |  |

Delta Sheet 14 Rev. 2.0, 2005-05-03

Table 2 Intel Bus Interface Timing Parameter Values (cont'd)

| No. | Parameter                      | Lir  | Unit   |    |  |

|-----|--------------------------------|------|--------|----|--|

|     |                                | Min. | Max.   |    |  |

| 30  | WR or RD delay after READY     |      | t.b.d. | ns |  |

| 31  | READY hold time after RD or WR |      | r      |    |  |

| 32  | Data stable before READY       |      | 1      |    |  |

| 33  | RD to READY delay              |      | 1      |    |  |

| 34  | WR to READY delay              |      |        | ns |  |

Figure 7 Motorola Read Cycle Timing

Delta Sheet 15 Rev. 2.0, 2005-05-03

Figure 8 Motorola Write Cycle Timing

Table 3

Motorola Bus Interface Timing Parameter Values

| No. | Parameter                                | Lir  | Limit Values |    |  |

|-----|------------------------------------------|------|--------------|----|--|

|     |                                          | Min. | Max.         |    |  |

| 17  | Address, BLE setup time before DS active | 15   |              | ns |  |

| 18  | Address, BLE hold after DS inactive      | 0    |              | ns |  |

| 19  | CS active before DS active               | 0    |              | ns |  |

| 19A | CS hold after DS inactive                | 0    |              | ns |  |

| 20  | RW stable before DS active               | 10   |              | ns |  |

| 21  | RW hold after DS inactive                | 0    |              | ns |  |

| 22  | DS pulse width (read access)             | 80   |              | ns |  |

| 22A | DS pulse width (write access)            | 70   |              | ns |  |

| 23  | DS control interval                      | 70   |              | ns |  |

| 24  | Data valid after DS active (read access) |      | 75           | ns |  |

Delta Sheet 16 Rev. 2.0, 2005-05-03

Table 3 Motorola Bus Interface Timing Parameter Values (cont'd)

| No. | Parameter                                   | Lir       | Unit |    |

|-----|---------------------------------------------|-----------|------|----|

|     |                                             | Min.      | Max. |    |

| 25  | Data hold after DS inactive (read access)   |           | 30   | ns |

| 26  | Data stable before DS active (write access) | 30        | ns   |    |

| 27  | Data hold after DS inactive (write access)  | 10        |      |    |

| 40  | DS delay after DTACK                        | t.b.d. ns |      |    |

| 41  | DTACK hold time after DS inactive           | ns        |      |    |

| 42  | DS to DTACK delay for write                 | ns        |      |    |

| 43  | DS to DTACK delay for read                  | ns        |      |    |

| 44  | data stable before DTACK                    |           |      | ns |

## 4 Serial Interfaces

Two additional serial interfaces are included to enable device programming and controlling:

- Slave Serial Control Interface (SCI)

- Slave Serial Peripheral Interface (SPI)

By using the SCI Interface, the OctalFALC<sup>TM</sup> can be easily connected to Infineon interworking devices like the SDC16. The SCI is used as interface also in the Infineon SHDSL- and ADSL-PHYs so that implementation of different line transmission technologies on the same line card easily is possible. The SCI interface is a three-wire bus and optionally replaces the parallel processor interface to reduce wiring overhead on the PCB, especially if multiple devices are used on a single board. Data on the bus is HDLC encapsulated and uses a message-based communication protocol. The OctalFALC<sup>TM</sup> SCI interface is always a slave.

If SCI interface with multipoint to multipoint configuration is used, address pins A(5:0) are used for SCI source (slave) address pin strapping.

In compatibility mode (pin COMP = 1) these both new interfaces are also supported.

The four possible interface modes - two microconroller modes and two serial interface modes - are selected by using the interface mode selection pins IM(1:0). This selection is valid immediately after reset becomes inactive.

After changing of the interface mode by IM(1:0), a hardware reset must be applied.

Note that after a reset writing into or reading from OctalFALC<sup>TM</sup> registers using the SCI-or SPI-Interface is not possible until the PLL is locked: If the SCI-Interface is used no acknowledge message will be send by the OctalFALC<sup>TM</sup>. If the SPI-Interface is used pin SDO has high impedance (SDO is pulled up by external resistor). To trace if the SPI

interface is accessible, the micro controller should poll for example the register DSTR so long as it read no longer the value  $F_H$ .

#### 4.1 SCI Interface

The Serial Control Interface (SCI) is selected if IM(1:0) is strapped to '11<sub>H</sub>'.

The SCI interface of the OctalFALC<sup>TM</sup> is always a slave.

Figure 9 shows a first application using the SCI interfaces of some OctalFALC<sup>™</sup>s were point to point full duplex connections are realized between every OctalFALC<sup>™</sup> and the microcontroller. Here the data out pins of the SCI interfaces (SCI\_TXD) of the OctalFALC<sup>™</sup>s must be configured as push-pull (PP), see configuration registerbit PP in Table 5.

Figure 10 shows an application with Multipoint to multipoint connections between the OctalFALC<sup>TM</sup>s and the microcontroller (half duplex). Here the data out pin of the SCI interfaces (SCI\_TXD) of all OctalFALC<sup>TM</sup>s must be configured as an open Drain (oD), see configuration registerbit PP in Table 5. Data out and data in pin (SCI\_RXD) of every OctalFALC<sup>TM</sup> are connected together and build the common data line. Together with a common pull up resistor for the data line, all open Drain data out pins are building a wired And.

The IFX propritary Daisy-Chain approach is not supported.

The group address of the SCI interface after reset is  $'00_{H}'$ . (Recommendation: set group address to  $'C4_{H}'$  by a configuration message, than it is disjunct to that of other infineon devices.)

In case of multipoint to multipoint applications the 6 MSBs of the SCI source address will be defined by pinstrapping of the address pins A5 to A0. The two LSBs of the SCI source address are constant  $'10_B'$ , see **Table 5**. The SCI source address can be overwritten by a write command into the SCI configuration register. For applications with point to point connections for the SCI interface the source address is not valid.

Because 14 bits are used for the register addresses in the SCI interface macro the two MSBs of the 16 bit wide register addresses are set fixed to zero. (Because the MSBs for global addresses are  $`00_H"$  and the MSBs for local addresses exceeds not the 14-bit range, there is no problem.)

Figure 9 SCI interface Application with Point to Point Connections

Figure 10 SCI interface Application with Multipoint to Multipoint Connection

The following configurations of the SCI interface of the OctalFALC<sup>TM</sup> can be set by the microcontroller by a write command into the SCI configuration register (control bits  $'10_B'$ , see **Table 4**, SCI register address is  $'0000_H'$ , see **Table 5** and **Figure 12**):

- Half duplex/full duplex (reset value: Half duplex), bit DUP

- OpenDrain/push-pull (configuration of output pin to openDrain/push-pull is in general independent of the duplex mode and must be set appropriately in application) (reset value: open Drain), bit PP

- CRC for transmit and receive on/off (reset value: off), bit CRC\_EN

- Automatic acknowledgement of CMD messages on/off (reset value: off), bit ACK EN

- Clock edge rising/falling (reset value: falling), bit CLK\_POL

- Clockgating (reset value: off), bit CLK\_GAT

The following SCI configurations are fixed and cannot be set by the microcontroller:

- Interrupt feature is disabled, bit INT\_EN = '0<sub>B</sub>'

- Arbitration always made with LAPD (only SCI applications like in **Figure 9** and **Figure 10** are possible), bit ARB =  $^{\prime}O_{R}^{\prime}$

Recommendation for configuring: Set CRC, automatic acknowledgement and clock gating to 'on'.

The maximum possible SCI clock frequency is 6 MHz for point to point applications (full duplex) and about 2 MHz for multipoint to multipoint applications, dependent on the electrical capacity of the bus lines of the PCB.

Figure 11 shows the message structure of the OctalFALC<sup>TM</sup>.

Figure 11 SCI Message Structure of OctalFALC<sup>TM</sup>

Every write into or read from a register of the OctalFALC<sup>TM</sup> is initiated by a command message CMD from the Host (microconroller) and is then confirmed by an acknowledge message ACK from the OctalFALC<sup>TM</sup> if in the SCI configuration automatic acknowledgement is set (bit ACK\_EN, see **Table 5**).

The frame structure of this messages are shown in Figure 12.

In general the LSB of every byte is transmitted first and lower bytes are transmitted before higher bytes (regarding the register address).

The HDLC flags mark beginning and end of all messages.

Source and destination addresses are 8 bits long. Only the first 6 bits are really used for addressing. The bit C/R (Command/Response) distinguishes between a command and a response. The bit MS (Master/Slave) is  ${}^{\circ}O_B{}^{\circ}$  for all Slaves and  ${}^{\circ}O_B{}^{\circ}$  for all masters, see **Table 5** and **Figure 12**.

The source address is defined by pinstrapping of A5 to A0 after reset, but other values can be configured by programming of the SCI configuration register.

The payload of the write CMD includes two control bits (MSBs of the payload), which distinguish between the different kind of commands, see **Table 4**, the 14 bit wide register address and the 8 bit wide data whereas the read CMD payload includes only the control bits and the register address. Register addresses can be either OctalFALC<sup>TM</sup> register

addresses or SCI configuration register addresses. Because of the address space of the OctalFALC<sup>TM</sup>, really 11 LSBs of the 14 bit address are used in the OctalFALC<sup>TM</sup>. The 3 MSBs are ignored.

The Frame Check Sequence FCS has16 bits.

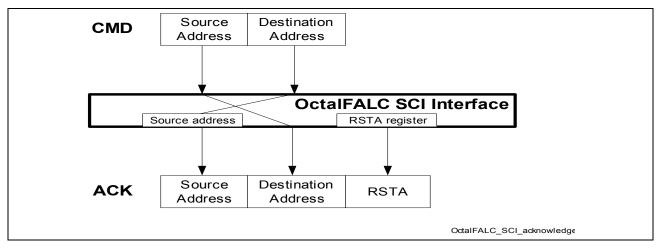

The Read Status Byte RSTA of the acknowledge message shows the status of the received message and is built by the SCI interface of the OctalFALC<sup>TM</sup>, see Figure 13 and Read Status Byte (RSTA) of the Acknowledge (ACK).

The destination address in the ACK message is always the source address of the corresponding CMD (the address of the microcontroller), see **Figure 13**, because no CMD messages will be sent by the OctalFALC<sup>TM</sup> SCI interface.

Figure 12 Frame Structure of OctalFALC<sup>™</sup> SCI Messages

Figure 13 Principle of Building of Addresses and RSTA Bytes in the SCI ACK Message

# Read Status Byte (RSTA) of the Acknowledge (ACK)

| 7 (MSB) | 6   | 5   | 4   | 3   | 2    | 1   | 0 (LSB) |

|---------|-----|-----|-----|-----|------|-----|---------|

| VFR     | RDO | CRC | RAB | SA( | 1:0) | C/R | TA      |

| Field | Bits | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VFR   | 7    | Valid Frame Indicates whether a valid frame has been received.  0 <sub>B</sub> VFR_0, received frame is invalid.  1 <sub>B</sub> VFR_1, received frame is valid.                                                                                                                                                                                                                               |

| RDO   | 6    | Reserved                                                                                                                                                                                                                                                                                                                                                                                       |

| CRC   | 5    | CRC Compare/Check Indicates wether a CRC check is failed or not  0 <sub>B</sub> CRC_0, CRC error check failed on the received frame.  1 <sub>B</sub> CRC_1, received frame is free of CRC errors.                                                                                                                                                                                              |

| RAB   | 4    | Receive Message Aborted  CMD Message abortion is declared. The receive message was aborted by the Host. A sequence of seven consecutive '1' was detected before closing the flag.  O <sub>B</sub> RAB_0, data reception is in progress.  1 <sub>B</sub> RAB_1, data reception has been aborted.  Note: ACK message and therefore RAB will be send not before destination address was received. |

| Field               | Bits  | Description |

|---------------------|-------|-------------|

| SA(1:0),<br>C/R, TA | [3:0] | Reserved    |

Table 4 Definition of Control Bits in Commands (CMD)

| Control Bits (MSB LSB) | Command Type                          |  |

|------------------------|---------------------------------------|--|

| 01                     | Read OctalFALC <sup>™</sup> register  |  |

| 00                     | Write OctalFALC <sup>™</sup> register |  |

| 10                     | Write SCI configuration register      |  |

| 11                     | Read SCI configuration register       |  |

Table 5

SCI Configuration Register Content

| Address              | bit 7<br>(MSB) | bit 6   | bit 5   | bit 4  | bit 3  | bit 2      | bit 1    | bit 0<br>(LSB) |

|----------------------|----------------|---------|---------|--------|--------|------------|----------|----------------|

| ′0000 <sub>H</sub> ′ | PP             | CLK_POL | CLK_GAT | ACK_EN | INT_EN | CRC_E<br>N | ARB      | DUP            |

| ′0001 <sub>H</sub> ′ | Source Address |         |         |        |        | 1 (= C/R)  | 0 (= MS) |                |

| ′0002 <sub>H</sub> ′ | Group Address  |         |         |        |        | 1 (= C/R)  | 0 (= MS) |                |

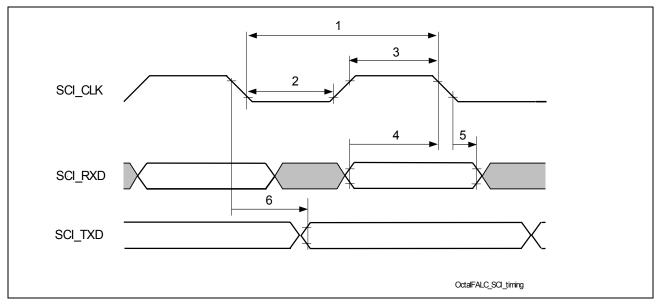

Figure 14 shows the timing of the SCI interface and Table 6 the appropriate timing parameter values.

Figure 14 SCI Interface Timing

Table 6 SCI Timing Parameter Values

| No | Parameter                           | Lin    | Unit   |    |

|----|-------------------------------------|--------|--------|----|

|    |                                     | Min.   | Max.   |    |

| 1  | SCI_CLK cycle time full duplex mode | 170    |        | ns |

| 1  | SCI_CLK cycle time half duplex mode | 500    |        | ns |

| 2  | SCI_CLK low time                    | t.b.d. |        | ns |

| 3  | SCI_CLK high time                   | t.b.d. |        | ns |

| 4  | SCI_RXD setup time before SCI_CLK   | t.b.d. |        | ns |

| 5  | SCI_RXD hold time after SCI_CLK     | 0      |        | ns |

| 6  | SCI_TXD delay time after SCI_CLK    |        | t.b.d. | ns |

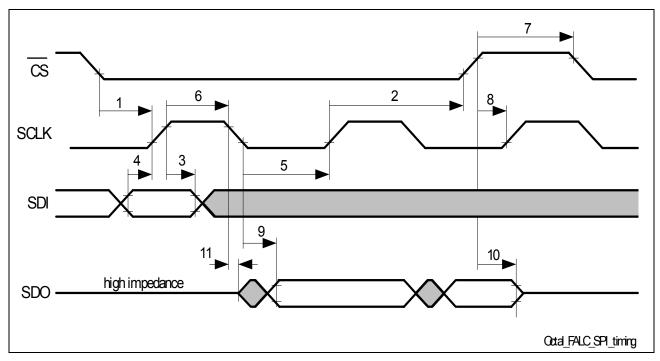

#### 4.2 SPI Interface

The Serial Peripheral Interface (SPI) is selected if IM(1:0) is strapped to  $'10_H'$ .

The SPI interface of the OctalFALC<sup>TM</sup> is always a slave.

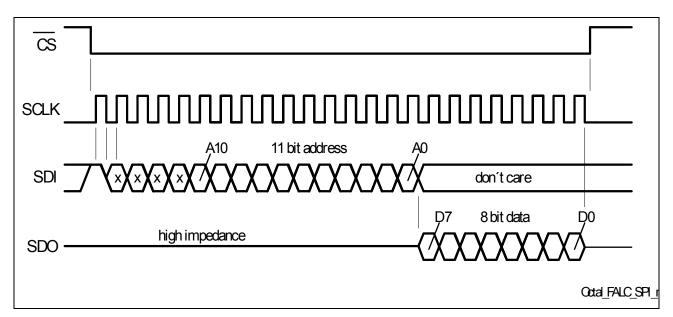

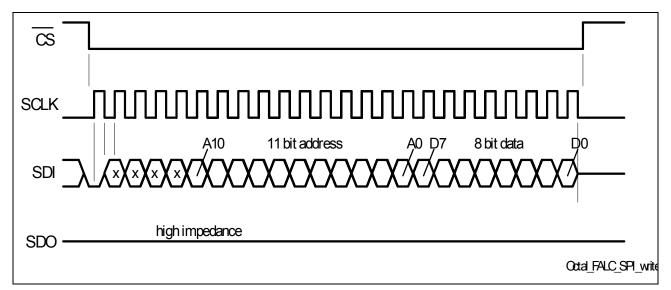

Figure 15 and Figure 16 show the read and the write operation respectively. The start of a read or write operation is marked by the falling edge of the chip select signal  $\overline{CS}$  whereas the end of the operations is marked by the rising edge of  $\overline{CS}$ . Because of  $\overline{CS}$  the SPI interface has no slave address.

The first bit of the serial data in (SDI) is  ${}^{'}1_{B}{}^{'}$  for a read operation and  ${}^{'}0_{B}{}^{'}$  for a write operation. The first four bits of the 15 bit address are not valid for the OctalFALC<sup>TM</sup>.

In read operation the OctalFALC<sup>TM</sup> delivers the 8 bit wide content of the addressed register at the serial data out (SDO).

In general SPI data are driven with the negative edge of the serial clock (SCLK) and sampled with the positive edge of SCLK. **Figure 17** shows the timing of the SPI interface and **Table** the appropriate timing parameter values.

Figure 15 SPI Read Operation

Figure 16 SPI Write Operation

Figure 17 SPI Interface Timing

Table 7 SPI Interface Timing Parameter Values

| No. | Parameter                            | Lir  | Unit   |     |

|-----|--------------------------------------|------|--------|-----|

|     |                                      | Min. | Max.   |     |

| -   | SCLK frequency                       |      | t.b.d. | MHz |

| 1   | CS setup time before SCLK            | 50   |        | ns  |

| 2   | CS hold time after SCLK              | 100  |        | ns  |

| 3   | SDI hold time after SCLK             | 150  |        | ns  |

| 4   | SDI setup time before SCLK           | 50   |        | ns  |

| 5   | SCLK low time                        | 205  |        | ns  |

| 6   | SCLK high time                       | 205  |        | ns  |

| 7   | CS high time                         | 100  |        | ns  |

| 8   | Clock disable time before SCLK       | 50   |        | ns  |

| 9   | SDO output stable after SCLK         |      | 150    | ns  |

| 10  | SDO output hold after CS disable     |      | 50     | ns  |

| 11  | SDO output High Impedance after SCLK | 0    |        |     |

# 5 Clock Modes

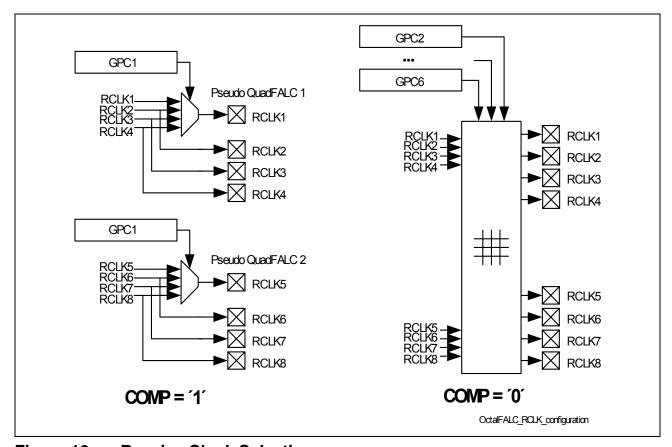

#### 5.1 Individual Receive Clock Selection

The source of every of the eight receive clocks (RCLK(8:1)) can be independently selected out of every of the eight channels. The additional registers GPC2 to GPC6 are used for controlling. GPC2 to GPC6 are not valid if COMP = ´1´. For COMP = ´1´ only the source of RCLK1 can be selected by the register GPC1 of the pseudo QuadFALC®1, RCLK2,3,4 sources are the appropriate channels. Equivalent, the RCLK5 source can be selected by the register GPC1 of the pseudo QuadFALC®2 and the sources of RCLK6,7,8 are the appropriate channels. For the principle see also **Figure 18**. After reset RCLK1 is sourced by channel 1 and RCLK5 is sourced by channel 5 and switched to the multi function ports RPC.

Note that in CT mode the DCO-R is always on.

Figure 18 Receive Clock Selection

# 5.2 Transmit Clock Switching

The transmit clock can be automatically switched between TCLK and SCLKX. This enables an automatic switch over between different clock sources within the system in case the original clock source is lost. In general the clock switching is glitch free.

TCLK loss is detected if the transmit clock derived from TCLK failed to occur.

Automatic transmit clock switching is controlled by the register bit CMR4.ATCS.

If the TCLK input is used directly as transmit clock XCLK, the output of the DCO-X (CU-ADPLL-X) is not used. The DCO-X reference clock is SCLKX. If loss of TCLK is detected, the transmit clock will be switched automatically to the DCO-X output which is synchronous to SCLKX if CMR4.ATCS = ´1´. This switching is shown in the interrupt status bit ISR7.XCLKSSO which is masked by IMR7.XCLKSSO. This switching cannot be done in general without occuring of phase jumps or spikes in the transmit clock XCLK. Additionally after loss of TCLK the transmit clock XCLK is also lossed during the "detection time" for loss of TCLK,

If the transmit clock XCLK is sourced by the DCO-X output and the DCO-X reference clock is TCLK, the DCO-X reference will be switched to SCLK after a loss of TCLK was detected if CMR4.ATCS = '1'. This switching is shown in the interrupt status bit ISR7.XCLKSS1 which is masked by IMR7.XCLKSS1.

In that case, the transmit clock XCLK fullfils the jitter-, wander- and frequency deviation-requiements as specified for E1/T1 after the clock source of the DCO-X was changed. Slipping of the (active) transmit buffer should be avoided.

Comment: TCLK is sourced by RCLK in normal application, so loss of TCLK happens because of loss of RCLK.

# 5.3 TCLK Frequency

TCLK supports 1.544, 3.088, 6.176, 12.352 and 24.704 MHz in T1/J1 mode and 2.048, 4.096, 8.192, 16.384 and 32.768 MHz in E1 mode and in T1/J1 channel translation mode. If COMP = '0'controlling is done by the register CMR5, bits STF(2:0), if COMP = '1' controlling is done by the register CMR1, bit STF.

# 5.4 RCLK Frequency

RCLK supports 1.544, 3.088, 6.176, and 12.352 in T1/J1 mode and 2.048, 4.096, 8.192, and 16.384 MHz in E1 mode and in T1/J1 channel translation mode. If COMP = '0'controlling is done by the register CMR4, bits RS(1:0), if COMP = '1' controlling is done by the register CMR1, bits RS(1:0). If the recovered clock out (of the clock data recovery) is the source of RCLK then only 2.048 MHz (1.544,) is possible. If the DCO-R is the source of RCLK all above described frequencies are possible.

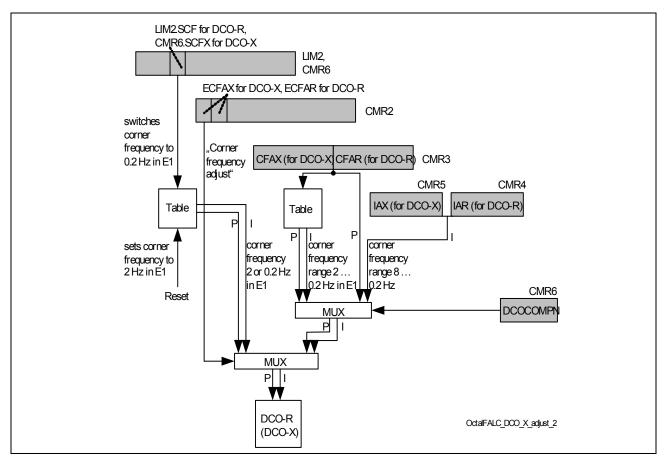

### 5.5 DCO-R/DCO-X Characteristics

The corner frequencies of DCO-R and DCO-X can be adjusted in a wider range. Proposal: The DCO-X and the DCO-R (2nd order PLLs) must have eigenfrequencies in the range 8 Hz to 0.2 Hz, for example 8 Hz, 4 Hz, 2 Hz, 1 Hz, 0.5 Hz, 0.25 Hz, 0.125 Hz

and should have an attunation factor of about 1.1 (minimum of equivalent noise bandwidth) for minimum jitter at the output. The appropriate P- and I- factors of the PLL loop filter and registerbits of CMR3 and CMR6 are to be defined.

The corner frequencies after reset are 2 Hz and can be switched to 0.2 Hz with the register bit LIM2.SCF for the receive direction (DCO-R) and with the register bit CMR5.SCFX for the transmit direction (DCO-X) if corner frequency adjust is not enabled by the register bit CMR2.ECFAX or CMR2.ECFAR respectively.

If corner frequency adjust is enabled it can be individually configured by using the registers CMR3, CMR4 and CMR5.

The adaption speed can be adjusted...

Figure 19 Principle of Setting Parameters of the DCO-X and DCO-R

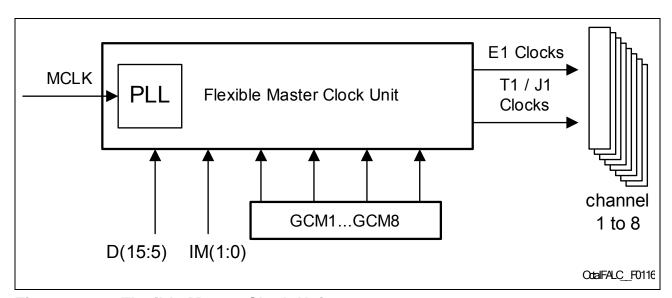

# 5.6 PLL Reset and Configuring

The OctalFALC<sup>TM</sup> provides a flexible clocking unit, which references to any clock in the range of 1.02 to 20 MHz supplied on pin MCLK, see **Figure 20**.

The clocking unit has two different modes:

In the "flexible master clocking mode" (GCM2.VFREQ\_EN = ´1´) the clocking unit

has to be tuned to the selected reference frequency by setting the global clock mode

registers GCM(8:1) accordingly, see formulas in GCM6 description. All eight ports can work in E1 or T1 mode individually. After reset the clocking unit is in "flexible master clocking mode".

• In the "clocking fixed mode" (GCM2.VFREQ\_EN = '0') the tuning of the clocking unit is done internally so that no setting of the global clock mode registers GCM(8:1) is necessary. All eight ports must work together either in E1 or in T1 mode.

For the calculation for the appropriate register settings the "flexible Master Clock Calculator" can be used which is part of the software support of the OctalFALC<sup>TM</sup>.

All required clocks for E1 or T1/J1 operation are generated by the device internally. The global setting depends only on the selected master clock frequency and is the same for E1 and T1/J1 because both clock rates are provided simultaneously.

To meet the E1 requirements the MCLK reference clock must have an accuracy of better than  $\pm$  32 ppm. The synthesized clock can be controlled on pins RCLK, SCLKR and XCLK.

Figure 20 Flexible Master Clock Unit

If the (asynchronous) microcontroller interface mode is selected by IM(1:0) the PLL must be configured either

- By programming of the registers GCM5 and GCM6 in "flexible master clocking mode". Every change of the contents of these registers - the divider factors N and M of the PLL - causes a reset of the PLL. Switching between E1 and T1 modes in arbitrary channels causes a reset of the clock unit but not of the PLL itself.

- Or by enabling of the "fixed mode": GCM2.VFREQ\_EN = '0'. Programming of registers GCM5 and GCM6 is not necessary. Any programming of GCM5 and GCM6 does NOT cause a reset of the PLL. Switching between E1 and T1 modes (for all channels) causes a reset of the clock unit but not of the PLL itself.

The SPI and SCI are synchronous interfaces and therefore need defined clocks immediately after reset, before any device configuration is done. To enable access to

serial interfaces, the clock MCLK must be active and must have a defined frequency before reset becomes inactive. Depending on the supplied MCLK frequency the internal PLL must be configured if the SCI- or SPI-Interface mode is selected by IM(1:0). This can be performed either

- By strapping of the pins D(15:5) if "flexible master clocking mode" is enabled (GCM2.VFREQ\_EN = ´1´). Because the "flexible master clocking mode" is enabled after reset, pinstrapping at D(15:5) is always necessary! Every status change of the signals at these pins causes a reset of the PLL. Configuring by the registers GCM5 and GCM6 has no effect and does not cause a reset of the main PLL

- Or by usage of the "clocking fixed mode" (GCM2.VFREQ\_EN = ´0´). This is only allowed if the values of N and M defined by pinstrapping are identical to that values which are internally used for the "clocking fixed mode". This avoids changing of N and M by switching into the "clocking fixed mode" and therefore a new reset of the PLL. (A reset of the PLL can cause a reset of the hole transceiver! Clock and data processing will be interrupted.) The used values of N and M in "clocking fixed mode" are: N = ´33<sub>10</sub>´, M = ´0<sub>10</sub>´. This requires the pinstrapping configuration to be: D(10:5) = ´HLLLLH´, D(15:11) = ´LLLLL´. In "clocking fixed mode" further programming of the registers GCM1 to GCM8 is no longer necessary. The pinstrapping configuration at the pins D(15:5) do not have any effect. Changing of these values does NOT cause a reset of the PLL. Switching between E1 and T1 modes causes a reset of the clock unit but not of the main PLL itself.

The configuration of the PLL by pinstrapping in case of serial interface modes is done in the same way as by using the registers GCM5 and GCM6 if asynchronous micro controller interface mode (Intel or Motorola) is selected. Calculation of the values to be configured by pinstrapping can be done also by using the formulas described for the registers GCM6 or by using the "flexible Master Clock Calculator" which is part of the software support of the OctalFALC<sup>TM</sup>. If the serial interfaces are selected, pinstrapping of D(15:5) configures the PLL directly, so changes causes a direct reset of the PLL.

The conditions to trigger a reset of the central clock PLL are listed in **Table 8**. Every reset of the PLL causes a reset of the clock system.

Table 8 Conditions for a PLL Reset

| Reset Pin | GCM2.VFREQ_EN                       | Used controller interface | A PLL reset is made |

|-----------|-------------------------------------|---------------------------|---------------------|

| active    | x<br>(will be set to ´1´by<br>reset | x                         | always              |

Table 8 Conditions for a PLL Reset (cont'd)

| Reset Pin | GCM2.VFREQ_EN | Used controller interface        | A PLL reset is made                                                                                           |

|-----------|---------------|----------------------------------|---------------------------------------------------------------------------------------------------------------|

|           | 1             | asynchron<br>(Motorola or Intel) | if GCM5 or GCM6<br>are written and their<br>values N or M<br>changes                                          |

|           |               | SCI or SPI                       | if pinstrappng<br>values change                                                                               |

| inactive  | 0             | asynchron<br>(Motorola or Intel) | never                                                                                                         |

|           |               | SCI or SPI                       | if pinstrappng values change                                                                                  |

|           | 0 -> 1        | asynchron<br>(Motorola or Intel) | if actual values of N<br>or M in GCM5 in<br>GCM6 are different<br>to internal settings<br>of the "fixed mode" |

|           | or<br>1 -> 0  | SCI or SPI                       | if pinstrap values in<br>are different to<br>internal settings of<br>the "fixed mode".<br>That is not allowed |

# 5.7 PLL Interrupt Status Bits

If the central clock PLL status indication bit GIS2.PLLLS *changes*, an interrupt is generated. An additional bit GIS2.PLLLC is provided to indicate the change. Masking can be made by GIMR.PLLL. The visibility of PLLLC can be set by the register bit IPC.VISPLL.

For COMP = ´1´ both of the pseudo QuadFALC®s have its own (interrupt) status register GIS2 and mask register GIMR. The status of the one PLL is "doubled" for the two status registers . So masking or setting of the visibility can be made Individually in both of the pseudo QuadFALC®s.

The status bit PLLLS is only available for COMP = '1', but the status of the PLL is shown in GIS2.PLLLS independent on the value of COMP.

.

**Framer Features**

## 6 Framer Features

# 6.1 Remote Defect Indication (E1 only)

In E1 mode, Remote Defect Indication (RDI) is implemented in compliance with ITU-T G.775 (chapter 6):

Criteria for detection and clearance of a Remote Defect Indication (RDI) defect, chapter 6.1 and 6.2:

"A Remote Defect Indication (RDI) defect at 2048 kbit/s TS-16 path termination functions is detected (status register bit FRS1.RDI) when the incoming signal has the "alarm indication to the remote" bit set to binary ONE ("1") for z consecutive CAS multiframe periods, where z = 1 ...5. z = 1

The RDI defect is cleared when the incoming signal has the "alarm indication to the remote end" bit set to binary ZERO ("0") for z consecutive CAS multiframe periods.

Note: The alarm indication to the remote end bit is the "y bit" in TS-16's frame 0 of the CAS multiframe defined in 5.1.3.2.2/G.704."

"A Remote Defect Indication (RDI) defect at 2048 kbit/s path termination functions is detected when the incoming signal has the "Remote alarm indication" bit set to binary ONE ("1") for z consecutive double frame periods, where z = 2,...5. z = 10 is not provisionable.

The RDI defect is cleared when the incoming signal has the "Remote alarm indication" bit set to binary ZERO ("0") for z consecutive double frame periods.

Note: The Remote alarm indication bit is the "A bit" in the 2048 kbit/s frame defined in Recommendation G.704."

#### Implementation:

Controlling of the number (z) of multiframe periods or double frame periods is performed by the register bits FMR4.RDIS(1:0) and FMR4.RDIC(1:0). The RDI bit FRS1.RDI is a status bit, not an interrupt status bit.

# 6.2 Automatic Sending of Transmit Remote Alarm (T1/J1 only)

Note: As in FALC56 V2

In T1/J1 mode, the Automatic Remote Alarm feature (AXRA) is now compliant with ANSI T1.403-1999 (see **Figure 21**).(The one-second requirement for on/off must be fulfilled.)

**Framer Features**

#### 9 Maintenance

#### 9.1 Remote Alarm Indication (RAI)

The Remote Alarm Indication signal was formerly widely known in the industry as the Yellow Alarm. The RAI designation is used in other ANSI standards and ITU-T Recommendations. An RAI signal shall be transmitted in the outgoing direction when DS1 terminal equipment located in either the network or the CI determines that it has effectively lost the incoming signal. The detailed requirements for sending RAI are contained in ANSI T1.231. An RAI signal shall be transmitted across the NI in the following forms:

- Superframe format:<sup>(2)</sup> For the duration of the alarm condition, but for at least one second, bit two in every DS0 channel shall be a zero. This arrangement shall be used even if the payload is not channelized;

- Extended superframe format: For the duration of the alarm condition, but for at least one second, a

repeating 16-bit pattern consisting of eight "ones" followed by eight "zeros" shall be transmitted

continuously on the ESF data link, but may be interrupted for a period not to exceed 100-ms per

interruption (see 9.5.1.1.1 and 9.6);

- Both formats: For either framing format, the minimum time between the end of one transmission of RAI and the beginning of another transmission of RAI shall be one second. Certain services provided by the carrier may require longer time intervals than these minimum values, or may require unequal on and off intervals, or both longer intervals and unequal "on" and "off" intervals.

## Figure 21 AXRA Requirements

# 6.3 RSC Interrupt (T1/J1 only)

The RSC interrupt can be suppressed for cleared channels to reduce the interrupt load. Suppression mode is selected by CCR1.RSCC = 1.

# 6.4 DL-Bit Access (T1/J1 only)

In T1/J1 ESF mode the DL-bit access is improved to reduce the number of required register accesses by 25%. For details see **Figure 22** and **Figure 23**. The optional mode is selected by the new register bit FMR5.DLM. The transmit direction works accordingly.

BOM-Codes can be inserted continuously without additional microcontroller access every multiframe.

The BOM code has the following format: 11111111 0xxxxxx0 were the left bit here of every byte is the MSB and the right one is the LSB. (11111111 is the BOM flag, xxxxxx is the BOM code) That's another ordering as in ANSI T1.403, 1999, table 4 !!. Sending is done as for HDLC: LSB first. That's consistent to the note 1) in the ANSI: "rightmost bit transmitted first".

#### **Framer Features**

Figure 22 Standard DL-Bit Access in ESF Mode

Figure 23 Optional DL-Bit Access in ESF Mode

**CAS Features**

# 7 CAS Features

## 7.1 Basic CAS Operation Mode

The basic operation mode (serial or register based) can be selected individually for receive and transmit direction.

If RSIG is configured on one of the RX multifunction ports RPA...RPC, serial RX-CAS data on RSIG are used automatically. If XSIG is configured on one of the TX multifunction ports XPA, RPB, serial TX-CAS data on XSIG are used automatically and XS1...16 registers are ignored.

# 7.2 Bit Robbing Force One in Cleared Channels (T1/J1 only)

In T1 mode the function to force all robbed bits to "one" can be selected to be not performed in CAS cleared channels. This mode is selected by setting register bit XC0.BRFO1 = 1.

# 7.3 Bit Robbing Idle (T1/J1 only)

In T1 mode the bit robbing idle function is selectable by register bit XC0.BRIF. If this bit is set, bit robbing information is not overwritten by the idle code in idle channels.

Delta Sheet 36 Rev. 2.0, 2005-05-03

#### **HDLC/BOM Controllers**

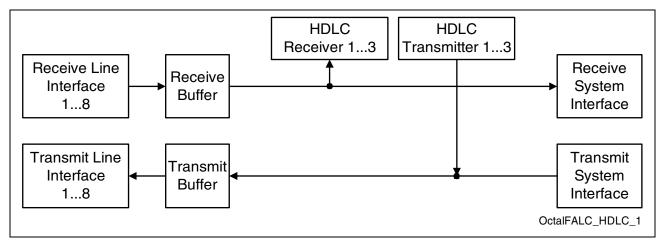

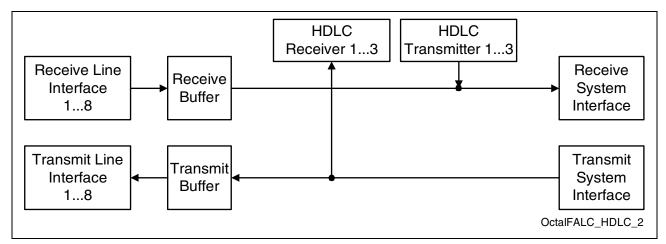

### 8 HDLC/BOM Controllers

Each of the eight ports provides three HDLC/BOM Controllers. Each of these units can be attached to either the line side ("standard") or the system side ("inverse"). Inverse HDLC mode is selected by setting MODE.HDLCI = 1, MODE2.HDLCI2 = 1, or MODE3.HDLCI3 = 1 (for each of the three HDLC controllers and each of the eight E1/T1/J1 ports individually). Note that a detection of a Out-Band loop message (BOM code) on the line side is only possible if the HDLC controller is attached to the line side; a detection of a BOM code on the system side is only ossible in the "inverse" mode of the HDLC controller.

Each HDLC/BOM controller can be reset individually without disturbing the transmission on the remaining channels. Use CMDR.SRES for HDLC channel 1, CMDR3.RRES and CMDR3.SRES for HDLC channel 2, and CMDR4.RRES and CMDR4.SRES for HDLC channel 3, respectively.

Each of the eight ports provides one signalling controller for SS7 signaling.

The signalling controller has an interrupt status bit ISR1.SUEX which shows exceeding of the error threshold in SS7 mode. These interrupt status bit is masked by the bit IMR1.SUEX.

The error counter for SS7 mode can be reset by setting the register bit CMDR2.RSUC.

The error threshold for SS7 mode can be configured by setting the register bit CCR5.SUET.

After an RDO interrupt on one HDLC controller, the receive HDLC controller needs no reset. So a receive HDLC controller reset per channel is not necessary.

Note: CMDR.RRES resets the whole RX path and therefor all HDLC channels.

The FIFO depth is doubled to 128 byte in RX, see **Table 9**, and 128 byte in TX (by setting register bit CCR2.TFTS) per HDLC/BOM controller (64 byte user and 64 byte shadow RAM).

As in the FALC56 version V2.1 the total length of the received frame can be always read directly in registers RBCL and RBCH after a RPF interrupt, except when the threshold is increased during reception of that frame, but additionally to the FALC56 version V2.1 bit RBC5 will be taken into account if the FIFO depth is 64 bytes, see **Table 9** as example for the HDLC channel 1. The register bits CCR3.RFT(2:0)2 and CCR4.RFT(2:0)3 set the FIFO depth in the same way for the HDLC channel 2 and 3 respectively.

If a HDLC frame was completely received the content of the register RSIS (HDLC channel1, RSIS2 andRSIS3 for HDLC channel 2 and 3) will be written as last byte into the receive FIFO.

#### **HDLC/BOM Controllers**

Table 9 Receive FIFO User Depth (HDLC channel 1) and Bit Positions in Register RBCL

| # bytes | CCR1.RFT(1:0) | MODE.RFT2 | Bit Positions in<br>RBCL Reset by a<br>CMDR.RMC<br>Command |

|---------|---------------|-----------|------------------------------------------------------------|

| 32      | 00            | 0         | RBC(4:0)                                                   |

| 16      | 01            | 0         | RBC(3:0)                                                   |

| 4       | 10            | 0         | RBC(1:0)                                                   |

| 2       | 11            | 0         | RBC0                                                       |

| 64      | xx            | 1         | RBC(5:0)                                                   |

Figure 24 HDLC Controller Standard Configuration for all three HDLC Channels

Figure 25 HDLC Controller Inverse Configuration for All Three HDLC Channels

Delta Sheet 38 Rev. 2.0, 2005-05-03

Switchin between HDLC and BOM (if both MODE.BRAC and MODE.HRAC are set) will be done in the following way:

- After reset the HDLC/BOM controller is in HDLC mode

- After eight consecutive ones (´FF<sub>H</sub>´) were received: switching to BOM mode (note that eight consecutive ones are also an HDLC abort)

- After one HDLC flag (´7E<sub>H</sub>´) was received: switching to HDLC mode (directly, additionalHDLC flags are not necessary)

- Asequence 'FF<sub>H</sub>', '7E<sub>H</sub>' are seen also as HDLC start flag

The status bit SIS.BOM reflects the actual mode of the HDLC/BOM controller.

Note that BOM codes  $7E_H$  should be avoid.

If a BOM message occurs "inside" of a HDLC protocoll, the HDLC protocoll (frame) is corrupted.

# 9 System Interface

### 9.1 System Multiplex Mode

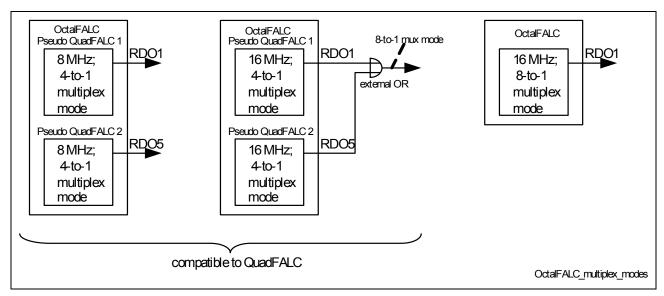

The following multiplex modes are supported, see **Figure 26**, were only pins RDO of the ports are shown, and **Table 10**:

- 8-to-1 Multiplex Mode at 16 Mbit/s. Multiplexing is done on port 1. Output pins of the other ports are set to tristate input pins of the other ports are unused.

- Dual 4-to-1 Multiplex Mode at 8 Mbit/s. Multiplexing is done on port 1 and port 5.

Output pins of the other ports are set to tristate, input pins of the other ports are unused.

- Dual 4-to-1 Multiplex Mode at 16 Mbit/s. Multiplexing is done on port 1 and port 5

were four phases are unused on every port. Disjunct phases must be used on both

ports. 16 Mbit/s multiplexing is done by external logical or on the PCB. Output RDO

is driven to low level for inactive phases. Output pins of the other ports are undefined,

input pins of the other ports are unused.

Switching between 8-to-1 Multiplex Mode (using only one port) and QuadFALC® compatible 4:1 Multiplex Modes (using two or more ports) is done by the register bit GPC6.SSI16, see **Table 10**.

Multiplexing of RSIG is done in the same way as shown for RDO in Figure 26. Demultiplexing of XDI and XSIG is done vice versa.

Figure 26 Principle of System Interface Multiplex Modes, shown for RDO

Table 10 System Multiplex Modes

| GPC1.SMM | GPC6:SSI16 | Mode                                                                                                                                                                                                                                                    |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 0          | No multiplexing                                                                                                                                                                                                                                         |

| 0        | 1          | Not defined                                                                                                                                                                                                                                             |

| 1        | 0          | 4:1 multiplexing; 8Mbit/s or 16Mbit/s dependent on SIC1.SSD1 and SIC1.SSC(1:0). For COMP = '1' setting of 4:1 multiplexing can be done individually in both pseudo QuadFALC® s; for COMP='0' 4:1 multiplexing is done in both of the pseudo QuadFALC® s |

| 1        | 1          | 8:1 multiplexing; 16Mbit/s. For COMP = '1' the register bit GPC1.SMM must be set to '1' in both of the pseudo QuadFALC® s. (For COMP = '0' only one register bit GPC1.SMM exists.)                                                                      |

To perform the system interface mode the following configuration of the multi function ports must be identical for all channels:

- SYPR has to be provided on RPA

- SYPX1 or XMFS has to be provided on XPA

- XSIG has to be provided on XPB

- RSIG must be output on RPB

All other assumptions to perform the system interface mode are the same as described in the data sheet of the QuadFALC<sup>®</sup>.

### 9.2 Clock Edge Selection

The active clock edge of SYPX can be selected related to that of the other interface transmit data and marker. Also selection of the clock edge for SYPR is possible related to that of the other interface receive data and marker. Use register bits SIC4.SYPRCE, or SIC4.SYPXCE. Note that the clock selection of the transmit data and marker with exception of SYPX is done by SIC3.RESX and that of the receive data and marker with exception of SYPR is done by SIC3.RESR.

#### 9.3 Tristate Modes

- FSC can be switched into tristate mode by setting SIC3.FSCT = 1.

- RDO and RSIG can be switched into tristate mode for unused time slots by setting SIC3.RTRI = '1'.

- RDO, RSIG, SCLKR and RFM can be set into tristate mode constantly (for redundancy applications) using the registerbit SIC3.RRTRI and if the RTDMT function is selected on one of the multi fuction port by RTDMT. If the RTDMT function is selected the values of RTDMT and SIC3.RRTRI are logically exored. This enables an easy redundance application using only one signal for switching between two devices, see the next chapter. If the RTDMT function is not selected SIC3.RRTRI = ´1´ set the pins into tristate mode constantly. In this mode "tristate" means high impedance against V<sub>DD</sub> and V<sub>SS</sub>: No pull up or pull down resistor is active.

Table 11 Tristate Configurations for the RDO, RSIG, SCLKR and RFM Pins

| - RRTRI / - RRTRI exor RTDMT if RTDMT is selected on MFP | RTRI | RDO, RSIG                                                        | SCLKR, RFM                                                       |  |  |  |  |

|----------------------------------------------------------|------|------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| 1                                                        | х    | Constant tristate<br>(without pull up and<br>pull down resistor) | Constant tristate<br>(without pull up and<br>pull down resistor) |  |  |  |  |

| 0                                                        | 0    | Never tristate                                                   | Never tristate                                                   |  |  |  |  |

| 0                                                        | 1    | Tristate during inactive channel phases (with pull up resistor)  |                                                                  |  |  |  |  |

### 9.4 Redundancy Mode

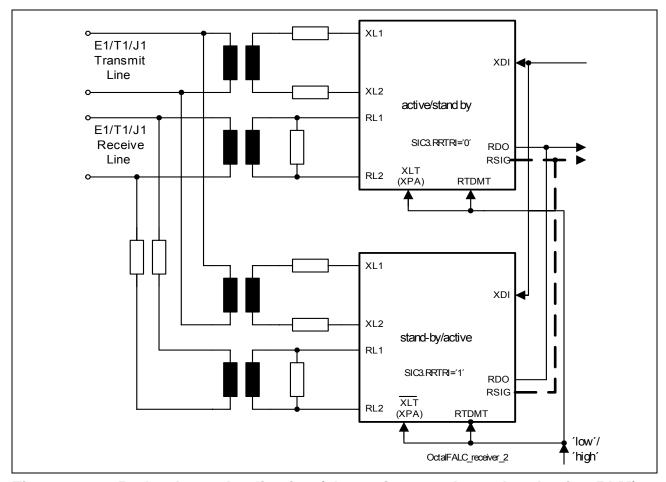

In redundancy mode the data inputs XDI are connected together. The outputs RDO and the signaling outputs RSIG (if used) of two channels can be connect together in the OctalFALC<sup>TM</sup> also, because one of them is set constantly into tristate respectively while the other is active. **Figure 27** shows the application.

Both channels must be configured identically and must be supplied with the same clocks and (transmit) data and signaling.

Switching between both channels can be done on the line side in transmit direction by a hardware signal if the multi function pin XPA is configured as tristate input XLT by the register bits PC1.XPC1 = '1000b'. If one pin XPA is programmed as low active (PC1.XPC1 = '1110b') and the one of the other channel as high active (PC1.XPC1 = '1000b'), no external inverter is necessary as shown in **Figure 27**. So switching between both channels on line side is possible using only one signal.

Switching can also be done on the line side in transmit direction by software, if setting the register bit XPM2.XLT. The register bit value XPM2.XLT and the pin value of XPA are logically ored. (That means if XPA is configured as low active then

tristate = XPM2.XLT or not( $\overline{XPA}$ ).)

Because the register bit XPM2.XLT and the multi function pin XPA exist individually for every channel, switching on the line side in transmit direction can be done between channels of different or of the same OctalFALC<sup>TM</sup> device.

Switching between both channels can be done on the system side in receive direction by using the registerbit SIC3.RRTRI and with or without selection of the multi function port as RTDMT. If the RTDMT function is selected the values of RTDMT and SIC3.RRTRI are logically exored. If in one of the both channels SIC3.RRTRI is set, RTDMT is low active because of the logical exor, and if in the other channel SIC3.RRTRI is cleared, RTDMT is low active because of the logical exor. So switching between both channels on system side in receive direction is possible using only one signal.

By using the XLT, XLT and RTDMT function of the multi function ports and do the appropriate programming of the bits SIC3.RRTRI, switching between both channels can be done on the system and the line side together with only one common signal, as shown in **Figure 27** and **Table 12**.

Table 12 Redundancy Application Using RLM Mode

| Configuration | Register Bits | Channel 1 (active/stand-by) | Channel 2 (stand-by/active) |  |  |  |

|---------------|---------------|-----------------------------|-----------------------------|--|--|--|

| XLT, XLT      | PC1.XPC1(3:0) | 1000                        | 1110                        |  |  |  |

| RTDMT         | PC1.RPC1(3:0) | 1101                        | 1101                        |  |  |  |

Table 12 Redundancy Application Using RLM Mode (cont'd)

| Configuration            | Register Bits | Channel 1 (active/stand-by) | Channel 2 (stand-by/active) |

|--------------------------|---------------|-----------------------------|-----------------------------|

| Receive system interface | SIC3.RRTRI    | 0                           | 1                           |

| RLM mode                 | LIM0.RLM      | 0                           | 1                           |

Figure 27 Redundancy Application (shown for one channel and using RLM)

To fulfill these requirements the RX- and TX-pathes of the two channels must be work synchronous to another.

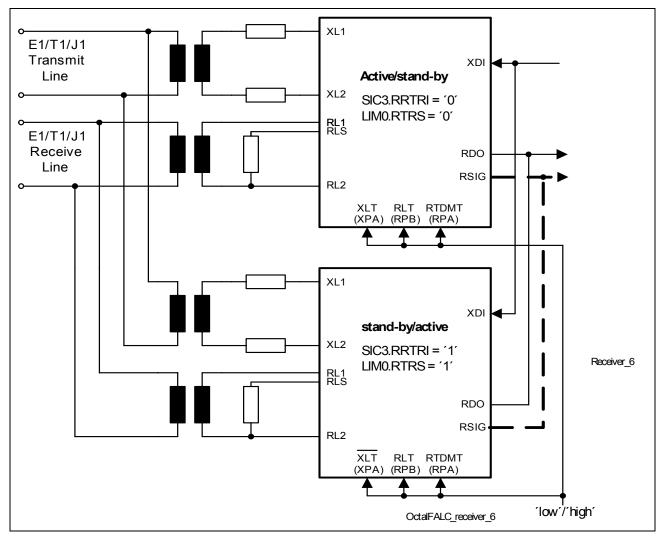

**Figure 28** shows a redundancy application for long haul mode using the internal analog switch. With the configuration shown in **Table 13**, switching between both channels is possible using only one board signal which is connected to XLT, XLT, RLT and RTDMT. Because the OctalFALC<sup>TM</sup> builds the logical equivalence out of RLT and LIM0.RTRS, the analog switches of both channels are controlled by these signal.

Figure 28 Long Haul Redundancy Application using the Analog Switch (shown for one line)

Table 13 Redundancy Application Using the Analog Switch, Switching with only one Board Signal

| Configuration            | Register Bits | Channel 1 (active/stand-by) | Channel 2 (stand-by/active) |  |  |

|--------------------------|---------------|-----------------------------|-----------------------------|--|--|

| XLT, XLT                 | PC1.XPC1(3:0) | 1000                        | 1110                        |  |  |

| RTDMT                    | PC1.RPC1(3:0) | 1101                        | 1101                        |  |  |

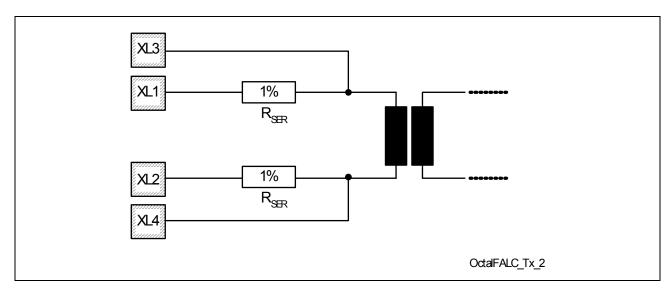

| Receive system interface | SIC3.RRTRI    | 0                           | 1                           |  |  |