# MC9S12E-Family Device User Guide V01.04

Original Release Date: 4 APR 2003 Revised: 04 NOV 2003

Motorola, Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

©Motorola, Inc., 2003

# **Revision History**

| Version<br>Number | Revision<br>Date | Author | Description of Changes                                                                                                                                                                                                                                                                       |

|-------------------|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01.00             | 04.APR.03        |        | Original Version.                                                                                                                                                                                                                                                                            |

| 01.01             | 24.JUN.03        |        | Minor typo corrections.                                                                                                                                                                                                                                                                      |

| 01.02             | 9.OCT.03         |        | MC9S12E32 added.                                                                                                                                                                                                                                                                             |

| 01.03             | 31.OCT.03        |        | Added Colpitts and Pierce connections to 2.3.8. Updated input capacitance. Updated Table A-8. Changed pin name ROMONE to ROMCTL. Added S12 LRAE to Flash section. Added EXTAL VIH and VIL min/max values and hysteresis value to Oscillator Characteristics. New wording on NVM Reliability. |

| 01.04             | 04.NOV.03        |        | Updated PCB layouts. Changed PP6 to PK7 on Table 4-1. Updated DAC Supply min voltage and Operating frequency. Added Non-multiplexed Address and Chip Select external bus timing.                                                                                                             |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

©Motorola, Inc., 2003

# **Table of Contents**

# **Section 1 Introduction**

| 1.1    | Overview                                                            |

|--------|---------------------------------------------------------------------|

| 1.2    | Features                                                            |

| 1.3    | Modes of Operation                                                  |

| 1.4    | Block Diagram                                                       |

| 1.5    | Device Memory Map                                                   |

| 1.6    | Detailed Register Map                                               |

| 1.7    | Part ID Assignments74                                               |

| Secti  | on 2 Signal Description                                             |

| 2.1    | Device Pinout                                                       |

| 2.2    | Signal Properties Summary                                           |

| 2.3    | Detailed Signal Descriptions80                                      |

| 2.3.1  | EXTAL, XTAL — Oscillator Pins                                       |

| 2.3.2  | RESET — External Reset Pin                                          |

| 2.3.3  | TEST — Test Pin80                                                   |

| 2.3.4  | XFC — PLL Loop Filter Pin                                           |

| 2.3.5  | BKGD / TAGHI / MODC — Background Debug, Tag High & Mode Pin80       |

| 2.3.6  | PA[7:0] / ADDR[15:8] / DATA[15:8] — Port A I/O Pins                 |

| 2.3.7  | PB[7:0] / ADDR[7:0] / DATA[7:0] — Port B I/O Pins                   |

| 2.3.8  | PE7 / NOACC / XCLKS — Port E I/O Pin 781                            |

| 2.3.9  | PE6 / MODB / IPIPE1 — Port E I/O Pin 6                              |

| 2.3.10 | PE5 / MODA / IPIPE0 — Port E I/O Pin 5                              |

| 2.3.11 | PE4 / ECLK— Port E I/O Pin 4 / E-Clock Output                       |

| 2.3.12 | PE3 / LSTRB / TAGLO — Port E I/O Pin 3 / Low-Byte Strobe (LSTRB) 83 |

| 2.3.13 |                                                                     |

| 2.3.14 | PE1 / IRQ — Port E input Pin 1 / Maskable Interrupt Pin             |

| 2.3.15 | PE0 / XIRQ — Port E input Pin 0 / Non Maskable Interrupt Pin        |

| 2.3.16 | PK7 / ECS / ROMCTL — Port K I/O Pin 7                               |

| 2.3.17 |                                                                     |

| 2.3.18 | PK[5:0] / XADDR[19:14] — Port K I/O Pins [5:0]                      |

| 2.3.19 | PAD[15:0] / AN[15:0] / KWAD[15:0] — Port AD I/O Pins [15:0]         |

| 2.3.20 | PM7 / SCL — Port M I/O Pin 785                                      |

#### Device User Guide — 9S12E128DGV1/D V01.04

| 2.3.21      | PM6 / SDA — Port M I/O Pin 6                                                    |

|-------------|---------------------------------------------------------------------------------|

| 2.3.22      | PM5 / TXD2 — Port M I/O Pin 5                                                   |

| 2.3.23      | PM4 / RXD2 — Port M I/O Pin 4                                                   |

| 2.3.24      | PM3 — Port M I/O Pin 3                                                          |

| 2.3.25      | PM1 / DAO1 — Port M I/O Pin 1                                                   |

| 2.3.26      | PM0 / DAO2 — Port M I/O Pin 0                                                   |

| 2.3.27      | PP[5:0] / PW0[5:0] — Port P I/O Pins [5:0]                                      |

| 2.3.28      | PQ[6:4] / IS[2:0] — Port Q I/O Pins [6:4]                                       |

| 2.3.29      | PQ[3:0] / FAULT[3:0] — Port Q I/O Pins [3:0]                                    |

| 2.3.30      | PS7 / SS — Port S I/O Pin 7                                                     |

| 2.3.31      | PS6 / SCK — Port S I/O Pin 6                                                    |

| 2.3.32      | PS5 / MOSI — Port S I/O Pin 5                                                   |

| 2.3.33      | PS4 / MISO — Port S I/O Pin 4                                                   |

| 2.3.34      | PS3 / TXD1 — Port S I/O Pin 3                                                   |

| 2.3.35      | PS2 / RXD1 — Port S I/O Pin 2                                                   |

| 2.3.36      | PS1 / TXD0 — Port S I/O Pin 1                                                   |

| 2.3.37      | PS0 / RXD0 — Port S I/O Pin 0                                                   |

| 2.3.38      | PT[7:4] / IOC1[7:4]— Port T I/O Pins [7:4]                                      |

| 2.3.39      | PT[3:0] / IOC0[7:4]— Port T I/O Pins [3:0]                                      |

| 2.3.40      | PU[7:6] — Port U I/O Pins [7:6]                                                 |

| 2.3.41      | PU[5:4] / PW1[5:4] — Port U I/O Pins [5:4]                                      |

| 2.3.42      | PU[3:0] / IOC2[7:4]/PW1[3:0] — Port U I/O Pins [3:0]                            |

| 2.4         | Power Supply Pins                                                               |

| 2.4.1       | VDDX,VSSX — Power & Ground Pins for I/O Drivers                                 |

| 2.4.2<br>89 | VDDR, VSSR — Power Supply Pins for I/O Drivers & for Internal Voltage Regulator |

| 2.4.3       | VDD1, VDD2, VSS1, VSS2 — Power Supply Pins for Internal Logic 89                |

| 2.4.4       | VDDA, VSSA — Power Supply Pins for ATD and VREG                                 |

| 2.4.5       | VRH, VRL — ATD Reference Voltage Input Pins                                     |

| 2.4.6       | VDDPLL, VSSPLL — Power Supply Pins for PLL                                      |

| Secti       | on 3 System Clock Description                                                   |

| Secti       | on 4 Modes of Operation                                                         |

| 4.1         | Overview                                                                        |

| 4.2         | Chip Configuration Summary                                                      |

| 4.3   | Security93                                                           |

|-------|----------------------------------------------------------------------|

| 4.3.1 | Securing the Microcontroller                                         |

| 4.3.2 | Operation of the Secured Microcontroller                             |

| 4.3.3 | Unsecuring the Microcontroller                                       |

| 4.4   | Low Power Modes                                                      |

| 4.4.1 | Stop                                                                 |

| 4.4.2 | Pseudo Stop                                                          |

| 4.4.3 | Wait                                                                 |

| 4.4.4 | Run94                                                                |

| Secti | on 5 Resets and Interrupts                                           |

| 5.1   | Overview                                                             |

| 5.2   | Vectors                                                              |

| 5.3   | Resets                                                               |

| 5.3.1 | Effects of Reset                                                     |

| Secti | on 6 HCS12 Core Block Description                                    |

| 6.1   | CPU12 Block Description                                              |

| 6.2   | HCS12 Background Debug Module (BDM) Block Description                |

| 6.3   | HCS12 Debug (DBG) Block Description                                  |

| 6.4   | HCS12 Interrupt (INT) Block Description                              |

| 6.5   | HCS12 Multiplexed External Bus Interface (MEBI) Block Description 97 |

| 6.6   | HCS12 Module Mapping Control (MMC) Block Description98               |

| Secti | on 7 Analog to Digital Converter (ATD) Block Description             |

| Secti | on 8 Clock Reset Generator (CRG) Block Description                   |

| 8.1   | Device-specific information                                          |

| 8.1.1 | XCLKS                                                                |

| Secti | on 9 Digital to Analog Converter (DAC) Block Description             |

| Secti | on 10 Flash EEPROM Block Description                                 |

| Secti | on 11 IIC Block Description                                          |

| Secti | on 12 Oscillator (OSC) Block Description                             |

|       | · · · · · · · · · · · · · · · · · · ·                                |

# Section 13 Port Integration Module (PIM) Block Description

| <b>Section 14</b> | Pulse width | Modulator wi | th Fault protection | n (PMF) | <b>Block Des</b> | crip- |

|-------------------|-------------|--------------|---------------------|---------|------------------|-------|

| tion              |             |              | -                   |         |                  | _     |

| Section | 15 Pulse  | Width  | Modulator  | (PWM)    | Block | <b>Description</b> |

|---------|-----------|--------|------------|----------|-------|--------------------|

| OCCHOIL | io i uisc | VVIGUI | Wiodulator | (I AAIAI | DIOCK | Description        |

| Section 16 Serial Communications Interface (SCI) Block Description |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

# Section 17 Serial Peripheral Interface (SPI) Block Description

# Section 18 Timer (TIM) Block Description

# Section 19 Voltage Regulator (VREG) Block Description

| 19.1 | VREGEN                 | 100 |

|------|------------------------|-----|

| 19.2 | VDD1, VDD2, VSS1, VSS2 | 100 |

# **Section 20 Printed Circuit Board Layout Proposals**

# **Appendix A Electrical Characteristics**

| A.1    | General                                       | . 105 |

|--------|-----------------------------------------------|-------|

| A.1.1  | Parameter Classification                      | . 105 |

| A.1.2  | Power Supply                                  | . 105 |

| A.1.3  | Pins                                          | . 106 |

| A.1.4  | Current Injection                             | . 106 |

| A.1.5  | Absolute Maximum Ratings                      | . 107 |

| A.1.6  | ESD Protection and Latch-up Immunity          | . 108 |

| A.1.7  | Operating Conditions                          | . 108 |

| A.1.8  | Power Dissipation and Thermal Characteristics | . 109 |

| A.1.9  | I/O Characteristics                           | . 111 |

| A.1.10 | Supply Currents                               | . 114 |

# **Appendix B Electrical Specifications**

| B.1   | Voltage Regulator (VREG_3V3) Operating Characteristics | 117 |

|-------|--------------------------------------------------------|-----|

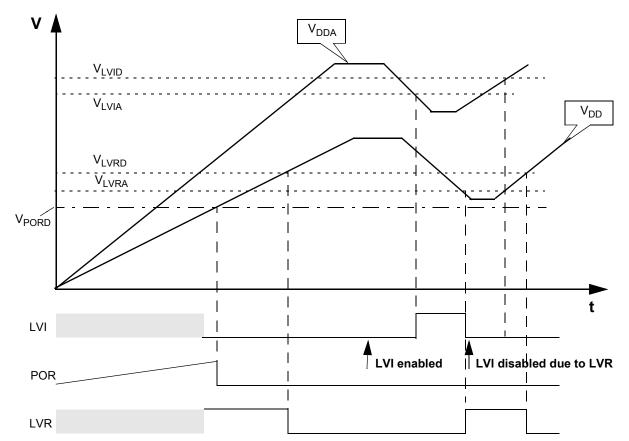

| B.2   | Chip Power-up and LVI/LVR graphical explanation        | 118 |

| B.3   | Output Loads                                           | 118 |

| B.3.1 | Resistive Loads                                        | 118 |

| B.3.2 | Capacitive Loads                           |

|-------|--------------------------------------------|

| B.4   | Reset, Oscillator and PLL121               |

| B.4.1 | Startup                                    |

| B.4.2 | Oscillator                                 |

| B.4.3 | Phase Locked Loop                          |

| B.5   | Flash NVM                                  |

| B.5.1 | NVM timing                                 |

| B.5.2 | NVM Reliability130                         |

| B.6   | SPI Characteristics                        |

| B.6.1 | Master Mode                                |

| B.6.2 | Slave Mode                                 |

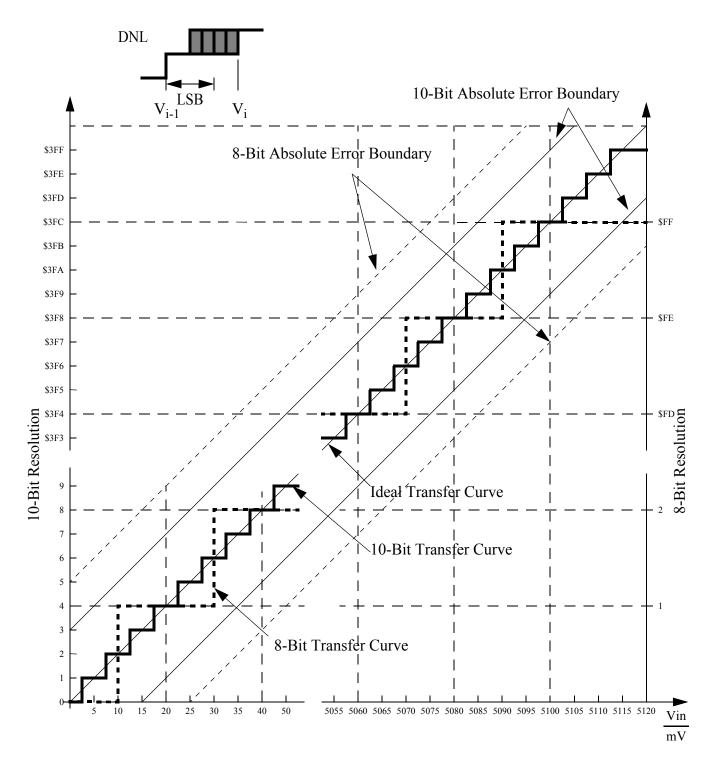

| B.7   | ATD Characteristics                        |

| B.7.1 | ATD Operating Characteristics - 5V Range   |

| B.7.2 | ATD Operating Characteristics - 3.3V Range |

| B.7.3 | Factors influencing accuracy               |

| B.7.4 | ATD accuracy - 5V Range                    |

| B.7.5 | ATD accuracy - 3.3V Range                  |

| B.8   | DAC Characteristics                        |

| B.8.1 | DAC Operating Characteristics              |

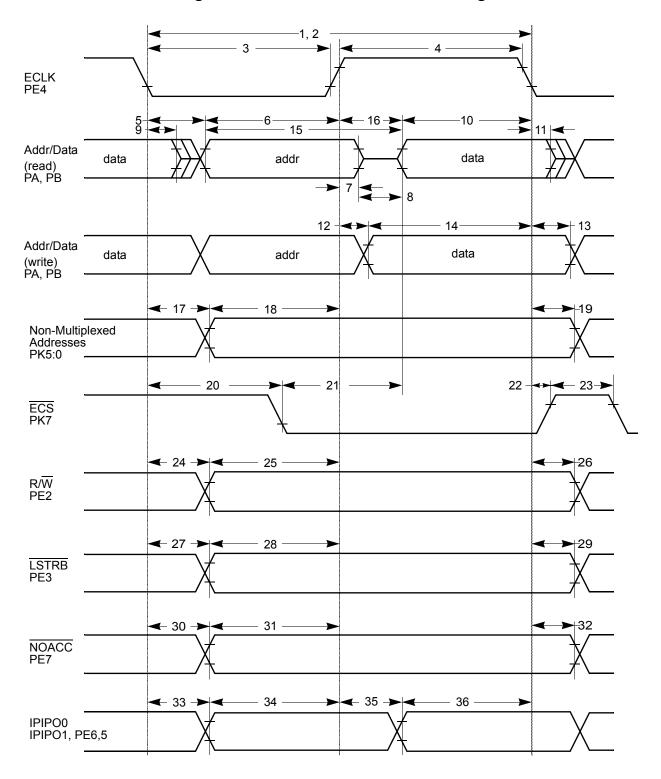

| Арре  | endix C External Bus Timing                |

| Appe  | endix D Package Information                |

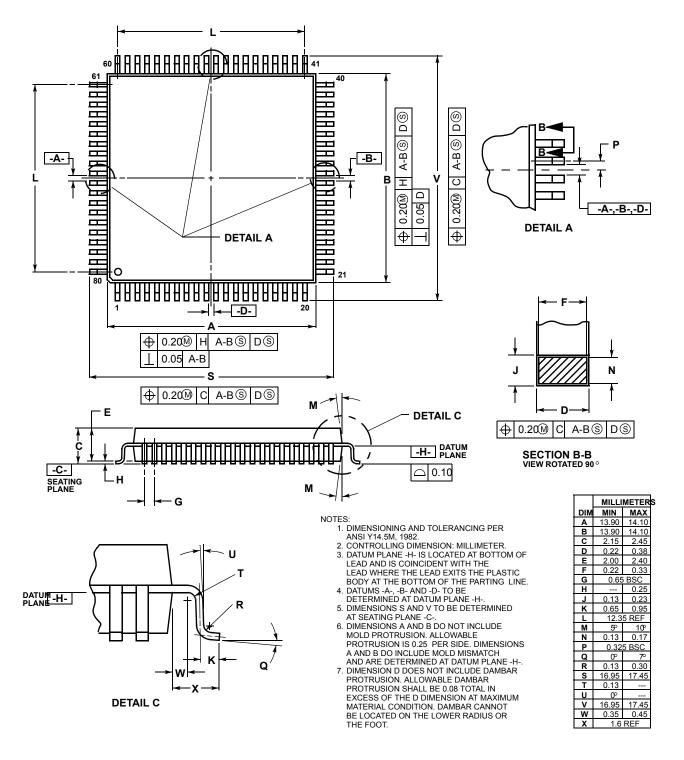

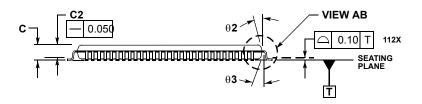

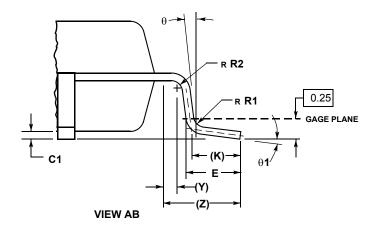

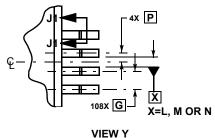

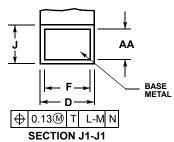

| D.1   | 80-pin QFP package                         |

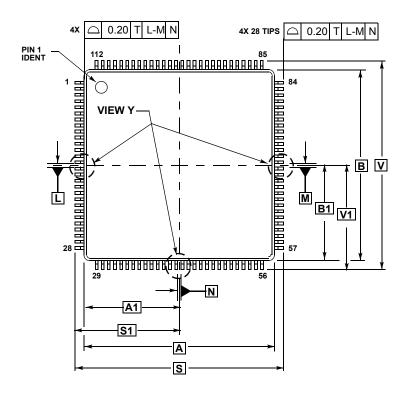

| D.2   | 112-pin LQFP package                       |

# **List of Figures**

| Figure 0-1  | Order Part Number Coding                                         | 14    |

|-------------|------------------------------------------------------------------|-------|

| Figure 1-1  | MC9S12E-Family Block Diagram                                     | 21    |

| Figure 1-2  | MC9S12E256 User Configurable Memory Map                          | 23    |

| Figure 1-3  | MC9S12E128 User Configurable Memory Map                          | 24    |

| Figure 1-4  | MC9S12E64 User Configurable Memory Map                           | 25    |

| Figure 1-5  | MC9S12E32 User configurable Memory Map                           | 26    |

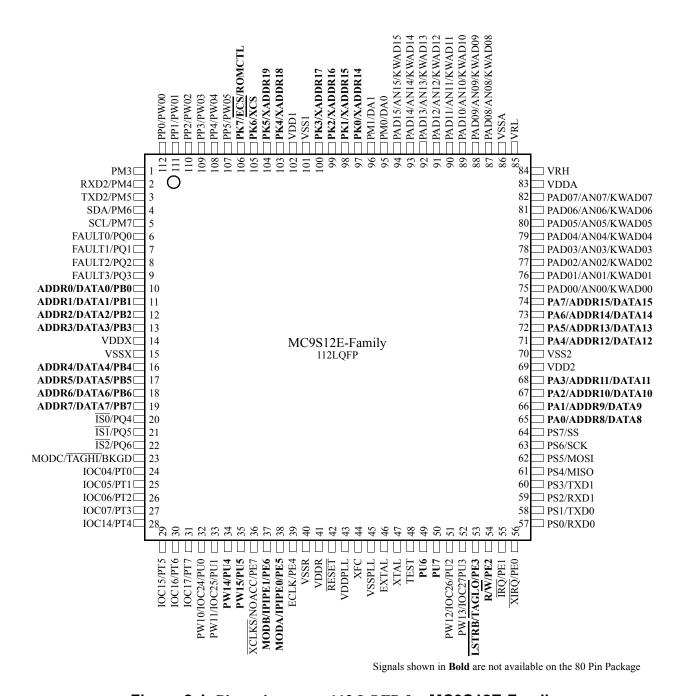

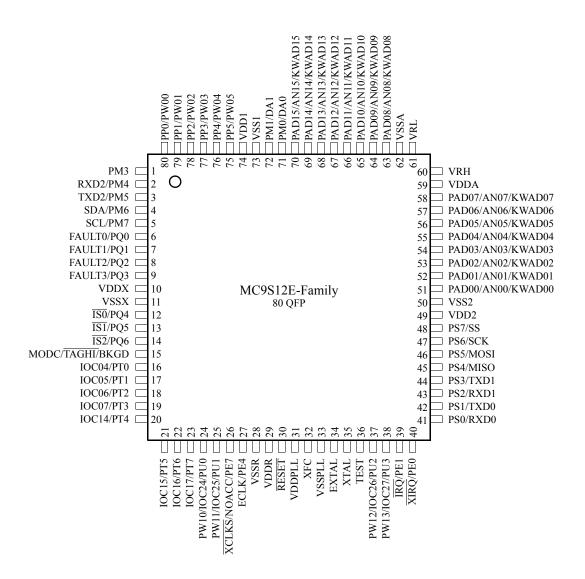

| Figure 2-1  | Pin assignments 112 LQFP for MC9S12E-Family                      | 76    |

| Figure 2-2  | Pin assignments in 80 QFP for MC9S12E-Family                     | 77    |

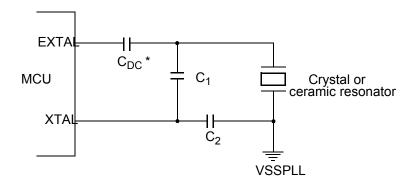

| Figure 2-3  | Colpitts Oscillator Connections (PE7=1)                          | 82    |

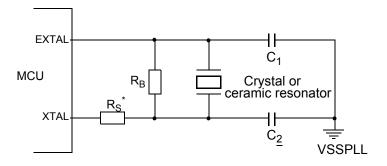

| Figure 2-4  | Pierce Oscillator Connections (PE7=0)                            | 82    |

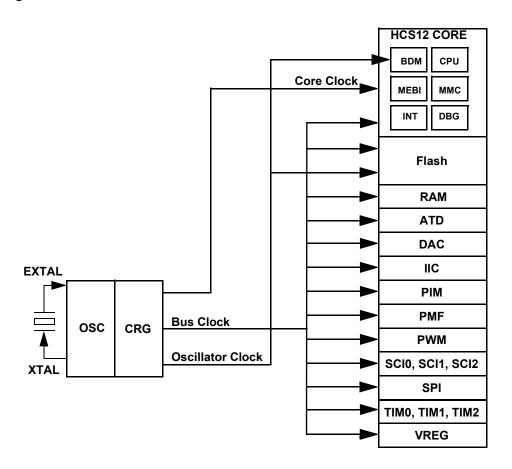

| Figure 3-1  | Clock Connections                                                | 91    |

| Figure 20-1 | Recommended PCB Layout (112 LQFP)                                | 102   |

| Figure 20-2 | Recommended PCB Layout (80 QFP)                                  | . 103 |

| Figure B-1  | Voltage Regulator - Chip Power-up and Voltage Drops (not scaled) | 118   |

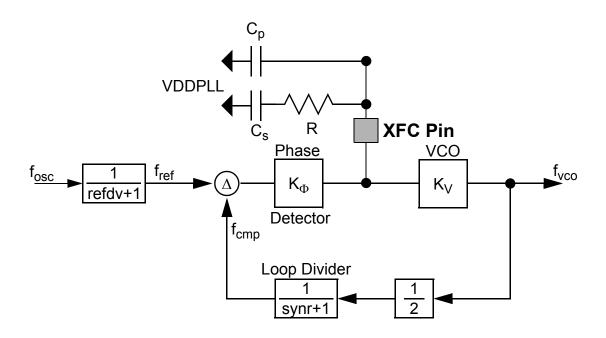

| Figure B-2  | Basic PLL functional diagram                                     | 124   |

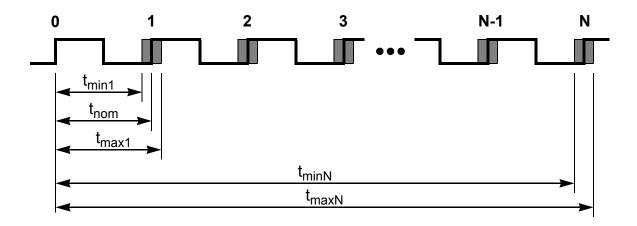

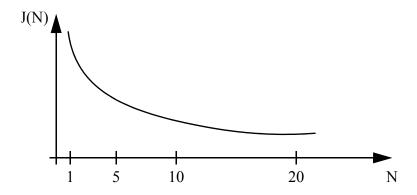

| Figure B-3  | Jitter Definitions                                               | 126   |

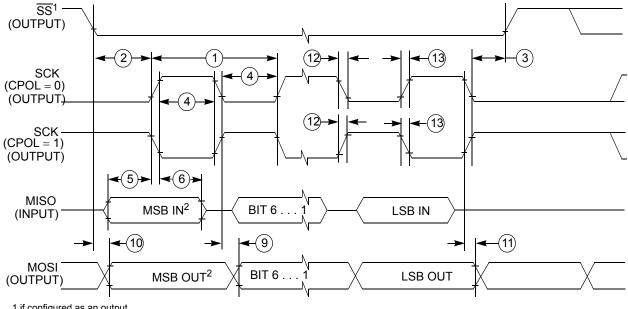

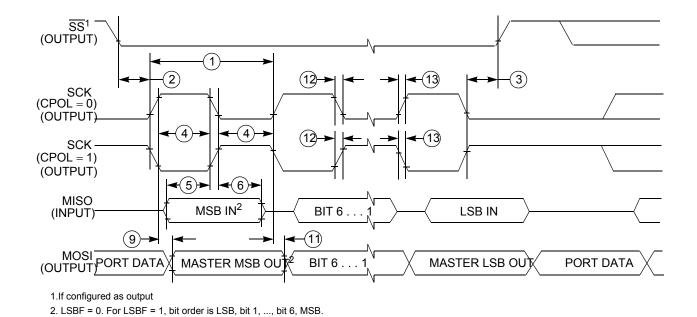

| Figure B-4  | SPI Master Timing (CPHA=0)                                       | 133   |

| Figure B-5  | SPI Master Timing (CPHA=1)                                       | 134   |

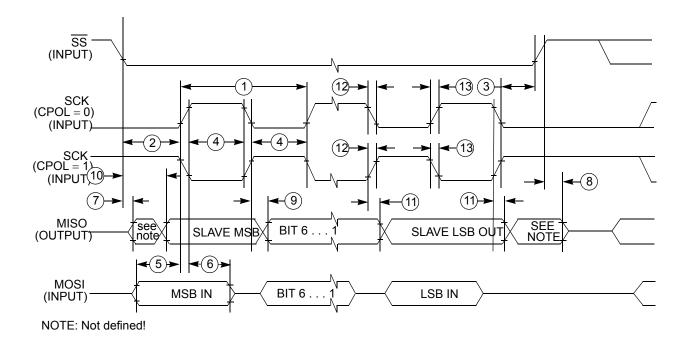

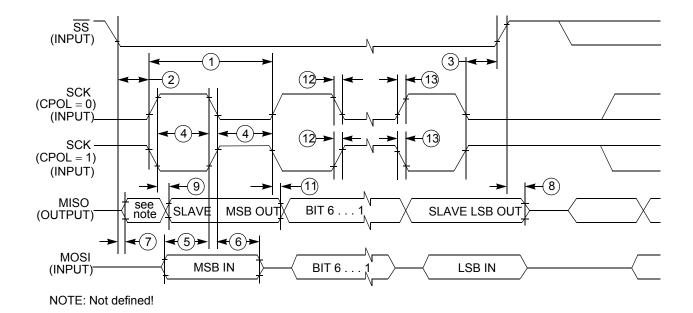

| Figure B-6  | SPI Slave Timing (CPHA=0)                                        | 135   |

| Figure B-7  | SPI Slave Timing (CPHA=1)                                        | 136   |

| Figure B-8  | ATD Accuracy Definitions                                         | 144   |

| Figure C-1  | General External Bus Timing                                      | 148   |

| Figure D-1  | 80-pin QFP Mechanical Dimensions (case no. 841B)                 | 153   |

# **List of Tables**

| Table 0-1  | Document References                                | 13  |

|------------|----------------------------------------------------|-----|

| Table 0-2  | Part Number Coding                                 | 14  |

| Table 0-3  | Package Option Summary                             | 15  |

| Table 0-4  | List of MC9S12E-Family members                     | 15  |

| Table 1-1  | Device Register Map Overview                       | 22  |

| Table 1-2  | Assigned Part ID Numbers                           | 74  |

| Table 1-3  | Memory size registers                              | 75  |

| Table 2-1  | Signal Properties                                  | 78  |

| Table 2-2  | MC9S12E-Family Power and Ground Connection Summary | 90  |

| Table 3-1  | Clock Selection Based on PE7                       | 91  |

| Table 4-1  | Mode Selection                                     | 92  |

| Table 4-2  | Clock Selection Based on PE7                       | 92  |

| Table 5-1  | Interrupt Vector Locations                         | 95  |

| Table 5-2  | Reset Summary                                      | 96  |

| Table 20-1 | Recommended decoupling capacitor choice            | 101 |

| Table A-1  | Absolute Maximum Ratings                           | 107 |

| Table A-2  | ESD and Latch-up Test Conditions                   | 108 |

| Table A-3  | ESD and Latch-Up Protection Characteristics        | 108 |

| Table A-4  | Operating Conditions                               | 109 |

| Table A-5  | Thermal Package Characteristics                    | 111 |

| Table A-6  | 5V I/O Characteristics                             | 112 |

| Table A-7  | Preliminary 3.3V I/O Characteristics               | 113 |

| Table A-8  | Supply Current Characteristics                     | 115 |

| Table 20-2 | VREG_3V3 - Operating Conditions                    | 117 |

| Table B-1  | Voltage Regulator - Capacitive Loads               | 119 |

| Table B-2  | Startup Characteristics                            | 121 |

| Table B-3  | Oscillator Characteristics                         | 123 |

| Table B-4  | PLL Characteristics                                | 127 |

| Table B-5  | NVM Timing Characteristics                         | 130 |

| Table B-6  | NVM Reliability Characteristics                    | 131 |

| Table B-7  | Measurement Conditions                             | 133 |

| Table B-8  | SPI Master Mode Timing Characteristics             | 134 |

| Table B-9  | SPI Slave Mode Timing Characteristics              | 136 |

#### Device User Guide — 9S12E128DGV1/D V01.04

| Table B-10 | 5V ATD Operating Characteristics                 | 139 |

|------------|--------------------------------------------------|-----|

| Table B-11 | 3.3V ATD Operating Characteristics               | 140 |

| Table B-12 | ATD Electrical Characteristics                   | 141 |

| Table B-14 | 3.3V ATD Conversion Performance                  | 142 |

| Table B-13 | 5V ATD Conversion Performance                    | 142 |

| Table B-15 | DAC Electrical Characteristics (Operating)       | 145 |

| Table B-16 | DAC Timing/Performance Characteristics           | 145 |

| Table C-1  | Expanded Bus Timing Characteristics (5V Range)   | 149 |

| Table C-2  | Expanded Bus Timing Characteristics (3.3V Range) | 151 |

# **Preface**

The Device User Guide provides information about the MC9S12E-Family devices made up of standard HCS12 blocks and the HCS12 processor core. This document is part of the customer documentation. A complete set of device manuals also includes all the individual Block Guides of the implemented modules. In a effort to reduce redundancy, all module specific information is located only in the respective Block Guide. If applicable, special implementation details of the module are given in the block description sections of this document.

See **Table 0-1** for names and versions of the referenced documents throughout the Device User Guide.

**Table 0-1 Document References**

| Block Guide                                                           | E256<br>Version | E128, E64<br>Version | E32<br>Version | Document Order<br>Number      |

|-----------------------------------------------------------------------|-----------------|----------------------|----------------|-------------------------------|

| CPU12 Reference Manual                                                | V02             | V02                  | V02            | S12CPUV2/D                    |

| HCS12 Background Debug (BDM)                                          | V04             | V04                  | V04            | S12BDMV4/D                    |

| HCS12 Debug (DBG)                                                     | V01             | V01                  | V01            | S12DBGV1/D                    |

| HCS12 Interrupt (INT)                                                 | V01             | V01                  | V01            | S12INTV1/D                    |

| HCS12 Multiplexed Expanded Bus Interface (MEBI)                       | V03             | V03                  | V03            | S12MEBIV3/D                   |

| HCS12 Module Mapping Control (MMC)                                    | V04             | V04                  | V04            | S12MMCV4/D                    |

| Analog to Digital Converter: 10-Bit, 16 Channels (ATD_10B16C)         | V04             | V02                  | V04            | S12ATD10B16CVx/D <sup>1</sup> |

| Clock and Reset Generator (CRG)                                       | V04             | V04                  | V04            | S12CRGV4/D                    |

| Digital to Analog Converter: 8-Bit, 1 Channel (DAC_8B1C)              | V01             | V01                  | V01            | S12DAC8B1CV1/D                |

| 256Kbyte Flash EEPROM (FTS256K2)                                      | V01             | N/A                  | N/A            | S12FTS256K2V1/D               |

| 128Kbyte Flash EEPROM (FTS128K1)                                      | N/A             | V01                  | N/A            | S12FTS128K1V1/D               |

| 32Kbyte Flash EEPROM (FTS32K)                                         | N/A             | N/A                  | V02            | S12FTS32KV2/D                 |

| Inter IC Bus (IIC)                                                    | V02             | V02                  | V02            | S12IICV2/D                    |

| Oscillator (OSC)                                                      | V02             | V02                  | V02            | S12OSCV2/D                    |

| Port Integration Module (PIM_9E128)                                   | V01             | V01                  | V01            | S12PIM9E128V1/D               |

| Pulse Modulator with Fault Protection: 15-Bit, 6 Channels (PMF_15B6C) | V02             | V02                  | V02            | S12PMF15B6CV2/D               |

| Pulse Width Modulator: 8-Bit, 6 Channels (PWM_8B6C)                   | V01             | V01                  | V01            | S12PWM8B6CV1/D                |

| Serial Communications Interface (SCI)                                 | V04             | V03                  | V04            | S12SCIVy/D <sup>2</sup>       |

| Serial Peripheral Interface (SPI)                                     | V03             | V03                  | V03            | S12SPIV3/D                    |

| Timer: 16-Bit, 4 Channels (TIM_16B4C)                                 | V01             | V01                  | V01            | S12TIM16B4CV1/D               |

| Voltage Regulator (VREG_3V3)                                          | V02             | V02                  | V02            | S12VREG3V3V2/D                |

#### NOTES:

<sup>1.</sup> x in S12ATD10B16CVx/D is 2 for E64 and E128, and 4 for E32 and E256.

<sup>2.</sup> y in S12SCIVy/D is 3 for E64 and E128, and 4 for E32 and E256.

# **Part Number**

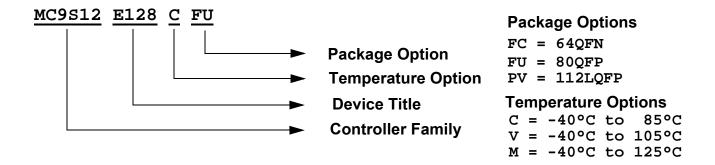

**Figure 0-1** provides an ordering number example.

Figure 0-1 Order Part Number Coding

**Table 0-2** lists the part number coding based on the package and temperature.

**Table 0-2 Part Number Coding**

| Part Number   | Temp.        | Package | Description |

|---------------|--------------|---------|-------------|

| MC9S12E256CFU | -40°C, 85°C  | 80QFP   | MC9S12E256  |

| MC9S12E256CPV | -40°C, 85°C  | 112LQFP | MC9S12E256  |

| MC9S12E256MFU | -40°C, 125°C | 80QFP   | MC9S12E256  |

| MC9S12E256MPV | -40°C, 125°C | 112LQFP | MC9S12E256  |

| MC9S12E128CFU | -40°C, 85°C  | 80QFP   | MC9S12E128  |

| MC9S12E128CPV | -40°C, 85°C  | 112LQFP | MC9S12E128  |

| MC9S12E128MFU | -40°C, 125°C | 80QFP   | MC9S12E128  |

| MC9S12E128MPV | -40°C, 125°C | 112LQFP | MC9S12E128  |

| MC9S12E64CFU  | -40°C, 85°C  | 80QFP   | MC9S12E64   |

| MC9S12E64CPV  | -40°C, 85°C  | 112LQFP | MC9S12E64   |

| MC9S12E64MFU  | -40°C, 125°C | 80QFP   | MC9S12E64   |

| MC9S12E64MPV  | -40°C, 125°C | 112LQFP | MC9S12E64   |

| MC9S12E32CFU  | -40°C, 85°C  | 80QFP   | MC9S12E32   |

| MC9S12E32MFU  | -40°C, 125°C | 80QFP   | MC9S12E32   |

**Table 0-3** summarizes the package option and size configuration.

**Table 0-3 Package Option Summary**

| Package | Device     | Part Number | Temp. <sup>1</sup><br>Options | Flash | RAM  | I/O <sup>2</sup> |

|---------|------------|-------------|-------------------------------|-------|------|------------------|

| 80QFP   | MC9S12E256 | MC9S12E256  | M, C                          | 256K  | 16K  | 60               |

| 112LQFP | MC9S12E256 | MC9S12E256  | M, C                          | 25010 | 1010 | 92               |

| 80QFP   | MC9S12E128 | MC9S12E128  | M, C                          | 128K  | 8K   | 60               |

| 112LQFP | MC9S12E128 | MC9S12E128  | M, C                          | 1201  | OIX  | 92               |

| 80QFP   | MC9S12E64  | MC9S12E64   | M, C                          | 64K   | 4K   | 60               |

| 112LQFP | MC9S12E64  | MC9S12E64   | M, C                          | 0411  | 711  | 92               |

| 64QFN   | MC9S12E32  | MC9S12E32   | M, C                          | 32K   | 2K   | 44               |

| 80QFP   | MC9S12E32  | MC9S12E32   | M, C                          | 52K   | ۷۱۸  | 60               |

#### NOTES:

- 1. C: T<sub>A</sub> = 85 C, f = 25MHz. M: T<sub>A</sub>= 125 C, f = 25MHz

- 2. I/O is the sum of ports capable to act as digital input or output.

Table 0-4 List of MC9S12E-Family members

| Device | Flash | RAM  | Package  | MEBI | TIM | SCI | SPI | IIC | A/D | D/A | PWM | PMF | KWU | I/O |

|--------|-------|------|----------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| E256   | 256K  | 16K  | 112 LQFP | 1    | 12  | 3   | 1   | 1   | 16  | 2   | 6   | 6   | 16  | 92  |

| E230   | 230K  | 1010 | 80 QFP   | 0    | 1.2 | 3   | 1   | 1   | 10  | 2   | 0   | 0   | 10  | 60  |

| E128   | 128K  | 8K   | 112 LQFP | 1    | 12  | 3   | 1   | 1   | 16  | 2.  | 6   | 6   | 16  | 92  |

| E126   | 120K  | oK   | 80 QFP   | 0    | 12  | 3   | 1   | 1   | 10  | 2   | 6   | U   | 10  | 60  |

| E64    | 64K   | 4K   | 112 LQFP | 1    | 12  | 3   | 1   | 1   | 16  | 2   | 6   | 6   | 16  | 92  |

| E04    | 04K   | 410  | 80 QFP   | 0    | 12  | 3   | 1   | 1   | 10  | 2   | 6   | U   | 10  | 60  |

| E32    | 32K   | 2K   | 80 QFP   | 0    | 8   | 2   | 1   | 1   | 16  | 2   | 0   | 6   | 16  | 60  |

#### • Pin out explanations:

- TIM is the number of channels.

- A/D is the number of A/D channels.

- D/A is the number of D/A channels.

- PWM is the number of channels.

- PMF is the number of channels.

- KWU is the number of key wake up interrupt pins.

- I/O is the sum of ports capable to act as digital input or output.

- 112 Pin Packages:

18 inputs provide Interrupt capability (AD = 16, IRQ, XIRQ)

80 Pin Packages:

$$E = 2 + 2$$

input only,  $M = 7$ ,  $P = 6$ ,  $Q = 7$ ,

$$S = 8$$

,  $T = 8$ ,  $U = 4$ ,  $AD = 16$ .

18 inputs provide Interrupt capability (AD = 16, IRQ, XIRQ)

- Versions with 3 SCI modules will have SCI0, SCI1 and SCI2.

- Versions with 2 SCI modules will have SCI0 and SCI1.

- Versions with 3 TIM modules will have TIM0, TIM1 and TIM2.

- Versions with 2 TIM modules will have TIM0 and TIM1.

# **Section 1 Introduction**

#### 1.1 Overview

The MC9S12E-Family is a 112/80 pin low cost general purpose MCU family. All members of the MC9S12E-Family are comprised of standard on-chip peripherals including a 16-bit central processing unit (HCS12 CPU), up to 256K bytes of Flash EEPROM, up to 16K bytes of RAM, three asynchronous serial communications interface modules (SCI), a serial peripheral interface (SPI), an Inter-IC Bus (IIC), three 4-channel 16-bit timer modules (TIM), a 6-channel 15-bit Pulse Modulator with Fault protection module (PMF), a 6-channel 8-bit Pulse Width Modulator (PWM), a 16-channel 10-bit analog-to-digital converter (ADC), and two 1-channel 8-bit digital-to-analog converters (DAC). The MC9S12E-Family has full 16-bit data paths throughout. The inclusion of a PLL circuit allows power consumption and performance to be adjusted to suit operational requirements. In addition to the I/O ports available on each module, 16 dedicated I/O port bits are available with Wake-Up capability from STOP or WAIT mode. Furthermore, an on chip bandgap based voltage regulator (VREG) generates the internal digital supply voltage of 2.5V (VDD) from a 3.135V to 5.5V external supply range.

#### 1.2 Features

- 16-bit HCS12 CORE

- HCS12 CPU

- i. Upward compatible with M68HC11 instruction set

- ii. Interrupt stacking and programmer's model identical to M68HC11

- iii. Instruction queue

- iv. Enhanced indexed addressing

- Module Mapping Control (MMC)

- Interrupt Control (INT)

- Background Debug Module (BDM)

- Debugger (DBG12) including breakpoints and change-of-flow trace buffer

- Multiplexed External Bus Interface (MEBI)

- Wake-Up interrupt inputs

- Up to 16 port bits available for wake up interrupt function with digital filtering

- Memory options

- 32K, 64K, 128K or 256K Byte Flash EEPROM

- 2K, 4K, 8K or 16K Byte RAM

- Two 1-channel Digital-to-Analog Converters (DAC)

- 8-bit resolution

#### Device User Guide — 9S12E128DGV1/D V01.04

- Analog-to-Digital Converter (ADC)

- 16-channel module with 10-bit resolution

- External conversion trigger capability

- Three 4-channel Timers (TIM)

- Programmable input capture or output compare channels

- Simple PWM mode

- Counter Modulo Reset

- External Event Counting

- Gated Time Accumulation

- 6 PWM channels (PWM)

- Programmable period and duty cycle

- 8-bit 6-channel or 16-bit 3-channel

- Separate control for each pulse width and duty cycle

- Center-aligned or left-aligned outputs

- Programmable clock select logic with a wide range of frequencies

- Fast emergency shutdown input

- 6-channel Pulse width Modulator with Fault protection (PMF)

- Three independent 15-bit counters with synchronous mode

- Complementary channel operation

- Edge and center aligned PWM signals

- Programmable dead time insertion

- Integral reload rates from 1 to 16

- Four fault protection shut down input pins

- Three current sense input pins

- Serial interfaces

- Three asynchronous serial communication interfaces (SCI)

- Synchronous serial peripheral interface (SPI)

- Inter-IC Bus (IIC)

- Clock and Reset Generator (CRG)

- Windowed COP watchdog

- Real Time interrupt

- Clock Monitor

- Pierce or low current Colpitts oscillator

- Phase-locked loop clock frequency multiplier

- Self Clock mode in absence of external clock

- Low power 0.5 to 16Mhz crystal oscillator reference clock

- Operating frequency

- 50MHz equivalent to 25MHz Bus Speed

- Internal 2.5V Regulator

- Input voltage range from 3.135V to 5.5V

- Low power mode capability

- Includes low voltage reset (LVR) circuitry

- Includes low voltage interrupt (LVI) circuitry

- 112-Pin LQFP or 80-Pin QFP package

- Up to 90 I/O lines with 5V input and drive capability (112 pin package)

- Up to two dedicated 5V input only lines (IRQ and XIRQ)

- Sixteen 3.3V/5V A/D converter inputs

- Development Support.

- Single-wire background debug<sup>TM</sup> mode

- On-chip hardware breakpoints

- Enhanced debug features

# 1.3 Modes of Operation

User modes (Expanded modes are only available in the 112 pin package version)

- Normal modes

- Normal Single-Chip Mode

- Normal Expanded Wide Mode

- Normal Expanded Narrow Mode

- Emulation Expanded Wide Mode

- Emulation Expanded Narrow Mode

- Special Operating Modes

- Special Single-Chip Mode with active Background Debug Mode

- Special Test Mode (Motorola use only)

- Special Peripheral Mode (Motorola use only)

#### Device User Guide — 9S12E128DGV1/D V01.04

- Low power modes

- Stop Mode

- Pseudo Stop Mode

- Wait Mode

# 1.4 Block Diagram

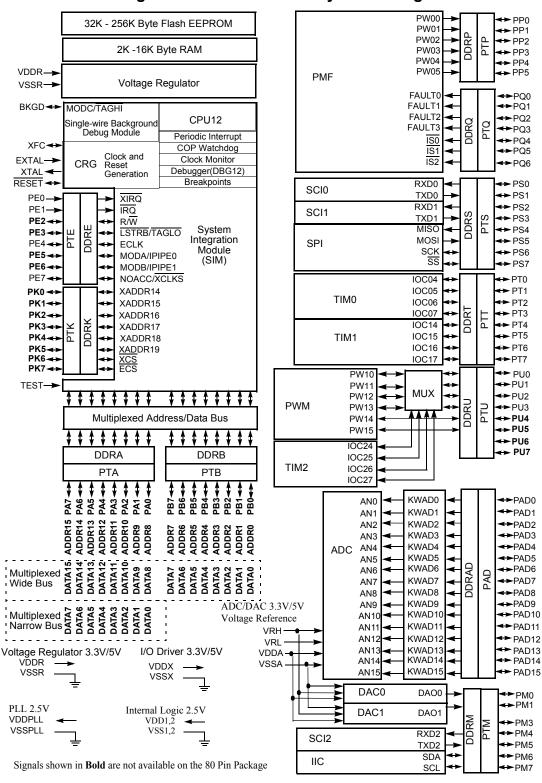

Figure 1-1 MC9S12E-Family Block Diagram

# 1.5 Device Memory Map

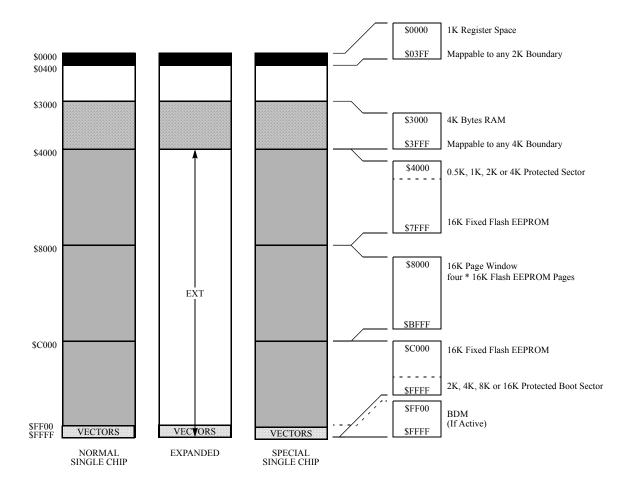

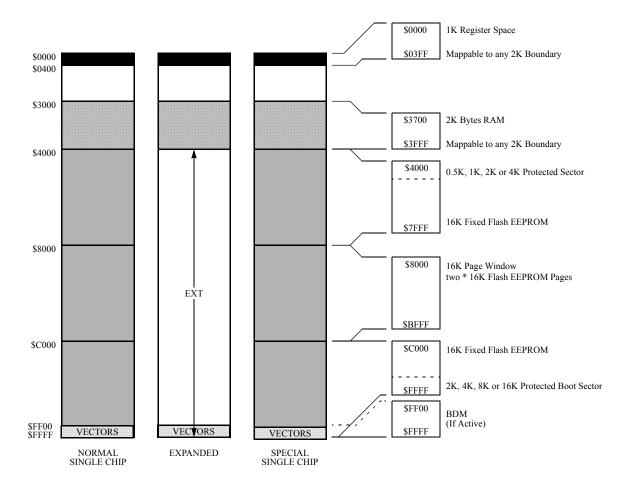

**Table 1-1** shows the device register map of the MC9S12E-Family after reset. The following figures (, **Figure 1-3**, and **Figure 1-4**) illustrate the full device memory map with Flash and RAM.

Table 1-1 Device Register Map Overview

| Address       | Module                                                   | Size |

|---------------|----------------------------------------------------------|------|

| \$000 - \$017 | CORE (Ports A, B, E, Modes, Inits, Test)                 | 24   |

| \$018         | Reserved                                                 | 1    |

| \$019         | Voltage Regulator (VREG)                                 | 1    |

| \$01A - \$01B | Device ID register (PARTID)                              | 2    |

| \$01C - \$01F | CORE (MEMSIZ, IRQ, HPRIO)                                | 4    |

| \$020 - \$02F | CORE (DBG)                                               | 16   |

| \$030 - \$033 | CORE (PPAGE, Port K)                                     | 4    |

| \$034 - \$03F | Clock and Reset Generator (PLL, RTI, COP)                | 12   |

| \$040 - \$06F | Standard Timer 16-bit 4 channels (TIM0)                  | 48   |

| \$070 - \$07F | Reserved                                                 | 16   |

| \$080 - \$0AF | Analog to Digital Converter 10-bit 16 channels (ATD)     | 48   |

| \$0B0 - \$0C7 | Reserved                                                 | 24   |

| \$0C8 - \$0CF | Serial Communications Interface 0 (SCI0)                 | 8    |

| \$0D0 - \$0D7 | Serial Communications Interface 1 (SCI1)                 | 8    |

| \$0D8 - \$0DF | Serial Peripheral Interface (SPI)                        | 8    |

| \$0E0 - \$0E7 | Inter IC Bus                                             | 8    |

| \$0E8 - \$0EF | Serial Communications Interface 2 (SCI2)                 | 8    |

| \$0F0 - \$0F3 | Digital to Analog Converter 8-bit 1-channel (DAC0)       | 4    |

| \$0F4 - \$0F7 | Digital to Analog Converter 8-bit 1-channel (DAC1)       | 4    |

| \$0F8 - \$0FF | Reserved                                                 | 8    |

| \$100- \$10F  | Flash Control Register                                   | 16   |

| \$110 - \$13F | Reserved                                                 | 48   |

| \$140 - \$16F | Standard Timer 16-bit 4 channels (TIM1)                  | 48   |

| \$170 - \$17F | Reserved                                                 | 16   |

| \$180 - \$1AF | Standard Timer 16-bit 4 channels (TIM2)                  | 48   |

| \$1B0 - \$1DF | Reserved                                                 | 48   |

| \$1E0 - \$1FF | Pulse Width Modulator 8-bit 6 channels (PWM)             | 32   |

| \$200 - \$23F | Pulse Width Modulator with Fault 15-bit 6 channels (PMF) | 64   |

| \$240 - \$27F | Port Integration Module (PIM)                            | 64   |

| \$280 - \$3FF | Reserved                                                 | 384  |

\$0000 - \$03FF: Register Space \$0000 - \$3FFF: 16K RAM (only 15K RAM visible \$0400 - \$3FFF)

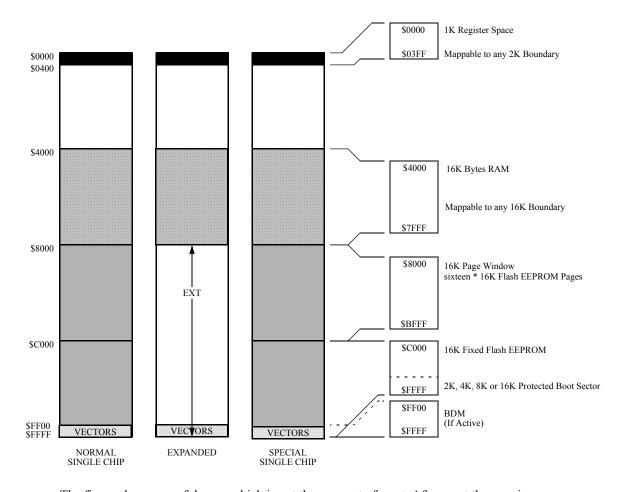

Figure 1-2 MC9S12E256 User Configurable Memory Map

\$0000 - \$03FF: Register Space \$0000 - \$1FFF: 8K RAM (only 7K RAM visible \$0400 - \$1FFF)

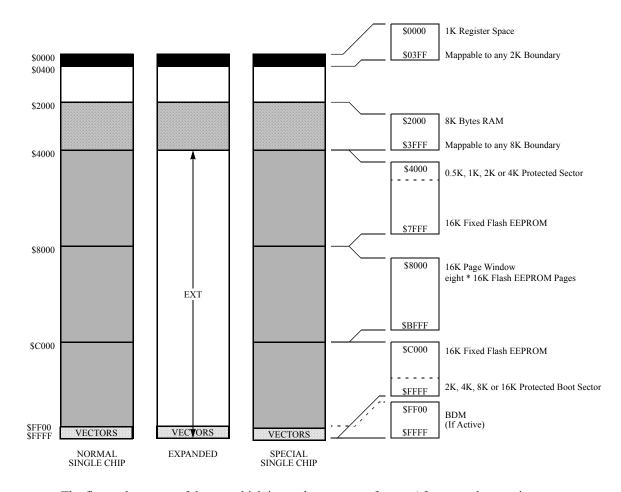

Figure 1-3 MC9S12E128 User Configurable Memory Map

\$0000 - \$03FF: Register Space \$0000 - \$0FFF: 4K RAM (only 3K RAM visible \$0400 - \$0FFF)

Figure 1-4 MC9S12E64 User Configurable Memory Map

\$0000 - \$03FF: Register Space \$0000 - \$07FF: 2K RAM (only 1K RAM visible \$0400 - \$07FF)

Figure 1-5 MC9S12E32 User configurable Memory Map

# 1.6 Detailed Register Map

The detailed register map of the MC9S12E-Family is listed in address order below. For detailed information about register function please refer to the appropriate block guide.

### \$0000 - \$000F

# MEBI map 1 of 3 (HCS12 Multiplexed External Bus Interface)

| Addres<br>s   | Name     |                    | Bit 7      | Bit 6 | Bit 5                                 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|----------|--------------------|------------|-------|---------------------------------------|-------|-------|-------|-------|-------|

|               | DODTA    | Read<br>:          | Dit 7      | 6     | 5                                     | 4     | 3     | c     | 1     | Dit 0 |

| \$0000        | PORTA    | Write<br>:         | Bit 7      | b     | 5                                     | 4     | ა     | 2     | 1     | Bit 0 |

| \$0001        | PORTB    | Read<br>:          | Bit 7      | 9     | 5                                     | 4     | 3     | 2     | 1     | Bit 0 |

| φοσοι         | TORTE    | Write<br>:         |            |       | , , , , , , , , , , , , , , , , , , , | т<br> | J     |       | '     | Dit 0 |

| \$0002        | DDRA     | Read<br>:          | Bit 7      | 6     | 5                                     | 4     | 3     | 2     | 1     | Bit 0 |

| Ψ0002         | 22.01    | Write<br>:         |            |       |                                       |       |       | _     | •     |       |

| \$0003        | DDRB     | Read<br>:          | Bit 7      | 6     | 5                                     | 4     | 3     | 2     | 1     | Bit 0 |

| <b>4</b> 0000 | 22.12    | Write :            |            |       |                                       | •     |       | _     | •     |       |

| \$0004        | Reserved | Read<br>:          | 0          | 0     | 0                                     | 0     | 0     | 0     | 0     | 0     |

| ,             |          | Write<br>:         |            |       |                                       |       |       |       |       |       |

| \$0005        | Reserved | Read :             | 0          | 0     | 0                                     | 0     | 0     | 0     | 0     | 0     |

| ·             |          | Write :            |            |       |                                       |       |       |       |       |       |

| \$0006        | Reserved | Read :             | 0          | 0     | 0                                     | 0     | 0     | 0     | 0     | 0     |

| ·             |          | Write :            |            |       |                                       |       |       |       |       |       |

| \$0007        | Reserved | Read :             | 0          | 0     | 0                                     | 0     | 0     | 0     | 0     | 0     |

|               |          | Write :            |            |       |                                       |       |       |       |       |       |

| \$0008        | PORTE    | Read<br>:          | Bit 7      | 6     | 5                                     | 4     | 3     | 2     | Bit 1 | Bit 0 |

|               |          | Write :            |            |       |                                       |       |       |       |       |       |

| \$0009        | DDRE     | Read :             | Bit 7      | 6     | 5                                     | 4     | 3     | Bit 2 | 0     | 0     |

|               |          | Write<br>:         |            |       |                                       |       |       |       |       |       |

| \$000A        | PEAR     | Read<br>:<br>Write | NOACC<br>E | 0     | PIPOE                                 | NECLK | LSTRE | RDWE  | 0     | 0     |

|               |          | vviile<br>:        | C          |       |                                       |       |       |       |       |       |

### \$0000 - \$000F

# MEBI map 1 of 3 (HCS12 Multiplexed External Bus Interface)

| \$000B | MODE      | Read<br>:  | MODC  | MODB | MODA   | 0     | IVIS | 0 | EMK     | EME   |

|--------|-----------|------------|-------|------|--------|-------|------|---|---------|-------|

| ФОООВ  | MIODE     | Write<br>: | MODC  | MODB | IVIODA |       | 1010 |   | EIVIK   | EIVIE |

| \$000C | PUCR      | Read<br>:  | PUPKE | 0    | 0      | PUPEE | 0    | 0 | PUPBE   | PUPAE |

| ψοσος  | TOOK      | Write<br>: | TOTAL |      |        | TOTEL |      |   | T OI BE | TOTAL |

| \$000D | RDRIV     | Read<br>:  | RDPK  | 0    | 0      | RDPE  | 0    | 0 | RDPB    | RDPA  |

| ΨΟΟΟΣ  | TOTAL V   | Write<br>: | NDI K |      |        | NDI L |      |   | NOI D   |       |

| \$000E | EBICTL    | Read<br>:  | 0     | 0    | 0      | 0     | 0    | 0 | 0       | ESTR  |

| Ψ000Ε  | 25.012    | Write<br>: |       |      |        |       |      |   |         |       |

| \$000F | Reserved  | Read<br>:  | 0     | 0    | 0      | 0     | 0    | 0 | 0       | 0     |

| ΨΟΟΟΙ  | 110001700 | Write<br>: |       |      |        |       |      |   |         |       |

### \$0010 - \$0014

# MMC map 1 of 4 (HCS12 Module Mapping Control)

| Addres<br>s   | Name      |            | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3    | Bit 2  | Bit 1       | Bit 0 |

|---------------|-----------|------------|---------|--------|--------|--------|----------|--------|-------------|-------|

| \$0010        | INITRM    | Read<br>:  | RAM15   | RAM14  | RAM13  | RAM12  | RAM11    | 0      | 0           | RAMHA |

| φοστο         | HALLIXIVI | Write<br>: | TVAINTS | IVANIT | TAMITS | TANTZ  | TVAIVITI |        |             | L     |

| \$0011        | INITRG    | Read<br>:  | 0       | REG14  | REG13  | REG12  | REG11    | 0      | 0           | 0     |

| φοστι         | IIIIIII   | Write<br>: |         | NLO14  | NLO13  | NLO 12 | KLOTI    |        |             |       |

| \$0012        | INITEE    | Read<br>:  | EE15    | EE14   | EE13   | EE12   | EE11     | 0      | 0           | EEON  |

| φ0012         | INITEL    | Write<br>: |         |        |        | LLIZ   |          |        |             | LLON  |

| \$0013        | MISC      | Read<br>:  | 0       | 0      | 0      | 0      | EVQTD1   | EVSTDO | ROMHM       | POMON |

| φ0013         | MIGC      | Write<br>: |         |        |        |        | LAGIRI   | LXSTRU | NOIVII IIVI | ROWON |

| £001 <i>4</i> | MTST0     | Read<br>:  | Bit 7   | 6      | 5      | 4      | 3        | 2      | 1           | Bit 0 |

| \$0014        | WITSTO    | Write<br>: |         |        |        |        |          |        |             |       |

#### \$0015 - \$0016

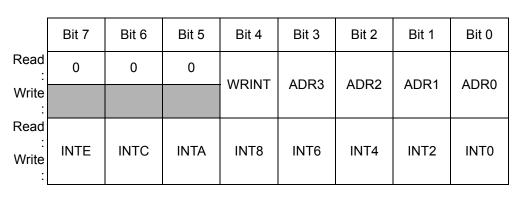

#### INT map 1 of 2 (HCS12 Interrupt)

| Addres<br>s | Name  |

|-------------|-------|

| \$0015      | ITCR  |

| \$0016      | ITEST |

#### \$0017 - \$0017

#### MMC map 2 of 4 (HCS12 Module Mapping Control)

| Addres | Name |

|--------|------|

| S      | Name |

\$0017 MTST1

|            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read<br>:  | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| Write<br>: |       |       |       |       |       |       |       |       |

\$0018 - \$0018

Addres Name

\$0018 Reserved

| Miscell | aneous | Periphe | erals (Do | evice U | ser G | uide) |

|---------|--------|---------|-----------|---------|-------|-------|

|         |        |         |           |         |       |       |

|            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read<br>:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Write<br>: |       |       |       |       |       |       |       |       |

\$0019 - \$0019

Addres Name

\$0019 VREGCTRL

### **VREG3V3 (Voltage Regulator)**

|           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read<br>: | 0     | 0     | 0     | 0     | 0     | LVDS  | LVIE  | LVIF  |

| Write :   |       |       |       |       |       |       | LVIE  | LVII  |

#### \$001A - \$001B

#### **Miscellaneous Peripherals (Device User Guide)**

| Addres<br>s | Name    |            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|---------|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$001A      | PARTIDH | Read<br>:  | ID15  | ID14  | ID13  | ID12  | ID11  | ID10  | ID9   | ID8   |

| Ф00 IA      | PARTIDH | Write<br>: |       |       |       |       |       |       |       |       |

| \$001B      | PARTIDL | Read<br>:  | ID7   | ID6   | ID5   | ID4   | ID3   | ID2   | ID1   | ID0   |

| φ001Β       | PARTIDE | Write<br>: |       |       |       |       |       |       |       |       |

# \$001C - \$001D User Guide)

# MMC map 3 of 4 (HCS12 Module Mapping Control, Device

| Addres<br>s | Name      |            | Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3 | Bit 2       | Bit 1       | Bit 0       |

|-------------|-----------|------------|-------------|-------------|-------------|-------------|-------|-------------|-------------|-------------|

| \$001C      | MEMSIZ0   | Read<br>:  | reg_sw0     | 0           | eep_sw<br>1 | eep_sw<br>0 | 0     | ram_sw<br>2 | ram_sw<br>1 | ram_sw<br>0 |

| \$00 IC     | MEMSIZU   | Write<br>: |             |             |             |             |       |             |             |             |

| \$001D      | MEMSIZ1   | Read<br>:  | rom_sw<br>1 | rom_sw<br>0 | 0           | 0           | 0     | 0           | pag_sw<br>1 | pag_sw<br>0 |

| φυστυ       | WILWISIZI | Write<br>: |             |             |             |             |       |             |             |             |

#### \$001E - \$001E

# MEBI map 2 of 3 (HCS12 Multiplexed External Bus Interface)

| Addres<br>s | Name  |            | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|------------|-------|--------|-------|-------|-------|-------|-------|-------|

| \$001E      | INTCR | Read<br>:  | IRQE  | IRQEN  | 0     | 0     | 0     | 0     | 0     | 0     |

| φ001E       | INTOR | Write<br>: | INQL  | INQLIN |       |       |       |       |       |       |

#### \$001F - \$001F

# INT map 2 of 2 (HCS12 Interrupt)

| \$001F HPRIO : PSEL7 PSEL6 PSEL5 PSEL4 PSE | EL3 PSEL2 | PSEL1 | 0 |

|--------------------------------------------|-----------|-------|---|

#### \$0020 - \$002F

# DBG (including BKP) map 1of 1 (HCS12 Debug)

| A ddroo     |                 |               |        |        |        |        | 1      |        |       |       |  |

|-------------|-----------------|---------------|--------|--------|--------|--------|--------|--------|-------|-------|--|

| Addres<br>s | Name            |               | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |  |

| \$0020      | DBGC1<br>-      | read<br>write | DBGEN  | ARM    | TRGSEL | BEGIN  | DBGBRK | 0      | CAPI  | MOD   |  |

| <b></b>     | DBGSC           | read          | AF     | BF     | CF     | 0      | TDC    |        |       |       |  |

| \$0021      | -               | write         |        |        |        |        |        | 11     | TRG   |       |  |

| \$0022      | DBGTBH          | read          | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |  |

| ψ00ZZ       | -               | write         |        |        |        |        |        |        |       |       |  |

| \$0023      | DBGTBL          | read          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |  |

| Ψ0020       | -               | write         |        | _      |        |        |        |        |       |       |  |

| \$0024      | DBGCNT          | read          | TBF    | 0      |        |        | CN     | NT .   |       |       |  |

|             | -<br>DBCCCV     | write         |        |        |        |        |        |        |       |       |  |

| \$0025      | DBGCCX<br>-     | read<br>write | PAG    | SEL    |        |        | EXT    | CMP    |       |       |  |

|             | DBGCCH          | read          |        |        |        |        |        |        |       |       |  |

| \$0026      | DD00011         | write         | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9     | Bit 8 |  |

| \$0027      | DBGCCL<br>-     | read<br>write | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1     | Bit 0 |  |

| \$0028      | DBGC2<br>BKPCT0 | read<br>write | BKABEN | FULL   | BDM    | TAGAB  | BKCEN  | TAGC   | RWCEN | RWC   |  |

| \$0029      | DBGC3<br>BKPCT1 | read<br>write | ВКАМВН | BKAMBL | ВКВМВН | BKBMBL | RWAEN  | RWA    | RWBEN | RWB   |  |

| \$002A      | DBGCAX<br>BKP0X | read<br>write | PAG    | SEL    |        |        | EXT    | CMP    |       |       |  |

| \$002B      | DBGCAH<br>BKP0H | read<br>write | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9     | Bit 8 |  |

| \$002C      | DBGCAL<br>BKP0L | read<br>write | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1     | Bit 0 |  |

| \$002D      | DBGCBX<br>BKP1X | read<br>write | PAG    | SEL    | EXTCMP |        |        |        |       |       |  |

| \$002E      | DBGCBH<br>BKP1H | read<br>write | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9     | Bit 8 |  |

| \$002F      | DBGCBL<br>BKP1L | read<br>write | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1     | Bit 0 |  |

### \$0030 - \$0031

# MMC map 4 of 4 (HCS12 Module Mapping Control)

| Addres<br>s | Name     |            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0 |

|-------------|----------|------------|-------|-------|-------|-------|--------|--------|--------|-------|

| \$0030      | PPAGE    | Read<br>:  | U     | 0     | PIX5  | PIX4  | PIX3   | PIX2   | PIX1   | PIX0  |

| \$0030      | PPAGE    | Write<br>: |       |       | PIAS  | 1 174 | 1 1/10 | 1 1/12 | 1 17(1 | 1 170 |

| \$0031      | Reserved | Read<br>:  | 0     | 0     | 0     | 0     | 0      | 0      | 0      | 0     |

| φυσι        | Reserved | Write<br>: |       |       |       |       |        |        |        |       |

#### \$0032 - \$0033

# MEBI map 3 of 3 (HCS12 Multiplexed External Bus Interface)

| Addres<br>s | Name  |                         | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$0032      | PORTK | Read<br>:<br>Write<br>: | ECS   | xcs   | XAB19 | XAB18 | XAB17 | XAB16 | XAB15 | XAB14 |

| \$0033      | DDRK  | Read<br>:<br>Write<br>: | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

#### \$0034 - \$003F

# **CRG (Clock and Reset Generator)**

|             |           | 1          |        |       | 1      |            | 1          |            | •          |            |

|-------------|-----------|------------|--------|-------|--------|------------|------------|------------|------------|------------|

| Addres<br>s | Name      |            | Bit 7  | Bit 6 | Bit 5  | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      |

|             |           | Read :     | 0      | 0     |        |            |            |            |            |            |

| \$0034      | SYNR      | Write      |        |       | SYN5   | SYN4       | SYN3       | SYN2       | SYN1       | SYN0       |

|             |           | Read       | 0      | 0     | 0      | 0          | DEED) (    | DEED) /    | DEEDV      | DEEDV      |

| \$0035      | REFDV     | Write :    |        |       |        |            | REFDV<br>3 | REFDV<br>2 | REFDV<br>1 | REFDV<br>0 |

|             | CTFLG     | Read<br>:  | TOUT7  | TOUT6 | TOUT5  | TOUT4      | TOUT3      | TOUT2      | TOUT1      | TOUT0      |

| \$0036      | TEST ONLY | Write      |        |       |        |            |            |            |            |            |

|             |           | Read       |        |       | 0      |            | LOCK       | TRACK      |            | SCM        |

| \$0037      | CRGFLG    | Write      | RTIF   | PROF  |        | LOCKIF     |            |            | SCMIF      |            |

|             |           | Read       |        | 0     | 0      |            | 0          | 0          |            | 0          |

| \$0038      | CRGINT    | :<br>Write | RTIE   |       |        | LOCKIE     |            |            | SCMIE      |            |

|             |           | :<br>Read  |        |       |        |            |            |            |            |            |

| \$0039      | CLKSEL    | :<br>Write | PLLSEL | PSTP  | SYSWAI | ROAWA<br>I | PLLWAI     | CWAI       | RTIWAI     | COPWA<br>I |

|             |           | :<br>Read  |        |       |        |            | 0          |            |            |            |

| \$003A      | PLLCTL    | :<br>Write | CME    | PLLON | AUTO   | ACQ        | U          | PRE        | PCE        | SCME       |

|             |           | :<br>Read  |        |       |        |            |            |            |            |            |

| \$003B      | RTICTL    | :          | 0      | RTR6  | RTR5   | RTR4       | RTR3       | RTR2       | RTR1       | RTR0       |

|             |           | Write<br>: |        |       |        |            |            |            |            |            |

# \$0034 - \$003F

# **CRG (Clock and Reset Generator)**

| Addres<br>s | Name                |                         | Bit 7      | Bit 6   | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|---------------------|-------------------------|------------|---------|-------|--------|-------|-------|-------|-------|

| \$003C      | COPCTL              | Read<br>:               |            | RSBCK - | 0     | 0      | 0     | CR2   | CR1   | CR0   |

|             |                     | Write<br>:              |            |         |       |        |       | 0112  |       |       |

| \$003D      | FORBYP<br>TEST ONLY | Read<br>:<br>Write<br>: | RTIRYP     | COPBY   | 0     | PLLBYP | BYP 0 | 0     | - FCM | 0     |

|             |                     |                         |            | Р       |       | PLLDIF |       |       |       |       |

| \$003E      | CTCTL<br>TEST ONLY  | Read<br>:               | TCTL7      | TCTL6   | TCTL5 | TCTL4  | TCLT3 | TCTL2 | TCTL1 | TCTL0 |

|             |                     | Write :                 |            |         |       |        |       |       |       |       |

| \$003F      | ARMCOP              | Read :                  | 0          | 0       | 0     | 0      | 0     | 0     | 0     | 0     |

|             |                     | ARMCOP Write            | Write<br>: | Bit 7   | 6     | 5      | 4     | 3     | 2     | 1     |

### \$0040 - \$006F

| Addres<br>s | Name      |            | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-----------|------------|--------|-------|-------|--------|-------|-------|-------|-------|

| \$0040      |           | Read<br>:  | : 1087 | IOS6  | IOS5  | IOS4   | 0     | 0     | 0     | 0     |

|             | TIOS      | Write<br>: |        |       |       |        |       |       |       |       |

| \$0041      | CFORC     | Read<br>:  | 0      | 0     | 0     | 0      | 0     | 0     | 0     | 0     |

| ΨΟΟΨΊ       | OI OILO   | Write<br>: | FOC7   | FOC6  | FOC5  | FOC4   |       |       |       |       |

| \$0042      | OC7M      | Read<br>:  | ОС7М7  | OC7M6 | OC7M5 | 007144 | 0     | 0     | 0     | 0     |

|             |           | Write<br>: |        |       |       | OC7M4  |       |       |       |       |

|             | OC7D      | Read       |        |       |       |        | 0     | 0     | 0     | 0     |

| \$0043      |           | Write :    | OC7D7  | OC7D6 | OC7D5 | OC7D4  |       |       |       |       |

|             |           | Read<br>:  | Bit 15 | 14    | 13    | 12     | 11    | 10    | 9     | Bit 8 |

| \$0044      | TCNT (hi) | Write      |        |       |       |        |       |       |       |       |

| \$0045      | TCNT (lo) | Read       | Bit 7  | 6     | 5     | 4      | 3     | 2     | 1     | Bit 0 |

|             |           | Write<br>: |        |       |       |        |       |       |       |       |

# \$0040 - \$006F

| Addres<br>s   | Name     |            | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|----------|------------|---------|-------|-------|-------|-------|-------|-------|-------|

| <b>#</b> 0040 | T00D4    | Read<br>:  | TEN     | TSWAI | TSFRZ | TFFCA | 0     | 0     | 0     | 0     |

| \$0046        | TSCR1    | Write<br>: | TEN     |       |       |       |       |       |       |       |

|               |          | Read<br>:  |         | TOV6  |       |       | 0     | 0     | 0     | 0     |

| \$0047        | TTOV     | Write      | TOV7    |       | TOV5  | TOV4  |       |       |       |       |

|               |          | Read       |         |       |       |       |       |       |       |       |

| \$0048        | TCTL1    | Write      | OM7     | OL7   | OM6   | OL6   | OM5   | OL5   | OM4   | OL4   |

|               |          | Read       | 0       | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0049        | Reserved | Write      |         |       |       |       |       |       |       |       |

| \$004A        | TCTL3    | Read       | : EDGZB | EDG7A | EDG6B | EDG6A | EDG5B | EDG5A | EDG4B | EDG4A |

|               |          | Write      |         |       |       |       |       |       |       |       |

|               |          | Read       | 0       | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$004B        | Reserved | Write      |         |       |       |       |       |       |       |       |

|               |          | Read       |         |       |       |       | 0     | 0     | 0     | 0     |

| \$004C        | TIE      | :<br>Write | C7I     | C6I   | C5I   | C4I   |       |       |       |       |

|               |          | :<br>Read  |         | 0     | 0     | 0     |       |       |       |       |

| \$004D        | TSCR2    | :<br>Write | TOI     |       |       |       | TCRE  | PR2   | PR1   | PR0   |

|               |          | :<br>Read  |         |       |       |       | 0     | 0     | 0     | 0     |

| \$004E        | TFLG1    | :<br>Write | C7F     | C6F   | C5F   | C4F   |       |       | 0     | J     |

|               |          | :<br>Read  |         | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$004F        | TFLG2    | :<br>Write | TOF     |       | 0     | 0     |       |       | 0     | J     |

|               |          | :<br>Read  |         | 0     | 0     | 0     | 0     | 0     | 0     |       |

| \$0050        | Reserved | :<br>Write | 0       | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|               |          | :          |         |       |       |       |       |       |       |       |

# \$0040 - \$006F

| Addres   | Name     |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

| S        | Name     | Read            |        |       |       |       |       |       |       |       |

| \$0051 F | Reserved | :               | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|          |          | Write<br>:      |        |       |       |       |       |       |       |       |

|          |          | Read            | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0052   | Reserved | Write<br>:      |        |       |       |       |       |       |       |       |

|          |          | Read            | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0053   | Reserved | Write<br>:      |        |       |       |       |       |       |       |       |

|          |          | Read            | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0054   | Reserved | Write<br>:      |        |       |       |       |       |       |       |       |

| \$0055 R |          | Read            | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|          | Reserved | Write           |        |       |       |       |       |       |       |       |

|          | Reserved | Read            | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0056   |          | Write<br>:      |        |       |       |       |       |       |       |       |

|          | Reserved | Read            | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0057   |          | Write<br>:      |        |       |       |       |       |       |       |       |

|          |          | Read            |        |       |       |       |       |       |       |       |

| \$0058   | TC4 (hi) | Write           | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

|          |          | Read            |        |       |       |       |       |       |       |       |

| \$0059   | TC4 (lo) | :<br>Write      | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|          |          | Read            |        |       |       |       |       |       |       |       |

| \$005A   | TC5 (hi) | :<br>Write      | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

|          |          | Read            |        |       |       |       |       |       |       |       |

| \$005B   | TC5 (lo) | :<br>Write<br>: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

# \$0040 - \$006F

| Addres<br>s | Name       |                         | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|------------|-------------------------|--------|-------|-------|-------|-------|-------|-------|-------|

| \$005C      | TC6 (hi)   | Read<br>:<br>Write      | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| \$005D      | TC6 (lo)   | Read<br>:<br>Write      | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$005E      | TC7 (hi)   | Read<br>:<br>Write      | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| \$005F      | TC7 (lo)   | Read<br>:<br>Write      | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0060      | PACTL      | Read<br>:<br>Write<br>: | 0      | PAEN  | PAMOD | PEDGE | CLK1  | CLK0  | PAOVI | PAI   |

| \$0061      | PAFLG      | Read<br>:<br>Write      | 0      | 0     | 0     | 0     | 0     | 0     | PAOVF | PAIF  |

| \$0062      | PACNT (hi) | Read<br>:<br>Write      | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| \$0063      | PACNT (lo) | Read<br>:<br>Write      | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0064      | Reserved   | Read :                  | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|             |            | Write<br>:<br>Read      | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0065      | Reserved   | :<br>Write<br>:         |        |       |       |       |       |       |       |       |

| \$0066      | Reserved   | Read<br>:<br>Write      | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|             |            | :                       |        |       |       |       |       |       |       |       |

\$0040 - \$006F TIM0 (Timer 16 Bit 4 Channels)

| Addres<br>s   | Name        |            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------------|------------|-------|-------|-------|-------|-------|-------|-------|-------|

|               |             | Read       | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0067        | Reserved    | Write      |       |       |       |       |       |       |       |       |

|               | _           | Read       | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0068        | Reserved    | Write      |       |       |       |       |       |       |       |       |

| *****         |             | Read<br>:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0069        | Reserved    | Write<br>: |       |       |       |       |       |       |       |       |

| <b>#000 A</b> | Decembed    | Read<br>:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$006A        | Reserved    | Write<br>: |       |       |       |       |       |       |       |       |

| ¢00cD         | Decembed    | Read<br>:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$006B        | Reserved    | Write<br>: |       |       |       |       |       |       |       |       |

| \$006C        | Reserved    | Read<br>:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$000C        | Reserved    | Write<br>: |       |       |       |       |       |       |       |       |

| \$006D        | Reserved    | Read<br>:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| ቅሀሀዕይ         | Reserved    | Write<br>: |       |       |       |       |       |       |       |       |

| \$006E        | Reserved    | Read<br>:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| φυυσ⊏         | Reserved    | Write<br>: |       |       |       |       |       |       |       |       |

| \$006F        | Reserved    | Read<br>:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| φυσοι         | i vesei veu | Write<br>: |       |       |       |       |       |       |       |       |

# \$0070 - \$007F Reserved

| \$0070<br>- | Reserved | Read<br>:  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|-------------|----------|------------|---|---|---|---|---|---|---|---|

| \$007F      | Reserved | Write<br>: |   |   |   |   |   |   |   |   |

| Addres<br>s | Name     |            | Bit 7           | Bit 6         | Bit 5  | Bit 4  | Bit 3           | Bit 2           | Bit 1              | Bit 0           |

|-------------|----------|------------|-----------------|---------------|--------|--------|-----------------|-----------------|--------------------|-----------------|

| \$0080      | ATDCTL0  | Read<br>:  | 0               | 0             | 0      | 0      | WDAD21          | MDAD21          | WRAP1 <sup>1</sup> | WDAD01          |

| φυσου       | AIDCILO  | Write<br>: |                 |               |        |        | WKAFS           | WNAFZ           | WKAFI              | VVICALO         |

| \$0081      | ATDCTL1  | Read<br>:  | ETRIGS          | 0             | 0      | 0      | ETRIGC          | ETRIGC          | ETRIGC             | ETRIGC          |

| ψοσοι       | AIDOILI  | Write<br>: | EL <sup>2</sup> |               |        |        | H3 <sup>2</sup> | H2 <sup>2</sup> | H1 <sup>2</sup>    | H0 <sup>2</sup> |

| \$0082      | ATDCTL2  | Read<br>:  | ADPU            | AFFC          | AWAI   | ETRIGL | ETRIGP          | ETRIG           | ASCIE              | ASCIF           |

| ψ0002       | AIDOILE  | Write<br>: | ADI 0           | AITO          | AVVAI  | E      | LIMOI           | LIKIO           | ZOGIL              |                 |

| \$0083      | ATDCTL3  | Read<br>:  | 0               | S8C           | S4C    | S2C    | S1C             | FIFO            | FRZ1               | FRZ0            |

| φυσσσ       | AIDOILS  | Write<br>: |                 | 300           | 570    | 020    | 310             | 1110            | 11121              | 11120           |

| \$0084      | ATDCTL4  | Read<br>:  | SRES8           | SMP1          | SMP0   | PRS4   | PRS3            | PRS2            | PRS1               | PRS0            |

| ΨΟΟΟΨ       | AIDOIL   | Write<br>: | ORLOG           | OWII 1        | OWN 0  | 11104  | 1100            | 1102            | 11101              | 11100           |

| \$0085      | ATDCTL5  | Read<br>:  | DJM             | DSGN          | SCAN   | MULT   | 0               | СС              | СВ                 | CA              |

| ψοσσσ       | 71100120 | Write<br>: | Dolvi           | D001 <b>1</b> | 00/114 | WIGET  |                 | - 00            | OB                 | 0/1             |

| \$0086      | ATDSTAT0 | Read<br>:  | SCF             | 0             | ETORF  | FIFOR  | 0               | CC2             | CC1                | CC0             |

| φοσσο       | AIDOIAIO | Write<br>: | 001             |               | LIOIU  | TII OK |                 |                 |                    |                 |

| \$0087      | Reserved | Read<br>:  | 0               | 0             | 0      | 0      | 0               | 0               | 0                  | 0               |

| φοσοι       | reserved | Write<br>: |                 |               |        |        |                 |                 |                    |                 |

| \$0088      | ATDTEST0 | Read<br>:  | 0               | 0             | 0      | 0      | 0               | 0               | 0                  | 0               |

| φοσσο       | AIDILOIO | Write<br>: |                 |               |        |        |                 |                 |                    |                 |

| \$0089      | ATDTEST1 | Read<br>:  | 0               | 0             | 0      | 0      | 0               | 0               | 0                  | sc              |

| φυσυσ       | AIDILOII | Write<br>: |                 |               |        |        |                 |                 |                    | 00              |

| \$008A      | ATDSTAT0 | Read<br>:  | CCF15           | CCF14         | CCF13  | CCF12  | CCF11           | CCF10           | CCF9               | CCF8            |

| ψυυση       | ALDOIAIO | Write<br>: |                 |               |        |        |                 |                 |                    |                 |

| Addres<br>s   | Name     |            | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|---------------|----------|------------|--------|--------|--------|--------|--------|--------|-------|-------|