# MILITARY i860™ XR 32/64-BIT MICROPROCESSOR

- Parallel Architecture that Supports Up to Three Operations per Clock

- One Integer or Control Instruction per Clock

- Up to Two Floating-Point Results per Clock

- High Performance Design

- -80 Peak Single Precision MFLOPs

- 60 Peak Double Precision MFLOPs

- 64-Bit External Data Bus

- --- 64-Bit Internal Instruction Cache Bus

- 128-Bit Internal Data Cache Bus

- High Level of Integration on One Chip

- 32-Bit Integer and Control Unit

- 32/64-Bit Pipelined Floating-Point Adder and Multiplier Units

- 64-Bit 3-D Graphics Unit

- Paging Unit with Translation Lookaside Buffer (TLB)

- 4 Kbyte Instruction Cache

- -8 Kbyte Data Cache

- Compatible with Industry Standards

- ANSI/IEEE Standard 754-1985 for Binary Floating-Point Arithmetic

- i386™/i486™ Microprocessor Data Formats and Page Table Entries

- Easy to Use

- On-Chip Debug Register

- Assembler, Linker, Simulator,

Debugger, C, FORTRAN and Ada

Compilers, FORTRAN Vectorizer,

Scalar and Vector Math Libraries for

both VMS\* and UNIX\* Environments

- Military Temperature Range:

- $-55^{\circ}$ C to  $+125^{\circ}$ C (T<sub>C</sub>)

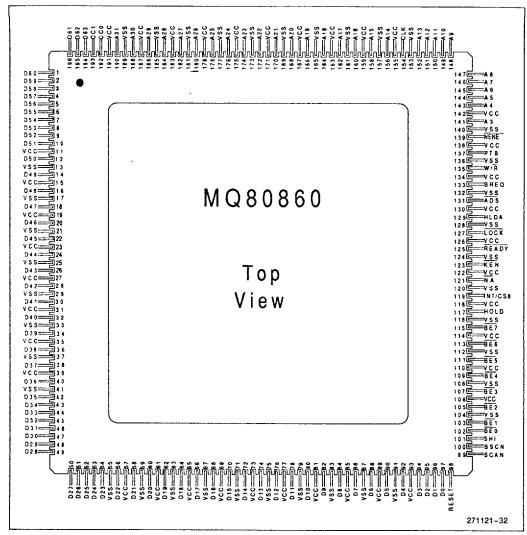

- Available in a 168-pin Ceramic Pin Grid Array Package (See Package/Module/PC Card Outlines and Dimensions, Order # 231369)

- Available in 196-Lead Ceramic Quad Flatpack (See Package/Module/PC Card Outlines and Dimensions, Order #231369)

The Intel I860TM XR Microprocessor delivers supercomputing performance in a single VLSI component. The 32/64-bit design of the i860 XR Microprocessor balances integer, floating point and graphics performance for applications such as target tracking, acoustic imaging, terrain data mapping and image processing. Its parallel architecture achieves high throughput with RISC design techniques, pipelined processing units, wide data paths, large on-chip caches, million-transistor design, and fast one-micron CHMOS IV silicon technology.

#### NOTE:

References to devices within this document refer to the Military versions of those devices.

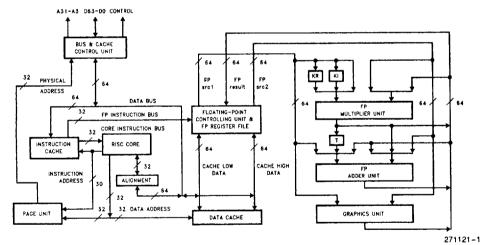

Figure 0.1 Block Diagram

Intel, intel, i386, i486 and i860 are trademarks of Intel Corporation

\*UNIX is a registered trademark of AT&T. \*VMS is a trademark of Digital Equipment Corporation.

October 1992 Order Number: 271121-005

# Military i860™ XR 32/64-Bit Microprocessor

| CONTENTS                                 | PAG                       |

|------------------------------------------|---------------------------|

| 1.0 FUNCTIONAL DESCRIPTION               | FAGI                      |

| 2.0 PROGRAMMING INTERFACE                | y-                        |

| 2.1 Data Types                           | 9-                        |

| 2.1.1 Integer                            | 9-1                       |

| 2.1.2 Ordinal                            | 9-1                       |

| 2.1.3 Single- and Double-Precision Real  | 9-6                       |

| 2.1.4 Pixel                              |                           |

| 2.2 Register Set                         | ••••••••••••••••••••••••• |

| 2.2.1 Integer Register File              |                           |

| 2.2.2 Floating-Point Register File       | 9-10                      |

| 2.2.3 Processor Status Register          | 9-10                      |

| 2.2.4 Extended Processor Status Register | 9-10                      |

| 2.2.5 Data Breakpoint Register           | 9-13                      |

| 2.2.6 Directory Base Register            | 9-14                      |

| 2.2.7 Fault Instruction Register         | 9-14                      |

| 2.2.8 Floating-Point Status Register     | 9-15                      |

| 2.2.9 KM, KI, I and MERGE Registers      |                           |

| 2.3 Addressing                           | 9-16                      |

| 2.4 Virtual Addressing                   | 9-17                      |

| 2.4.1 Page Frame                         | <u> </u>                  |

| 2.4.2 Virtual Address                    | 9-19                      |

| 2.4.3 Page Tables                        | 9-19                      |

| 2.4.4 Table Entries                      | 9-19                      |

| 2.4.5 Address Translation Algorithm      |                           |

| 2.4.6 Address Translation Faults         | 0.00                      |

| 2.4.7 rage translation Cache             | 0.00                      |

| 2.3 Caching and Cache Flushing           | 0.00                      |

| 2.0 instruction Set                      | 0.04                      |

| 2.0.1 Pipelined and Scalar Operations    |                           |

| 2.6.2 Dual-Instruction Mode              | 9-24                      |

| 2.6.3 Dual-Operation Instructions        | 9-2/                      |

# MILITARY 1860TM XR MICROPROCESSOR

| CONTENTS                                                             | PAGE |

|----------------------------------------------------------------------|------|

| 2.0 PROGRAMMING INTERFACE (Continued)                                |      |

| 2.7 Addressing Modes                                                 | 9-28 |

| 2.8 Traps and Interrupts                                             |      |

| 2.8.1 Trap Handler Invocation                                        | 9-29 |

| 2.8.2 Instruction Fault                                              |      |

| 2.8.3 Floating-Point Fault                                           |      |

| 2.8.4 Instruction Access Fault                                       |      |

| 2.8.5 Data Access Fault                                              |      |

| 2.8.6 Interrupt Trap                                                 |      |

| 2.8.7 Reset Trap                                                     |      |

| 2.9 Debugging                                                        | 9-32 |

| 3.0 HARDWARE INTERFACE                                               | 9-32 |

| 3.1 Signal Description                                               | 9-32 |

| 3.1.1 Clock (CLK)                                                    | 9-33 |

| 3.1.2 System Reset (RESET)                                           |      |

| 3.1.3 Bus Hold (HOLD) and Bus Hold Acknowledge (HLDA)                |      |

| 3.1.4 Bus Request (BREQ)                                             | 9-33 |

| 3.1.5 Interrupt/Code-Size (INT/CS8)                                  |      |

| 3.1.6 Address Pins (A31-A3) and Byte Enables (BE7-BE0)               |      |

| 3.1.7 Data Pins (D63-D0)                                             |      |

| 3.1.8 Bus Lock (LOCK)                                                |      |

| 3.1.9 Write/Read Bus Cycle (W/R)                                     | 9-35 |

| 3.1.10 Next Near (NENE)                                              |      |

| 3.1.11 Next Address Request (NA)                                     |      |

| 3.1.12 Transfer Acknowledge (READY)                                  |      |

| 3.1.13 Address Status (ADS)                                          |      |

| 3.1.14 Cache Enable (KEN)                                            |      |

| 3.1.15 Page Table Bit (PTB)                                          |      |

| 3.1.16 Boundary Scan Shift Input (SHI)                               |      |

| 3.1.17 Boundary Scan Enable (BSCN)                                   |      |

| 3.1.18 Shift Scan Path (SCAN)                                        |      |

| 3.1.19 Configuration (CC1-CC0)                                       |      |

| 3.1.20 System Power (V <sub>CC</sub> ) and Ground (V <sub>SS</sub> ) |      |

| 3.2 Initialization                                                   |      |

| 3.3 Testability                                                      |      |

| 3.3.1 Normal Mode                                                    | 9-38 |

**4826175 0137343 113**

3.3.2 Shift Mode .....

# MILITARY i860™ XR MICROPROCESSOR

| CONTENTS                                          | PAGE       |

|---------------------------------------------------|------------|

| 4.0 BUS OPERATION                                 | 0.00       |

| 4.1 Pipelining                                    | 9-38       |

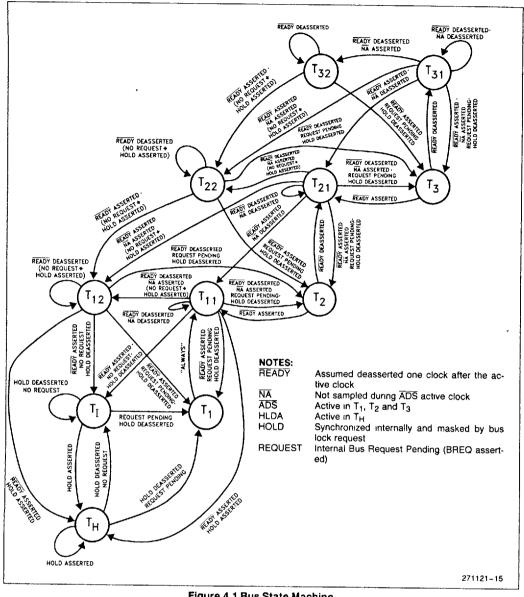

| 4.2 Bus State Machine                             | 9-38       |

| 4.3 Bus Cycles                                    | 9-38       |

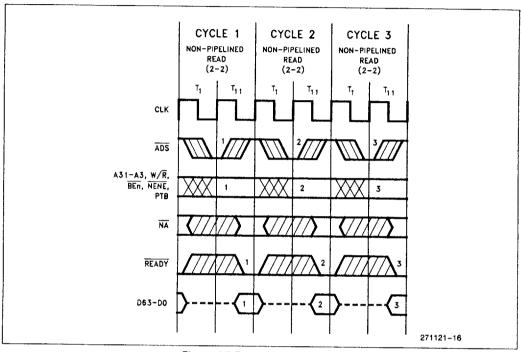

| 4.3.1 Nonpipelined Read Cycles                    | 0.44       |

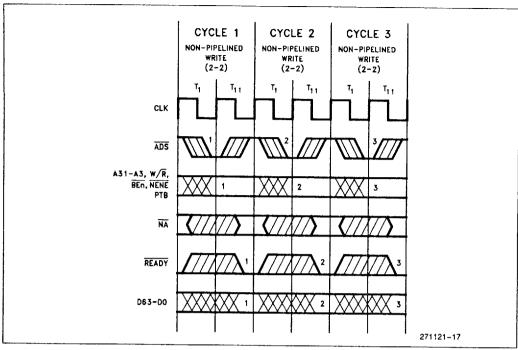

| 4.3.2 Nonpipelined Write Cycles                   | 9.41       |

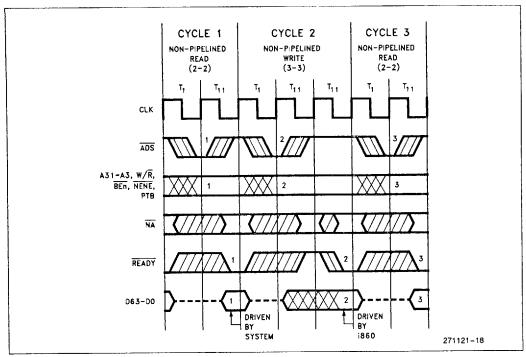

| 4.3.3 Pipelined Read and Write Cycles             | 9-14       |

| 4.3.4 Locked Cycles                               | 9.46       |

| 4.3.5 HOLD and BREQ Arbitration Cycles            | 9-46       |

| 4.4 Bus States During RESET                       | 9-47       |

| 5.0 MECHANICAL DATA                               |            |

|                                                   |            |

| 6.0 ELECTRICAL DATA                               | 9-55       |

| 6.1 Absolute Maximum Ratings                      | 9-55       |

| 6.2 Operating Conditions                          |            |

| 6.3 DC Characteristics                            | 9-55       |

| 6.4 AC Characteristics                            |            |

| 7.0 INSTRUCTION SET                               |            |

| 7.1 Instruction Definitions in Alphabetical Order |            |

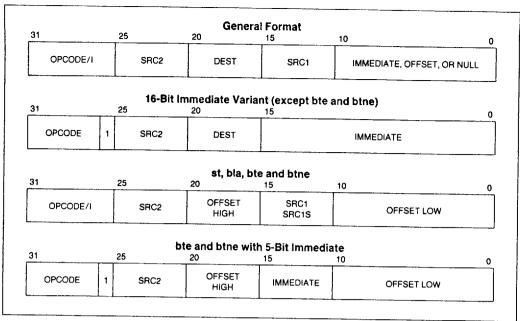

| 7.2 Instruction Format and Encoding               | 9-67       |

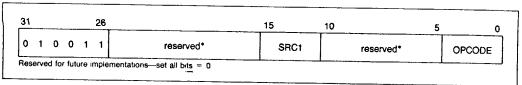

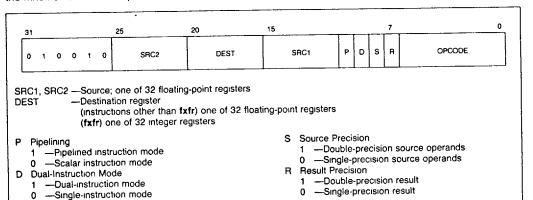

| 7.2.1 REG-Format Instructions                     | ····· 9-67 |

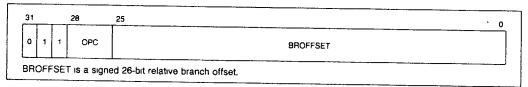

| 7.2.2 CTRL-Format Instructions                    |            |

| 7.2.3 Floating-Point Instructions                 | 9-71       |

| 7.3 Instruction Timings                           | 9-73       |

| 7.4 Instruction Characteristics                   |            |

# MILITARY 1860TM XR MICROPROCESSOR

## **FIGURES**

| Figure | 0.1 | Block | Diagram |

|--------|-----|-------|---------|

|        |     |       |         |

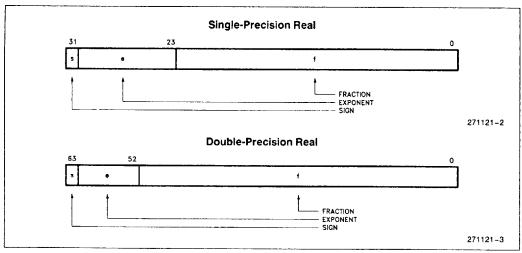

- Figure 2.1 Real Number Formats

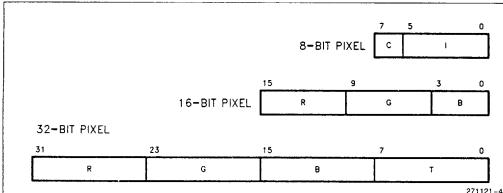

- Figure 2.2 Pixel Format Example

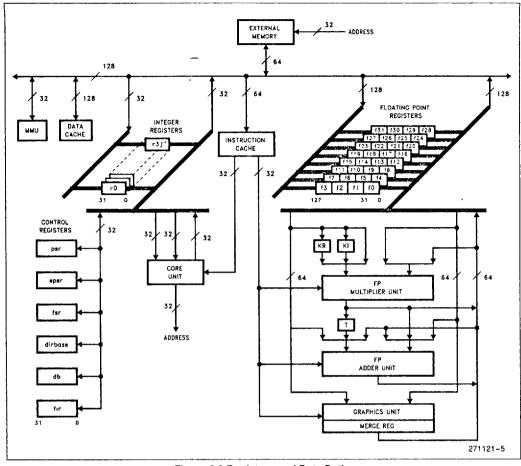

- Figure 2.3 Registers and Data Paths

- Figure 2.4 Processor Status Register (psr)

- Figure 2.5 Extended Processor Status Register (epsr)

- Figure 2.6 Directory Base Register (dirbase)

- Figure 2.7 Floating-Point Status Register (fsr)

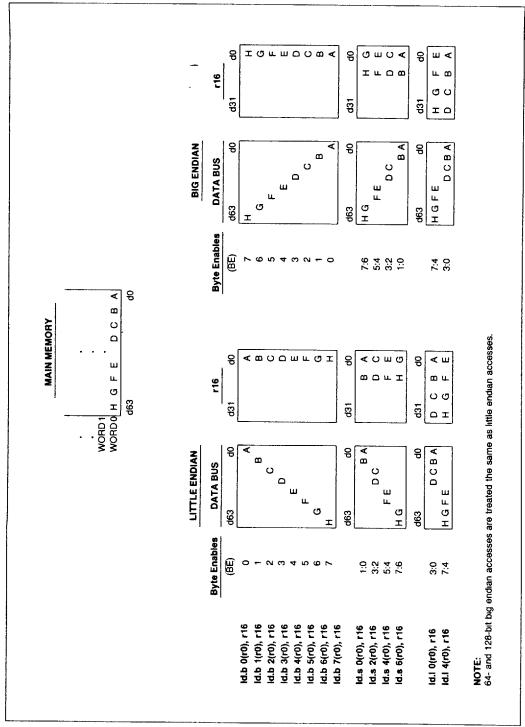

- Figure 2.8 Little and Big Endian Accesses

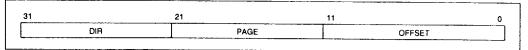

- Figure 2.9 Format of a Virtual Address

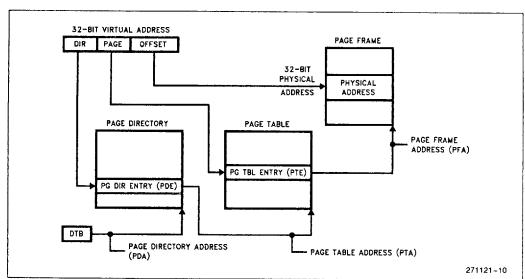

- Figure 2.10 Address Translation

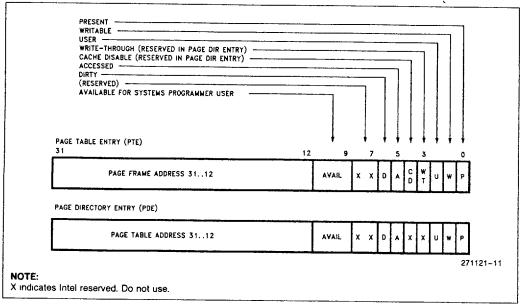

- Figure 2.11 Format of a Page-Table and Page-Directory Entry

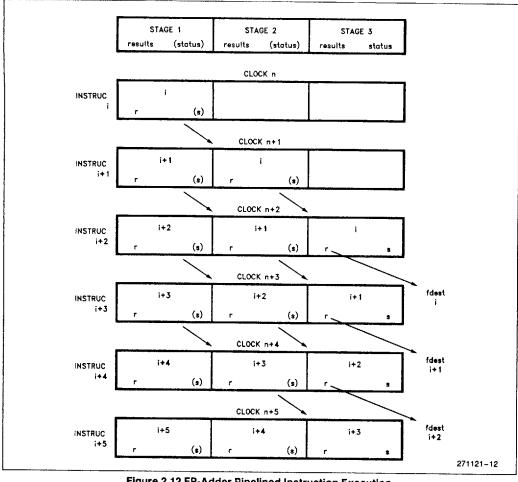

- Figure 2.12 FP-Adder Pipelined Instruction Execution

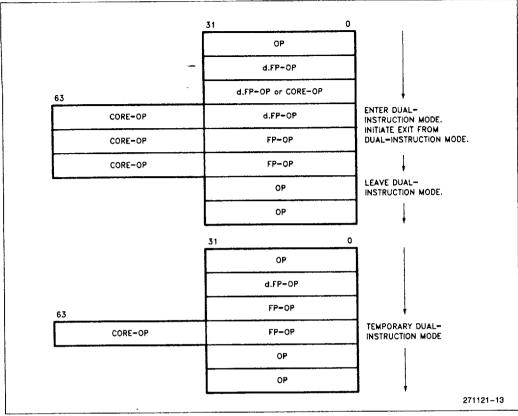

- Figure 2.13 Dual-Instruction Mode Transitions

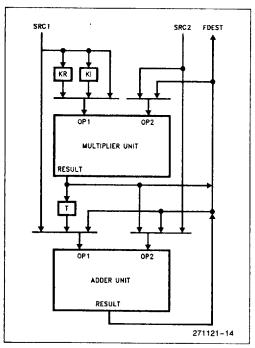

- Figure 2.14 Dual-Operation Data Paths

- Figure 3.1 Order of Boundary Scan Chain

- Figure 4.1 Bus State Machine

- Figure 4.2 Fastest Read Cycles

- Figure 4.3 Fastest Write Cycles

- Figure 4.4 Fastest Read/Write Cycles

- Figure 4.5 Pipelined Read Followed by Pipelined Write

- Figure 4.6 Pipelined Write Followed by Pipelined Read

- Figure 4.7 Pipelining Driven by NA

- Figure 4.8 NA Active with No Internal Bus Request

- Figure 4.9 Locked Cycles

- Figure 4.10 HOLD, HLDA and BREQ

- Figure 4.11 Reset Activities

- Figure 5.1 168-Pin Ceramic Pin Grid Array. Pin Configuration—View from Top Side

- Figure 5.2 168-Pin Ceramic Pin Grid Array. Pin Configuration—View from Pin Side

- Figure 5.3 196-Pin Ceramic Quad Flatpack. Pin Configuration—View from Lid Side

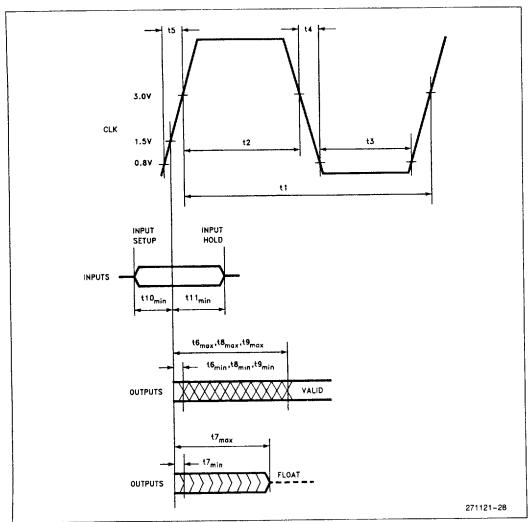

- Figure 6.1 CLK, Input and Output Timings

- Figure 7.1 REG-Format Variations

- Figure 7.2 Core Escape Instruction Format

- Figure 7.3 CTRL Instruction Format

- Figure 7.4 Floating-Point Instruction Encoding

#### **TABLES**

- Table 2.1 Pixel Formats

- Table 2.2 Values of PS

- Table 2.3 Values of RB

- Table 2.4 Values of RC

- Table 2.5 Values of RM

- Table 2.6 Combining Directory and Page Protections

- Table 2.7 Instruction Set

- Table 2.8 Types of Traps

- Table 2.9 Register and Cache Values after Reset

- Table 3.1 Pin Summary

- Table 3.2 Indentifying Instruction Fetches

- Table 3.3 Cacheability Based on KEN and CD or WT

- Table 3.4 Output Pin Status During Reset

- Table 3.5 Test Mode Selection

- Table 3.6 Test Mode Latches

- Table 5.1 168-Pin Ceramic PGA Pin Assignment by Location

- Table 5.2 168-Pin Ceramic PGA Pin Assignment by Function

- Table 5.3 196-Pin Ceramic Quad Flatpack (CQFP) Pin Assignment by Location

- Table 5.4 196-Pin Ceramic Quad Flatpack (CQFF) Pin Assignment by Function

- Table 6.1 DC Characteristics

- Table 6.2 AC Characteristics

- Table 7.1 Precision Specification

- Table 7.2 FADDP MERGE Update

- Table 7.3 Register Encoding

- Table 7.4 REG-Format Opcodes

- Table 7.5 Core Escape Opcodes

- Table 7.6 CTRL-Format Opcodes

- Table 7.7 Floating-Point Opcodes

- Table 7.8 DPC Encoding

- Table 7.9 Instruction Characteristics

# 1.0 FUNCTIONAL DESCRIPTION

As shown by the block diagram on the front page, the Military i860 XR microprocessor consists of 9 units:

- 1. RISC Based Core Execution Unit

- 2. Floating-Point Control Unit

- 3. Floating-Point Adder Unit

- 4. Floating-Point Multiplier Unit

- 5. Graphics Unit

- 6. Paging Unit

- 7. Instruction Cache

- 8. Data Cache

- 9. Bus and Cache Control Unit

The core execution unit controls overall operation of the Military i860 XR microprocessor. The core unit executes load, store, integer, bit, and control-transfer operations, and fetches instructions for the floating-point unit as well. A set of 32 x 32-bit general-purpose registers are provided for the manipulation of integer data. Load and store instructions move 8-, 16-, and 32-bit data to and from these registers. Its full set of integer, logical, and control-transfer instructions give the core unit the ability to execute complete systems software and applications programs. A trap mechanism provides rapid response to exceptions and external interrupts. Debugging is supported by the ability to trap on data or instruction reference.

The floating-point hardware is connected to a separate set of floating-point registers, which can be accessed as 16 x 64-bit registers, or 32 x 32-bit registers. Special load and store instructions can also access these same registers as 8 x 128-bit registers. All floating-point instructions use these registers as their source and destination operands,

The floating-point control unit controls both the floating-point adder and the floating-point multiplier, issuing instructions, handling all source and result exceptions, and updating status bits in the floating-point status register. The adder and multiplier can operate in parallel, producing up to two floating-point results per clock. The floating-point data types, floating-point instructions and exception handling all support the IEEE Standard for Binary Floating-Point Arithmetic (ANSI/IEEE Std 754-1985).

The floating-point adder performs addition, subtraction, comparison, and conversions on 64- and 32-bit floating-point values. An adder instruction executes in three clocks; however, in pipelined mode, a new result is generated every clock.

The floating-point multiplier performs floating-point and integer multiply and floating-point reciprocal operations on 64- and 32-bit floating-point values. A multiplier instruction executes in three to four clocks;

PRELIMINARY

# MILITARY 1860TM XR MICROPROCESSOR

however, in pipelined mode, a new result can be generated every clock for single-precision and every other clock for double precision.

The graphics unit has special integer logic that supports three-dimensional drawing in a graphics frame buffer, with color intensity shading and hidden surface elimination via the Z-buffer algorithm. The graphics unit recognizes the pixel as an 8-, 16- or 32-bit data type. It can compute individual red, blue and green color intensity values within a pixel; but it does so with parallel operations that take advantage of the 64-bit internal word size and 64-bit external bus. The graphics features of the Military 1860 XR microprocessor assume that the surface of a solid object is drawn with polygon patches whose shapes approximate the original object. The color intensities of the vertices of the polygon and their distances from the viewer are known, but the distances and intensities of the other points must be calculated by interpolation. The graphics instructions of the Military i860 XR microprocessor directly aid such interpolation.

The paging unit implements a protected, paged, virtual memory system via a 64-entry, four-way set-associative TLB (Translation Lookaside Buffer). The paging unit uses the TLB to perform the translation of logical address to physical address, and to check for access violations. The access protection scheme employs two levels of privilege: user and supervisor.

The instruction cache is a two-way set-associative memory of four Kbytes, with a 32-byte line size. It transfers up to 64 bits per clock (266 Mbyte/sec at 33 MHz).

The data cache is a two-way set-associative memory of eight Kbytes, with a 32-byte line size. It transfers up to 128 bits per clock (640 Mbyte/sec at 40 MHz). The Military i860 XR microprocessor uses writeback caching, i.e. memory writes update the cache (if applicable) without necessarily updating memory immediately; however, caching can be inhibited by software where necessary.

The bus and cache control unit performs data and instruction accesses for the core unit. It receives cycle requests and specifications from the core unit, performs the data-cache or instuction-cache miss processing, controls TLB translation, and provides the interface to the external bus. Its pipelined structure supports up to three outstanding bus cycles.

#### 2.0 PROGRAMMING INTERFACE

The programmer-visible aspects of the architecture of the Military i860 XR microprocessor include data types, registers, instructions and traps.

### 2.1 Data Types

The Military i860 XR microprocessor provides operations for integer and floating-point data. Integer operations are performed on 32-bit operands with some support also for 64-bit operands. Load and store instructions can reference 8-bit, 16-bit, 32-bit, 64-bit and 128-bit operands. Floating-point operations are performed on IEEE-standard 32- and 64-bit formats. Graphics oriented instructions operate on arrays of 8-, 16- or 32-bit pixels.

#### 2.1.1 INTEGER

An integer is a 32-bit signed value in standard two's complement form. A 32-bit integer can represent a value in the range -2,147,483,648 ( $-2^{31}$ ) to 2,147,483,647 ( $+2^{31}-1$ ). Arithmetic operations on 8- and 16-bit integers can be performed by sign-extending the 8- or 16-bit values to 32 bits, then using the 32-bit operations.

There are also add and subtract instructions that operate on 64-bit long integers.

Load and store instructions may also reference (in addition to the 32- and 64-bit formats previously mentioned) 8- and 16-bit items in memory. When an 8- or 16-bit item is loaded into a register, it is converted to an integer by sign-extending the value to 32 bits. When an 8- or 16-bit item is stored from a register, the corresponding number of low-order bits of the register are used.

#### 2.1.2 ORDINAL

Arithmetic operations are available for 32-bit ordinals. An ordinal is an unsigned integer. An ordinal can represent values in the range 0 to  $4,294,967,295 (+2^{32}-1)$ .

Also, there are add and subtract instructions that operate on 64-bit ordinals.

#### 2.1.3 SINGLE- AND DOUBLE-PRECISION REAL

Figure 2.1 shows the real number formats. A single-precision real (also called "single real") data type is a 32-bit binary floating-point number. Bit 31 is the sign bit; bits 30..23 are the exponent; and bits 22..0 are the fraction. In accordance with ANSI/IEEE standard 754, the value of a single-precision real is defined as follows:

- If e = 0 and f ≠ 0 or e = 255 then generate a floating-point source-exception trap when encountered in a floating-point operation.

- 2. If 0 < e < 255, then the value is (-1)s  $\times$  1.f  $\times$  2e-127.

- 3. If e = 0 and f = 0, then the value is signed zero.

A double-precision real (also called "double real") data type is a 64-bit binary floating-point number. Bit 63 is the sign bit; bits 62..52 are the exponent; and bits 51..0 are the fraction. In accordance with ANSI/IEEE standard 754, the value of a double-precision real is defined as follows:

- If e = 0 and f ≠ 0 or e = 2047, then generate a floating-point source-exception trap when encountered in a floating-point operation.

- 2. If 0 < e < 2047, then the value is  $(-1)^s \times 1.f \times 2^{e-1023}$ .

Figure 2.1 Real Number Formats

9-8

3. If e = 0 and f = 0, then the value is signed zero.

The special values infinity, NaN ("Not a Number"), indefinite, and denormal generate a trap when encountered. The trap handler implements IEEE-standard results.

A double-precision real value occupies an even/odd pair of floating-point registers. Bits 31..0 are stored in the even-numbered floating-point register; bits 63..32 are stored in the next higher odd-numbered floating-point register.

#### **2.1.4 PIXEL**

A pixel may be 8, 16, or 32 bits long depending on color and intensity resolution requirements. Regardless of the pixel size, the Military i860 XR microprocessor always operates on 64 bits worth of pixels at a time. The pixel data type is used by two kinds of instructions:

- The selective pixel-store instruction that helps implement hidden surface elimination.

- The pixel add instruction that helps implement 3-D color intensity shading.

To perform color intensity shading efficiently in a variety of applications, the Military i860 XR microprocessor defines three pixel formats according to Table 2.1.

Figure 2.2 illustrates one way of assigning meaning to the fields of pixels. These assignments are for illustration purposes only. The Military i860 XR microprocessor defines only the field sizes, not the specific use of each field. Other ways of using the fields of pixels are possible.

**Table 2.1 Pixel Formats**

| Pixel<br>Size<br>(in bits) | Bits of<br>Color 1<br>Intensity Bits of<br>Color 2<br>Intensity |   | Bits of<br>Color 3<br>Intensity | Bits of<br>Other<br>Attribute<br>(Texture) |

|----------------------------|-----------------------------------------------------------------|---|---------------------------------|--------------------------------------------|

| 8                          | N (≤ 8) bits of intensity*                                      |   |                                 | 8 - N                                      |

| 16                         | 6                                                               | 6 | 4                               | 0                                          |

| 32                         | 8                                                               | 8 | 8                               | 8                                          |

The intensity attribute fields may be assigned to colors in any order convenient to the application.

\*With 8-bit pixels, up to 8 bits can be used for intensity; the remaining bits can be used for any other attribute, such as color. The intensity bits must be the low-order bits of the pixel.

## 2.2 Register Set

As Figure 2.3 shows, the Military i860 XR microprocessor has the following registers:

- · An integer register file

- A floating-point register file

- Six control registers (psr, epsr, db, dirbase, fir and fsr)

- Four special-purpose registers (KR, KI, T and MERGE)

The control registers are accessible only by load and store control-register instructions; the integer and floating-point registers are accessed by arithmetic operations and load and store instructions. The special-purpose registers KR, KI, T and MERGE are used by a few specific instructions.

I—Intensity, R—Red intensity, G—Green intensity, B—Blue intensity, C—Color, T—Texture

These assignments of specific meanings to the fields of pixels are for illustration purposes only. Only the field sizes are defined, not the specific use of each field.

Figure 2.2 Pixel Format Example

#### 2.2.1 INTEGER REGISTER FILE

There are 32 integer registers, each 32 bits wide, referred to as **r0** through **r31**, which are used for address computation and scalar integer computations. Register **r0** always returns zero when read, independently of what is stored in it. This special behavior of **r0** makes it useful for modifying the function of certain instructions.

#### 2.2.2 FLOATING-POINT REGISTER FILE

There are 32 floating-point registers, each 32-bits wide, referred to as f0 through f31, which are used for floating-point computations. Registers f0 and f1 always return zero when read, independently of what is stored in them. The floating-point registers are also used by a set of graphics operations, primarily for 3D graphics computations.

When accessing 64-bit floating-point or integer values, the Military i860 XR microprocessor uses an even/odd pair of registers. When accessing 128-bit values, it uses an aligned set of four contiguous registers (f0, f4, f8, ..., f28). The instruction must designate the lowest register number of the set of registers containing 64- or 128-bit values. The register with the lowest number contains the least significant part of the value. For 128-bit values, the register pair with the lower numbers contain the least significant 64 bits while the register pair with the higher numbers contain the most significant 64 bits.

The 128-bit load and store instructions, along with the 128-bit data path between the floating-point registers and the data cache help to sustain the extraordinarily high rate of computation.

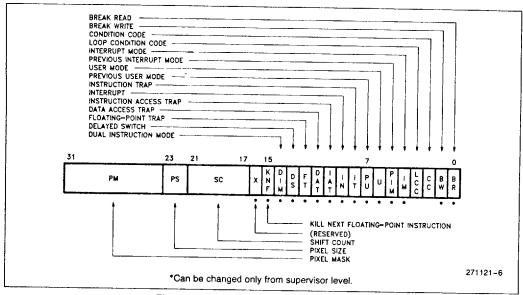

### 2.2.3 PROCESSOR STATUS REGISTER

The processor status register (psr) contains state information for the current process. Figure 2.4 shows the format of psr.

- BR (Break Read) and BW (Break Write) enable a data access trap when the operand address matches the address in the Data Breakpoint (db) register and a read or write (respectively) occurs.

- Various instructions set CC (Condition Code) according to tests they perform. The branch-on-condition-code instructions test its value. The Branch on CC and Add instruction sets and tests LCC (Loop Condition Code).

- IM (Interrupt Mode) enables external interrupts if set; disables interrupts if clear.

- U (User Mode) is set when the Military i860 XR microprocessor is executing in user mode; it is clear when the Military i860 XR microprocessor is executing in supervisor mode. In user mode, writes to some control registers are inhibited. This bit also controls the memory protection mechanism. See section 2.4.4.3 for a description of memory protection in user and supervisor modes.

9-10

Figure 2.3 Registers and Data Paths

Figure 2.4 Processor Status Register (psr)

Figure 2.5 Extended Processor Status Register (epsr)

- PIM (Previous Interrupt Mode) and PU (Previous User Mode) save the corresponding status bits (IM and U) on a trap, because those status bits are changed when a trap occurs. They are restored into their previous state upon returning from a trap handler with a branch indirect instruction when a trap flag is set in the psr.

- FT (Floating-Point Trap), DAT (Data Access Trap), IAT (Instruction Access Trap), IN (Interrupt) and IT (Instruction Trap) are trap flags. They are set when the corresponding trap condition occurs. The trap handler examines these bits to determine which condition or conditions caused the trap.

- DS (Delayed Switch) is set if a trap occurs during the instruction before dual-instruction mode is entered or exited. If DS is set and DIM (Dual Instruction Mode) is clear, the Military i860 XR microprocessor switches to dual-instruction mode one instruction after returning from the trap handler. If DS and DIM are both set, the Military i860 XR microprocessor switches to single-instruction mode one instruction after returning from the trap handler.

- When a trap occurs, the Military 1860 XR microprocessor sets DIM if it is executing in dual-instruction mode; it clears DIM if it is executing in single-instruction mode. If DIM is set after returning from a trap handler, the Military 1860 XR microprocessor resumes execution in dual-instruction mode.

9-12

# int<sub>e</sub>l،

#### MILITARY 1860TM XR MICROPROCESSOR

- When KNF (Kill Next Floating-Point Instruction) is set, the next floating-point instruction is suppressed (except that its dual-instruction mode bit is interpreted). A trap handler sets KNF if the trapped floating-point instruction should not be reexecuted.

- SC (Shift Count) stores the shift count used by the last right-shift instruction. It controls the number of shifts executed by the double-shift instruction.

- PS (Pixel Size) and PM (Pixel Mask) are used by the pixel-store instruction and by the graphics instructions. The values of PS control pixel size as defined by Table 2.2. The bits in PM correspond to pixels to be updated by the pixel-store instruction pst.d The low-order bit of PM corresponds to the low-order pixel of the 64-bit source operand of pst.d The number of low-order bits of PM that are actually used is the number of pixels that fit into 64-bits, which depends upon PS. If a bit of PM is set, then pst.d stores the corresponding pixel. Refer also to the pst.d instruction in Section 7.

Table 2.2 Values of PS

| Value | Pixel Size in bits | Pixel Size<br>in bytes |

|-------|--------------------|------------------------|

| 00    | 8                  | 1                      |

| 01    | 16                 | 2                      |

| 10    | 32                 | 4                      |

| 11    | (undefined)        | (undefined)            |

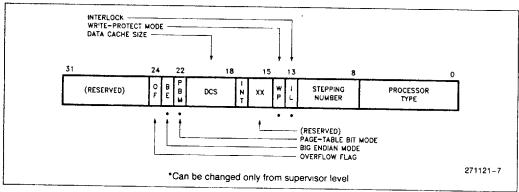

# 2.2.4 EXTENDED PROCESSOR STATUS REGISTER

The extended processor status register (epsr) contains additional state information for the current process beyond that stored in psr. Figure 2.5 shows the format of epsr.

- The processor type is one (1) for the Military i860 XR microprocessor (Read Only field).

- The stepping number has a unique value that distinguishes among different revisions of the processor (Read Only field).

- IL (Interlock) is set if a trap occurs after a lock instruction but before the load or store following the subsequent unlock instruction. IL indicates to the trap handler that a locked sequence has been interrupted. When the trap handler finds IL set, it should scan backwards for the lock instruction and restart at that point. The absence of a lock instruction within 30–33 instructions of the trap indicates a progamming error.

- WP (write protect) controls the semantics of the W bit of page table entries. A clear W bit in either the directory or the page table entry causes writes to be trapped. When WP is clear, writes are trapped in user mode, but not in supervisor mode. When WP is set, writes are trapped in both user and supervisor modes. After the value of the WP bit is changed, the TLB must be invalidated by setting the ITI bit of the dirbase register, before any stores are performed.

- INT (Interrupt) is the value of the INT input pin.

- DCS (Data Cache Size) is a read-only field that tells the size of the on-chip data cache. The number of bytes actually available is 2<sup>12+DCS</sup>; therefore, a value of zero indicates 4 Kbytes, one indicates 8 Kbytes, etc. For the i860 processor, DCS = 1

Figure 2.6 Directory Base Register (dirbase)

PRELIMINARY

int<sub>el®</sub>

- PBM (Page-Table Bit Mode) determines which bit

of page-table entries is output on the PTB pin.

When PBM is clear, the PTB signal reflects bit CD

of the page-table entry used for the current cycle.

When PBM is set, the PTB signal reflects bit WT

of the page-table entry used for the current cycle.

- BE (Big Endian) controls the ordering of bytes within a data item in memory. Normally (i.e. when BE is clear) the Military i860 XR microprocessor operates in little endian mode, in which the addressed byte is the low-order byte. When BE is set (big endian mode), the low-order three bits of all load and store addresses are complemented, then masked to the appropriate boundary for alignment. This causes the addressed byte to be the most significant byte. Section 2.3 discusses little and big endian addressing.

- OF (Overflow Flag) is set by adds, addu, subs, and subu when integer overflow occurs. For adds and subs, OF is set if the carry from bit 31 is different than the carry from bit 30. For addu, OF is set if there is a carry from bit 31. For subu, OF is set if there is no carry from bit 31. Under all other conditions, it is cleared by these instructions. OF controls the function of the intovr instruction.

#### 2.2.5 DATA BREAKPOINT REGISTER

The data breakpoint register (db) is used to generate a trap when the Military i860 XR microprocessor makes a data-operand access to the address stored in this register. The trap is enabled by BR and BW in psr. The db register can only be changed from supervisor level. When comparing, a number of low order bits of the address are ignored, depending on the size of the operand. For example, a 16-bit access ignores the low-order bit of the address when comparing to db; a 32-bit access ignores the two low-order bits. This ensures that any access that overlaps the address contained in the register will generate a trap. The data access trap occurs before the data is accessed and prevents the load or store from completing.

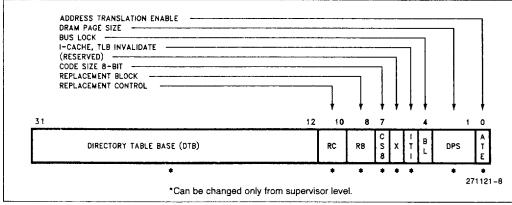

#### 2.2.6 DIRECTORY BASE REGISTER

The directory base register **dirbase** (shown in Figure 2.6) controls address translation, caching, and bus options. The **dirbase** register can only be changed from the supervisor level. However, the BL bit can be changed from user level with the **lock** and **unlock** instructions.

ATE (Address Translation Enable), when set, enables the virtual-address translation algorithm.

The data cache must be flushed before changing the ATE bit.

- DPS (DRAM Page Size) controls how many bits to ignore when comparing the current bus-cycle address with the previous bus-cycle address to generate the NENE signal. This feature allows for higher speeds when using static column or pagemode DRAMs and consecutive reads and writes access the same column or page. The comparison ignores the low-order 12 + DPS bits. A value of zero is appropriate for one bank of 256K × n RAMs, one for 1M × n RAMS, etc.

- When BL (Bus Lock) is set, external bus accesses are locked. The LOCK signal is asserted on the next bus cycle whose internal bus request is generated after BL is set. It remains asserted on all subsequent bus cycles as long as BL remains set. The LOCK signal is deasserted on the next bus cycle whose internal bus request is generated after BL is cleared. Traps immediately clear BL. The lock and unlock instructions control the BL bit.

- ITI (I-Cache, TLB Invalidate), when set in the value being stored into dirbase, causes the instruction cache and address-translation cache (TLB) to be flushed. The ITI bit does not remain set in dirbase. ITI always appears as zero when reading dirbase. Section 2.5 discusses flushing the data cache before invalidating the TLB.

- When CS8 (Code Size 8-Bit) is set, instruction cache misses are processed as 8-bit bus cycles. When this bit is clear, instruction cache misses are processed as 64-bit bus cycles. This bit can not be set by software; hardware sets this bit at initialization time. It can be cleared by software (one time only) to allow the system to execute out of 64-bit memory after bootstrapping from 8-bit EPROM. A nondelayed branch to code in 64-bit memory should directly follow the st.c (store control register) instruction that clears CS8, in order to make the transition from 8-bit to 64-bit memory occur at the correct time. The branch must be aligned on a 64-bit boundary.

- RB (Replacement Block) identifies the cache block to be replaced by cache replacement algorithms. The high-order bit of RB is ignored by the instruction and data caches. RB conditions the cache flush instruction flush, which is discussed in Section 7. Table 2.3 explains the values of RB.

- RC (Replacement Control) controls cache replacement algorithms. Table 2.4 explains the significance of the values of RC.

- DTB (Directory Table Base) contains the high-order 20 bits of the physical address of the page directory when address translation is enabled (i.e. ATE = 1). The twelve low-order bits of the address are zeros.

9-14

## MILITARY 1860TM XR MICROPROCESSOR

Figure 2.7 Floating-Point Status Register (fsr)

Table 2.3 Values of RB

| Val | lue | Replace<br>TLB Block | Replace Instruction and Data Cache Block |

|-----|-----|----------------------|------------------------------------------|

| 0   | 0   | 0                    | 0                                        |

| 0   | 1   | 1                    | 1                                        |

| 1   | 0   | 2                    | О                                        |

| 1   | 1   | 3                    | 1                                        |

# Table 2.4 Values of RC

| Value | Meaning                                                                                                                                                                                             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00    | Selects the normal replacement algorithm where any block in the set may be replaced on cache misses in all caches.                                                                                  |

| 01    | Instruction, data, and TLB cache misses replace the block selected by RB. The instruction and data caches ignore the high-order bit of RB. This mode is used for instruction cache and TLB testing. |

| 10    | Data cache misses replace the block selected by the low-order bit of RB.                                                                                                                            |

| 11    | Disables data cache replacement.                                                                                                                                                                    |

#### 2.2.7 FAULT INSTRUCTION REGISTER

When a trap occurs, this register contains the address of the trapping instruction (not necessarily the instruction that created the conditions that required the trap). The fir is a read only register. The address of the Id.c instruction used to read the fir is returned in rdest when reading the fir at any time other than the first Id.c fir after a trap.

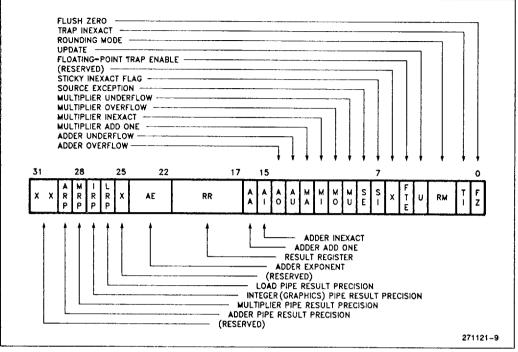

#### 2.2.8 FLOATING-POINT STATUS REGISTER

The floating-point status register (fsr) contains the floating-point trap and rounding-mode status for the current process. Figure 2.7 shows its format. The fsr is writable in user level.

- If FZ (Flush Zero) is clear and underflow occurs, a result-exception trap is generated. When FZ is set and underflow occurs, the result is set to zero, and no trap due to underflow occurs.

- If TI (Trap Inexact) is clear, inexact results do not cause a trap. If TI is set, inexact results cause a trap. The sticky inexact flag (SI) is set whenever an inexact result is produced, regardless of the setting of TI.

- RM (Rounding Mode) specifies one of the four rounding modes defined by the IEEE standard. Given a true result b that cannot be represented

PRELIMINARY

Table 2.5 Values of RM

| Value | Rounding Mode            | Rounding Action                                                                                            |

|-------|--------------------------|------------------------------------------------------------------------------------------------------------|

| 00    | Round to nearest or even | Closer to b of a or c, if equally close, select even number (the one whose least significant bit is zero). |

| 01    | Round down (toward - ∞)  | a                                                                                                          |

| 10    | Round up (toward + ∞     | C                                                                                                          |

| 11    | Chop (toward zero)       | Smaller in magnitude of a or c.                                                                            |

by the target data type, the Military  $^{1860}$  XR microprocessor determines the two representable numbers a and c that most closely bracket b in value (a < b < c). The Military  $^{1860}$  XR microprocessor then rounds (changes) b to a or c according to the mode selected by RM as defined in Table 2.5. Rounding introduces an error in the result that is less than one least-significant bit.

- The U-bit (Update Bit), if set in the value that is loaded into fsr by a st.c instruction, enables updating of the result-status bits (AE, AA, AI, AO, AU, MA, MI, MO and MU) in the first-stage of the floating-point adder and multiplier pipelines. If this bit is clear, the result-status bits are unaffected by a st.c instruction; st.c ignores the corresponding bits in the value that is being loaded. A st.c always updates fsr bits 21..17 and 8..0 directly. The U-bit does not remain set; it always appears as zero when read.

- The FTE (Floating-Point Trap Enable) bit, if clear, disables all floating-point traps (invalid input operand, overflow, underflow, and inexact result).

- SI (Sticky Inexact) is set when the last stage result of either the multiplier or adder is inexact (i.e. when either AI or MI is set). SI is "sticky" in the sense that it remains set until reset by software. AI and MI, on the other hand, can by changed by the subsequent floating-point instruction.

- SE (Source Exception) is set when one of the source operands of a floating-point operation is invalid; it is cleared when all the input operands are valid. Invalid input operands include denormals, infinities, and all NaNs (both quiet and signaling).

- When read from the fsr, the result-status bits MA, MI, MO, and MU (Multiplier Add-One, Inexact, Overflow and Underflow, respectively) describe the last stage result of the multiplier.

When read from the fsr, the result-status bits AA, AI, AO, AU, and AE (Adder Add-One, Inexact, Overflow, Underflow and Exponent, respectively) describe the last stage result of the adder. The high-order three bits of the 11-bit exponent of the adder result are stored in the AE field.

The Adder Add One and Multiplier Add One bits indicate that the absolute value of the result frac-

tion grew by one least-significant bit due to rounding. AA and MA are not influenced by the sign of the result.

After a floating-point operation in a given unit (adder or multiplier), the result-status bits of that unit are undefined until the point at which result exceptions are reported.

When written to the **fsr** with the U-bit set, the result-status bits are placed into the first stage of the adder and multiplier pipelines. When the processor executes pipelined operations, it propagates the result-status bits of a particular unit (multiplier or adder) one stage for each pipelined floating-point operation for that unit. When they reach the last stage, they replace the normal result-status bits in the **fsr**. When the U-bit is not set, result-status bits in the word being written to the **fsr** are ignored.

In a floating-point dual-operation instruction (e.g. add-and-multiply) or subtract-and-multiply), both the multiplier and the adder may set exception bits. The result-status bits for a particular unit remain set until the next operation that uses that unit.

- RR (Result Register) specifies which floatingpoint register (f0-f31) was the destination register when a result-exception trap occurs due to a scalar operation.

- LRP (Load Pipe Result Precision), IRP (Integer (Graphics) Pipe Result Precision), MRP (Multiplier Pipe Result Precision) and ARP (Adder Pipe Result Precision) aid in restoring pipeline state after a trap or process switch. Each defines the precision of the last stage result in the corresponding pipeline. One of these bits is set when the result in the last stage of the corresponding pipeline is double precision; it is cleared if the result is single precision. These bits cannot be changed by software.

#### 2.2.9 KR, KI, T AND MERGE REGISTERS

The KR, KI, and T registers are special-purpose registers used by the dual-operation floating-point instructions **pfam**, pfmam, pfsm and **pfmsm**, which

9-16

initiate both an adder (A-unit) operation and a multiplier (M-unit) operation. The KR, KI and T registers can store values from one dual-operation instruction and supply them as inputs to subsequent dual-operation instructions. (Refer to Figure 2.14.)

The MERGE register is used only by the graphics instructions. The purpose of the MERGE register is to accumulate (or merge) the results of multiple-addition operations that use as operands the color-intensity values from pixels or distance values from a Z-buffer. The accumulated results can then be stored in one 64-bit operation.

Two multiple-addition instructions and an OR instruction use the MERGE register. The addition instructions are designed to add interpolation values to each color-intensity field in an array of pixels or to each distance value in a Z-buffer.

Refer to the instruction descriptions in Section 7 for more information about these registers.

# 2.3 Addressing

Memory is addressed in byte units within a paged virtual-address space of 2<sup>32</sup> bytes. Data and instructions can be located anywhere in this address space. Address arithmetic is performed using 32-bit input values and produces 32-bit results. The low-order 32 bits of the result are used in case of overflow.

Normally, multibyte data values are stored in memory in little endian format, i.e., with the least significant byte at the lowest memory address. As an option, the ordering can be dynamically selected by software in supervisor mode. The Military i860 XR microprocessor also offers big endian mode, in which the most significant byte of a data item is at the lowest address. Figure 2.8 shows the difference between the two storage modes. Big endian and little endian data areas should not be mixed within a 64-bit data word. Illustrations of data structures in this data sheet show data stored in little endian mode, i.e., the rightmost (low-order) byte is at the lowest memory address.

### MILITARY 1860TM XR MICROPROCESSOR

Code accesses are always done with little endian addressing. This implies that code will appear differently than documented here when accessed as big endian data. Intel recommends that disassemblers running in a big endian system, convert instructions which have been read as data back to little endian form and present them in the format documented here.

Page directories and page tables are also accessed in little endian mode, regardless of the value of the BE bit.

Alignment requirements are as follows (any violation results in a data-access trap):

- 128-bit values are aligned on 16-byte boundaries when referenced in memory (i.e. the four least significant address bits must be zero).

- 64-bit values are aligned on 8-byte boundaries when referenced in memory (i.e. the three least significant address bits must be zero).

- 32-bit values are aligned on 4-byte boundaries when referenced in memory (i.e. the two least significant address bits must be zero).

- 16-bit values are aligned on 2-byte boundaries when referenced in memory (i.e. the least significant address bit must be zero).

## 2.4 Virtual Addressing

When address translation is enabled, the Military i860 XR microprocessor maps instruction and data virtual addresses into physical addresses before referencing memory. This address transformation is compatible with that of the Military 386 microprocessor and implements the basic features needed for page-oriented virtual-memory systems and pagelevel protection.

The address translation is optional. Address translation is in effect only when the ATE bit of **dirbase** is set. This bit is typically set by the operating system during software initialization. The ATE bit must be set if the operating system is to implement page-oriented protection or page-oriented virtual memory.

PRELIMINARY

Figure 2.8 Little and Big Endian Accesses

# MILITARY i860™ XR MICROPROCESSOR

Figure 2.9 Format of a Virtual Address

Address translation is disabled when the processor is reset. It is enabled when a store to **dirbase** sets the ATE bit. It is disabled again when a store clears the ATE bit.

#### 2.4.1 PAGE FRAME

A page frame is a 4-Kbyte unit of contiguous addresses of physical main memory. Page frames begin on 4-Kbyte boundaries and are fixed in size. A page is the collection of data that occupies a page frame when that data is present in main memory. The data may also occupy some location in secondary storage when there is not sufficient space in main memory.

#### 2.4.2 VIRTUAL ADDRESS

A virtual address refers indirectly to a physical address by specifying a page table, a page within that table, and an offset within that page. Figure 2.9 shows the format of a virtual address.

Figure 2.10 shows how the Military i860 XR microprocessor converts the DIR, PAGE, and OFFSET fields of a virtual address into the physical address by consulting two levels of page tables. The addressing mechanism uses the DIR field as an index into a page directory, uses the PAGE field as an index into the page table determined by the page directory, and uses the OFFSET field to address a byte within the page determined by the page table.

#### 2.4.3 PAGE TABLES

A page table is simply an array of 32-bit page specifiers. A page table is itself a page, and therefore contains 4 Kbytes of memory or at most 1K 32-bit entries.

Two levels of tables are used to address a page of memory. At the higher level is a page directory. The page directory addresses up to 1K page tables of the second level. A page table of the second level addresses up to 1K pages. All the tables addressed by one page directory, therefore, can address 1M pages ( $2^{20}$ ). Because each page contains 4 Kbytes ( $2^{12}$  bytes), the tables of one page directory can span the entire physical address space of the Miltary i860 XR microprocessor ( $2^{20} \times 2^{12} = 2^{32}$ ).

The physical address of the current page directory is stored in DTB field of the **dirbase** register. Memory management software has the option of using one page directory for all processes, one page directory for each process, or some combination of the two.

Figure 2.10 Address Translation

Preliminary

#### 2.4.4 TABLE ENTRIES

Table entries in either level of page tables have the same general format. Figure 2.11 illustrates this format for a page-directory entry and a page-table entry.

# 2.4.4.1 Page Frame Address Generation

The page frame address specifies the physical starting address of a page Because pages are located on 4K boundaries, the low-order 12 bits are always zero. In a page directory, the page table address is the address of a page table. In a second-level page table, the page frame address is the address of the page frame that contains the desired memory operand.

#### 2.4.4.2 Present Bit

The P (present) bit indicates whether a page table entry can be used in address translation. P=1 indicates that the entry can be used. When P=0 in either level of page tables, the entry is not valid for address translation, and the rest of the entry is available for software use; none of the other bits in the entry are tested by the hardware. If P=0 in either level of page tables when an attempt is made to use a page-table entry for address translation, the processor signals either a data-access fault or an in-

struction-access fault. In software systems that support paged virtual memory, the trap handler can bring the required page into physical memory.

Note that there is no P bit for the page directory itself. The page directory may be not-present while the associated process is suspended, but the operating system must ensure that the page directory indicated by the dirbase image associated with the process is present in physical memory before the process is dispatched.

#### 2.4.4.3 Writable and User Bits

The W (writable) and U (user) bits are used for pagelevel protection, which the Military i860 XR microprocessor performs at the same time as address translation. The concept of privilege for pages is implemented by assigning each page to one of two levels:

- Supervisor level (U = 0)—for the operating system and other systems software and related data.

- User level (U = 1)—for applications procedures and data.

The U bit of the psr indicates whether the Military i860 XR microprocessor is executing at user or supervisor level. The Military i860 XR microprocessor maintains the U bit of psr as follows:

Figure 2.11 Format of a Page-Table and Page-Directory Entry

9-20

#### MILITARY 1860TM XR MICROPROCESSOR

# int<sub>e</sub>l.

- The Military i860 XR microprocessor clears the psr U bit to indicate supervisor level when a trap occurs (including when the trap instruction causes the trap). The prior value of U is copied into PU.

- The Military i860 XR microprocessor copies the psr PU bit into the U bit when an indirect branch is executed and one of the trap bits is set. If PU was one, the Military i860 XR microprocessor enters user level.

With the U bit of **psr** and the W and U bits of the page table entries, the Military i860 XR microprocessor implements the following protection rules:

- When at user level, a read or write of a supervisor-level page causes a trap.

- When at user level, a write to a page whose W bit is clear causes a trap.

- When at user level, st.c to certain control registers is ignored.

When the Military i860 XR microprocessor is executing at supervisor level, all pages are addressable, but, when it is executing at user level, only pages that belong to the user-level are addressable

When the Military i860 XR microprocessor is executing at supervisor level, all pages are readable. Whether a page is writable depends upon the write-protection mode controlled by WP bit of **epsr**.

WP = 0 All pages are writable.

WP = 1 A write to a page whose W bit is clear causes a trap.

When the Military i860 XR microprocessor is executing at user level, only pages that belong to user level and are marked writable are actually writable; pages that belong to supervisor level are neither readable nor writable from user level.

#### 2.4.4.4 Write-Through Bit

The Military i860 XR microprocessor does not implement a write-through caching policy for the on-chip data cache; however, the WT (write-through) bit in the second-level page-table entry does determine internal caching policy. If WT is set in a PTE, on-chip caching of data from the corresponding page is inhibited. The Military i860 CPU may place pages having WT = 1 into the instruction cache Future implementations of the Military i860 architecture may adhere to a write-through data caching policy. Therefore, they may cache pages having the WT bit of the PTE set If WT is clear, the normal write-back policy is applied to data from the page in the on-chip caches. The WT bit of page directory entries is not referenced by the processor, but is **reserved**.

The WT bit is independent of the CD bit; therefore, data may be placed in a second-level coherent cache, but kept out of the on-chip caches.

2.4.4.5 Cache Disable Bit

If the CD (cache disable) bit in the second-level page-table entry is set, data from the associated page is not placed in instruction or data caches. Clearing CD permits the cache hardware to place data from the associated page into caches. The CD bit of page directory entries is not referenced by the processor, but is **reserved.**

To control external caches, the Military i860 XR microprocessor outputs on its PTB pin either the CD or WT bit. The PBM bit of **epsr** determines which bit is output.

#### 2.4.4.6 Accessed and Dirty Bits

The A (accessed) and D (dirty) bits provide data about page usage in both levels of the page tables.

The Military i860 XR microprocessor sets the corresponding accessed bits in both levels of page tables before a read or write operation to a page. The processor tests the dirty bit in the second-level page table before a write to an address covered by that page table entry, and, under certain conditions, causes traps. The trap handler then has the opportunity to maintain appropriate values in the dirty bits. The dirty bit in directory entries is not tested by the Military i860 XR microprocessor. The precise algorithm for using these bits is specified in Section 2.4.5.

An operating system that supports paged virtual memory can use these bits to determine what pages to eliminate from physical memory when the demand for memory exceeds the physical memory available. The D and A bits in the PDE (Page-Directory Entry) or the PTE (Page-Table Entry) are normally initialized to zero by the operating system. The processor sets the A bit when a page is accessed either by a read or write operation. When a data- or instruction-access fault occurs, the trap handler sets the D bit if an allowable write is being performed, then re-executes the instruction.

The operating system is responsible for coordinating its updates to the accessed and dirty bits with updates by the CPU and by other processors that may share the page tables. The Military i860 XR microprocessor automatically asserts the LOCK signal while setting the A bit. If an A-bit of a PTE is found not set during a locked sequence (created by the lock instruction), a trap will occur and the processor will not update the A-bit.

# 2.4.4.7 Combining Protection of Both Levels of Page Tables

For any one page, the protection attributes of its page directory entry may differ from those of its page table entry. The Military i860 XR microprocessor computes the effective protection attributes for a

PRELIMINARY

page by examining the protection attributes in both the directory and the page table. Table 2.6 shows the effective protection provided by the possible combinations of protection attributes.

#### 2.4.5 ADDRESS TRANSLATION ALGORITHM

Referring to Figure 2-10, the algorithm below defines the translation of each virtual address to a physical address. Let DIR, PAGE, and OFFSET be the fields of the virtual address; let PTA be the page table address and PFA be the page frame address of the first and second level page tables respectively; DTB is the page directory table base address stored in the dirbase register.

- Read the PDE (Page Directory Entry) at the physical address formed by DTB:DIR:00.

- If P in the PDE is zero, generate a data- or instruction-access fault.

- If W in the PTE is zero, the operation is a write, and either the U-bit of the PSR is set or WP = 1, generate a data or instruction access fault.

- If the U-bit in the PDE is zero and the U-bit in the psr is set, generate a data or instruction access fault.

- 5. If A in the PDE is zero, and if the TLB miss occurred while the bus was locked, generate a data or instruction access fault. (The trap allows software to set A to one and restart the sequence. This avoids ambiguity in determining what address corresponds to a locked semaphore for external bus hardware use.)

- 6. If A in the PDE is zero, and if the TLB miss occurred while the bus was not locked, assert LOCK. Re-fetch and check the PDE, set A, and store the PDE. Deassert LOCK during the store.

- Locate the PTE (Page Table Entry) at the physical address formed by PTA:PAGE:00.

- 8. Perform the P, W, U and A checks as in steps 2 through 6 with the second-level PTE.

- If D in the PTE is clear and the operation is a write, generate a data or instruction access fault.

- 10. Form the physical address as PFA:OFFSET.

The Military i860 XR microprocessor looks only in external memory for Page Directories and Page Tables, in the translation process. The data cache is not searched. Therefore, any code which modifies Page Directories or Page Tables must keep them out of the cache. The tables should be kept in non-cacheable memory, or flushed from the cache.

**Table 2.6 Combining Directory and Page Protections**

| Page D | Page Directory Page Table Combined |       | Page Table<br>Entry |        | mbined Protecti | on     |

|--------|------------------------------------|-------|---------------------|--------|-----------------|--------|

| _      | Entry                              |       |                     |        | Super<br>Acc    |        |

| U-bit  | W-bit                              | U-bit | W-bit               | WP = X | WP = 0          | WP = 1 |

| 0      | 0                                  | 0     | 0                   | N      | R/W             | R      |

| 0      | 0                                  | 0     | 1                   | N      | R/W             | R      |

| 0      | 0                                  | 1     | 0                   | N      | R/W             | R      |

| 0      | 0                                  | 1     | 1                   | N      | R/W             | R      |

| 0      | 1                                  | 0     | 0                   | N      | R/W             | R      |

| 0      | 1                                  | 0     | 1                   | N      | R/W             | R/W    |

| 0      | 1                                  | 1     | 0                   | N      | R/W             | R      |

| 0      | 1                                  | 1     | 1                   | N      | R/W             | R/W    |

| 1      | 0                                  | 0     | 0                   | N      | R/W             | R      |

| 1      | 0                                  | 0     | 1                   | N      | R/W             | R      |

| 1      | 0                                  | 1     | 0                   | R      | R/W             | R      |

| 1      | 0                                  | 1     | 1                   | R      | R/W             | R      |

| 1      | 1                                  | 0     | 0                   | N      | R/W             | R      |

| 1      | 1                                  | 0     | 1                   | N      | R/W             | R/W    |

| 1      | 1                                  | 1     | 0                   | R      | R/W             | R      |

| 1      | 1                                  | 1     | 1                   | R/W    | R/W             | R/W    |

#### NOTES:

N = No access allowed

R/W = Both reads and writes allowed

R = Read access only

X = Don't care

9-22

The Military i860 XR microprocessor expects Page Directories and Page Tables to be in little endian format. The operating system must maintain these tables in little endian format by either setting BE = 0 when manipulating the tables or by complementing bit 2 of the address when loading or storing entries.

#### 2.4.6 ADDRESS TRANSLATION FAULTS

The address translation fault is one instance of the data-access fault. The instruction causing the fault can be re-executed upon returning from the trap handler.

#### 2.4.7 PAGE TRANSLATION CACHE

For greatest efficiency in address translation, the Military i860 XR microprocessor stores the most recently used page-table data in an on-chip cache called the TLB (translation lookaside buffer). Only if the necessary paging information is not in the cache must both levels of page tables be referenced.

## 2.5 Caching and Cache Flushing

The Military i860 XR microprocessor has the ability to cache instruction, data, and address-translation information in on-chip caches. Caching uses virtual-address tags. The effects of mapping two different virtual addresses in the same address space to the same physical address are undefined.

Instruction, data and address-translation caching on the i860 XR microprocessor are not transparent. Because the data cache uses a write-back protocol, writes do not immediately update memory, and writes to memory by other bus devices do not update the cache. Changes to page tables do not automatically update the TLB, and changes to instructions do not automatically update the instruction cache. Under certain circumstances, such as I/O references, self-modifying code, page-table updates or shared data in a multiprocessing system, it is necessary to bypass or to flush the caches. The The i860 XR microprocessor provides the following methods for doing this:

Bypassing Instruction and Data Caches. If deasserted during cache-miss processing, the KEN pin disables instruction and data caching of the referenced data. If the CD bit of the associat-

#### MILITARY 1860TM XR MICROPROCESSOR

ed second-level PTE is set, caching of data and instructions is disabled. The Military i860 CPU may place pages having WT = 1 into the instruction cache. Future implementations of the Military i860 architecture may adhere to a write-through data cache policy. Thus, they may cache pages having the WT bit of the PTE set. The value of the CD bit or the WT bit is output on the PTB pin for use by external caches.

• Flushing Instruction and Address-Translation Caches. Storing to the dirbase register with the ITI bit set invalidates the contents of the instruction and address-translation caches. This bit should be set when a page table or a page containing code is modified or when changing the DTB field of dirbase. Note that in order to make the instruction or address-translation caches consistent with the data cache, the data cache must be flushed before invalidating the other caches.

The mapping of the page containing the currently executing instruction and the next six instructions should not be different in the new page tables when **st.c** dirbase changes DTB or activates ITI. The six instructions following the **st.c** should be **nops** and should lie in the same page as the **st.c**.

Flushing the Data Cache. The data cache is flushed by a software routine using the flush instruction. The data cache must be flushed prior to flushing the instruction or address-translation caches (as controlled by the ITI bit of dirbase) or enabling or disabling address translation (via the ATE bit). The data cache does not need flushing if the program is modifying only the P, U, W, A, or D bits of a PDE or PTE (as long as the Page Table or Page Frame Address is not changed and the entry itself was not in the data cache.) The Military i860 CPU does not check these protection bits on cache line writeback. Thus, a trap handler can service a Data Access Fault for Dbit-zero by setting D = 1 and then ITI = 1. In the case of setting the P or A bits active, there is no need to invalidate or flush any caches because the processor does not load entries into the TLB that have P = 0 or A = 0. The Military i860 XR microprocessor searches only external memory for Page Directories and Page Tables in the translation process. The data cache is not searched. Therefore, Page Tables and Directories should be kept in non-cacheable memory, or flushed from the cache by any code which ac-

# 2.6 Instruction Set

Table 2.7 shows the complete set of instructions grouped by function and data type. Refer to Section 7 for an algorithmic definition of each instruction.

The architecture of the Military i860 XR microprocessor uses parallelism to increase the rate at which operations may be introduced into the unit. Parallelism in the Military i860 XR microprocessor is **not** transparent; rather, programmers have complete control over parallelism and therefore can achieve maximum performance for a variety of computational problems.

#### 2.6.1 PIPELINED AND SCALAR OPERATIONS

One type of parallelism used within the floating-point unit is "pipelining". The pipelined architecture treats each operation as a series of more primitive operations (called "stages") that can be executed in parallel. Consider just the floating-point adder unit as an example. Let  $\mathbf{A}$  represent the operation of the adder. Let the stages be represented by  $\mathbf{A_1}$ ,  $\mathbf{A_2}$ , and  $\mathbf{A_3}$ . The stages are designed such that  $\mathbf{A_{i+1}}$  for one adder instruction can execute in parallel with  $\mathbf{A_i}$  for the next adder instruction. Furthermore, each  $\mathbf{A_i}$  can be executed in just one clock. The pipelining within the multiplier and graphics units can be described similarly, except that the number of stages may be different

Figure 2.12 illustrates three-stage pipelining as found in the floating-point adder (also in the floatingpoint multiplier when single-precision input operands are employed). The columns of the figure represent the three stages of the pipeline. Each stage holds intermediate results and also (when introduced into first stage by software) holds status information pertaining to those results. The figure assumes that the instruction stream consists of a series of consecutive floating-point instructions, all of one type (i.e. all adder instructions or all single-precision multiplier instructions). The instructions are represented as I,  $\mathbf{i}+\mathbf{1}$ , etc. The rows of the figure represent the states of the unit at successive clock cycles. Each time a pipelined operation is performed, the result of the last stage of the pipeline is stored in the destination register fdest, the pipeline is advanced one stage. and the input operands src1 and src2 are transferred to the first stage of the pipeline.

In the Military i860 XR microprocessor, the number of pipeline stages ranges from one to three. A pipelined operation with a three-stage pipeline stores the result of the third prior operation. A pipelined operation with a two-stage pipeline stores the result of the second prior operation. A pipelined operation with a one-stage pipeline stores the result of the prior operation.

There are four floating-point pipelines: one for the multiplier, one for the adder, one for the graphics unit, and one for floating-point loads. The adder pipeline has three stages. The number of stages in the multiplier pipeline depends on the precision of the source operands in the pipeline. Single precision has three stages and double precision has two stages. The graphics unit has one stage for all precisions. The load pipeline has three stages for all precisions.

Changing the FZ (flush zero), RM (rounding mode), or RR (result register) bits of **fsr** while there are results in either the multiplier or adder pipeline produces effects that are not defined.

#### 2.6.1.1 Scalar Mode

In addition to the pipelined execution mode, the Military i860 XR microprocessor also can execute floating-point instructions in "scalar" mode. Most floating-point instructions have both pipelined and scalar variants, distinguished by a bit in the instruction encoding. In scalar mode, the floating-point unit does not start a new operation until the previous floating-point operation is completed. The scalar operation passes through all stages of its pipeline before a new operation is introduced, and the result is stored automatically. Scalar mode is used when the next operation depends on results from the previous floating-point operations (or when the compiler or programmer does not want to deal with pipelining).

#### 2.6.1.2 Pipelining Status Information

Result status information in the **fsr** consists of the AA, AI, AO, AU and AE bits, for the adder, and the MA, MI, MO and MU bits, for the multiplier. This information arrives at the **fsr** via the pipeline in one of two ways:

9-24

# intel.

# MILITARY i860™ XR MICROPROCESSOR

# Table 2.7 Instruction Set

|                                                                                                                                                                                                                                                                                                                      | Core Unit                                                                                                            |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Mnemonic                                                                                                                                                                                                                                                                                                             | Description                                                                                                          |  |  |  |

| Load and St                                                                                                                                                                                                                                                                                                          | ore Instructions                                                                                                     |  |  |  |

| ld.x<br>st.x<br>fld.y<br>pfld.z<br>fst.y<br>pst.d                                                                                                                                                                                                                                                                    | Load integer Store integer F-P load Pipelined F-P load F-P store                                                     |  |  |  |

| <del></del>                                                                                                                                                                                                                                                                                                          | Pixel store Register Moves                                                                                           |  |  |  |

| ixfr<br>fxfr                                                                                                                                                                                                                                                                                                         | Transfer integer to F-P register<br>Transfer F-P to integer register                                                 |  |  |  |

| Integer Arit                                                                                                                                                                                                                                                                                                         | hmetic Instructions                                                                                                  |  |  |  |

| addu<br>adds<br>subu<br>subs                                                                                                                                                                                                                                                                                         | Add unsigned<br>Add signed<br>Subtract unsigned<br>Subtract signed                                                   |  |  |  |

| Shift Instru                                                                                                                                                                                                                                                                                                         | ctions                                                                                                               |  |  |  |

| shl<br>shr<br>shra<br>shrd                                                                                                                                                                                                                                                                                           | shr Shift right shra Shift right arithmetic                                                                          |  |  |  |

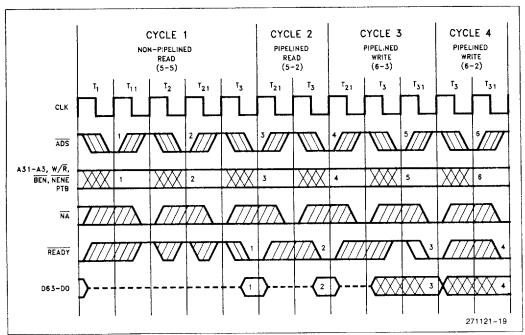

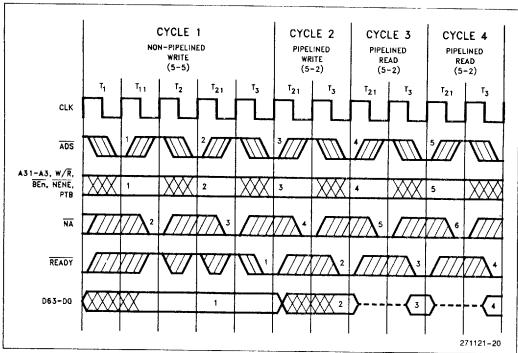

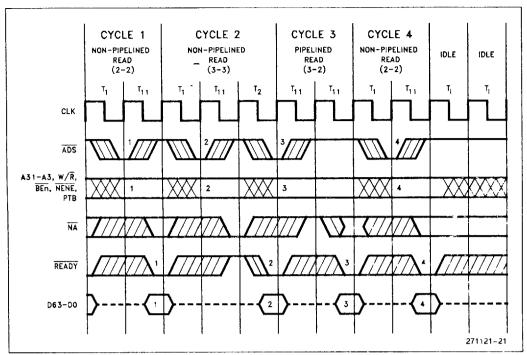

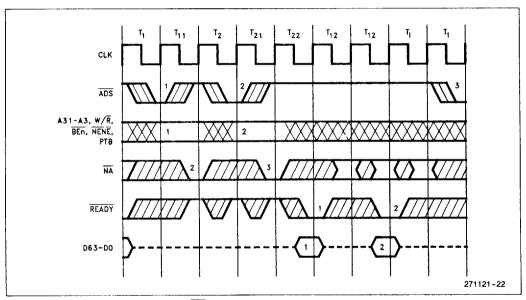

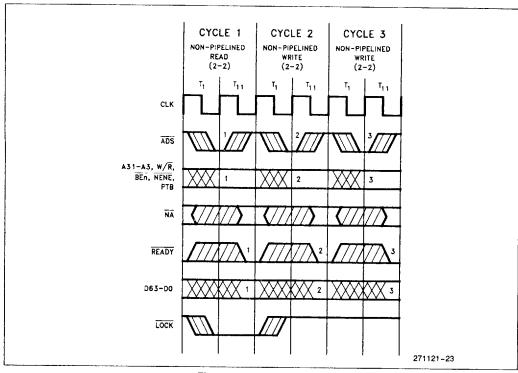

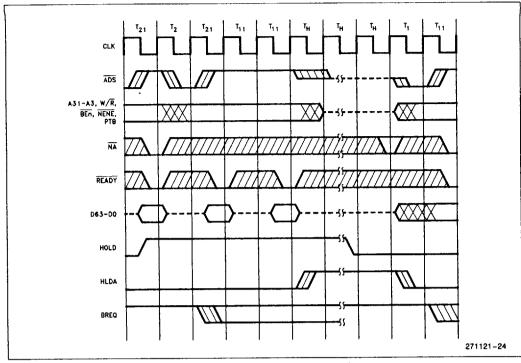

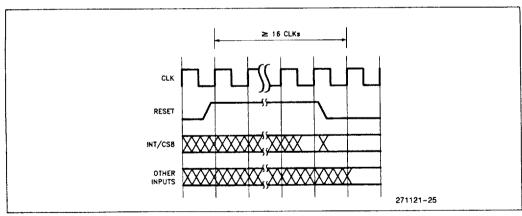

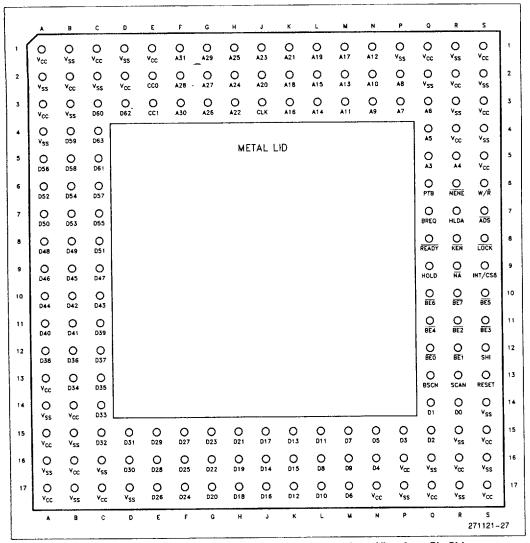

| Logical Inst                                                                                                                                                                                                                                                                                                         | tructions                                                                                                            |  |  |  |