Click here to ask an associate for production status of specific part numbers.

# 65V, 7.6A High Current Single H-Bridge with Integrated Current-Sense

#### **General Description**

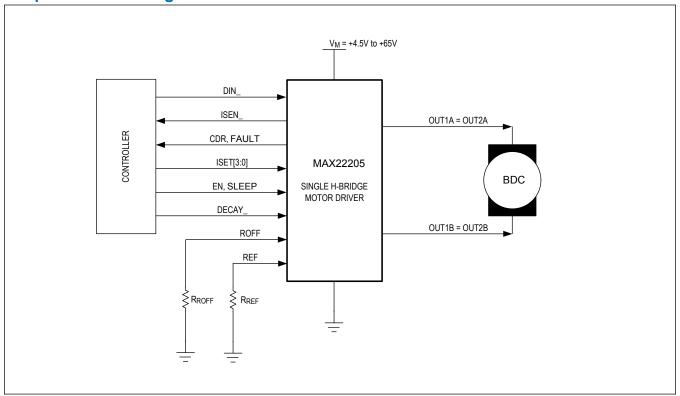

The MAX22205 integrates a high current 65V, 7.6A<sub>MAX</sub> H-Bridge to drive one Brushed DC motor or one half Stepper motor. The H-Bridge FETs feature very low impedance, resulting in high driving efficiency and low heat. The typical total  $R_{ON}$  (high-side + low-side) is 0.15 $\Omega$ . The H-Bridge can be PWM controlled by two logic inputs (DINA, DINB). A third Enable (EN) logic input can be used to configure the outputs to high impedance for coasting the motor.

The MAX22205 features an accurate optional Current Drive Regulation (CDR), which can be used to limit the start up current of a Brushed DC motor or control the phase current for stepper operation. The bridge output current is sensed by a non-dissipative Integrated Current Sensing (ICS) and it is then compared with the desired threshold current. As soon as the bridge current exceeds the threshold (ITRIP), the device enforces the decay for a fixed OFFtime (t<sub>OFF</sub>). The non-dissipative ICS eliminates the bulky external power resistors normally required for this function, resulting in a dramatic space and power saving compared with mainstream applications based on the external sense resistor. A current proportional to the internally-sensed motor current is output to the analog pins (ISE-NA, ISENB) to monitor current. Also, one open-drain output (CDR pin) is asserted every time the internal current regulation is taking control of the driver so that the activity of the internal current loop can be monitored.

The maximum output current per H-Bridge is  $I_{MAX} = 7.6A_{MAX}$  limited by the Overcurrent Protection (OCP). The device delivers up to 4ARMS at VM = +24V and TA = 25°C with proper PCB ground plane for thermal dissipation. The current capability depends on the PCB thermal characteristic (PCB ground planes, heatsinks, ventilation, etc.).

The MAX22205 features Overcurrent Protection (OCP), Thermal Shutdown (TSD), and <u>Undervoltage</u> Lockout (UVLO). An open-drain active low FAULT pin is activated every time a fault condition is detected. During Thermal Shutdown and Undervoltage Lockout, all the channels are disabled until normal operating conditions are restored.

The MAX22205 is packaged into a small TQFN38 5mm x 7mm package.

#### **Applications**

- Brushed DC Motor Driver

- Stepper Motor Driver

- Solenoid Driver

- Latched Valves

#### **Benefits and Features**

- One H-Bridge with +65V Voltage Rating

- Total R<sub>DS(ON)</sub> (High-Side + Low-Side): 150mΩ Typical (T<sub>A</sub> = 25°C)

- Current Ratings per H-Bridge (Typical at 25°C):

- I<sub>MAX</sub> = 7.6A<sub>MAX</sub> (Impulsive Current for Driving Capacitive Loads)

- I<sub>FS</sub> = 6A (Max Full Scale Current Setting for Internal Current Drive Regulation)

- I<sub>RMS</sub> = 4A<sub>RMS</sub> (T<sub>A</sub> = 25°C, V<sub>M</sub> = +24V)

- Integrated Current Control

- Full-Scale DAC Current Configurable with External Resistance

- Internal Current Sensing (ICS) Eliminates External Bulky Resistors and Improves Efficiency

- Current Drive Regulation Monitor Output Pin (CDR Pin)

- Integrated DAC Sets the Output Current Level among 16 Values

- · Multiple Decay Modes (Slow, Mixed, Fast)

- Fixed OFF Time Configurable with External Resistance

- Current-Sense Output (Current Monitor)

- Fault Indicator Pin (FAULT)

- Protections

- Overcurrent Protection for each Individual Channel (OCP)

- Undervoltage Lockout (UVLO)

- Thermal Shutdown T<sub>.1</sub> = 155°C (TSD)

- TQFN38 5mm x 7mm Package (TSSOP38 4.4mm x 9.7mm Available in the Future)

Ordering Information appears at end of data sheet.

19-101140A; Rev 0; 8/21

# **Simplified Block Diagram**

# 65V, 7.6A High Current Single H-Bridge with Integrated Current-Sense

## **TABLE OF CONTENTS**

| General Description                            | . 1 |

|------------------------------------------------|-----|

| Applications                                   | . 1 |

| Benefits and Features                          | . 1 |

| Simplified Block Diagram                       | . 2 |

| Absolute Maximum Ratings                       | . 6 |

| Package Information                            | . 6 |

| TQFN 38 - 5mm x 7mm                            | . 6 |

| Electrical Characteristics                     | . 6 |

| Pin Configuration                              | . 9 |

| Pin Configuration                              | . 9 |

| Pin Description                                | . 9 |

| Functional Diagrams                            | 11  |

| Detailed Description                           | 12  |

| Sleep Mode (SLEEP Pin)                         | 12  |

| PWM Control                                    | 12  |

| Current-Sense Output (CSO) - Current Monitor   | 13  |

| Current Drive Regulation                       | 15  |

| Integrated Current-Sense (ICS)                 | 15  |

| Setting the Full-Scale Current – Pin REF       | 15  |

| Bridge Current Control                         | 15  |

| Setting the Fixed OFF_TIME (t <sub>OFF</sub> ) | 16  |

| CDR Open-Drain Output                          | 16  |

| Operating Modes                                | 17  |

| Setting the Decay Mode                         | 18  |

| Protections                                    | 18  |

| Overcurrent Protection – (OCP)                 | 18  |

| Thermal Shutdown Protection (TSD)              | 19  |

| Undervoltage Lockout Protection (UVLO)         | 19  |

| Ordering Information                           | 20  |

| Revision History                               | 21  |

# 65V, 7.6A High Current Single H-Bridge with Integrated Current-Sense

| LIST OF FIGURES                                  |    |

|--------------------------------------------------|----|

| Figure 1. ISEN Current                           | 14 |

| Figure 2. CDR Monitor Timing Diagram             | 1  |

| Figure 3. Current Flow During ON and Decay Modes | 18 |

# 65V, 7.6A High Current Single H-Bridge with Integrated Current-Sense

| LIST OF TABLES                          |      |

|-----------------------------------------|------|

| Table 1. MAX22205 Truth Table           | . 12 |

| Table 2. H-Bridge ISET Pins Truth Table | . 15 |

| Table 3. Decay Mode Truth Table         | . 18 |

#### **Absolute Maximum Ratings**

| V 4- OND               | 0.0)//70)/                                               | DOFF IS OND                    | 1                                      |

|------------------------|----------------------------------------------------------|--------------------------------|----------------------------------------|

| VM to GND              | 0.3V to +70V                                             | ROFF to GND0.3V                | to min (+2.2V, V <sub>DD</sub> + 0.3V) |

| V <sub>DD</sub> to GND | 0.3V to min (+2.2V, V <sub>M</sub> + 0.3V)               | ISEN_ to GND0.3                | to min (+2.2V, $V_{DD}$ + 0.3V)        |

| PGND to GND            | 0.3V to +0.3V                                            | DIN_ to GND                    | 0.3V to 6V                             |

| OUT                    | 0.3V to V <sub>M</sub> + 0.3V                            | EN to GND                      | 0.3V to 6V                             |

| V <sub>CP</sub> to GND | V <sub>M</sub> - 0.3V to min (+74V, V <sub>M</sub> + 6V) | DECAY_ to GND                  | 0.3V to 6V                             |

| C <sub>P2</sub> to GND | V <sub>M</sub> - 0.3V to V <sub>CP</sub> + 0.3V          | SLEEP to GND0.3                | $V \text{ to min (+70V, } V_M + 0.3V)$ |

| C <sub>P1</sub> to GND | 0.3V to V <sub>M</sub> + 0.3V                            | Operating Temperature Range    | 40°C to 125°C                          |

| FAULT to GND           | 0.3V to 6V                                               | Junction Temperature           | +150°C                                 |

| CDR to GND             | 0.3V to 6V                                               | Storage Temperature Range      | 65°C to +150°C                         |

| ISET_ to GND           | 0.3V to 6V                                               | Soldering Temperature (Reflow) | 260°C                                  |

| REF to GND             | 0.3V to min (+2.2V, V <sub>DD</sub> + 0.3V)              | . , , ,                        |                                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### **TQFN 38 - 5mm x 7mm**

| T3857-1C                              |  |  |  |  |

|---------------------------------------|--|--|--|--|

| <u>21-0172</u>                        |  |  |  |  |

| <u>90-0076</u>                        |  |  |  |  |

|                                       |  |  |  |  |

| 38°C/W                                |  |  |  |  |

| 1°C/W                                 |  |  |  |  |

| Thermal Resistance, Four-Layer Board: |  |  |  |  |

| 28°C/W                                |  |  |  |  |

| 1°C/W                                 |  |  |  |  |

|                                       |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(V<sub>M</sub> = from +4.5V to +65V, R<sub>ROFF</sub> = from 15k $\Omega$  to 120k $\Omega$  , R<sub>REF</sub> = from 13k $\Omega$  to 60k $\Omega$ ,

Limits are 100% tested at TA = +25°C. Limits over the operating temperature range are guaranteed by design and characterization.

| PARAMETER                        | SYMBOL                | CONDITIONS                                       | MIN | TYP           | MAX | UNITS |  |

|----------------------------------|-----------------------|--------------------------------------------------|-----|---------------|-----|-------|--|

| POWER SUPPLY                     | POWER SUPPLY          |                                                  |     |               |     |       |  |

| Supply Voltage Range             | V <sub>M</sub>        |                                                  | 4.5 |               | 65  | V     |  |

| Sleep Mode Current consumption   | I <sub>VM</sub>       | SLEEP = logic low                                |     |               | 20  | μΑ    |  |

| Quiescent Current<br>Consumption | I <sub>VM</sub>       | SLEEP = logic high                               |     |               | 5   | mA    |  |

| 1.8V Regulator Output Voltage    | V <sub>VDD</sub>      | V <sub>M</sub> = +4.5V, I <sub>LOAD</sub> = 20mA |     | 1.8           |     | V     |  |

| V <sub>DD</sub> Current Limit    | I <sub>VDD(LIM)</sub> | V <sub>DD</sub> shorted to GND                   | 18  |               |     | mA    |  |

| Charge Pump Voltage              | V <sub>CP</sub>       |                                                  |     | $V_{M} + 2.7$ |     | V     |  |

## **Electrical Characteristics (continued)**

(V<sub>M</sub> = from +4.5V to +65V, R<sub>ROFF</sub> = from 15k $\Omega$  to 120k $\Omega$  , R<sub>REF</sub> = from 13k $\Omega$  to 60k $\Omega$ ,

Limits are 100% tested at TA = +25°C. Limits over the operating temperature range are guaranteed by design and characterization.

, Typical Values are at  $V_M = 36V$  and  $TA = +25^{\circ}C$ )

| PARAMETER                                          | SYMBOL                 | CONDITIONS                   | MIN  | TYP   | MAX  | UNITS |

|----------------------------------------------------|------------------------|------------------------------|------|-------|------|-------|

| LOGIC LEVEL INPUTS-C                               | DUTPUTS                |                              |      |       |      |       |

| Input Voltage Level -<br>High                      | V <sub>IH</sub>        |                              | 1.2  |       |      | V     |

| Input Voltage Level -<br>Low                       | V <sub>IL</sub>        |                              |      |       | 0.65 | V     |

| Input Hysteresis                                   | V <sub>HYS</sub>       |                              |      | 110   |      | mV    |

| Pulldown Current                                   | I <sub>PD</sub>        | Logic supply $(V_L) = +3.3V$ | 16   | 34    | 60   | μA    |

| Open-Drain Output<br>Logic-Low Voltage             | V <sub>OL</sub>        | I <sub>LOAD</sub> = 5mA      |      |       | 0.4  | V     |

| Open-Drain Output<br>Logic-High Leakage<br>Current | ІОН                    | V <sub>PIN</sub> = +3.3V     | -1   |       | 1    | μA    |

| SLEEP Voltage Level<br>High                        | V <sub>IH(SLEEP)</sub> |                              | 0.9  |       |      | V     |

| SLEEP Voltage Level<br>Low                         | V <sub>IL(SLEEP)</sub> |                              |      |       | 0.6  | V     |

| SLEEP Pulldown Input<br>Resistance                 | R <sub>PD(SLEEP)</sub> |                              | 0.8  | 1.5   |      | МΩ    |

| <b>OUTPUT SPECIFICATIO</b>                         | NS                     |                              |      |       |      |       |

| Output ON-Resistance<br>Low-Side                   | RonLS                  | OUT1A = OUT1B, OUT2A = OUT2B |      | 0.075 | 0.15 | Ω     |

| Output ON-Resistance<br>High-Side RonHS            |                        | OUT1A = OUT1B, OUT2A = OUT2B |      | 0.075 | 0.15 | Ω     |

| Output Leakage                                     | I <sub>LEAK</sub>      | Driver OFF                   | -20  |       | +20  | uA    |

| Dead Time                                          | t <sub>DEAD</sub>      |                              |      | 100   |      | ns    |

| Output Slew Rate                                   | SR                     |                              |      | 300   |      | V/µs  |

| PROTECTION CIRCUITS                                |                        |                              |      |       |      |       |

| Overcurrent Protection<br>Threshold                | OCP                    |                              | 7.6  |       |      | А     |

| Overcurrent Protection Blanking Time               | t <sub>OCP</sub>       |                              |      | 2.2   | 3.5  | μs    |

| Autoretry OCP Time                                 | t <sub>RETRY</sub>     |                              |      | 3     |      | ms    |

| UVLO Threshold on V <sub>M</sub>                   | UVLO                   | V <sub>M</sub> rising        | 3.75 | 4     | 4.25 | V     |

| UVLO Threshold on VM<br>Hysteris                   | UVLO <sub>HYS</sub>    |                              |      | 0.12  |      | V     |

| Thermal Protection Threshold Temperature           | T <sub>SD</sub>        |                              |      | 155   |      | °C    |

| Thermal Protection<br>Temperature Hysteresis       | T <sub>SD_HYST</sub>   |                              |      | 20    |      | °C    |

| CURRENT REGULATION                                 | 1                      |                              |      |       |      |       |

| REF Pin Resistor Range                             | R <sub>REF</sub>       |                              | 12   |       | 60   | kΩ    |

| REF Output Voltage                                 | V <sub>REF</sub>       |                              |      | 900   |      | mV    |

#### **Electrical Characteristics (continued)**

(V<sub>M</sub> = from +4.5V to +65V, R<sub>ROFF</sub> = from 15k $\Omega$  to 120k $\Omega$  , R<sub>REF</sub> = from 13k $\Omega$  to 60k $\Omega$ ,

Limits are 100% tested at TA = +25°C. Limits over the operating temperature range are guaranteed by design and characterization.

, Typical Values are at  $V_M$  = 36V and TA = +25°C)

| PARAMETER                      | SYMBOL              | CONDITIONS                         |                                                                                                               | MIN | TYP   | MAX | UNITS |

|--------------------------------|---------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| Full-Scale Current<br>Constant | KIFS                |                                    |                                                                                                               |     | 72    |     | KV    |

| Current Trip Regulation        | DITRIP1             | - I <sub>FS</sub> = 6A (Note 1)    | I <sub>TRIP</sub> from 2.2A to 6A                                                                             | -6  |       | +6  | - %   |

| Accuracy                       | DITRIP2             | IFS - OA (Note 1)                  | I <sub>TRIP</sub> from 1A to 2.2A                                                                             | -10 |       | +10 | 70    |

| Fixed OFF – Time<br>Internal   | t <sub>OFF</sub>    | ROFF shorted to V <sub>D</sub>     | D                                                                                                             | 16  | 20    | 24  | μs    |

| Fixed OFF – Time<br>Constant   | KTOFF               | $R_{ROFF}$ from 15KΩ to 120KΩ      |                                                                                                               |     | 0.667 |     | μs/kΩ |

| PWM Blanking time              | t <sub>BLK</sub>    |                                    |                                                                                                               |     | 2.5   |     | μs    |

| <b>CURRENT SENSE MONI</b>      | TOR                 |                                    |                                                                                                               |     |       |     |       |

| ISEN_ Voltage Range            | V <sub>ISEN</sub>   | Voltage Range at Pi                | n ISEN_                                                                                                       | 0   |       | 1.1 | V     |

| Current Monitor Scaling Factor | KISEN               | the Current Sense C                | See the I <sub>SEN</sub> Output Current Equation in the Current Sense Output (CSO) - Current Monitor Section. |     | 7500  |     | A/A   |

| Current Monitor                | DKISEN <sub>1</sub> | L_ = 6A (Note 1)                   | I <sub>TRIP</sub> from 2.2A to 6A                                                                             | -5  |       | +5  | - %   |

| Accuracy                       | DKISEN <sub>2</sub> | TIFS - OA (NOIE I)                 | I <sub>TRIP</sub> from 1A to 2.2A                                                                             |     |       | +10 | 70    |

| Settling Time                  | t <sub>S</sub>      | I <sub>FS</sub> = I <sub>MAX</sub> |                                                                                                               |     | 0.5   |     | μs    |

| FUNCTIONAL TIMINGS             |                     |                                    |                                                                                                               |     |       |     |       |

| Sleep Time                     | tSLEEP              | SLEEP = 1 to OUT_ tristate         |                                                                                                               |     | 40    |     | μs    |

| Wakeup Time From<br>Sleep      | t <sub>WAKE</sub>   | SLEEP = 0 to normal operation      |                                                                                                               |     |       | 2.7 | ms    |

Note 1: Guaranteed by design, not production tested.

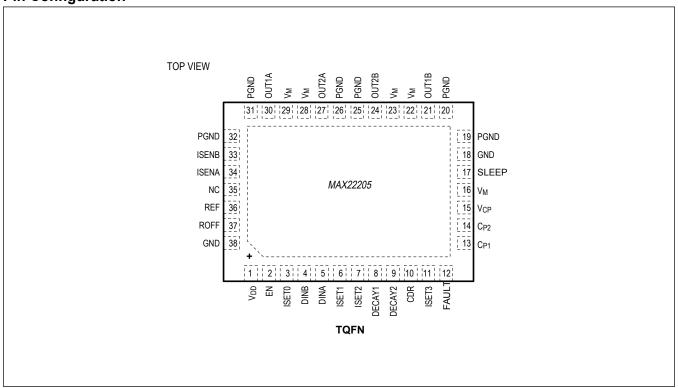

# **Pin Configuration**

## **Pin Configuration**

## **Pin Description**

| PIN                   | NAME            | FUNCTION                                                                                                                                                               | TYPE        |  |  |

|-----------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| 16, 22, 23,<br>28, 29 | V <sub>M</sub>  | Supply Voltage Input. Connect at least 1µF SMD plus 10µF electrolytic bypass capacitors to GND. Higher values can be considered depending on application requirements. |             |  |  |

| 15                    | $V_{CP}$        | Charge Pump Output. Connect a 5V, $1\mu F$ capacitor between $V_{\mbox{\footnotesize{CP}}}$ and $V_{\mbox{\footnotesize{M}}}$ as close as possible to the device.      | Output      |  |  |

| 13                    | C <sub>P1</sub> | Charge Pump Flying Capacitor Pin1. Connect a $V_M$ -rated 22nF capacitor between $C_{P1}$ and $C_{P2}$ as close as possible to the device.                             | Output      |  |  |

| 14                    | C <sub>P2</sub> | Charge Pump Flying Capacitor Pin 2. Connect a $V_M$ -rated 22nF capacitor between $C_{P1}$ and $C_{P2}$ as close as possible to the device.                            | Output      |  |  |

| 1                     | $V_{DD}$        | 1.8V LDO Output. Connect a 5V, 2.2µF to GND close to the device.                                                                                                       |             |  |  |

| 17                    | SLEEP           | Active Low Sleep Pin                                                                                                                                                   | Logic Input |  |  |

| 21, 24, 27, 30        | OUT_            | Driver Output Pins. Connect OUT1A and OUT2A and connect OUT1B and OUT2B together by wide, low-resistance PCB traces.                                                   |             |  |  |

| 12                    | FAULT           | Open-Drain Output Active Low-Fault Indicator. Connect a $2K\Omega$ resistor to the controller supply voltage.                                                          |             |  |  |

| 33, 34                | ISEN_           | Current-Sense Output Monitor. Connect a resistor to GND (see the Current-Sense Output section).                                                                        |             |  |  |

# 65V, 7.6A High Current Single H-Bridge with Integrated Current-Sense

# **Pin Description (continued)**

| PIN                       | NAME   | FUNCTION                                                                                                                                                                                                                                                 | TYPE                 |

|---------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2                         | EN     | Logic Input Pin. Enable Pin                                                                                                                                                                                                                              | Logic Input          |

| 4, 5                      | DIN_   | CMOS PWM Input                                                                                                                                                                                                                                           | Logic Input          |

| 8, 9                      | DECAY_ | Logic Input. Set the Decay Mode                                                                                                                                                                                                                          | Logic Input          |

| 3, 6, 7, 11               | ISET_  | Programmable Current Logic Input                                                                                                                                                                                                                         | Logic Input          |

| 10                        | CDR    | Open-Drain Output - Current Drive Regulator. Add a pullup resistor to the controller supply voltage. The pullup resistor value depends on application requirements. Values between $1K\Omega$ to $5K\Omega$ meet the requirements for most applications. | Open Drain<br>Output |

| 36                        | REF    | Programmable Current Analog Input. Connect a resistor from REF to GND to set the full scale current.                                                                                                                                                     | Analog Input         |

| 37                        | ROFF   | $t_{OFF}$ Programmable Off Time Pin. Connect ROFF to $V_{DD}$ to use the internal fixed $t_{OFF}$ time. Connect a resistor $R_{ROFF}$ from ROFF to GND to set the fixed OFF time to a desired value.                                                     |                      |

| 18, 38                    | GND    | Analog Ground. Connect to ground plane.                                                                                                                                                                                                                  |                      |

| 19, 20, 25,<br>26, 31, 32 | PGND   | Power GND. Connect to ground plane.                                                                                                                                                                                                                      |                      |

| EP                        | EP     | Exposed PAD. Connect to GND.                                                                                                                                                                                                                             | GND                  |

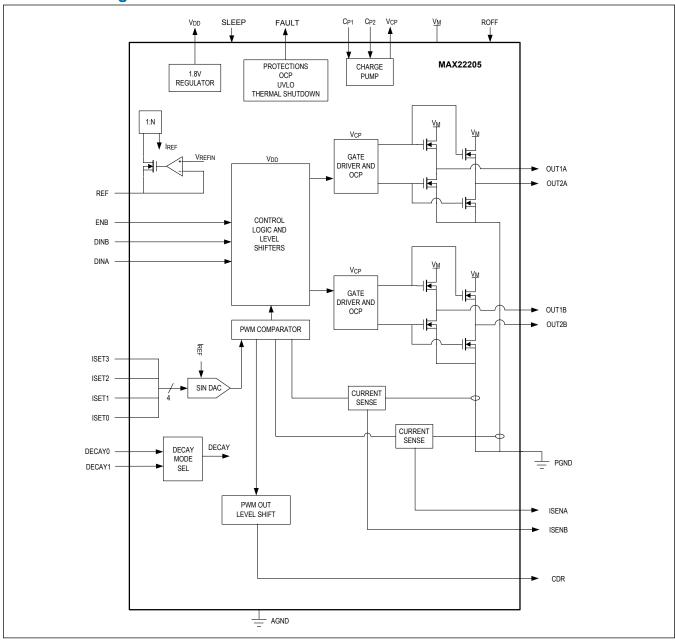

# **Functional Diagrams**

#### **Detailed Description**

The MAX22205 integrates an high current 65V,  $7.6A_{MAX}$  H-Bridge. It can be used to drive one Brushed DC motor or one half Stepper motor. The H-Bridge FETs feature very low impedance, resulting in high driving efficiency and low heat generated. The typical total  $R_{ON}$  (high-side + low-side) is  $0.15\Omega$ . The H-Bridge can be individually PWM controlled with two logic inputs (DINA, DINB). A third Enable (EN) logic input can be used to configure the outputs to high impedance for coasting the motor.

The MAX22205 features an accurate optional Current Drive Regulation (CDR), which can be used to limit the start-up current of a Brushed DC motor or to control the phase current for stepper operation. The bridge output current is sensed by a non-dissipative Integrated Current Sensing (ICS) and it is then compared with the desired threshold current. As soon as the bridge current exceeds the threshold (I<sub>TRIP</sub>), the device enforces the decay for a fixed OFF-time (t<sub>OFF</sub>).

The non-dissipative ICS eliminates the bulky external power resistors, which are normally required for this function, resulting in a dramatic space and power saving compared with mainstream applications based on the external sense resistor. A current proportional to the internally-sensed motor current is output to analog pins (ISENA, ISENB) to monitor the current. Also, one open-drain output (CDR pin) is asserted every time the internal current regulation is taking control of the driver so that the activity of the internal current loop can be monitored.

The maximum output current per H-Bridge is  $I_{MAX} = 7.6A_{MAX}$  limited by the Overcurrent Protection (OCP). The device delivers up to  $4A_{RMS}$  at  $V_{M} = +24V$  and  $T_{A} = 25^{\circ}C$  with proper PCB ground plane for thermal dissipation. The current capability depends on the PCB thermal characteristic (PCB ground planes, heatsinks, ventilation, etc.).

The MAX22205 features Overcurrent Protection (OCP), Thermal Shutdown (TSD), and Undervoltage Lockout (UVLO). An open-drain active low FAULT pin is activated every time a fault condition is detected. During Thermal Shutdown and Undervoltage Lockout, all the channels are disabled until normal operating conditions are restored.

The MAX22205 is packaged into a small TQFN38 5mm x 7mm package.

### Sleep Mode (SLEEP Pin)

Drive this pin low to enter in the lowest power mode. All outputs are tristated and the internal circuits are biased off. The charge pump is also disabled. A pulldown resistor is connected between SLEEP and GND to ensure the part is disabled whenever this pin is not actively driven. This mode corresponds to the lowest power consumption possible. Waking up from Sleep mode to Normal mode takes up to 2.7ms maximum.

#### **PWM Control**

OUT1A must be externally connected to OUT2A and OUT1B must be externally connected to OUT2B.

When the part is Enabled (EN = Logic High) and the H-Bridge current is below the configured current limit, the average output voltage can be controlled by DINA and DINB logic input pins using PWM techniques. Setting Enable logic low causes the output to enter a high impedance mode and the motor to coast. The Enable input pin frequency must not exceed 1KHz and cannot be used for PWM control.

Table 1 shows the control Truth Table.

Table 1. MAX22205 Truth Table

| EN | DINA | DINB | OUT1A = OUT2A | OUT1B = OUT2B | DESCRIPTION                             |

|----|------|------|---------------|---------------|-----------------------------------------|

| 0  | Х    | Х    | High-Z        | High-Z        | H-Bridge Disabled. High Impedance (HiZ) |

| 1  | 0    | 0    | L             | L             | Brake Low; Slow Decay                   |

| 1  | 1    | 0    | Н             | L             | Current from OUT2 to OUT1               |

| 1  | 0    | 1    | L             | Н             | Current from OUT1 to OUT2               |

| 1  | 1    | 1    | Н             | Н             | Brake High; Slow Decay                  |

PWM techniques can be used to control the output duty cycle and hence to implement motor speed control. Typically, for brushed DC motor drivers, Slow Decay is preferred as it results in less ripple and higher efficiency. With this approach, during the OFF phase, both the low-side FETs are activated effectively grounding the motor winding terminals. The current built up into the motor winding slowly decays. This decay is often referred to as Slow Decay.

# 65V, 7.6A High Current Single H-Bridge with Integrated Current-Sense

Alternatively, Fast Decay can also be implemented by reversing the bridge during the OFF phase.

#### **Current-Sense Output (CSO) - Current Monitor**

Currents proportional to the internally-sensed motor currents are output to pins ISENA, ISENB for half-bridge A (OUT1A = OUT2A) and B (OUT1B = OUT2B) respectively. The current is sensed only when the low side FET is ON and sinks current. During the blanking time, the ISEN current is zero.

The following equation shows the relationship between the current sourced at ISEN and the half-bridge low-side FET current:

$$I_{\text{ISEN}}(A) = \frac{I_{\text{OUT}}(A)}{K_{\text{ISEN}}}$$

**Equation - ISEN Output Current**

in which  $K_{ISEN}$  represents the current mirror factor between the output current and its replica at pin ISEN.  $K_{ISEN}$  is typically 7500 A/A. For instance, if the instantaneous output current is 2A, the current sourced at ISEN is 266 $\mu$ A.

ISENA can be externally tied to ISENB to sum up the two half-bridges low-side currents and monitor the full-bridge current. When used in this configuration, the ISEN = ISENA + ISENB current reflects the motor current during the Forward, Reverse, and Slow Decay statuses while it is zeroed during Fast Decay or Coast Status.

Figure Figure 1 shows an idealized behavior of the ISEN = ISENA + ISENB current when Slow or Fast Decay are used. Blanking times, delays, and rise/fall edges are ignored.

Figure 1. ISEN Current

By connecting an external signal resistor,  $R_{ISEN}$ , between ISEN\_ and GND, a voltage proportional to the motor current is generated. The voltage built up on  $R_{ISEN}$  can be input into the ADC of an external controller in applications in which the motor control algorithm requires the current/torque information. The designer can choose  $R_{ISEN}$  value so that the peak voltage meets the ADC full-scale requirement. The following equation shows the design formula to calculate  $R_{ISEN}$  once the ADC full scale voltage ( $V_{FS}$ ) and the maximum operating current ( $I_{MAX}$ ) are known:

$$R_{\mathsf{ISEN}}(\Omega) = K_{\mathsf{ISEN}} \times \frac{V_{\mathsf{FS}}(V)}{I_{\mathsf{MAX}}(A)}$$

For example, if the ADC operates up to 1V FS and the maximum operating output current is 2A, then  $R_{ISEN}$  is 7500 x  $1V/2A = 3.75K\Omega$ .

The  $R_{\rm ISEN}$  value also sets the output impedance of the Current-Sense Output circuit (ISEN\_ output impedance). Normally, the input impedance of the ADC is much higher than  $R_{\rm ISEN}$ , enabling a direct connection to the ISEN pin without attenuation. If a low input impedance ADC is used, a preamplifier (buffer) is required.

The Current-Sense Output circuit bandwidth and step response performances (see Specifications) ensure the current monitor tracks the driver current in PWM motor drive application.

#### **Current Drive Regulation**

The MAX22205 features embedded Current Drive Regulation (CDR).

The embedded current drive regulation provides an accurate control of the current flowing into the motor windings.

The bridge current is sensed by a non-dissipative Integrated Current Sensing (ICS) circuit and it is then compared with the threshold current ( $I_{TRIP}$ ). As soon as the bridge current exceeds the threshold, the device enforces the decay for a fixed OFF-time ( $I_{OFF}$ ). The device supports different decay modes as described in the following paragraphs.

Once  $t_{\text{OFF}}$  elapses, the driver is re-enabled for the next PWM cycle. During current regulation, the PWM duty cycle and frequency depend on the supply voltage, on the motor inductance, and on motor speed and load conditions.

The tope duration can be configured with an external resistor connected to the ROFF pin.

#### **Integrated Current-Sense (ICS)**

A non-dissipative current sensing is integrated. This feature eliminates the bulky external power resistors normally required for this function. This feature results in a dramatic space and power saving compared with mainstream applications based on the external sense resistor.

#### Setting the Full-Scale Current – Pin REF

Connect a resistor from REF to GND to set the full scale chopping current I<sub>ES</sub>.

The following equation shows the typical  $I_{FS}$  current as a function of the  $R_{REF}$  shunt resistor connected to pin REF. The proportionality constant  $K_{IFS}$  is typically 72KV. The external resistor  $R_{REF}$  can range between 12K $\Omega$  and 60K $\Omega$ , which correspondents to  $I_{FS}$  setting ranging from about 6A down to 1.2A.

$$I_{\text{FS}} = \frac{K_{\text{IFS}}(KV)}{R_{\text{REF}}(K\Omega)}$$

#### **Bridge Current Control**

Four input pins, ISET[3:0], are used to program the regulated output current. <u>Table 2</u> shows the bridge current levels for each input combination.

Table 2. H-Bridge ISET Pins Truth Table

| ISET3 | ISET2 | ISET1 | ISET0 | RELATIVE CURRENT |

|-------|-------|-------|-------|------------------|

| IOLIO |       | IOLIT |       | (% OF IFS)       |

| 0     | 0     | 0     | 0     | 100%             |

| 0     | 0     | 0     | 1     | 99.2%            |

| 0     | 0     | 1     | 0     | 97.6%            |

| 0     | 0     | 1     | 1     | 95.3%            |

| 0     | 1     | 0     | 0     | 91.3%            |

| 0     | 1     | 0     | 1     | 86.6%            |

| 0     | 1     | 1     | 0     | 81.1%            |

Table 2. H-Bridge ISET Pins Truth Table (continued)

| 0 | 1 | 1 | 1 | 74.0% |

|---|---|---|---|-------|

| 1 | 0 | 0 | 0 | 66.9% |

| 1 | 0 | 0 | 1 | 59.1% |

| 1 | 0 | 1 | 0 | 50.4% |

| 1 | 0 | 1 | 1 | 40.9% |

| 1 | 1 | 0 | 0 | 30.7% |

| 1 | 1 | 0 | 1 | 20.5% |

| 1 | 1 | 1 | 0 | 10.2% |

| 1 | 1 | 1 | 1 | 0.0%  |

#### Setting the Fixed OFF\_TIME (t<sub>OFF</sub>)

The current regulation circuit is based on a constant  $t_{OFF}$  PWM control. When the bridge current exceeds the target  $t_{ITRIP}$  current, an OFF phase begins and Decay modes are activated. The OFF phase has a fixed time duration ( $t_{OFF}$ ).  $t_{OFF}$  can be configured to a desired value by connecting an external resistor ( $t_{ROFF}$ ) to pin ROFF. When the ROFF pin is shorted to  $t_{DD}$ , the  $t_{OFF}$  time is internally set at a fixed value (20µs typical).

By connecting an external resistor to the pin ROFF, configure  $t_{OFF}$  as shown in the following equation, in which  $R_{ROFF}$  is an external resistor connected to the ROFF pin (in  $K\Omega$ ) and  $KT_{OFF}$  is an internal constant equal to 0.667 $\mu$ s/ $K\Omega$ .

$$t_{OFF}(\mu s) = R_{ROFF} \times K_{TOFF}$$

t<sub>OFF</sub> can be programmed from a range of 10µs to 80µs.

#### **CDR Open-Drain Output**

This pin is an active-low open-drain output, which is asserted during the fixed decay time interval ( $t_{OFF}$ ) enforced by the current drive regulation loop. This way, the external controller can monitor if the integrated current loop has taken control of the driver overwriting the status of the PWM logic inputs (DINA, DINB). The CDR signal can be used by the external controller for several reasons and provides information about the actual load during current regulation. In the use case in which the PWM logic inputs are permanently held in the Forward or Reverse mode and the control is entirely entrusted to the internal Current Drive Regulation loop, the CDR pin status directly reflects the driver output status. In this case, the duty cycle of the CDR can possibly be used to detect stall conditions.

Connect a pullup resistor from the CDR pin to the controller voltage supply. The pullup resistor value depends on the application requirements. Values between  $1K\Omega$  to  $5K\Omega$  meet the requirements for most applications.

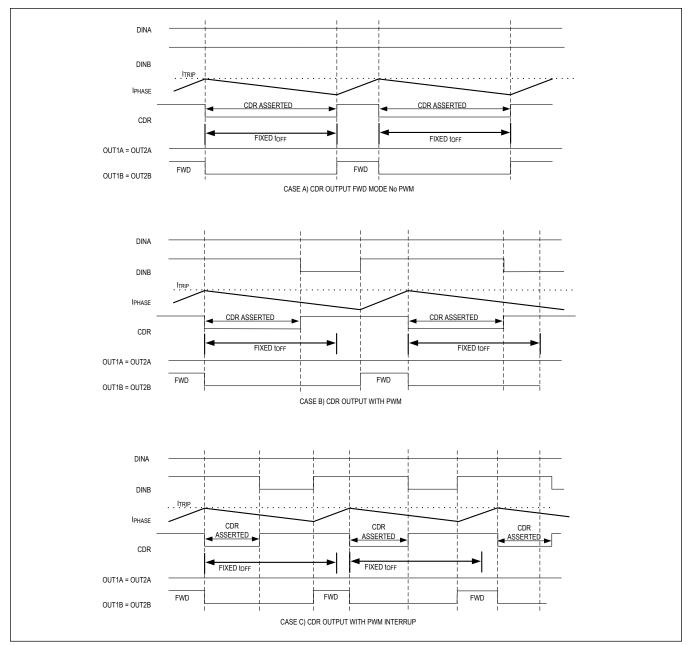

The time diagram in Figure 2 shows the behavior of this function when the motor spins in the forward direction respectively with DINB held firmly high (Case A) or when DINB is toggling (Cases B and C). The CDR output is asserted only when the Slow Decay mode is forced by the internal CDR. Note that any PWM transitions reset the fixed off time of the CDR circuit. In Case B, the actual Slow Decay Interval is longer than together.

Figure 2. CDR Monitor Timing Diagram

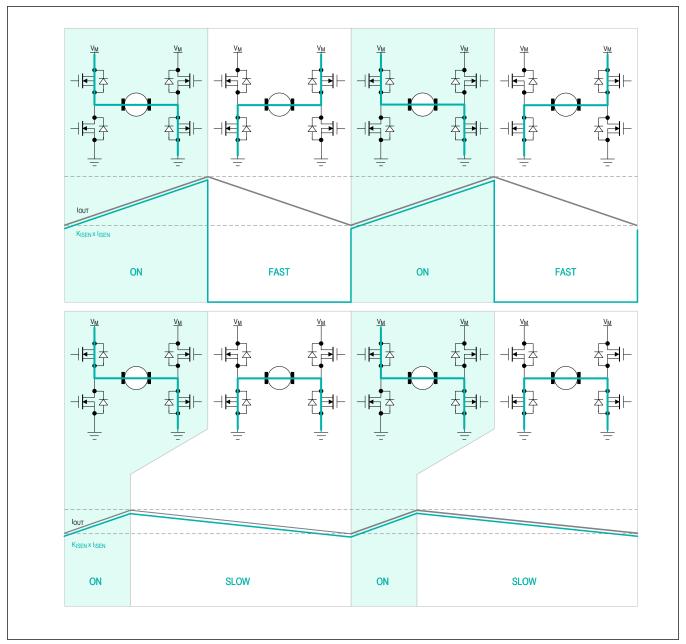

#### **Operating Modes**

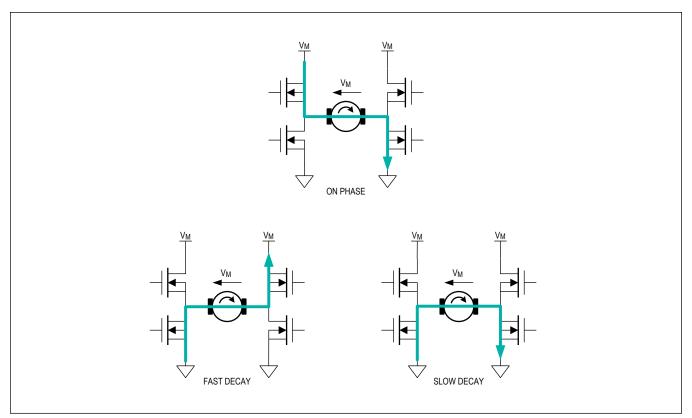

During PWM chopping, the driver output alternates the Energizing (ON) and Decay phases. The MAX22205 supports different Decay modes. Slow Decay, Fast Decay, and different combinations between Slow and Fast.

Figure 3 shows the current path in the three different modes of operation.

Figure 3. Current Flow During ON and Decay Modes

#### **Setting the Decay Mode**

Two logic input pins allow to set the Decay Mode during t<sub>OFF</sub>. The MAX22205 supports Slow, Fast, and Mixed Decay modes.

<u>Table 3</u> shows the Truth Table for the Decay selection.

**Table 3. Decay Mode Truth Table**

| DECAY2 | DECAY1 | DECAY MODE                 |

|--------|--------|----------------------------|

| 0      | 0      | SLOW                       |

| 0      | 1      | MIXED 30% FAST* / 70% SLOW |

| 1      | 0      | MIXED 60% FAST* / 40% SLOW |

| 1      | 1      | FAST*                      |

<sup>\*</sup>To prevent reversal of current during fast decay, outputs go to the high-impedance state as the current approaches 0A.

#### **Protections**

#### Overcurrent Protection – (OCP)

An Overcurrent Protection (OCP) protects the device against short circuits to the rails (supply voltage and ground) and across the load terminals.

The OCP threshold is set at 7.6A minimum. If the output current is greater than the OCP threshold for longer than the Deglitch Time (Blanking Time), then an OCP event is detected.

When an OCP event is detected, the H bridge is immediately disabled, and a fault indication is output on pin FAULT. The H-Bridge is kept in HiZ mode for 3ms (see t<sub>RETRY</sub> specification). After that, the H-bridge is re-enabled according to the

# 65V, 7.6A High Current Single H-Bridge with Integrated Current-Sense

current state. If the short circuit is still present, this cycle repeats, otherwise normal operation resumes.

Avoid prolonged operation under the short-circuit failure mode as a prolonged OCP auto-retry could affect the device reliability.

#### **Thermal Shutdown Protection (TSD)**

If the die temperature exceeds 155°C (typical value), a fault indication is output on pin FAULT and the driver is tristated until the junction temperature drops below 135°C. After that, the driver is re-enabled.

#### **Undervoltage Lockout Protection (UVLO)**

The device UVLO on  $V_M$  is set at 4.25V maximum. When a UVLO event occurs, a fault indication is output on pin  $\overline{FAULT}$  and driver outputs are tristated. Normal operation resumes (and the  $\overline{FAULT}$  pin deasserts) as soon as the supply voltages are back in the nominal operating range.

# 65V, 7.6A High Current Single H-Bridge with Integrated Current-Sense

# **Ordering Information**

| PART NUMBER    | TEMPERATURE RANGE | PIN-PACKAGE |  |

|----------------|-------------------|-------------|--|

| MAX22205ATU+T  | -40°C to +125°C   | 38 TQFN     |  |

| MAX22205AUU+T* | -40°C to +125°C   | 38 TSSOP    |  |

<sup>+</sup> Denotes a lead(Pb)-free/RoHS-compliant package.

T Denotes tape-and-reel.

<sup>\*</sup> Denotes future product. Contact factory for availability.

# 65V, 7.6A High Current Single H-Bridge with Integrated Current-Sense

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 8/21          | Initial release | _                |