www.ti.com

# LM6172QML Dual High Speed, Low Power, Low Distortion, Voltage Feedback Amplifiers

Check for Samples: LM6172QML

#### **FEATURES**

- Available with Radiation Specification

- High Dose Rate 300 krad(Si)

- ELDRS Free 100 krad(Si)

- · Easy to Use Voltage Feedback Topology

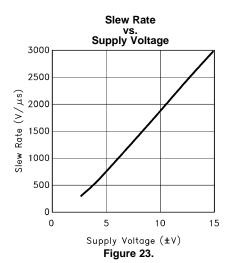

- High Slew Rate 3000V/µs

- Wide Unity-Gain Bandwidth 100MHz

- Low Supply Current 2.3mA / Amplifier

- High Output Current 50mA / Amplifier

- Specified for ±15V and ±5V Operation

#### **APPLICATIONS**

- Scanner I- to -V Converters

- ADSL/HDSL Drivers

- Multimedia Broadcast Systems

- Video Amplifiers

- NTSC, PAL® and SECAM Systems

- ADC/DAC Buffers

- Pulse Amplifiers and Peak Detectors

# **Connection Diagram**

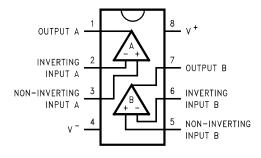

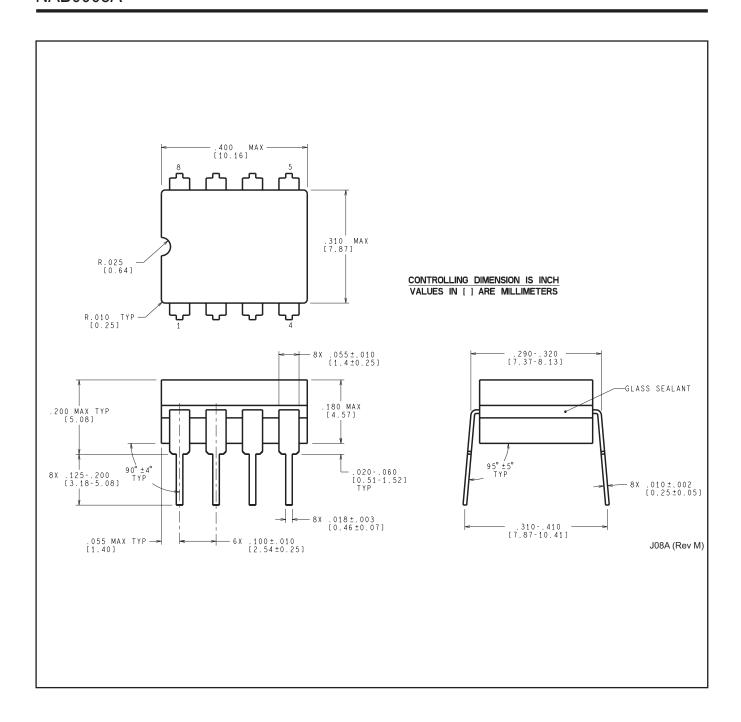

Figure 1. 8-Pin CDIP Top View

#### DESCRIPTION

The LM6172 is a dual high speed voltage feedback amplifier. It is unity-gain stable and provides excellent DC and AC performance. With 100MHz unity-gain bandwidth, 3000V/µs slew rate and 50mA of output current per channel, the LM6172 offers high performance in dual amplifiers; yet it only consumes 2.3mA of supply current each channel.

The LM6172 operates on ±15V power supply for systems requiring large voltage swings, such as ADSL, scanners and ultrasound equipment. It is also specified at ±5V power supply for low voltage applications such as portable video systems.

The LM6172 is built with TI's advanced  $VIP^{TM}$  III (Vertically Integrated PNP) complementary bipolar process.

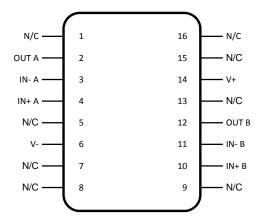

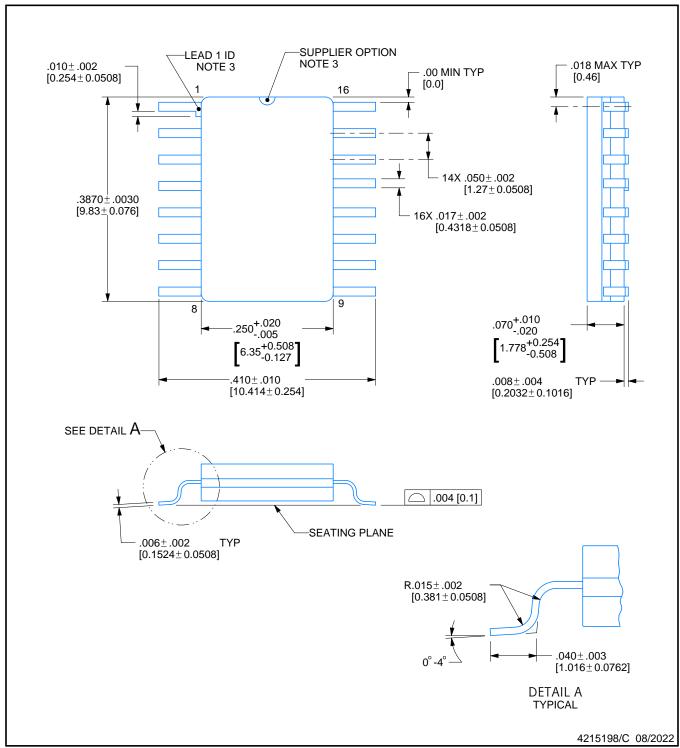

Figure 2. 16LD CLGA Top View

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

VIP is a trademark of Texas Instruments.

PAL is a registered trademark of and used under lisence from Advanced Micro Devices, Inc.. All other trademarks are the property of their respective owners.

# LM6172 Driving Capacitive Load

# LM6172 Simplified Schematic (Each Amplifier)

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### **ABSOLUTE MAXIMUM RATINGS (1)**

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) |                   |                                     | 36V                                          |

|---------------------------------------------------|-------------------|-------------------------------------|----------------------------------------------|

| Differential Input Voltage (2)                    |                   |                                     | ±10V                                         |

| Maximum Junction Tempera                          | ture              |                                     | 150°C                                        |

| Power Dissipation (3), (4)                        |                   |                                     | 1.03W                                        |

| Output Short Circuit to Groun                     | nd <sup>(5)</sup> |                                     | Continuous                                   |

| Storage Temperature Range                         |                   |                                     | -65°C ≤ T <sub>A</sub> ≤ +150°C              |

| Common Mode Voltage Ran                           | ge                |                                     | V <sup>+</sup> +0.3V to V <sup>−</sup> −0.3V |

| Input Current                                     |                   |                                     | ±10mA                                        |

| Thermal Resistance (6)                            | $\theta_{JA}$     | 8LD CDIP (Still Air)                | 100°C/W                                      |

|                                                   |                   | 8LD CDIP (500LF/Min Air Flow)       | 46°C/W                                       |

|                                                   |                   | 16LD CLGA (Still Air) "WG"          | 124°C/W                                      |

|                                                   |                   | 16LD CLGA (500LF/Min Air Flow) "WG" | 74°C/W                                       |

|                                                   |                   | 16LD CLGA (Still Air) "GW"          | 135°C/W                                      |

|                                                   |                   | 16LD CLGA (500LF/Min Air Flow) "GW" | 85°C/W                                       |

|                                                   | $\theta_{JC}$     | 8LD CDIP (4)                        | 2°C/W                                        |

|                                                   |                   | 16LD CLGA "WG" (4)                  | 6°C/W                                        |

|                                                   |                   | 16LD CLGA "GW"                      | 7°C/W                                        |

| Package Weight                                    | 8LD CDIF          |                                     | 980mg                                        |

|                                                   | 16LD CLO          | GA "WG"                             | 365mg                                        |

|                                                   | 16LD CLO          | GA "GW"                             | 410mg                                        |

| ESD Tolerance (7)                                 |                   |                                     | 4KV                                          |

|                                                   |                   |                                     |                                              |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- (2) Differential Input Voltage is measured at  $V_S = \pm 15V$ .

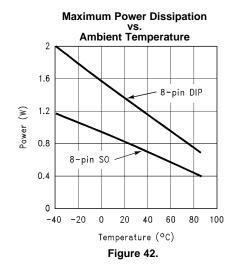

- (3) The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$  (maximum junction temperature),  $\theta_{JA}$  (package junction to ambient thermal resistance), and  $T_A$  (ambient temperature). The maximum allowable power dissipation at any temperature is  $P_{Dmax} = (T_{Jmax} T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower.

- temperature is P<sub>Dmax</sub> = (T<sub>Jmax</sub> T<sub>A</sub>)/θ<sub>JA</sub> or the number given in the Absolute Maximum Ratings, whichever is lower.

The package material for these devices allows much improved heat transfer over our standard ceramic packages. In order to take full advantage of this improved heat transfer, heat sinking must be provided between the package base (directly beneath the die), and either metal traces on, or thermal vias through, the printed circuit board. Without this additional heat sinking, device power dissipation must be calculated using θ<sub>JA</sub>, rather than θ<sub>JC</sub>, thermal resistance. It must not be assumed that the device leads will provide substantial heat transfer out the package, since the thermal resistance of the leadframe material is very poor, relative to the material of the package base. The stated θ<sub>JC</sub> thermal resistance is for the package material only, and does not account for the additional thermal resistance between the package base and the printed circuit board. The user must determine the value of the additional thermal resistance and must combine this with the stated value for the package, to calculate the total allowed power dissipation for the device.

- (5) Continuous short circuit operation can result in exceeding the maximum allowed junction temperature of 150°C

- (6) All numbers apply for packages soldered directly into a PC board.

- (7) Human body model, 1.5 k $\Omega$  in series with 100 pF.

#### RECOMMENDED OPERATING CONDITIONS (1)

| Supply Voltage              | 5.5V ≤ V <sub>S</sub> ≤ 36V     |

|-----------------------------|---------------------------------|

| Operating Temperature Range | -55°C ≤ T <sub>A</sub> ≤ +125°C |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Product Folder Links: LM6172QML

#### QUALITY CONFORMANCE INSPECTION

Mil-Std-883, Method 5005 - Group A

| Subgroup | Description         | Temp (°C) |

|----------|---------------------|-----------|

| 1        | Static tests at     | +25       |

| 2        | Static tests at     | +125      |

| 3        | Static tests at     | -55       |

| 4        | Dynamic tests at    | +25       |

| 5        | Dynamic tests at    | +125      |

| 6        | Dynamic tests at    | -55       |

| 7        | Functional tests at | +25       |

| 8A       | Functional tests at | +125      |

| 8B       | Functional tests at | -55       |

| 9        | Switching tests at  | +25       |

| 10       | Switching tests at  | +125      |

| 11       | Switching tests at  | -55       |

| 12       | Settling time at    | +25       |

| 13       | Settling time at    | +125      |

| 14       | Settling time at    | -55       |

# LM6172 (±5V) ELECTRICAL CHARACTERISTICS (1) DC PARAMETERS

The following conditions apply, unless otherwise specified.  $T_J = 25^{\circ}C$ ,  $V^+ = +5V$ ,  $V^- = -5V$ ,  $V_{CM} = 0V & R_L > 1M\Omega$

| Symbol          | Parameter                    | Conditions                  | Notes   | Min | Max  | Units | Sub-<br>groups |

|-----------------|------------------------------|-----------------------------|---------|-----|------|-------|----------------|

| V               | Input Offset Voltage         |                             |         |     | 1.0  | mV    | 1              |

| $V_{IO}$        | Input Offset Voltage         |                             |         |     | 3.0  | mV    | 2, 3           |

|                 | Input Pine Current           |                             |         |     | 2.5  | μΑ    | 1              |

| I <sub>IB</sub> | Input Bias Current           |                             |         |     | 3.5  | μΑ    | 2, 3           |

| 1               | Input Offset Current         |                             |         |     | 1.5  | μΑ    | 1              |

| I <sub>IO</sub> | input Onset Current          |                             |         |     | 2.2  | μΑ    | 2, 3           |

| CMRR Com        | Common Mode Rejection Ratio  | V - 12.5V                   |         | 70  |      | dB    | 1              |

|                 | Common wode Rejection Ratio  | $V_{CM} = \pm 2.5V$         |         | 65  |      | dB    | 2, 3           |

| PSRR            | Power Supply Rejection Ratio | \/ - 115\/ to 15\/          |         | 75  |      | dB    | 1              |

| FORK            |                              | $V_S = \pm 15V$ to $\pm 5V$ |         | 70  |      | dB    | 2, 3           |

|                 |                              | B 41/0                      | See (2) | 70  |      | dB    | 1              |

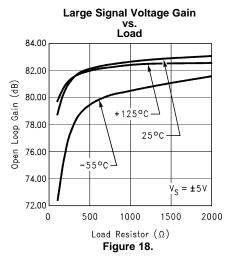

| Δ.              | Laura Cimal Valtana Cain     | $R_L = 1K\Omega$            | See (2) | 65  |      | dB    | 2, 3           |

| $A_V$           | Large Signal Voltage Gain    | D 4000                      | See (2) | 65  |      | dB    | 1              |

|                 |                              | $R_L = 100\Omega$           | See (2) | 60  |      | dB    | 2, 3           |

|                 |                              | D 4KO                       |         | 3.1 | -3.1 | V     | 1              |

| .,              | Outrat Suite a               | $R_L = 1K\Omega$            |         | 3.0 | -3.0 | V     | 2, 3           |

| Vo              | Output Swing                 | D 4000                      |         | 2.5 | -2.4 | V     | 1              |

|                 |                              | $R_L = 100\Omega$           |         | 2.4 | -2.3 | V     | 2, 3           |

<sup>(1)</sup> Pre and post irradiation limits are identical to those listed under AC and DC electrical characteristics. These parts may be dose rate sensitive in a space environment and demonstrate enhanced low dose rate effect. Radiation end point limits for the noted parameters are specified only for the conditions as specified in Mil-Std-883, Method 1019.5, Condition A.

<sup>(2)</sup> Large signal voltage gain is the total output swing divided by the input signal required to produce that swing. For V<sub>S</sub> = ±15V, V<sub>OUT</sub> = ±5V. For V<sub>S</sub> = ±5V, V<sub>OUT</sub> = ±1V.

# LM6172 (±5V) ELECTRICAL CHARACTERISTICS (1) DC PARAMETERS (continued)

The following conditions apply, unless otherwise specified.  $T_J = 25^{\circ}C$ ,  $V^+ = +5V$ ,  $V^- = -5V$ ,  $V_{CM} = 0V$  &  $R_L > 1M\Omega$

| Symbol         | Parameter                  | Conditions                 | Notes              | Min | Max | Units | Sub-<br>groups |

|----------------|----------------------------|----------------------------|--------------------|-----|-----|-------|----------------|

|                |                            |                            | See (3)            | 25  |     | mA    | 1              |

|                | Output Current (Open Loop) | Sourcing $R_L = 100\Omega$ | See <sup>(3)</sup> | 24  |     | mA    | 2, 3           |

| IL.            |                            | Sinking $R_L = 100\Omega$  | See (3)            |     | -24 | mA    | 1              |

|                |                            |                            | See (3)            |     | -23 | mA    | 2, 3           |

| I <sub>S</sub> | Supply Current             | Dath Amplifian             |                    |     | 6.0 | mA    | 1              |

|                | Supply Current             | Both Amplifiers            |                    |     | 7.0 | mA    | 2, 3           |

<sup>(3)</sup> The open loop output current is specified by measurement of the open loop output voltage swing using 100Ω output load.

# DC DRIFT PARAMETERS(1)

The following conditions apply, unless otherwise specified.  $T_J = 25^{\circ}\text{C}$ ,  $V^+ = +5\text{V}$ ,  $V^- = -5\text{V}$ ,  $V_{\text{CM}} = 0\text{V}$  &  $R_L > 1\text{M}\Omega$  Delta calculations performed on QMLV devices at group B , subgroup 5.

| Symbol          | Parameter            | Conditions | Notes | Min   | Max  | Units | Sub-<br>groups |

|-----------------|----------------------|------------|-------|-------|------|-------|----------------|

| $V_{IO}$        | Input Offset Voltage |            |       | -0.25 | 0.25 | mV    | 1              |

| I <sub>IB</sub> | Input Bias Current   |            |       | -0.50 | 0.50 | μA    | 1              |

| I <sub>IO</sub> | Input Ofset Current  |            |       | -0.25 | 0.25 | μA    | 1              |

<sup>(1)</sup> Pre and post irradiation limits are identical to those listed under AC and DC electrical characteristics. These parts may be dose rate sensitive in a space environment and demonstrate enhanced low dose rate effect. Radiation end point limits for the noted parameters are specified only for the conditions as specified in Mil-Std-883, Method 1019.5, Condition A.

# LM6172 (±15V) ELECTRICAL CHARACTERISTICS DC PARAMETERS (1)

The following conditions apply, unless otherwise specified.  $T_J = 25^{\circ}C$ ,  $V^+ = +15V$ ,  $V^- = -15V$ ,  $V_{CM} = 0V$ , &  $R_L = 1M\Omega$

| Symbol          | Parameter                    | Conditions                             | Notes   | Min | Max | Units | Sub-<br>groups |

|-----------------|------------------------------|----------------------------------------|---------|-----|-----|-------|----------------|

| V <sub>IO</sub> | Input Offset Voltage         |                                        |         |     | 1.5 | mV    | 1              |

| VIO.            | input Onset Voltage          |                                        |         |     | 3.5 | mV    | 2, 3           |

|                 | Input Bias Current           |                                        |         |     | 3.0 | μA    | 1              |

| I <sub>IB</sub> | Input bias Current           |                                        |         |     | 4.0 | μΑ    | 2, 3           |

|                 | Input Offset Current         |                                        |         |     | 2.0 | μΑ    | 1              |

| I <sub>IO</sub> | input Onset Current          |                                        |         |     | 3.0 | μΑ    | 2, 3           |

| CMDD            | Common Mode Dejection Detic  | V .40V                                 |         | 70  |     | dB    | 1              |

| CMRR            | Common Mode Rejection Ratio  | $V_{CM} = \pm 10V$                     |         | 65  |     | dB    | 2, 3           |

| PSRR            | Dawer Cumply Dejection Datio | \\\\\.\.\.\.\.\.\.\.\.\.\.\.\.\.\.\.\. |         | 75  |     | dB    | 1              |

| PSKK            | Power Supply Rejection Ratio | $V_S = \pm 15V$ to $\pm 5V$            |         | 70  |     | dB    | 2, 3           |

|                 |                              | B 4100                                 | See (2) | 75  |     | dB    | 1              |

|                 | Large Signal Voltage Gain    | $R_L = 1K\Omega$                       | See (2) | 70  |     | dB    | 2, 3           |

| A <sub>V</sub>  |                              | D 4000                                 | See (2) | 65  |     | dB    | 1              |

|                 |                              | $R_L = 100\Omega$                      | See (2) | 60  |     | dB    | 2, 3           |

Product Folder Links: LM6172QML

<sup>(1)</sup> Pre and post irradiation limits are identical to those listed under AC and DC electrical characteristics. These parts may be dose rate sensitive in a space environment and demonstrate enhanced low dose rate effect. Radiation end point limits for the noted parameters are specified only for the conditions as specified in Mil-Std-883, Method 1019.5, Condition A.

<sup>(2)</sup> Large signal voltage gain is the total output swing divided by the input signal required to produce that swing. For V<sub>S</sub> = ±15V, V<sub>OUT</sub> = ±5V. For V<sub>S</sub> = ±5V, V<sub>OUT</sub> = ±1V.

# LM6172 (±15V) ELECTRICAL CHARACTERISTICS DC PARAMETERS (1) (continued)

The following conditions apply, unless otherwise specified.  $T_J = 25^{\circ}C$ ,  $V^+ = +15V$ ,  $V^- = -15V$ ,  $V_{CM} = 0V$ , &  $R_L = 1M\Omega$

| Symbol         | Parameter                                                | Conditions                 | Notes   | Min  | Max   | Units | Sub-<br>groups |

|----------------|----------------------------------------------------------|----------------------------|---------|------|-------|-------|----------------|

|                |                                                          | B 4KO                      |         | 12.5 | -12.5 | V     | 1              |

|                | Output Swing  Output Current (Open Loop)  Supply Current | $R_L = 1K\Omega$           |         | 12   | -12   | V     | 2, 3           |

| Vo             | Output Swing                                             | $R_L = 100\Omega$          |         | 6.0  | -6.0  | V     | 1              |

|                |                                                          |                            |         | 5.0  | -5.0  | V     | 2, 3           |

|                |                                                          | Councin a B 4000           | See (3) | 60   |       | mA    | 1              |

|                | 0.1                                                      | Sourcing $R_L = 100\Omega$ | See (3) | 50   |       | mA    | 2, 3           |

| I <sub>L</sub> | Output Current (Open Loop)                               | Oisting D. 1000            | See (3) |      | -60   | mA    | 1              |

|                |                                                          | Sinking $R_L = 100\Omega$  | See (3) |      | -50   | mA    | 2, 3           |

|                | 2                                                        | D. II. A. III.             |         |      | 8.0   | mA    | 1              |

| Is             | <b>Бирріу Ситепі</b>                                     | Both Amplifiers            |         |      | 9.0   | mA    | 2, 3           |

<sup>(3)</sup> The open loop output current is specified by measurement of the open loop output voltage swing using 100Ω output load.

#### AC PARAMETERS (1)

The following conditions apply, unless otherwise specified.  $T_J = 25^{\circ}C$ ,  $V^+ = +15V$ ,  $V^- = -15V$ ,  $V_{CM} = 0V$

| Symbol | Parameter            | Conditions                                           | Notes        | Min  | Max | Units | Sub-<br>groups |

|--------|----------------------|------------------------------------------------------|--------------|------|-----|-------|----------------|

| SR     | Slew Rate            | $A_V = 2$ , $V_I = \pm 2.5V$<br>3nS Rise & Fall time | See (2), (3) | 1700 |     | V/µS  | 4              |

| GBW    | Unity-Gain Bandwidth |                                                      | See (4)      | 80   |     | MHz   | 4              |

<sup>(1)</sup> Pre and post irradiation limits are identical to those listed under AC and DC electrical characteristics. These parts may be dose rate sensitive in a space environment and demonstrate enhanced low dose rate effect. Radiation end point limits for the noted parameters are specified only for the conditions as specified in Mil-Std-883, Method 1019.5, Condition A.

- (2) See AN0009 for SR test circuit.

- (3) Slew Rate measured between ±4V.

- (4) See AN0009 for GBW test circuit.

#### DC DRIFT PARAMETERS (1)

The following conditions apply, unless otherwise specified.  $T_J = 25^{\circ}\text{C}$ ,  $V^+ = +15\text{V}$ ,  $V^- = -15\text{V}$ ,  $V_{\text{CM}} = 0\text{V}$  Delta calculations performed on QMLV devices at group B, subgroup 5.

| Symbol          | Parameter            | Conditions | Notes | Min   | Max  | Units | Sub-<br>groups |

|-----------------|----------------------|------------|-------|-------|------|-------|----------------|

| $V_{IO}$        | Input Offset Voltage |            |       | -0.25 | 0.25 | mV    | 1              |

| I <sub>IB</sub> | Input Bias Current   |            |       | -0.50 | 0.50 | μΑ    | 1              |

| I <sub>IO</sub> | Input Offset Current |            |       | -0.25 | 0.25 | μΑ    | 1              |

(1) Pre and post irradiation limits are identical to those listed under AC and DC electrical characteristics. These parts may be dose rate sensitive in a space environment and demonstrate enhanced low dose rate effect. Radiation end point limits for the noted parameters are specified only for the conditions as specified in Mil-Std-883, Method 1019.5, Condition A.

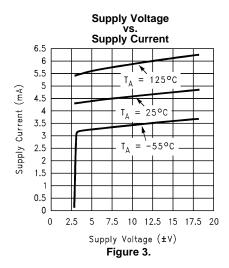

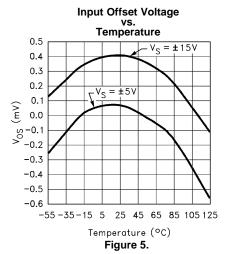

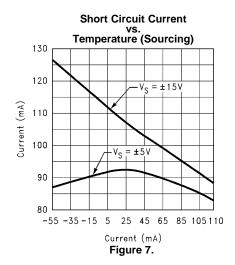

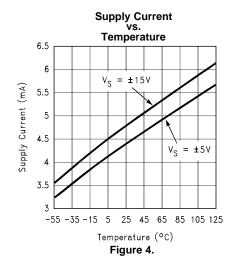

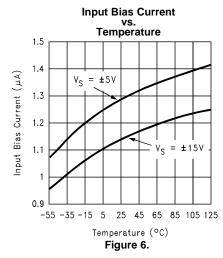

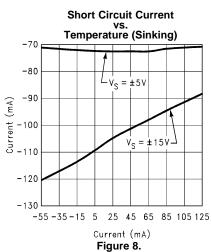

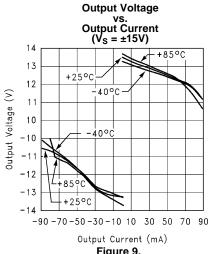

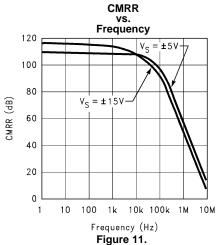

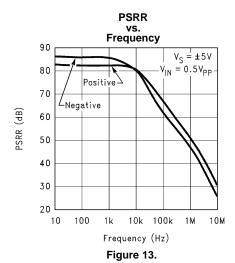

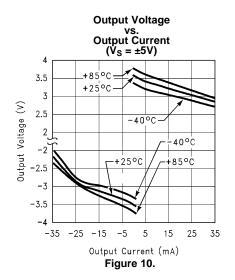

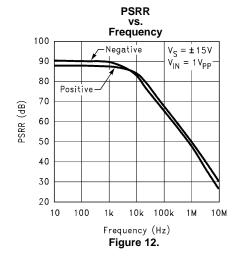

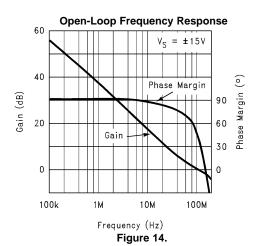

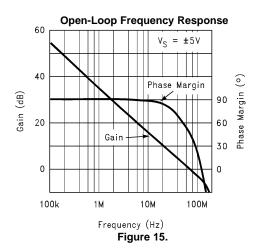

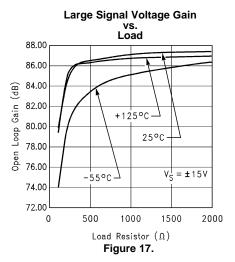

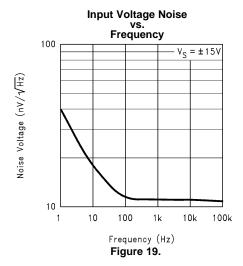

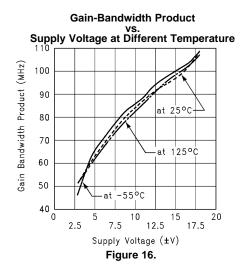

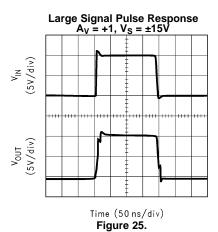

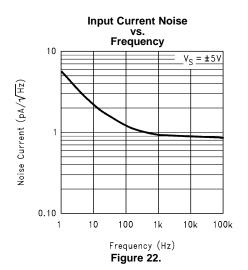

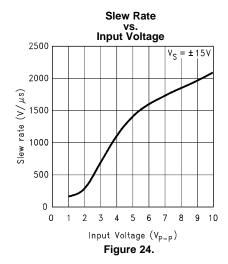

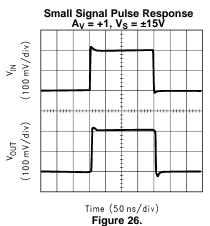

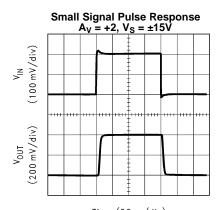

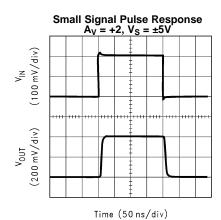

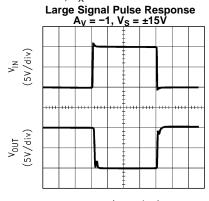

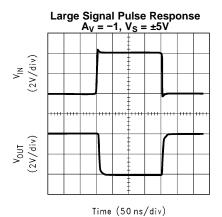

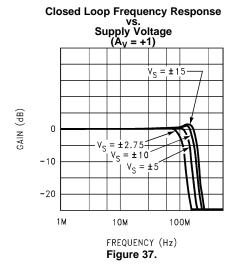

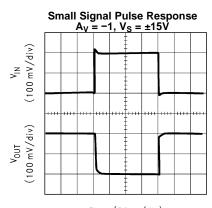

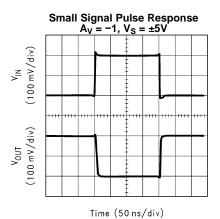

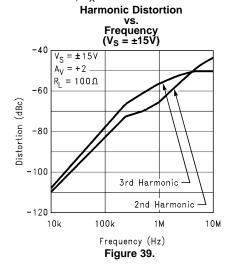

#### TYPICAL PERFORMANCE CHARACTERISTICS

Unless otherwise noted,  $T_A = 25$ °C

Unless otherwise noted,  $T_A = 25$ °C

Figure 9.

Unless otherwise noted,  $T_A = 25$ °C

Unless otherwise noted,  $T_A = 25$ °C

Unless otherwise noted,  $T_A = 25$ °C

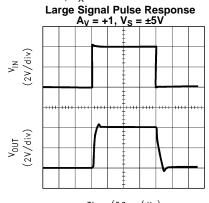

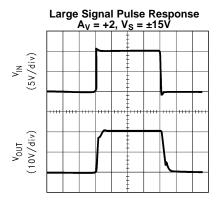

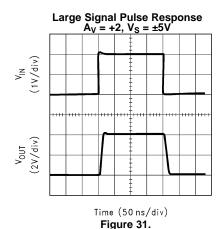

Time (50 ns/div) **Figure 27.**

Time (50 ns/div) Figure 29.

Time (50 ns/div) **Figure 28.**

Time (50 ns/div) **Figure 30.**

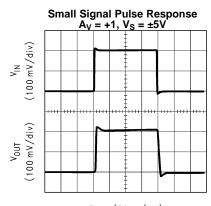

Figure 32.

Unless otherwise noted,  $T_A = 25$ °C

Time (50 ns/div) Figure 33.

Figure 35.

Time (50 ns/div) Figure 34.

Figure 36.

Figure 38.

Unless otherwise noted,  $T_A = 25$ °C

#### **APPLICATION NOTES**

#### LM6172 PERFORMANCE DISCUSSION

The LM6172 is a dual high-speed, low power, voltage feedback amplifier. It is unity-gain stable and offers outstanding performance with only 2.3mA of supply current per channel. The combination of 100MHz unity-gain bandwidth,  $3000V/\mu s$  slew rate, 50mA per channel output current and other attractive features makes it easy to implement the LM6172 in various applications. Quiescent power of the LM6172 is 138mW operating at  $\pm 15V$  supply and 46mW at  $\pm 5V$  supply.

#### **LM6172 CIRCUIT OPERATION**

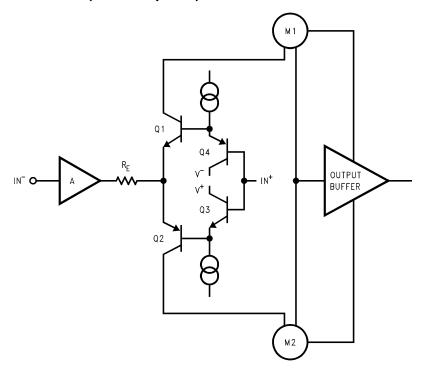

The class AB input stage in LM6172 is fully symmetrical and has a similar slewing characteristic to the current feedback amplifiers. In the LM6172 Simplified Schematic (Page 2), Q1 through Q4 form the equivalent of the current feedback input buffer, R<sub>E</sub> the equivalent of the feedback resistor, and stage A buffers the inverting input. The triple-buffered output stage isolates the gain stage from the load to provide low output impedance.

#### LM6172 SLEW RATE CHARACTERISTIC

The slew rate of LM6172 is determined by the current available to charge and discharge an internal high impedance node capacitor. This current is the differential input voltage divided by the total degeneration resistor  $R_E$ . Therefore, the slew rate is proportional to the input voltage level, and the higher slew rates are achievable in the lower gain configurations.

When a very fast large signal pulse is applied to the input of an amplifier, some overshoot or undershoot occurs. By placing an external series resistor such as  $1k\Omega$  to the input of LM6172, the slew rate is reduced to help lower the overshoot, which reduces settling time.

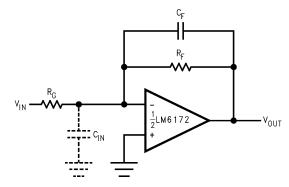

#### REDUCING SETTLING TIME

The LM6172 has a very fast slew rate that causes overshoot and undershoot. To reduce settling time on LM6172, a  $1k\Omega$  resistor can be placed in series with the input signal to decrease slew rate. A feedback capacitor can also be used to reduce overshoot and undershoot. This feedback capacitor serves as a zero to increase the stability of the amplifier circuit. A 2pF feedback capacitor is recommended for initial evaluation. When the LM6172 is configured as a buffer, a feedback resistor of  $1k\Omega$  must be added in parallel to the feedback capacitor.

Another possible source of overshoot and undershoot comes from capacitive load at the output. Please see the section "Driving Capacitive Loads" for more detail.

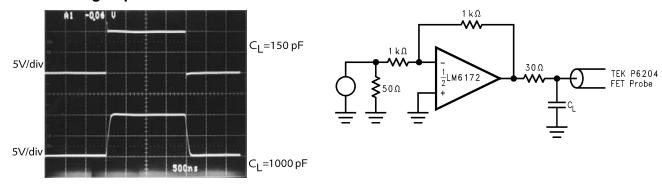

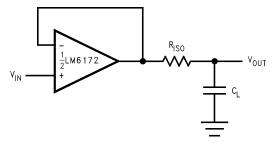

#### DRIVING CAPACITIVE LOADS

Amplifiers driving capacitive loads can oscillate or have ringing at the output. To eliminate oscillation or reduce ringing, an isolation resistor can be placed as shown in Figure 43. The combination of the isolation resistor and the load capacitor forms a pole to increase stability by adding more phase margin to the overall system. The desired performance depends upon the value of the isolation resistor; the bigger the isolation resistor, the more damped (slow) the pulse response becomes. For LM6172, a  $50\Omega$  isolation resistor is recommended for initial evaluation.

Figure 43. Isolation Resistor Used to Drive Capacitive Load

Figure 44. The LM6172 Driving a 510pF Load with a 30Ω Isolation Resistor

Figure 45. The LM6172 Driving a 220 pF Load with a 50Ω Isolation Resistor

# LAYOUT CONSIDERATION

#### **Printed Circuit Boards And High Speed Op Amps**

There are many things to consider when designing PC boards for high speed op amps. Without proper caution, it is very easy to have excessive ringing, oscillation and other degraded AC performance in high speed circuits. As a rule, the signal traces should be short and wide to provide low inductance and low impedance paths. Any unused board space needs to be grounded to reduce stray signal pickup. Critical components should also be grounded at a common point to eliminate voltage drop. Sockets add capacitance to the board and can affect frequency performance. It is better to solder the amplifier directly into the PC board without using any socket.

#### **Using Probes**

Active (FET) probes are ideal for taking high frequency measurements because they have wide bandwidth, high input impedance and low input capacitance. However, the probe ground leads provide a long ground loop that will produce errors in measurement. Instead, the probes can be grounded directly by removing the ground leads and probe jackets and using scope probe jacks.

#### **Components Selection And Feedback Resistor**

It is important in high speed applications to keep all component leads short because wires are inductive at high frequency. For discrete components, choose carbon composition-type resistors and mica-type capacitors. Surface mount components are preferred over discrete components for minimum inductive effect.

Large values of feedback resistors can couple with parasitic capacitance and cause undesirable effects such as ringing or oscillation in high speed amplifiers. For LM6172, a feedback resistor less than  $1k\Omega$  gives optimal performance.

Copyright © 2010–2011, Texas Instruments Incorporated

#### **COMPENSATION FOR INPUT CAPACITANCE**

The combination of an amplifier's input capacitance with the gain setting resistors adds a pole that can cause peaking or oscillation. To solve this problem, a feedback capacitor with a value

$$C_F > (R_G \times C_{IN})/R_F$$

can be used to cancel that pole. For LM6172, a feedback capacitor of 2pF is recommended. Figure 46 illustrates the compensation circuit.

Figure 46. Compensating for Input Capacitance

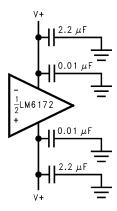

#### POWER SUPPLY BYPASSING

Bypassing the power supply is necessary to maintain low power supply impedance across frequency. Both positive and negative power supplies should be bypassed individually by placing 0.01µF ceramic capacitors directly to power supply pins and 2.2µF tantalum capacitors close to the power supply pins.

Figure 47. Power Supply Bypassing

#### **TERMINATION**

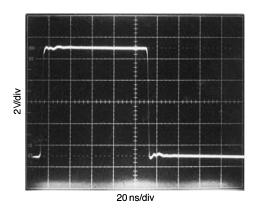

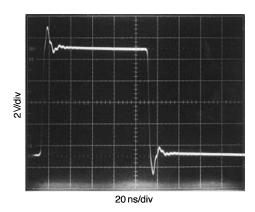

In high frequency applications, reflections occur if signals are not properly terminated. Figure 48 shows a properly terminated signal while Figure 49 shows an improperly terminated signal.

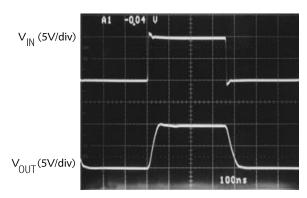

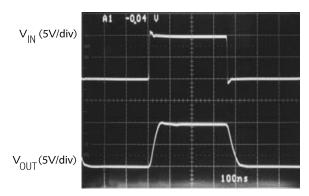

Figure 48. Properly Terminated Signal

Figure 49. Improperly Terminated Signal

To minimize reflection, coaxial cable with matching characteristic impedance to the signal source should be used. The other end of the cable should be terminated with the same value terminator or resistor. For the commonly used cables, RG59 has  $75\Omega$  characteristic impedance, and RG58 has  $50\Omega$  characteristic impedance.

#### POWER DISSIPATION

The maximum power allowed to dissipate in a device is defined as:

$$P_D = (T_{J(max)} - T_A)/\theta_{JA}$$

Where

- P<sub>D</sub> is the power dissipation in a device

- T<sub>J(max)</sub> is the maximum junction temperature

- T<sub>A</sub> is the ambient temperature

- $\theta_{IA}$  is the thermal resistance of a particular package

For example, for the LM6172 in a SOIC-16 package, the maximum power dissipation at  $25^{\circ}$ C ambient temperature is 1000 mW.

Thermal resistance,  $\theta_{JA}$ , depends on parameters such as die size, package size and package material. The smaller the die size and package, the higher  $\theta_{JA}$  becomes. The 8-pin CDIP package has a lower thermal resistance (95°C/W) than that of 8-pin SOIC (160°C/W). Therefore, for higher dissipation capability, use an 8-pin CDIP package.

The total power dissipated in a device can be calculated as:

$$P_D = P_Q + P_L$$

- P<sub>Q</sub> is the quiescent power dissipated in a device with no load connected at the output.

- P<sub>L</sub> is the power dissipated in the device with a load connected at the output; it is not the power dissipated by

Copyright © 2010–2011, Texas Instruments Incorporated

the load.

#### Furthermore,

- P<sub>Q</sub>: = supply current x total supply voltage with no load

- P<sub>L</sub>: = output current x (voltage difference between supply voltage and output voltage of the same supply)

For example, the total power dissipated by the LM6172 with  $V_S = \pm 15 V$  and both channels swinging output voltage of 10V into  $1 k \Omega$  is

$P_D$ : =  $P_Q + P_L$

= 2[(2.3mA)(30V)] + 2[(10mA)(15V - 10V)]

= 138 mW + 100 mW

= 238mW

# **Application Circuits**

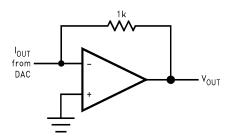

Figure 50. I- to -V Converters

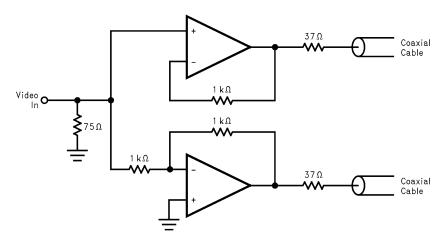

Figure 51. Differential Line Driver

# **REVISION HISTORY**

| Released   | Revision | Section                                                    | Changes                                                                                                                                                                                            |

|------------|----------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12/08/2010 | А        | New Release, Corporate format                              | 1 MDS data sheet converted into one Corp. data sheet format. MNLM6172AM-X-RH Rev 0A0 will be archived.                                                                                             |

| 10/05/2011 | В        | Features, Ordering Information, Abs Max Ratings, Footnotes | Update Radiation, Add new ELDRS FREE die id, 'GW' NSID'S w/coresponding SMD numbers. Add 'GW' Theta JA & Theta JC along with weight.Add Note 15, Modify Note 14. LM6172QML Rev A will be archived. |

Copyright © 2010–2011, Texas Instruments Incorporated

16-May-2023 www.ti.com

# **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan            | Lead finish/<br>Ball material | MSL Peak Temp    | Op Temp (°C) | Device Marking<br>(4/5)                                       | Samples |

|------------------|------------|--------------|--------------------|------|----------------|---------------------|-------------------------------|------------------|--------------|---------------------------------------------------------------|---------|

| 5962-9560401QPA  | ACTIVE     | CDIP         | NAB                | 8    | 40             | Non-RoHS<br>& Green | Call TI                       | Level-1-NA-UNLIM | -55 to 125   | LM6172AMJQML<br>5962-95604<br>01QPA Q ACO<br>01QPA Q >T       | Samples |

| 5962-9560402QXA  | ACTIVE     | CFP          | NAC                | 16   | 42             | Non-RoHS<br>& Green | Call TI                       | Level-1-NA-UNLIM | -55 to 125   | LM6172AMGW<br>-QML Q<br>5962-95604<br>02QXA ACO<br>02QXA >T   | Samples |

| 5962F9560401V9A  | ACTIVE     | DIESALE      | Υ                  | 0    | 39             | RoHS & Green        | Call TI                       | Level-1-NA-UNLIM | -55 to 125   |                                                               | Samples |

| 5962F9560401VPA  | ACTIVE     | CDIP         | NAB                | 8    | 40             | Non-RoHS<br>& Green | Call TI                       | Level-1-NA-UNLIM | -55 to 125   | LM6172AMJFQV<br>5962F95604<br>01VPA Q ACO<br>01VPA Q >T       | Samples |

| 5962F9560402VXA  | ACTIVE     | CFP          | NAC                | 16   | 42             | Non-RoHS<br>& Green | Call TI                       | Level-1-NA-UNLIM | -55 to 125   | LM6172AMGWF<br>QMLV Q<br>5962F95604<br>02VXA ACO<br>02VXA >T  | Samples |

| 5962R9560403V9A  | ACTIVE     | DIESALE      | Y                  | 0    | 39             | RoHS & Green        | Call TI                       | Level-1-NA-UNLIM | -55 to 125   |                                                               | Samples |

| 5962R9560403VXA  | ACTIVE     | CFP          | NAC                | 16   | 42             | Non-RoHS<br>& Green | Call TI                       | Level-1-NA-UNLIM | -55 to 125   | LM6172AMGW<br>RLQMLV Q<br>5962R95604<br>03VXA ACO<br>03VXA >T | Samples |

| LM6172 MDR       | ACTIVE     | DIESALE      | Y                  | 0    | 39             | RoHS & Green        | Call TI                       | Level-1-NA-UNLIM | -55 to 125   |                                                               | Samples |

| LM6172-MDE       | ACTIVE     | DIESALE      | Υ                  | 0    | 39             | RoHS & Green        | Call TI                       | Level-1-NA-UNLIM | -55 to 125   |                                                               | Samples |

| LM6172AMGW-QML   | ACTIVE     | CFP          | NAC                | 16   | 42             | Non-RoHS<br>& Green | Call TI                       | Level-1-NA-UNLIM | -55 to 125   | LM6172AMGW<br>-QML Q<br>5962-95604<br>02QXA ACO<br>02QXA >T   | Samples |

# **PACKAGE OPTION ADDENDUM**

www.ti.com 16-May-2023

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan (2)        | Lead finish/<br>Ball material<br><sup>(6)</sup> | MSL Peak Temp    | Op Temp (°C) | <b>Device Marking</b> (4/5)                                   | Samples |

|------------------|------------|--------------|--------------------|------|----------------|---------------------|-------------------------------------------------|------------------|--------------|---------------------------------------------------------------|---------|

| LM6172AMGWFQMLV  | ACTIVE     | CFP          | NAC                | 16   | 42             | Non-RoHS<br>& Green | Call TI                                         | Level-1-NA-UNLIM | -55 to 125   | LM6172AMGWF<br>QMLV Q<br>5962F95604<br>02VXA ACO<br>02VXA >T  | Samples |

| LM6172AMGWRLQV   | ACTIVE     | CFP          | NAC                | 16   | 42             | Non-RoHS<br>& Green | Call TI                                         | Level-1-NA-UNLIM | -55 to 125   | LM6172AMGW<br>RLQMLV Q<br>5962R95604<br>03VXA ACO<br>03VXA >T | Samples |

| LM6172AMJ-QML    | ACTIVE     | CDIP         | NAB                | 8    | 40             | Non-RoHS<br>& Green | Call TI                                         | Level-1-NA-UNLIM | -55 to 125   | LM6172AMJQML<br>5962-95604<br>01QPA Q ACO<br>01QPA Q >T       | Samples |

| LM6172AMJFQMLV   | ACTIVE     | CDIP         | NAB                | 8    | 40             | Non-RoHS<br>& Green | Call TI                                         | Level-1-NA-UNLIM | -55 to 125   | LM6172AMJFQV<br>5962F95604<br>01VPA Q ACO<br>01VPA Q >T       | Samples |

| LM6172NAB/EM     | ACTIVE     | CDIP         | NAB                | 8    | 40             | Non-RoHS<br>& Green | Call TI                                         | Level-1-NA-UNLIM | -55 to 125   | LM6172NABEM<br>EVAL ONLY<br>ACO                               | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(2)</sup> **RoHS**: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

# PACKAGE OPTION ADDENDUM

www.ti.com 16-May-2023

(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF LM6172QML, LM6172QML-SP:

Military: LM6172QML

Space: LM6172QML-SP

NOTE: Qualified Version Definitions:

• Military - QML certified for Military and Defense Applications

Space - Radiation tolerant, ceramic packaging and gualified for use in Space-based application

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 1-Aug-2023

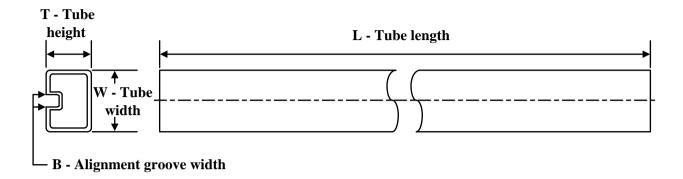

# **TUBE**

\*All dimensions are nominal

| Device          | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-----------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| 5962-9560401QPA | NAB          | CDIP         | 8    | 40  | 506.98 | 15.24  | 13440  | NA     |

| 5962F9560401VPA | NAB          | CDIP         | 8    | 40  | 506.98 | 15.24  | 13440  | NA     |

| LM6172AMJ-QML   | NAB          | CDIP         | 8    | 40  | 506.98 | 15.24  | 13440  | NA     |

| LM6172AMJFQMLV  | NAB          | CDIP         | 8    | 40  | 506.98 | 15.24  | 13440  | NA     |

| LM6172NAB/EM    | NAB          | CDIP         | 8    | 40  | 506.98 | 15.24  | 13440  | NA     |

CERAMIC FLATPACK

#### NOTES:

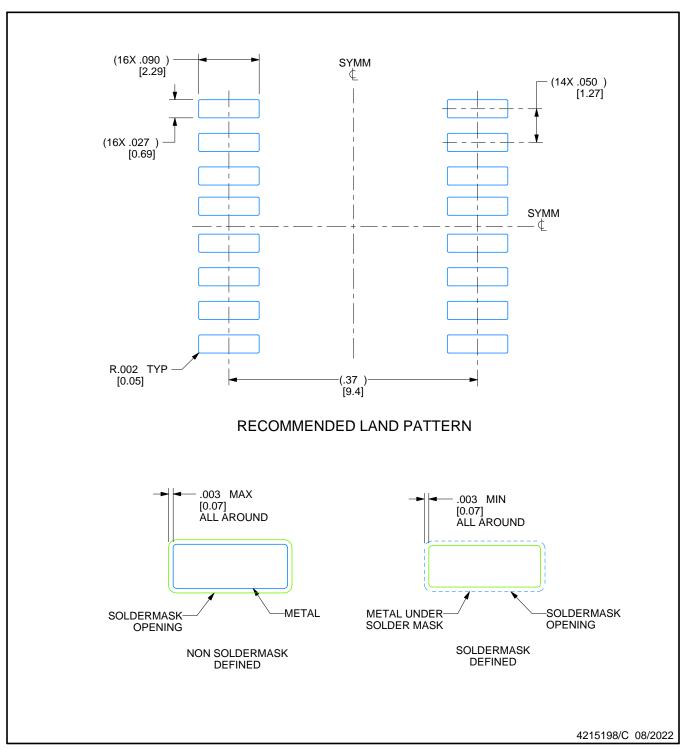

- 1. Controlling dimension is Inch. Values in [] are milimeters. Dimensions in () for reference only.

2. For solder thickness and composition, see the "Lead Finish Composition/Thickness" link in the packaging section of the Texas Instruments website

- 3. Lead 1 identification shall be:

- a) A notch or other mark within this area

- b) A tab on lead 1, either side

- 4. No JEDEC registration as of December 2021

CERAMIC FLATPACK

|       |                                                                                                               | RF\/IS | SIONS            |                               |                                        |                                         |                    |

|-------|---------------------------------------------------------------------------------------------------------------|--------|------------------|-------------------------------|----------------------------------------|-----------------------------------------|--------------------|

| REV   | DESCRIPTION                                                                                                   | vic    | 2.3.10           | E.C.N.                        | DATE                                   | BY/AP                                   | P'D                |

|       |                                                                                                               |        |                  |                               |                                        |                                         |                    |

|       |                                                                                                               |        |                  |                               |                                        |                                         |                    |

|       |                                                                                                               |        |                  |                               |                                        |                                         |                    |

| A B C | RELEASE TO DOCUMENT CONTROL  NO CHANGE TO DRAWING; REVISION FOR YODA RELEASE;  .387± .003 WAS .39000± .00012; |        |                  | 2197879<br>2198832<br>2200917 | 12/30/2021<br>02/15/2022<br>08/08/2022 | TINA TRAN / A  K. SINCE  D. CHIN / K. S | ANIS FAUZI<br>RBOX |

|       |                                                                                                               |        |                  |                               |                                        |                                         |                    |

|       |                                                                                                               |        |                  |                               |                                        |                                         |                    |

|       |                                                                                                               |        |                  |                               |                                        |                                         |                    |

|       |                                                                                                               |        |                  |                               |                                        |                                         |                    |

|       |                                                                                                               | SCALE  | SIZE<br><b>A</b> |                               | 421519                                 | 98                                      | REV PAGE 4 OF 4    |

# **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated