# 54LS195A/DM74LS195A 4-Bit Parallel Access Shift Register

#### **General Description**

This 4-bit register features parallel inputs, parallel outputs,  $J-\overline{K}$  serial inputs, shift/load control input, and a direct overriding clear. All inputs are buffered to lower the input drive requirements. The registers have two modes of operation:

Parallel (broadside) load

Shift (in the direction QA toward QD)

Parallel loading is accomplished by applying the four bits of data and taking the shift/load control input low. The data is loaded into the associated flip-flop and appears at the outputs after the positive transition of the clock input. During loading, serial data flow is inhibited.

Shifting is accomplished synchronously when the shift/load control input is high. Serial data for this mode is entered at the J- $\overline{K}$  inputs. These inputs permit the first stage to perform as a J- $\overline{K}$ , D, or T-type flip-flop as shown in the truth table.

#### **Features**

- Synchronous parallel load

- Positive-edge-triggered clocking

- Parallel inputs and outputs from each flip-flop

- Direct overriding clear

- J and K inputs to first stage

- Complementary outputs from last stage

- For use in high-performance: accumulators/processors serial-to-parallel, parallel-to-serial converters

- Typical clock frequency 39 MHz

- Typical power dissipation 70 mW

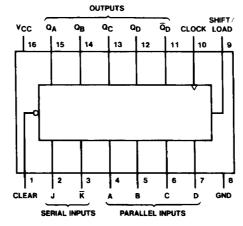

#### **Connection Diagram**

#### **Dual-In-Line Package**

TL/F/6408-1

Order Number 54LS195ADMQB, 54LS195AFMQB, 54LS195ALMQB, DM74LS195AM or DM74LS195AN See NS Package Number E20A, J16A, M16A, N16E or W16A

#### **Absolute Maximum Ratings (Note)**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage 7V Input Voltage 7V

Operating Free Air Temperature Range

54LS -55°C to +125°C DM74LS 0°C to +70°C

Storage Temperature Range -65°C to +150°C

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

### **Recommended Operating Conditions**

| Symbol           | Parame                           |            | 54LS195A | ١.  |      | Units |      |        |      |

|------------------|----------------------------------|------------|----------|-----|------|-------|------|--------|------|

| Cyllide.         | rarame                           | Min        | Nom      | Max | Min  | Nom   | Max  | Ullits |      |

| V <sub>CC</sub>  | Supply Voltage                   | 4.5        | 5        | 5.5 | 4.75 | 5     | 5.25 | ٧      |      |

| V <sub>IH</sub>  | High Level Input Volta           | ge         | 2        |     |      | 2     |      |        | ٧    |

| V <sub>IL</sub>  | Low Level Input Voltage          |            |          |     | 0.7  |       |      | 0.8    | ٧    |

| Юн               | High Level Output Current        |            |          |     | -0.4 |       |      | -0.4   | mA   |

| loL              | Low Level Output Current         |            |          |     | 4    |       |      | 8      | mA   |

| fclk             | Clock Frequency (Not             | 30         |          | 0   | 0    |       | 30   | MHz    |      |

|                  | Clock Frequency (Not             | 30         |          | 0   | 0    |       | 25   | MHz    |      |

| t <sub>W</sub>   | Pulse Width<br>(Note 3)          | Clock      | 16       |     |      | 16    |      |        | ns   |

|                  |                                  | Clear      | 14       |     |      | 12    |      |        |      |

| tsu              | Setup Time                       | Shift/Load | 25       |     |      | 25    |      |        | ns   |

|                  | (Note 3)                         | Data       | 15       |     |      | 15    |      | •      | l ns |

| tH               | Hold Time (Note 3)               |            | 0        |     |      | 0     |      |        | ns   |

| t <sub>REL</sub> | Shift/Load Release Time (Note 3) |            | 10       |     |      | 10    |      |        | ns   |

|                  | Clear Release Time (Note 3)      |            | 25       |     |      | 25    |      |        |      |

| TA               | Free Air Operating Te            | -55        |          | 125 | 0    |       | 70   | °C     |      |

Note 1:  $C_L = 15 \text{ pF}$ ,  $T_A = 25^{\circ}\text{C}$  and  $V_{CC} = 5\text{V}$ .

Note 2:  $C_L = 50$  pF,  $R_L = 2$  k $\Omega$ ,  $T_A = 25^{\circ}$ C and  $V_{CC} = 5$ V.

Note 3:  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ .

## Electrical Characteristics over recommended operating free air temperature range (unless otherwise noted)

| Symbol           | Parameter                            | Conditions                                    | Min    | Typ<br>(Note 4) | Max  | Units |    |

|------------------|--------------------------------------|-----------------------------------------------|--------|-----------------|------|-------|----|

| VI               | Input Clamp Voltage                  | $V_{CC}$ = Min, $I_{I}$ = -18 mA              |        |                 |      | -1.5  | V  |

| V <sub>OH</sub>  | High Level Output                    | V <sub>CC</sub> = Min, I <sub>OH</sub> = Max  | 54LS   | 2.5             |      |       | ٧  |

|                  | Voltage                              | V <sub>IL</sub> = Max, V <sub>IH</sub> = Min  | DM74LS | 2.7             | 3.4  |       |    |

| V <sub>OL</sub>  | Low Level Output                     | V <sub>CC</sub> = Min, I <sub>OL</sub> = Max  | 54LS   |                 |      | 0.4   | ٧  |

|                  | Voltage                              | V <sub>IL</sub> = Max, V <sub>IH</sub> = Min  | DM74LS |                 | 0.35 | 0.5   |    |

|                  |                                      | I <sub>OL</sub> = 4 mA, V <sub>CC</sub> = Min |        |                 | 0.25 | 0.4   |    |

| 1 <sub>1</sub>   | Input Current @ Max<br>Input Voltage | V <sub>CC</sub> = Max, V <sub>I</sub> = 7V    |        |                 |      | 0.1   | mA |

| 1 <sub>IH</sub>  | High Level Input Current             | $V_{CC} = Max, V_I = 2.7V$                    |        |                 |      | 20    | μΑ |

| I <sub>Ι</sub> L | Low Level Input Current              | $V_{CC} = Max, V_I = 0.4V$                    |        |                 |      | -0.4  | mA |

| los              | Short Circuit                        | V <sub>CC</sub> = Max                         | 54LS   | -20             |      | - 100 | mA |

|                  | Output Current                       | (Note 5)                                      | -20    |                 | -100 | шА    |    |

| lcc              | Supply Current                       | V <sub>CC</sub> = Max, (Note 6)               |        |                 | 14   | 21    | mA |

Note 4: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C.

Note 5: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 6: With all inputs open, SHIFT/LOAD grounded, and 4.5V applied to the J,  $\overline{K}$ , and data inputs,  $I_{CC}$  is measured by applying a momentary ground, then 4.5V to the CLEAR and then applying a momentary ground then 4.5V to the CLOCK.

# **Switching Characteristics** at $V_{CC} = 5V$ and $T_A = 25^{\circ}C$ (See Section 1 for Test Waveforms and Output Load)

|                  |                                                    |                             | 54               | ILS   | DM7                                  | Units |     |  |

|------------------|----------------------------------------------------|-----------------------------|------------------|-------|--------------------------------------|-------|-----|--|

| Symbol           | Parameter                                          | From (Input)<br>To (Output) | C <sub>L</sub> = | 15 pF | R <sub>L</sub> =<br>C <sub>L</sub> = |       |     |  |

|                  |                                                    |                             | Min              | Max   | Min                                  | Max   | 1   |  |

| fmax             | Maximum Clock<br>Frequency                         |                             | 30               |       | 25                                   |       | MHz |  |

| t <sub>PLH</sub> | Propagation Delay Time<br>Low to High Level Output | Clock to<br>Any Q           |                  | 21    |                                      | 26    | ns  |  |

| t <sub>PHL</sub> | Propagation Delay Time<br>High to Low Level Output | Clock to<br>Any Q           |                  | 24    |                                      | 35    | ns  |  |

| t <sub>PHL</sub> | Propagation Delay Time<br>High to Low Level Output | Clear to<br>Any Q           |                  | 26    | -                                    | 38    | ns  |  |

#### **Function Table**

| Inputs |                |          |       |    |      |   |     | Outputs |                 |                 |                 |                 |                                      |  |

|--------|----------------|----------|-------|----|------|---|-----|---------|-----------------|-----------------|-----------------|-----------------|--------------------------------------|--|

| Clear  | Shift/<br>Load | Shift/   | Clock | Se | rial |   | Par | allel   |                 |                 |                 |                 |                                      |  |

|        |                | O.OOK    | J     | K  | Α    | В | С   | D       | QA              | QB              | QC              | Q <sub>D</sub>  | $\overline{\mathbf{Q}}_{\mathbf{D}}$ |  |

| L      | Х              | Х        | X     | X  | Х    | Х | Х   | Х       | L               | Ĺ               | L               |                 | н                                    |  |

| Н      | L              | 1        | X     | Х  | a    | b | С   | ď       | a               | b               | c               | ď               | <br>a                                |  |

| Н      | Н              | L        | X     | Х  | X    | Х | Х   | Х       | Q <sub>A0</sub> | Q <sub>B0</sub> | Q <sub>C0</sub> | $Q_{D0}$        | $\overline{Q}_{D0}$                  |  |

| Н      | Н              | <b>1</b> | L     | Н  | l x  | Х | Х   | Х       | Q <sub>A0</sub> | Q <sub>A0</sub> | Q <sub>Bn</sub> | Q <sub>Cn</sub> | Q <sub>Cn</sub>                      |  |

| Н      | Н              | <b>↑</b> | L     | L  | x    | Х | X   | X       | L               | QAn             | Q <sub>Bn</sub> | Q <sub>Cn</sub> | Q <sub>Cn</sub>                      |  |

| Н      | Н              | 1        | н     | Н  | х    | X | X   | х       | Н               | QAn             | Q <sub>Bn</sub> | Q <sub>Cn</sub> | Q <sub>Cn</sub>                      |  |

| Н      | Н              |          | Н     | L  | Х    | Х | X   | Х       | Q <sub>An</sub> | Q <sub>An</sub> | Q <sub>Bn</sub> | Q <sub>Cn</sub> | Q <sub>Cn</sub>                      |  |

H = High Level (steady state), L = Low Level (steady state), X = Don't Care (any input, including transitions)

$Q_{A0},\,Q_{B0},\,Q_{C0},\,Q_{D0}\,=\,\text{The level of Q}_{A},\,Q_{B},\,Q_{C},\,\text{or Q}_{D},\,\text{respectively, before the indicated steady state input conditions were established}.$

$\mathbf{Q}_{An},\,\mathbf{Q}_{Bn},\,\mathbf{Q}_{Cn}\,=\,\text{The level of }\mathbf{Q}_{A},\,\mathbf{Q}_{B},\,\mathbf{Q}_{C},\,\text{respectively, before the most recent transition of the clock}.$

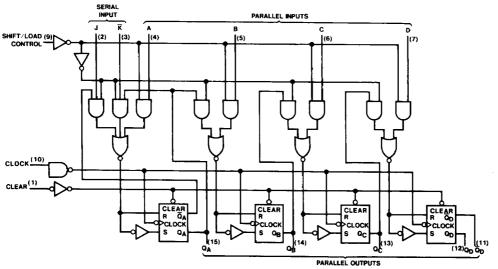

## **Logic Diagram**

TL/F/6408-2

<sup>↑ =</sup> Transition from low to high level

a, b, c, d = The level of steady state input at A, B, C, or D, respectively.

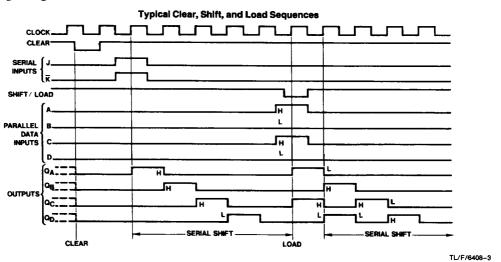

# **Timing Diagram**