# **General Description**

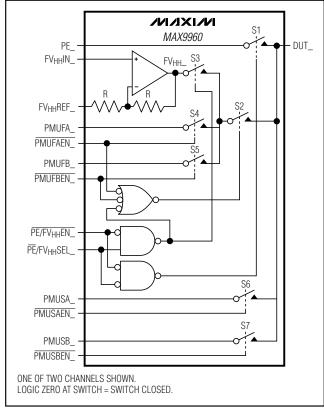

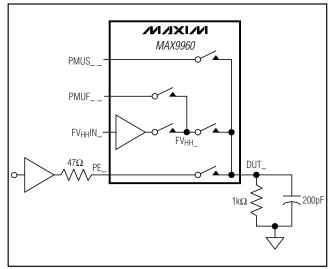

The MAX9960 dual-flash-pin electronics/supervoltage switch matrix replaces most of the relays and switches commonly needed to connect system resources to each of two pins in a flash memory or SOC ATE system (Figure 1). The device provides seven switches per channel to select up to four independent sources: the pin electronics (PE), two parametric measurement units (PMUs) or other Kelvin analog resources, and a flash memory programming supervoltage (FVHH\_). The force-and-sense PMU switches are independently controlled, enabling their use to connect two non-Kelvin resources in place of each PMU or Kelvin resource. Each MAX9960 contains two complete seven-switch channels with fully independent controls.

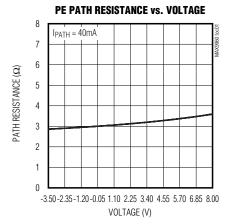

The MAX9960 features signal path switches with wide 600MHz bandwidth, low  $3\Omega$  series resistance, and low 8pF shunt capacitance over a voltage range compatible with common pin electronics ICs. An on-chip voltage-doubling buffer with selectable 1x or 2x gain generates the flash supervoltage, allowing a 6.5V DAC reference input to generate up to a maximum of 13V for flash-memory programming levels.

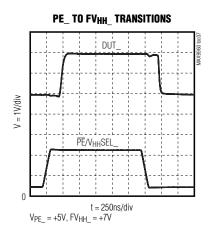

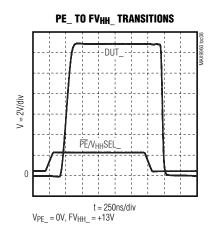

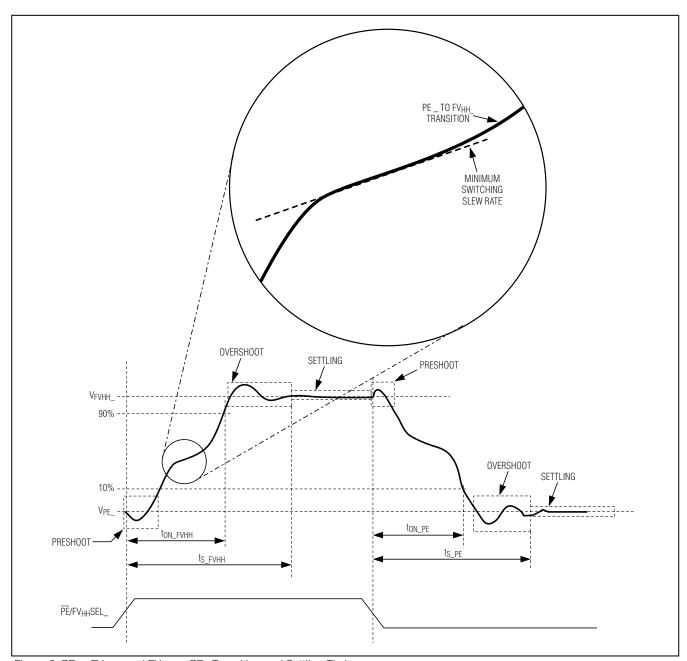

When switching from the FV<sub>HH</sub> to PE\_ or from PE\_ to FV<sub>HH</sub>, the device-under-test (DUT\_) voltage behaves monotonically. Switching transitions between the PE\_ and FV<sub>HH</sub> inputs are typically less than 350ns.

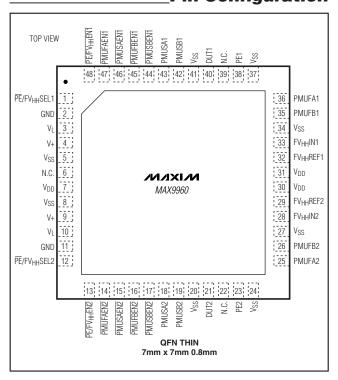

The MAX9960 operates over a commercial 0°C to +70°C temperature range, and is available in the 48-pin thin QFN package (7mm x 7mm x 0.8mm) with an exposed pad on the bottom for heat removal.

# **Applications**

Flash Memory Automatic Test Equipment SOC Automatic Test Equipment

#### **Features**

- ♦ Dual Supervoltage Switch Arrays

- ♦ 3Ω, 8pF, 600MHz Bandwidth Pin Electronics Paths

- **♦ 13V Flash Programming Paths**

- ♦ On-Chip 1x and 2x Selectable Gains

- ♦ 2 Kelvin PMU Paths

- ♦ Fast Switching: 350ns (typ)

- ♦ Monotonic Slew Rate When Switching Between PE\_ and FVHH\_

# **Ordering Information**

| PART        | TEMP<br>RANGE   | PIN-PACKAGE*                            | PKG<br>CODE |

|-------------|-----------------|-----------------------------------------|-------------|

| MAX9960BCTM | 0°C to<br>+70°C | 48 Thin QFN-EP**<br>(7mm x 7mm x 0.8mm) | T4877-6     |

<sup>\*</sup>See full package information at the end of this data sheet. \*\*EP = Exposed pad.

# Pin Configuration

## **MAX9960**

### **Part Number Table**

#### Notes:

- 1. See the MAX9960 QuickView Data Sheet for further information on this product family or download the MAX9960 full data sheet (PDF, 632kB).

- 2. Other options and links for purchasing parts are listed at: http://www.maxim-ic.com/sales.

- 3. Didn't Find What You Need? Ask our applications engineers. Expert assistance in finding parts, usually within one business day.

- 4. Part number suffixes: T or T&R = tape and reel; + = RoHS/lead-free; # = RoHS/lead-exempt. More: See full data sheet or Part Naming Conventions.

- 5. \* Some packages have variations, listed on the drawing. "PkgCode/Variation" tells which variation the product uses.

| Part Number    | Free<br>Sample | Buy<br>Direct | Package: TYPE PINS SIZE  DRAWING CODE/VAR *                                         | Temp       | RoHS/Lead-Free?<br>Materials Analysis    |

|----------------|----------------|---------------|-------------------------------------------------------------------------------------|------------|------------------------------------------|

| MAX9960BCTM-TD |                |               |                                                                                     | 0C to +70C | RoHS/Lead-Free: No                       |

| MAX9960BCTM+D  |                |               |                                                                                     | 0C to +70C | RoHS/Lead-Free: Yes                      |

| MAX9960BCTM+TD |                |               |                                                                                     | 0C to +70C | RoHS/Lead-Free: Yes                      |

| MAX9960BCTM-D  |                |               | THIN QFN;48 pin;7x7x0.8mm<br>Dwg: 21-0144F (PDF)<br>Use pkgcode/variation: T4877-6* | 0C to +70C | RoHS/Lead-Free: No<br>Materials Analysis |

Didn't Find What You Need?

CONTACT US: SEND US AN EMAIL

Copyright 2007 by Maxim Integrated Products, Dallas Semiconductor • Legal Notices • Privacy Policy

### **ABSOLUTE MAXIMUM RATINGS**

| V+ to GND0.3V to +26V                                              | Peak Current (100ns), PE±300mA                                |

|--------------------------------------------------------------------|---------------------------------------------------------------|

| V <sub>DD</sub> to GND0.3V to +16.5V                               | Peak Current (100ns), PMUS±20mA                               |

| V <sub>SS</sub> to GND6.5V to +0.3V                                | Peak Current (100ns), PMUFA_ + PMUFB_ +                       |

| V <sub>L</sub> to GND0.3V to +6V                                   | (FVHH_Path)±70mA                                              |

| V+ to V <sub>SS</sub> +32V                                         | Package Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

| Digital Inputs(GND - 0.3V) to $(V_L + 0.3V)$                       | 48-Pin QFN-EP, on Single-Layer Board                          |

| FV <sub>HH</sub> IN(the higher of -4V and                          | (derate 27.8mW/°C above +70°C)2222mW                          |

| $(V_{SS} - 0.3V)$ ) to (the lower of +10V and $(V_{DD} + 0.3V)$ )  | 48-Pin QFN-EP, on Multilayer Board                            |

| All Other Pins(V <sub>SS</sub> - 0.3V) to (V <sub>DD</sub> + 0.3V) | (derate 40.0mW/°C above +70°C)3200mW                          |

| Continuous Current, PE±120mA                                       | Operating Temperature Range0°C to +70°C                       |

| Continuous Current, PMUS±10mA                                      | Junction Temperature+150°C                                    |

| Continuous Current, PMUFA_ + PMUFB_ +                              | Storage Temperature Range65°C to +150°C                       |

| (FVHH_ Path)±45mA                                                  | Lead Temperature (soldering 10s)+300°C                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V+=+24V,\,V_{DD}=+15V,\,V_{SS}=-5V,\,V_L=+3.3V,\,T_A=+25^{\circ}C,\,unless\,\,otherwise\,\,noted.\,\,Specifications\,\,at\,\,T_A=0^{\circ}C\,\,and\,\,T_A=+70^{\circ}C\,\,degree \, T_A=-10^{\circ}C\,\,degree \, T_A=-10^{\circ}$ are guaranteed by design and characterization. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Figure 1)

| PARAMETER                   | SYMBOL             | CONDITIONS                                                                                                 | MIN   | TYP | MAX                      | UNITS |  |

|-----------------------------|--------------------|------------------------------------------------------------------------------------------------------------|-------|-----|--------------------------|-------|--|

| DC CHARACTERISTICS          | •                  | •                                                                                                          | •     |     |                          |       |  |

| PE_ PATH                    |                    |                                                                                                            |       |     |                          |       |  |

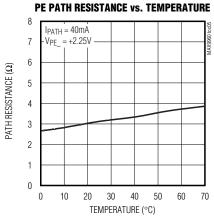

| On-Resistance               | Dov                | V <sub>DUT</sub> = +2.5V, I <sub>SW</sub> = -40mA to +40mA,<br>T <sub>A</sub> = 0°C to +30°C (Note 1)      | 2.5   | 3.0 | 3.5                      | 0     |  |

| Off-nesistatice             | RON                | $V_{DUT}$ = +2.5V, I <sub>SW</sub> = -40mA to +40mA, $T_A$ = +30°C to +70°C (Note 1)                       | 2.5   |     | 4.2                      | 4.2   |  |

| On-Resistance Flatness      | RFLAT(ON)          | V <sub>DUT</sub> _ = 0 to +5V (Note 1)                                                                     | -0.6  |     | +0.6                     | Ω     |  |

| Ch1 to Ch2 Resistance Match | Rматсн             | $V_{DUT}$ = +2.5V, $I_{SW}$ = -40mA to +40mA                                                               | -0.5  |     | +0.5                     | Ω     |  |

| Signal Voltage Range        | V <sub>PE</sub>    |                                                                                                            | -3.5  |     | +8.0                     | V     |  |

| Operating DC Current Range  | Isw                |                                                                                                            | -40   |     | +40                      | mA    |  |

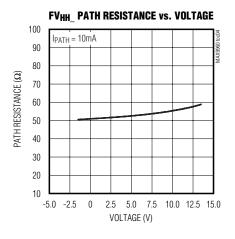

| FV <sub>HH</sub> _ PATH     |                    |                                                                                                            |       |     |                          |       |  |

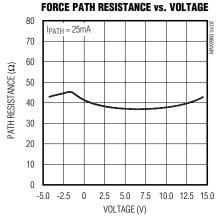

| On-Resistance               | Ron                | FV <sub>HH</sub> _ = -1.5V to (V <sub>DD</sub> - 1.5V),<br>I <sub>HH</sub> _ = -10mA to +10mA (Notes 1, 2) | 32    |     | 100                      | Ω     |  |

| Operating Voltage Range     | FV <sub>HH</sub> _ |                                                                                                            | -1.5  |     | V <sub>DD</sub> -<br>1.5 | V     |  |

| Operating DC Current Range  | Isw                |                                                                                                            | -10   |     | +10                      | mA    |  |

| FORCE PATHS                 | 1                  |                                                                                                            | •     |     |                          |       |  |

| On-Resistance               | Ron                | VPMUF = -4.25V to +14.5V,<br>IPMUF = -25mA to +25mA (Note 1)                                               |       |     | 70                       | Ω     |  |

| Operating Voltage Range     | VPMUF              |                                                                                                            | -4.25 |     | +14.5                    | V     |  |

| Operating DC Current Range  | Isw                |                                                                                                            | -25   |     | +25                      | mA    |  |

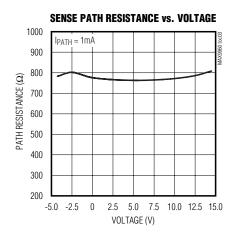

| SENSE PATHS                 |                    |                                                                                                            |       |     |                          |       |  |

| On-Resistance               | Ron                | VPMUS_ = -4.25V to +14.5V,<br>IPMUS_ = -1mA to +1mA (Note 1)                                               |       |     | 1250                     | Ω     |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+24V, V_{DD}=+15V, V_{SS}=-5V, V_L=+3.3V, T_A=+25^{\circ}C, unless otherwise noted.$  Specifications at  $T_A=0^{\circ}C$  and  $T_A=+70^{\circ}C$  are guaranteed by design and characterization. Typical values are at  $T_A=+25^{\circ}C, unless$  otherwise noted.) (Figure 1)

| PARAMETER                                | SYMBOL                            | CONDITIONS                                                                                                                                                       | MIN   | TYP  | MAX                       | UNITS |

|------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------------------------|-------|

| Operating Voltage Range                  | V <sub>PMUS</sub>                 |                                                                                                                                                                  | -4.25 |      | +14.5                     | V     |

| Operating DC Current Range               | Isw                               |                                                                                                                                                                  | -1    |      | +1                        | mA    |

| FV <sub>HH</sub> _ BUFFERS               |                                   |                                                                                                                                                                  |       |      |                           |       |

| DC Output Current                        | lodc                              | $FV_{HH} = -1.5V \text{ to } (V_{DD} - 1.5V)$                                                                                                                    | 10    |      |                           | mA    |

| Current Limit                            | l                                 | DUT_ sourcing current                                                                                                                                            | +15   |      | +25                       | mΛ    |

| Current Limit                            | ILIM                              | DUT_ sinking current                                                                                                                                             | -25   |      | -15                       | mA    |

| Operating Voltage Range                  | FV <sub>HH</sub>                  | FV <sub>HH</sub> REF_ = 0 (Note 2)                                                                                                                               | -1.5  |      | V <sub>DD</sub> -<br>1.5V | V     |

| Linearity Error                          | L <sub>ER</sub> _FV <sub>HH</sub> | FV <sub>HH</sub> REF_ = 0; no load; relative to 2-point line between V <sub>DUT</sub> _ = 0 and +13V; measured at V <sub>DUT</sub> _ = +3.25V, +6.5V, and +9.75V | -2    |      | +2                        | mV    |

| Gain                                     | GFV <sub>HH</sub>                 | FV <sub>HH</sub> REF_ = 0, no load,<br>V <sub>DUT</sub> _ = 0 to +13V (Note 3)                                                                                   | 1.98  | 2.00 | 2.02                      | V/V   |

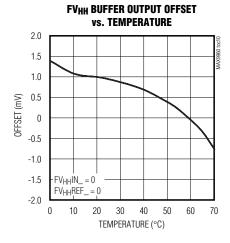

| Output Offset                            | Vos_FV <sub>HH</sub>              | FV <sub>HH</sub> REF_ = 0, V <sub>DUT</sub> _ = +12V, no load                                                                                                    | -50   |      | +50                       | mV    |

| Output Offset Temperature<br>Coefficient | T <sub>C_VOS</sub>                | V <sub>DUT</sub> = 0 to +13V, FV <sub>HH</sub> REF_ = 0,<br>T <sub>CASE</sub> = +30°C to +50°C                                                                   |       | ±0.2 |                           | mV/°C |

| Input Bias Current                       | IFV <sub>HH</sub>                 | FV <sub>HH</sub> IN_ = -1.5V to +7.5V,<br>FV <sub>HH</sub> REF_ = open                                                                                           | -25   |      | +25                       | μA    |

| Gain Resistor Ground                     | FV <sub>HHREF</sub>               | (Note 4)                                                                                                                                                         | -1.5  |      | +0.5                      | V     |

| Gain Resistor Current                    | IVHHREF                           | Measured with FV <sub>HH</sub> IN_ = +5V,<br>FV <sub>HH</sub> REF_ = 0                                                                                           |       | 0.4  |                           | mA    |

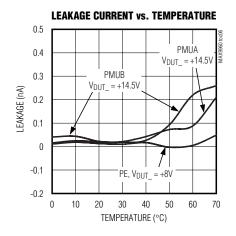

| LEAKAGE (Notes 5, 6)                     |                                   |                                                                                                                                                                  |       |      |                           |       |

| DUT_ Leakage, Disabled                   | I <sub>LEAK_OFF</sub>             | Switches S1, S2, S6, S7 open;<br>VDUT_ = -4.25V to +14.5V                                                                                                        | -1    |      | +1                        | nA    |

| PE_ Leakage                              | ILEAK_PE                          | S1 closed; S2, S6, S7 open;<br>V <sub>DUT</sub> _ = -3.5V to +8V                                                                                                 | -1    |      | +1                        | nA    |

| PMUA_ Path Leakage, Enabled              | ILEAK_PMU<br>A_ON                 | S2, S4, S6 closed; S1, S3, S5, S7 open;<br>VDUT_ = -4.25V to +14.5V                                                                                              | -1    |      | +1                        | nA    |

| PMUB_ Path Leakage, Enabled              | ILEAK_PMU<br>B_ON                 | S2, S5, S7 closed; S1, S3, S4, S6 open;<br>V <sub>DUT</sub> = -4.25V to +14.5V                                                                                   | -1    |      | +1                        | nA    |

| PMUA_ Path Leakage, Disabled             | ILEAK_PMU<br>A_OFF                | S4, S6 open; V <sub>PMUFA</sub> = -4.25V to +14.5V; measured at PMUFA with PMUSA externally connected to PMUFA                                                   | -1    |      | +1                        | nA    |

| PMUB_ Path Leakage, Disabled             | ILEAK_PMU<br>B_OFF                | S5, S7 open; V <sub>PMUFB</sub> = -4.25V to +14.5V; measured at PMUFB with PMUSB externally connected to PMUFB                                                   | -1    |      | +1                        | nA    |

| DIGITAL INPUTS (PMUF_EN_, P              | MUS_EN_, PE                       | FV <sub>HH</sub> EN_, PE/FV <sub>HH</sub> SEL_)                                                                                                                  |       |      |                           |       |

| Input High Voltage                       | VIH                               |                                                                                                                                                                  | +2.3  |      |                           | V     |

| Input Low Voltage                        | VIL                               |                                                                                                                                                                  |       |      | +0.4                      | V     |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V+ = +24V, V_{DD} = +15V, V_{SS} = -5V, V_L = +3.3V, T_A = +25^{\circ}C$ , unless otherwise noted. Specifications at  $T_A = 0^{\circ}C$  and  $T_A = +70^{\circ}C$  are guaranteed by design and characterization. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Figure 1)

| PARAMETER                                         | SYMBOL                            | CONDITIONS                                                                                                                           | MIN   | TYP  | MAX   | UNITS |  |

|---------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|--|

| Input Voltage Range                               | VIN                               |                                                                                                                                      | -0.2  |      | VL    | V     |  |

| Input Current                                     | I <sub>IH</sub> , I <sub>IL</sub> | $V_{IN} = -0.2V$ to $V_L$                                                                                                            | -10   |      | +10   | μΑ    |  |

| POWER SUPPLIES                                    |                                   |                                                                                                                                      |       |      |       |       |  |

| Positive Supply                                   | $V_{\mathrm{DD}}$                 |                                                                                                                                      | 14.5  | 15   | 16.0  | V     |  |

| Negative Supply                                   | V <sub>SS</sub>                   |                                                                                                                                      | -6.00 | -5   | -4.25 | V     |  |

| High Voltage Supply                               | V+                                | (Note 1)                                                                                                                             | 23    | 24   | 25    | V     |  |

| Logic Supply                                      | VL                                |                                                                                                                                      | 3.0   | 3.3  | 3.6   | V     |  |

| Quiescent Positive Supply<br>Current              | $\Sigma$ (I <sub>DD</sub> , I+)   | $V+=+24V,\ V_{DD}=+15V,\\ V_{SS}=-5V,\ V_L=+3.3V,\\ FV_{HH}IN_=+6.5V,\ FV_{HH}REF_=0,\\ all\ digital\ inputs=+2.3V,\ no\ loads$      |       |      | 10    | mA    |  |

| Quiescent Negative Supply<br>Current              | I <sub>SS</sub>                   | $V+=+24V,\ V_{DD}=+15V, \\ V_{SS}=-5V,\ V_L=+3.3V, \\ FV_{HH}IN\_=+6.5V,\ FV_{HH}REF\_=0, \\ all\ digital\ inputs=+2.3V,\ no\ loads$ |       |      | 8.5   | mA    |  |

| Quiescent Logic Supply Current                    | l <sub>VL</sub>                   | $V+=+24V,\ V_{DD}=+15V, \\ V_{SS}=-5V,\ V_L=+3.3V, \\ FV_{HH}IN\_=+6.5V,\ FV_{HH}REF\_=0, \\ all\ digital\ inputs=+2.3V,\ no\ loads$ |       |      | 2     | mA    |  |

| Quiescent Power Dissipation                       | P <sub>DQ</sub>                   | $V+=+24V, V_{DD}=+15V, \\ V_{SS}=-5V, V_L=+3.3V, \\ FV_{HH}IN_=+6.5V, FV_{HH}REF_=0, \\ all digital inputs=+2.3V, no loads$          |       |      | 200   | mW    |  |

| AC CHARACTERISTICS                                |                                   |                                                                                                                                      |       |      |       |       |  |

| SWITCHING TIMES BETWEEN P                         | E_ AND FVH                        | <b> PATHS</b> (Note 7) (Figure 3)                                                                                                    |       |      |       |       |  |

| Switch PE to FV <sub>HH</sub>                     | tov. 5.4.11                       | +5V to +7V transition                                                                                                                | 275   |      | 425   | no    |  |

| SWILCTIFE_ TO FVHH_                               | ton_fvhh                          | 0 to +13V transition                                                                                                                 |       | 350  | 500   | ns    |  |

| FV <sub>HH</sub> _ Settling Time                  | ts_FVHH                           | Settling to within larger of 1% step voltage or 50mV of final value                                                                  |       | 500  |       | ns    |  |

| Switch FV <sub>HH</sub> to PE_                    | ton_pe                            |                                                                                                                                      |       | 300  | 425   | ns    |  |

| PE_ Settling Time                                 | ts_pe                             | Settling to within larger of 1% step voltage or 50mV of final value                                                                  |       | 500  |       | ns    |  |

| PE_ TO FV <sub>HH</sub> _<br>Overshoot/Undershoot |                                   |                                                                                                                                      |       | ±100 |       | mV    |  |

| PE_ to FV <sub>HH</sub> _ Preshoot                |                                   |                                                                                                                                      |       | ±150 |       | mV    |  |

| Minimum Switching Slew Rate                       | SR <sub>MIN</sub>                 | Over 20% to 80% region                                                                                                               |       | ±10  |       | V/µs  |  |

| SWITCHING TIMES, SAME PATH                        | (Note 8) (Fig                     | ure 2)                                                                                                                               |       |      |       |       |  |

| PE_ Switch On-Time                                | ton_1                             | $V_{PE}$ = +5V from 47 $\Omega$ source                                                                                               |       | 150  |       | ns    |  |

| FV <sub>HH</sub> _ Switch On-Time                 | tON_2,3                           | FV <sub>HH</sub> IN_ = +2.5V, FV <sub>HH</sub> REF_ = 0                                                                              |       | 350  |       | ns    |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+24V,\,V_{DD}=+15V,\,V_{SS}=-5V,\,V_L=+3.3V,\,T_A=+25^{\circ}C,\,$  unless otherwise noted. Specifications at  $T_A=0^{\circ}C$  are guaranteed by design and characterization. Typical values are at  $T_A=+25^{\circ}C,\,$  unless otherwise noted.) (Figure 1)

| PARAMETER                                               | SYMBOL                | CONDITIONS                                                                                            | MIN TYP MA | X UNITS |

|---------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------|------------|---------|

| PMUF Switch On-Time                                     | ton_2,4<br>ton_2,5    | V <sub>PMUF</sub> = +5V                                                                               | 150        | ns      |

| PMUS Switch On-Time                                     | tON_6<br>tON_7        | VPMUS = +5V                                                                                           | 300        | ns      |

| PE_, FV <sub>HH</sub> _, PMUF, PMUS<br>Switch Off-Times | toff                  |                                                                                                       | 700        | ns      |

| CAPACITANCE AND BANDWIDT                                | <b>H</b> (Note 5)     |                                                                                                       |            |         |

| Capacitance, All Paths<br>Disconnected                  | C <sub>DUT_OFF</sub>  | All switches disconnected, for frequencies greater than 2MHz (Note 9)                                 | 20         | pF      |

| Capacitance, PE_ Path                                   |                       | Switch S1 closed, all others open, for frequencies greater than 2MHz                                  | 8          |         |

| Connected (Note 9)                                      | C <sub>DUT_PE</sub>   | Switch S1 closed, all others open, for frequencies less than 1kHz                                     | 50         | pF      |

| Unit-to-Unit Variation, PE_ Path Connected              | ΔC <sub>DUT_PE</sub>  | Switch S1 closed, all others open, for frequencies greater than 2MHz (Note 9)                         | ±2         | рF      |

| Capacitance, PMUFA_ and PMUSA_ Path Connected           | CDUT_PMUA             | S2, S4, and S6 closed; all others open (Note 9)                                                       | 35         | рF      |

| Capacitance, PMUFB_ and PMUSB_ Path Connected           | CDUT_PMUB             | S2, S5, and S7 closed; all others open (Note 9)                                                       | 35         | pF      |

| Capacitance, PMUFA_ Path<br>Disconnected                | CPMUFA_OFF            | S4 open, measured at PMUFA_ (Note 9)                                                                  | 10         | pF      |

| Capacitance, PMUFB_ Path Disconnected                   | CPMUFB_OFF            | S5 open, measured at PMUFB_ (Note 9)                                                                  | 10         | pF      |

| Capacitance, PMUSA_ Path<br>Connected                   | C <sub>PMUSA_ON</sub> | S6 closed, all others open, measured at PMUSA_ (Note 9)                                               | 10         | pF      |

| Capacitance, PMUSB_ Path<br>Connected                   | C <sub>PMUSB_ON</sub> | S7 closed, all others open, measured at PMUSB_ (Note 9)                                               | 10         | pF      |

| Capacitance, PMUSA_ Path<br>Disconnected                | CPMUSA_OFF            | S6 open, measured at PMUSA_ (Note 9)                                                                  | 5          | pF      |

| Capacitance, PMUSB_ Path Disconnected                   | CPMUSB_OFF            | S7 open, measured at PMUSB_ (Note 9)                                                                  | 5          | pF      |

| PE_ Signal Bandwidth                                    | f <sub>3DB</sub>      | Only PE_ path enabled (Note 10)                                                                       | 600        | MHz     |

| FV <sub>HH</sub> _ BUFFER                               |                       |                                                                                                       |            |         |

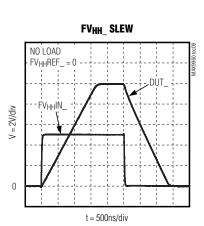

| Slew Rate                                               | SRFV <sub>HH</sub>    | FV <sub>HH</sub> REF_ = 0, (gain = 2), FV <sub>HH</sub> IN_<br>stepped from 0 to +5V and +5V to 0     | ±5         | V/µs    |

| Cottling                                                | to                    | C <sub>DUT</sub> = 200pF to within 0.1% of step voltage, after FV <sub>HH</sub> IN_ changes           | 25         |         |

| Settling                                                | ts                    | C <sub>DUT</sub> = 4000pF to within 0.1% of step voltage, after FV <sub>HH</sub> IN_changes (Note 11) | 50         | μs      |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V+ = +24V, V_{DD} = +15V, V_{SS} = -5V, V_L = +3.3V, T_A = +25^{\circ}C$ , unless otherwise noted. Specifications at  $T_A = 0^{\circ}C$  are guaranteed by design and characterization. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Figure 1)

- Note 1: V+ should be at least 8V above V<sub>DD</sub> to guarantee specified path resistance values.

- **Note 2:** When the FV<sub>HH</sub> buffer is configured for a gain of +1 (FV<sub>HH</sub>REF\_ open), the output voltage range is limited to -1.5V to +7.5V.

- Note 3: FV<sub>HH</sub>\_ buffer gain is typically +1, when FV<sub>HH</sub>REF\_ is open.

- **Note 4:** FV<sub>HH</sub>REF\_ is tested by repeating the FV<sub>HH</sub>\_ path resistance tests over the variation of FV<sub>HH</sub>REF\_. For each value of FV<sub>HH</sub>REF\_, FV<sub>HH</sub>IN\_ is adjusted to FV<sub>HH</sub>IN\_ = (FV<sub>HH</sub>\_ + FV<sub>HH</sub>REF\_) / 2.

- Note 5: All measurements taken at DUT\_, except where noted.

- **Note 6:** These specifications are guaranteed by design and characterization. In addition, these specifications will be production tested with min/max test limits of ±10nA.

- Note 7: Voltage source driving PE\_ has 47Ω source resistance. PE\_ = 0 to +5.0V, FV<sub>HH</sub>\_ = +7 to +13V. Measured from 50% point of input logic to 90% of analog swing.

- Note 8: All unused switches open, unless otherwise noted. Measured from 50% point of input logic to 90% of analog swing.

- **Note 9:** Unless otherwise noted, measured at DUT\_. No external connections to any of the switched analog pins—PE\_, DUT\_, PMUFA\_, PMUFB\_, PMUSA\_, or PMUSB\_—except as needed to make measurement.

- Note 10: Z<sub>DUT</sub> = 50Ω; equivalent bandwidth calculated from measured DUT\_ rise and fall time with PE\_ stimulated by a 3V step with 1ns 10% to 90% rise/fall time.

- Note 11: The maximum load for FV<sub>HH</sub> buffer is 4000pF.

# Typical Operating Characteristics

$(V + = +24V, V_{DD} = +15V, V_{SS} = -5V, V_{L} = +3.3V, T_{A} = +25^{\circ}C, unless otherwise noted.)$

# Typical Operating Characteristics (continued)

(V+ = +24V,  $V_{DD}$  = +15V,  $V_{SS}$  = -5V,  $V_{L}$  = +3.3V,  $T_{A}$  = +25°C, unless otherwise noted.)

# Pin Description

| PIN                                | NAME                     | FUNCTION                                                                                                                                                                                                          |

|------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                  | PE/FV <sub>HH</sub> SEL1 | PE1 or FV <sub>HH</sub> 1 Select. Selects either PE1 or FV <sub>HH</sub> 1 to be connected to DUT1. Force low to select PE1, force high to select FV <sub>HH</sub> 1.                                             |

| 2, 11                              | GND                      | Ground                                                                                                                                                                                                            |

| 3, 10                              | VL                       | Logic Power Supply. Nominally 3.3V.                                                                                                                                                                               |

| 4, 9                               | V+                       | Analog Positive Gate-Drive Power Supply. Nominally 24V.                                                                                                                                                           |

| 5, 8, 20,<br>24, 27, 34,<br>37, 41 | V <sub>SS</sub>          | Analog Negative Power Supply. Nominally -5V.                                                                                                                                                                      |

| 6, 22, 39                          | N.C.                     | No Connection. Make no connection to this pin.                                                                                                                                                                    |

| 7, 30, 31                          | $V_{DD}$                 | Analog Positive Power Supply. Nominally 15V.                                                                                                                                                                      |

| 12                                 | PE/FV <sub>HH</sub> SEL2 | PE2 or FV <sub>HH</sub> 2 Select. Selects either PE2 or FV <sub>HH</sub> 2 to be connected to DUT2. Force low to select PE2, force high to select FV <sub>HH</sub> 2.                                             |

| 13                                 | PE/FV <sub>HH</sub> EN2  | PE2 and FV <sub>HH</sub> 2 Enable. Enables PE2 and FV <sub>HH</sub> 2 to be connected to DUT2, as determined by PE/FV <sub>HH</sub> SEL2. Force low to enable signal path, force high to disable the signal path. |

| 14                                 | PMUFAEN2                 | PMUFA2 Enable. Controls the connection of PMUFA2 to DUT2. Force low to connect PMUFA2 to DUT2, force high to disconnect PMUFA2 from DUT2.                                                                         |

| 15                                 | PMUSAEN2                 | PMUSA2 Enable. Controls the connection of PMUSA2 to DUT2. Force low to connect PMUSA2 to DUT2, force high to disconnect PMUSA2 from DUT2.                                                                         |

| 16                                 | PMUFBEN2                 | PMUFB2 Enable. Controls the connection of PMUFB2 to DUT2. Force low to connect PMUFB2 to DUT2, force high to disconnect PMUFB2 from DUT2.                                                                         |

| 17                                 | PMUSBEN2                 | PMUSB2 Enable. Controls the connection of PMUSB2 to DUT2. Force low to connect PMUSB2 to DUT2, force high to disconnect PMUSB2 from DUT2.                                                                         |

| 18                                 | PMUSA2                   | Sense A Analog Output for Channel 2. Kelvin feedback output for the channel 2 force A path.                                                                                                                       |

| 19                                 | PMUSB2                   | Sense B Analog Output for Channel 2. Kelvin feedback output for the channel 2 force B path.                                                                                                                       |

| 21                                 | DUT2                     | Analog I/O for Channel 2. Connects to the DUT.                                                                                                                                                                    |

| 23                                 | PE2                      | Analog I/O for Channel 2. Connects to the pin electronics I/O.                                                                                                                                                    |

| 25                                 | PMUFA2                   | Analog Input Force A for Channel 2. Connects to an external DC resource such as a PMU.                                                                                                                            |

| 26                                 | PMUFB2                   | Analog Input Force B for Channel 2. Connects to an external DC resource such as a PMU.                                                                                                                            |

| 28                                 | FV <sub>HH</sub> IN2     | Analog Supervoltage Input for Channel 2. The voltage applied to FV <sub>HH</sub> IN2 is amplified as determined by FV <sub>HH</sub> REF2 (see the <i>Functional Block Diagram</i> ).                              |

| 29                                 | FV <sub>HH</sub> REF2    | Analog Gain-Setting Input for Channel 2. Sets the gain of the FV <sub>HH</sub> 2 buffer.                                                                                                                          |

| 32                                 | FV <sub>HH</sub> REF1    | Analog Gain-Setting Input for Channel 1. Sets the gain of the FV <sub>HH</sub> 1 buffer.                                                                                                                          |

| 33                                 | FV <sub>HH</sub> IN1     | Analog Supervoltage Input for Channel 1. The voltage applied to FV <sub>HH</sub> IN1 is amplified as determined by FV <sub>HH</sub> REF1 (see the <i>Functional Block Diagram</i> ).                              |

| 35                                 | PMUFB1                   | Analog Input Force B for Channel 1. Connects to an external DC resource such as a PMU.                                                                                                                            |

| 36                                 | PMUFA1                   | Analog Input Force A for Channel 1. Connects to an external DC resource such as a PMU.                                                                                                                            |

| 38                                 | PE1                      | Analog I/O for Channel 1. Connects to the pin electronics I/O.                                                                                                                                                    |

| 40                                 | DUT1                     | Analog I/O for Channel 1. Connects to the DUT.                                                                                                                                                                    |

| 42                                 | PMUSB1                   | Sense B Analog Output for Channel 1. Kelvin feedback output for the channel 1 force B path.                                                                                                                       |

| 43                                 | PMUSA1                   | Sense A Analog Output for Channel 1. Kelvin feedback output for the channel 1 force A path.                                                                                                                       |

## Pin Description (continued)

| PIN | NAME                    | FUNCTION                                                                                                                                                                                                          |

|-----|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44  | PMUSBEN1                | PMUSB1 Enable. Controls the connection of PMUSB1 to DUT1. Force low to connect PMUSB1 to DUT1, force high to disconnect PMUSB1 from DUT1.                                                                         |

| 45  | PMUFBEN1                | PMUFB1 Enable. Controls the connection of PMUFB1 to DUT1. Force low to connect PMUFB1 to DUT1, force high to disconnect PMUFB1 from DUT1.                                                                         |

| 46  | PMUSAEN1                | PMUSA1 Enable. Controls the connection of PMUSA1 to DUT1. Force low to connect PMUSA1 to DUT1, force high to disconnect PMUSA1 from DUT1.                                                                         |

| 47  | PMUFAEN1                | PMUFA1 Enable. Controls the connection of PMUFA1 to DUT1. Force low to connect PMUFA1 to DUT1, force high to disconnect PMUFA1 from DUT1.                                                                         |

| 48  | PE/FV <sub>HH</sub> EN1 | PE1 and FV <sub>HH</sub> 1 Enable. Enables PE1 and FV <sub>HH</sub> 1 to be connected to DUT1, as determined by PE/FV <sub>HH</sub> SEL1. Force low to enable signal path, force high to disable the signal path. |

| _   | EP                      | Exposed Pad for Heat Removal. Internally biased to VSS. Connect to VSS or leave floating.                                                                                                                         |

Figure 1. Functional Block Diagram

# Detailed Description

The MAX9960 is a dual analog switch matrix featuring two Kelvin PMU paths, a PE path, and a flash programming supervoltage circuit that allows testing of flash memory using standard PE devices. It makes possible, without the use of relays, a fully functional pin with both AC and DC capabilities.

The signal path switches feature 600MHz bandwidth,  $3\Omega$  series resistance, and 8pF shunt capacitance over a voltage range compatible with common pin-electronics ICs. The voltage-doubling buffer, with selectable 1x or 2x gain, generates the 13V flash memory programming level from a 6.5V input. Configure the switches using digital inputs  $\overline{PMUFAEN}_-$ ,  $\overline{PMUSAEN}_-$ ,  $\overline{PMUFBEN}_-$ ,  $\overline{PMUSBEN}_-$ ,  $\overline{PE/FV_{HH}EN}_-$ , and  $\overline{PE/FV_{HH}EN}_-$ , and  $\overline{PE/FV_{HH}EN}_-$ , as indicated in Tables 1 and 2.

The switching speed between PE\_ and FV<sub>HH\_</sub> paths is less than 350ns typical (Figure 3), and during switching, DUT\_ behaves monotonically.

#### **FV<sub>HH</sub> Buffer Load Capacitance**

The maximum load capacitance for the FV<sub>HH</sub> buffer is 4000pF. While this amount of load capacitance is not expected during normal operation, an application may call for the buffer to be connected to a highly capacitive PMU path occasionally for calibration purposes. No damage to the MAX9960 will result as a consequence of this condition.

#### Supervoltage FV<sub>HH</sub> Buffer Gain

The FV<sub>HH</sub> buffer gain can be selected using FV<sub>HH</sub>REF<sub>\_</sub>. If FV<sub>HH</sub>REF<sub>\_</sub> is grounded, the gain of the buffer is +2. If FV<sub>HH</sub>REF<sub>\_</sub> is left floating, the buffer gain is +1.

## **Table 1. Switch Control, All Possible Combinations**

| PMUFAEN_ | PMUFBEN_ | PMUSAEN_                   | PMUSBEN_ | PE/FV <sub>HH</sub> EN_ | PE/FV <sub>HH</sub> SEL_ | DUT_                              |

|----------|----------|----------------------------|----------|-------------------------|--------------------------|-----------------------------------|

| 0        | X        | X                          | X        | X                       | X                        | PMUFA_ path connected             |

| X        | 0        | X                          | X        | X                       | X                        | PMUFB_ path connected             |

| X        | X        | 0                          | X        | X                       | X                        | PMUSA_ path connected             |

| Х        | X        | X                          | 0        | Х                       | Х                        | PMUSB_ path connected             |

| Х        | X        | X                          | X        | 0                       | 1                        | FV <sub>HH</sub> _ path connected |

| X        | X        | X                          | X        | 0                       | 0                        | PE_ path connected                |

|          |          | Every path is disconnected |          |                         |                          |                                   |

## **Table 2. Switch Control, Use Cases**

| PMUFAEN_ | PMUFBEN_ | PMUSAEN_ | PMUSBEN_ | PE/FV <sub>HH</sub> EN_ | PE/FV <sub>HH</sub> SEL_ | DUT_                                       |

|----------|----------|----------|----------|-------------------------|--------------------------|--------------------------------------------|

| 1        | 1        | 1        | 1        | 0                       | 0                        | PE_                                        |

| 1        | 1        | 1        | 1        | 0                       | 1                        | FV <sub>HH</sub> _                         |

| 0        | 1        | 0        | 1        | 1                       | X                        | PMUFA_ + PMUSA_                            |

| 1        | 0        | 1        | 0        | 1                       | X                        | PMUFB_ + PMUSB_                            |

| 0        | 1        | 0        | 1        | 0                       | 0                        | PE_ + PMUFA_ + PMUSA_                      |

| 1        | 0        | 1        | 0        | 0                       | 0                        | PE_ + PMUFB_ + PMUSB_                      |

| 0        | 1        | 0        | 1        | 0                       | 1                        | FV <sub>HH</sub> _ + PMUFA_ + PMUSA_       |

| 1        | 0        | 1        | 0        | 0                       | 1                        | FV <sub>HH</sub> _ + PMUFB_ + PMUSB_       |

| 0        | 0        | 0        | 0        | 0                       | 0                        | PE_ + PMUFA_ + PMUSA_ +<br>PMUFB_ + PMUSB_ |

### **Power-Supply Considerations**

The MAX9960 requires four power-supply voltages, typically V+ = +24V,  $V_{DD}$  = +15V,  $V_{SS}$  = -5V, and  $V_{L}$  = +3.3V. Use a 0.1µF bypass capacitor close to each supply pin, and provide bulk bypassing where power enters the circuit board. The MAX9960 does not require any special power-up sequencing.

## Chip Information

TRANSISTOR COUNT: 2020

PROCESS: BICMOS

Figure 2. Switching Time Test Circuit

Figure 3. PE\_ - FV<sub>HH</sub>\_ and FV<sub>HH</sub>\_ - PE\_ Transition and Settling Timing

## Package Information

For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

\_ 11

## **MAX9960**

### **Part Number Table**

#### Notes:

- 1. See the MAX9960 QuickView Data Sheet for further information on this product family or download the MAX9960 full data sheet (PDF, 632kB).

- 2. Other options and links for purchasing parts are listed at: http://www.maxim-ic.com/sales.

- 3. Didn't Find What You Need? Ask our applications engineers. Expert assistance in finding parts, usually within one business day.

- 4. Part number suffixes: T or T&R = tape and reel; + = RoHS/lead-free; # = RoHS/lead-exempt. More: See full data sheet or Part Naming Conventions.

- 5. \* Some packages have variations, listed on the drawing. "PkgCode/Variation" tells which variation the product uses.

| Part Number    | Free<br>Sample | Buy<br>Direct | Package: TYPE PINS SIZE  DRAWING CODE/VAR *                                         | Temp       | RoHS/Lead-Free?<br>Materials Analysis    |

|----------------|----------------|---------------|-------------------------------------------------------------------------------------|------------|------------------------------------------|

| MAX9960BCTM-TD |                |               |                                                                                     | 0C to +70C | RoHS/Lead-Free: No                       |

| MAX9960BCTM+D  |                |               |                                                                                     | 0C to +70C | RoHS/Lead-Free: Yes                      |

| MAX9960BCTM+TD |                |               |                                                                                     | 0C to +70C | RoHS/Lead-Free: Yes                      |

| MAX9960BCTM-D  |                |               | THIN QFN;48 pin;7x7x0.8mm<br>Dwg: 21-0144F (PDF)<br>Use pkgcode/variation: T4877-6* | 0C to +70C | RoHS/Lead-Free: No<br>Materials Analysis |

Didn't Find What You Need?

CONTACT US: SEND US AN EMAIL

Copyright 2007 by Maxim Integrated Products, Dallas Semiconductor • Legal Notices • Privacy Policy